Philips TSA5521T-C3, TSA5521T-C3-M1, TSA5521M-C4, TSA5521M-C3-R1, TSA5521M-C3 Datasheet

...

DATA SH EET

Product specification

Supersedes data of 1995 Mar 16

File under Integrated Circuits, IC02

1996 Oct 10

INTEGRATED CIRCUITS

TSA5520; TSA5521

1.3 GHz universal bus-controlled

TV synthesizer

1996 Oct 10 2

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

FEATURES

• Complete 1.3 GHz single chip system

• Four PNP band switch buffers (40 mA)

• 33 V output tuning voltage

• In-lock detector

• 15-bit programmable divider

• Programmable reference divider ratio

(512, 640 or 1024)

• Programmable charge-pump current (60 or 280 µA)

• Varicap drive disable

• Universal bus protocol I

2

C-bus or 3-wire bus (the

TSA5520/TSA5521 I2C-bus mode only includes the

write mode; if both read and write modes are required

the TSA5526/TSA5527 devices should be selected):

– bus protocol for 18 or 19 bits transmission

(3-wire bus)

– extra protocol for 27 bits for test and features

(3-wire bus)

– address plus 4 data bytes transmission (I2C-bus)

– three independent I2C-bus addresses

• Low power and low radiation.

APPLICATIONS

• TV tuners and front ends

• VCR tuners.

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

TSA5520M SSOP16 plastic shrink small outline package; 16 leads; body width 4.4 mm SOT369-1

TSA5520T SO16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

TSA5521M SSOP16 plastic shrink small outline package; 16 leads; body width 4.4 mm SOT369-1

TSA5521T SO16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

1996 Oct 10 3

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

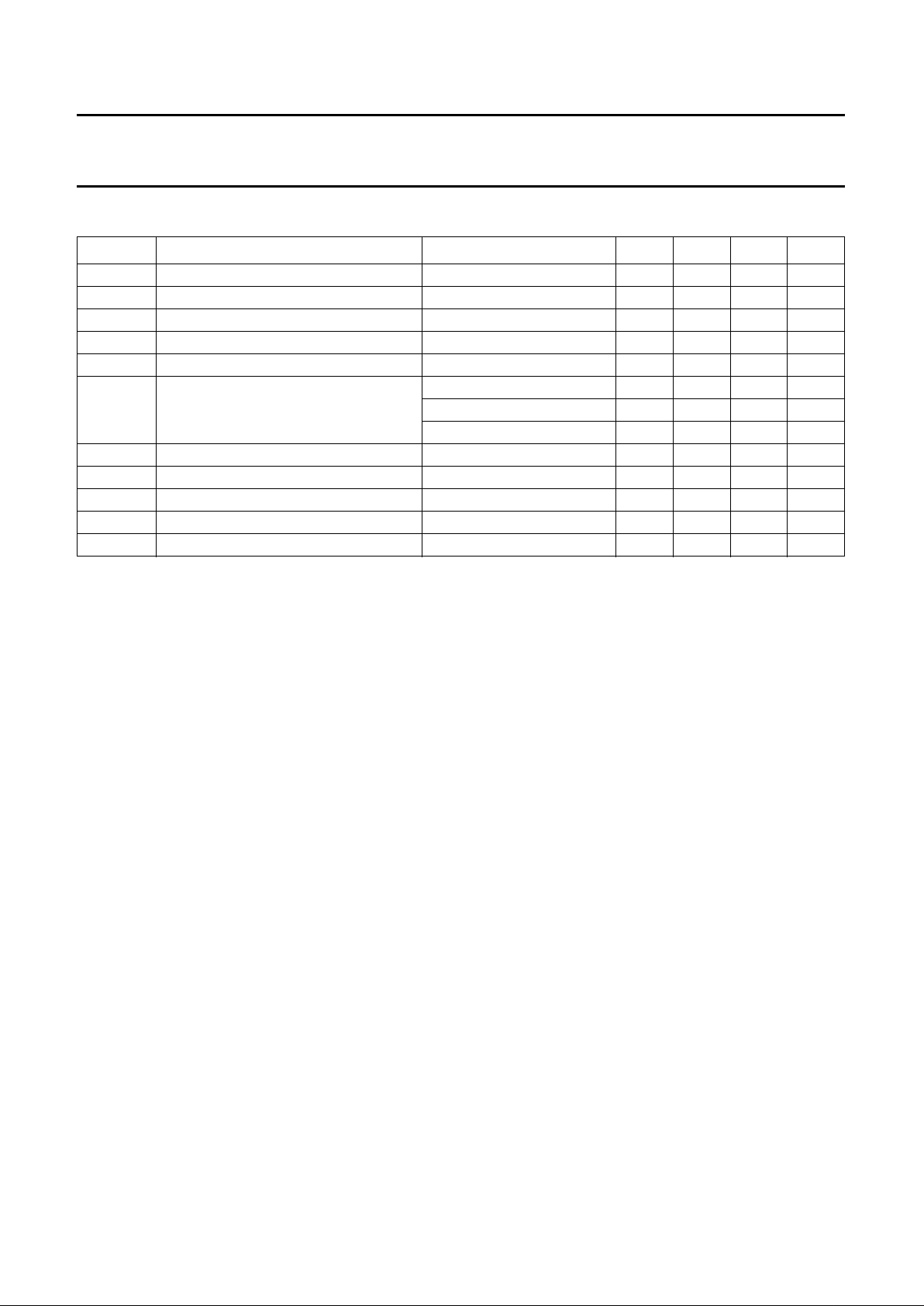

QUICK REFERENCE DATA

Notes

1. One band switch buffer ON with 40 mA.

2. One buffer ON, I

o

= 40 mA; two buffers ON, maximum sum of Io= 50 mA.

3. The power dissipation is calculated as follows:

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC1

supply voltage (+5 V) 4.5 − 5.5 V

V

CC2

band switch supply voltage (12 V) V

CC1

12 13.5 V

I

CC1

supply current − 20 25 mA

I

CC2

band switch supply current note 1 − 50 55 mA

f

RF

RF input frequency 64 − 1300 MHz

V

i(RF)

RF input voltage 80 to 150 MHz −25 − +3 dBm

150 MHz to 1 GHz −28 − +3 dBm

1 to 1.3 GHz −15 − +3 dBm

f

xtal

crystal oscillator input frequency 3.2 4.0 4.48 MHz

I

o(PNP)

PNP band switch buffers output current note 2 4 − 50 mA

P

tot

total power dissipation note 3 − 250 400 mW

T

stg

IC storage temperature −40 − +150 °C

T

amb

operating ambient temperature −20 − +85 °C

P

D

V

CC1ICC1VCC2ICC2Io

–()I

o

V

CE satPNP()

V33 2⁄()

2

27 kΩ⁄+×+×+×=

1996 Oct 10 4

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

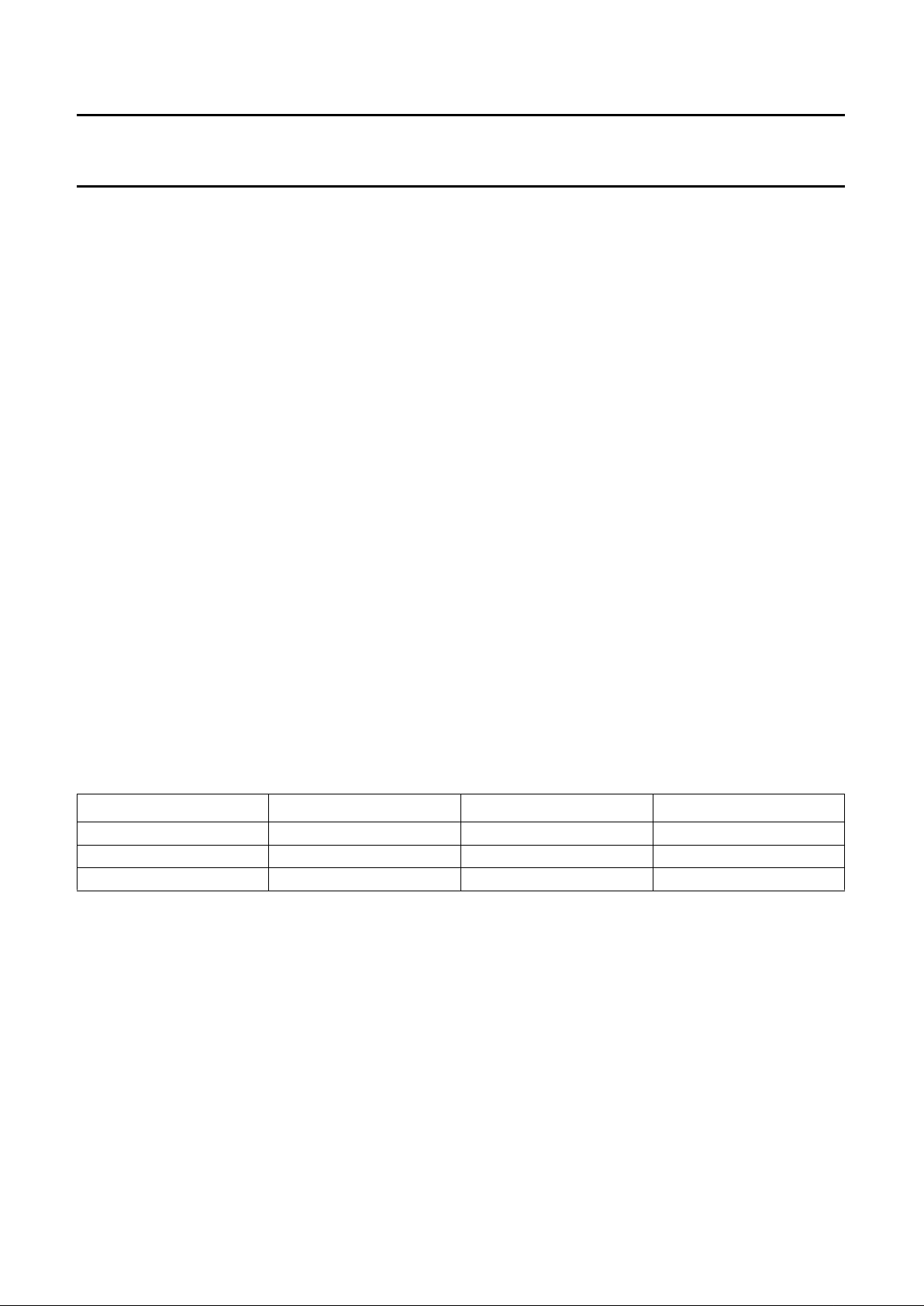

Table 1 Differences between TSA5520 and TSA5521

Notes

1. The selection of the reference divider is given by an automatic identification of the data word length.

2. The reference divider is set to 640 at power-on reset.

TYPE NUMBER DATA WORD REFERENCE DIVIDER FREQUENCY STEP (kHz)

TSA5520 18-bit 512

(1)

62.5

TSA5520 19-bit 1024

(1)

31.25

TSA5521 18-bit or 19-bit 640

(2)

50

The device has three independent I2C-bus addresses

which can be selected by applying a specific voltage on the

CE input (see Table 5). The general address C2 is always

valid. When the I2C-bus format is fully used, TSA5520 and

TSA5521 are equal.

3-wire bus format (SW = V

CC1

or open-circuit)

Data is transmitted to the device during a HIGH level on

the CE input (enable line pin 15). The device is compatible

with 18-bit and 19-bit data formats. The first four bits are

used to program the PNP band switch buffers and the

remaining bits are used to control the programmable

divider. A 27-bit data format may also be used to set the

charge-pump current, the reference divider ratio and for

test purposes. The difference between TSA5520 and

TSA5521 are given in Table 1.

When the 27-bit format is used, the TSA5520 and

TSA5521 are equal and the reference divider is controlled

by the RSA and RSB bits (see Table 7). More details are

given in Chapter “Functional description” Section “3-wire

bus mode (SW = open-circuit or V

CC1

); see

Figs 3, 4 and 5”.

GENERAL DESCRIPTION

The device is a single-chip PLL frequency synthesizer

designed for TV and VCR tuning systems. The circuit

consists of a divide-by-eight prescaler with its own

preamplifier, a 15-bit programmable divider, a crystal

oscillator and its programmable reference divider and a

phase/frequency detector combined with a charge-pump

which drives the tuning amplifier and the 33 V output.

Four high-current PNP band switch buffers are provided

for band switching. Two PNP buffers can be switched on

simultaneously. The sum of the collector currents is limited

to 50 mA.

Depending on the reference divider ratio (512, 640 or

1024), the phase comparator operates at 3.90625 kHz,

6.25 kHz or 7.8125 kHz using a 4 MHz crystal.

The lock detector output is LOW when the PLL loop is

locked. In the test mode, this output is used as a test

output for f

ref

and 1/2f

div

(see Table 6). The device can be

controlled in accordance with the I2C-bus format or the

3-wire bus format depending on the voltage applied to the

SW input (see Table 2).

I

2

C-bus format (SW = LOW)

Five serial bytes (including address byte) are required to

address the device, select the VCO frequency, program

the four PNP band switch buffers, set the charge-pump

current and the reference divider ratio.

1996 Oct 10 5

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

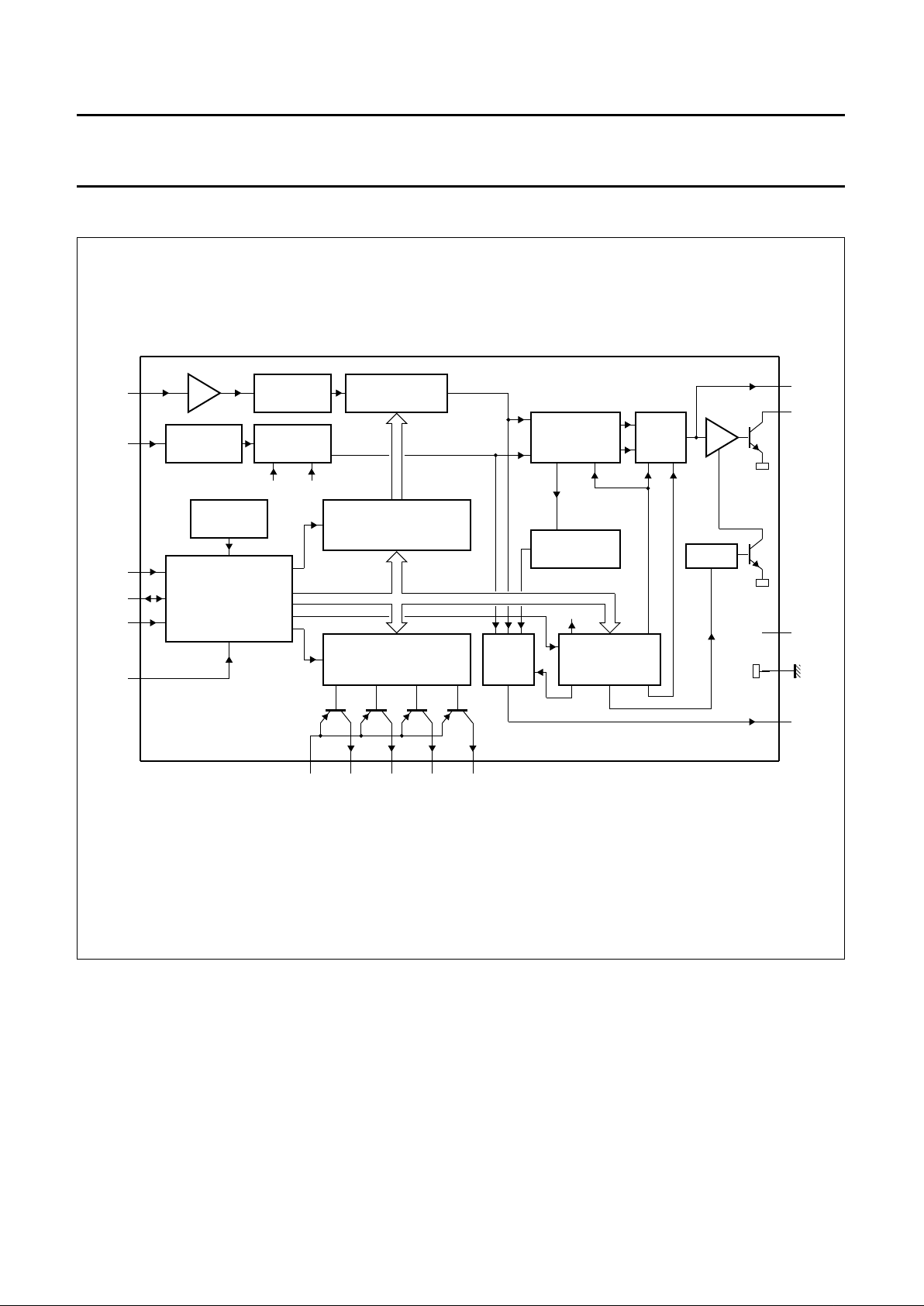

BLOCK DIAGRAM

Fig.1 Block diagram.

handbook, full pagewidth

MKA965

8

BS17BS26BS35BS4

4-BIT BAND SWITCH

REGISTER

GATE

7-BIT CONTROL

REGISTER

15-BIT FREQUENCY

REGISTER

IN-LOCK

DETECTOR

LOCK

DIGITAL

PHASE

COMPARATOR

RSA,RSB

T2,T1,T0

11

15

14

13

SCL

SDA

CE

I C/3-WIRE BUS

RECEIVER

2

T2,T1,T0

AMP

CHARGE

PUMP

9

10

LOGIC

V

CC1

V

EE

3

2

12

LOCK

4

V

CC2

SW

POWER-ON

RESET

XTAL

OSCILLATOR

DIVIDER

512/640/1024

RSA

AMP

RSB

XTAL

16

OS

CP

CP

PRESCALER

DIVIDE-BY-8

1

RF

15-BIT

PROGRAMMABLE

DIVIDER

f

div

f

ref

TSA5520

TSA5521

V

tune

1996 Oct 10 6

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

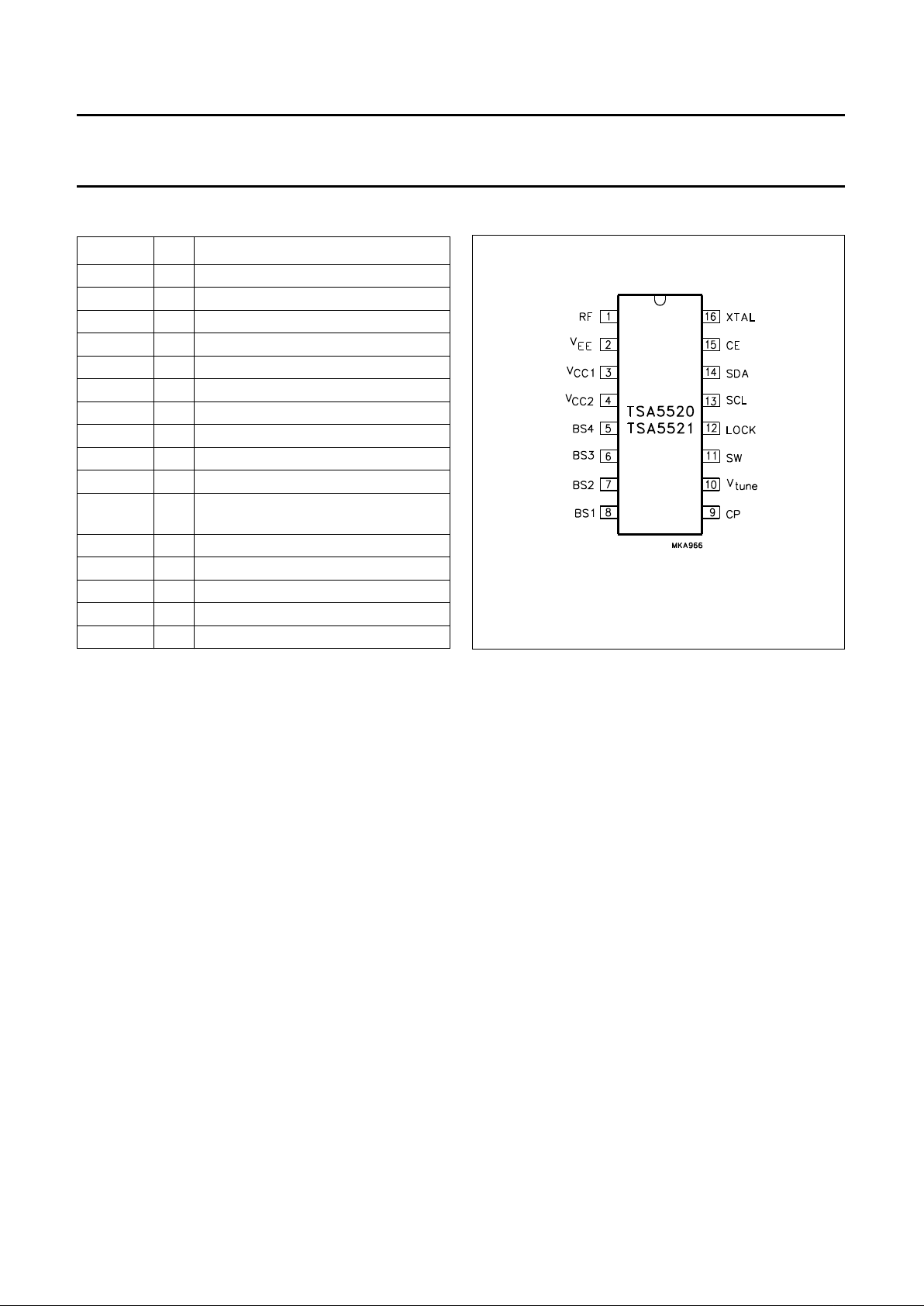

PINNING

SYMBOL PIN DESCRIPTION

RF 1 RF signal input

V

EE

2 ground

V

CC1

3 supply voltage (+5 V)

V

CC2

4 band switch supply voltage (+12 V)

BS4 5 PNP band switch buffer output 4

BS3 6 PNP band switch buffer output 3

BS2 7 PNP band switch buffer output 2

BS1 8 PNP band switch buffer output 1

CP 9 charge-pump output

V

tune

10 tuning voltage output

SW 11 bus format selection input, I

2

C-bus or

3-wire

LOCK 12 lock detector output

SCL 13 serial clock input

SDA 14 serial data input/output

CE 15 chip enable/address selection input

XTAL 16 crystal oscillator input

Fig.2 Pin configuration.

FUNCTIONAL DESCRIPTION

The device is controlled via the I2C-bus or the 3-wire bus

depending on the voltage applied to the SW input (pin 11).

A HIGH level on the SW input enables the 3-wire bus

inputs which are Chip Enable (CE), serial data input (SDA)

and serial clock input (SCL). A LOW level on the SW input

enables the I2C-bus inputs which are CE [Address

Selection (AS) input], serial data input/output (SDA) and

serial clock input (SCL). The bus format selection is given

in Table 2.

I

2

C-bus mode (SW = LOW); see Table 3

Data bytes can be sent to the device after the address

transmission (first byte). Four data bytes are required to

fully program the device. The bus receiver has an

auto-increment facility which permits the programming of

the device within one single transmission

(address + 4 data bytes).

The device can also be partially programmed providing

that the first data byte following the address is Divider

Byte 1 (DB1) or the Control Byte (CB). The bits in the data

bytes are defined in Table 3.

The first bit of the first data byte transmitted indicates

whether frequency data (first bit = 0) or control and band

switch data (first bit = 1) will follow. Until an I

2

C-bus STOP

command is sent by the controller, additional data bytes

can be entered without the need to re-address the device.

The frequency register is loaded after the 8th clock pulse

of the second Divider Byte (DB2), the control register is

loaded after the 8th clock pulse of the Control Byte (CB)

and the band switch register is loaded after the 8th clock

pulse of the Band switch Byte (BB).

I

2

C-bus address selection

The module address contains programmable address bits

(MA1 and MA0) which offer the possibility of having

several synthesizers (up to 3) in one system by applying a

specific voltage to the CE input.

The relationship between MA1 and MA0 and the input

voltage applied to the CE input is given in Table 5.

1996 Oct 10 7

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

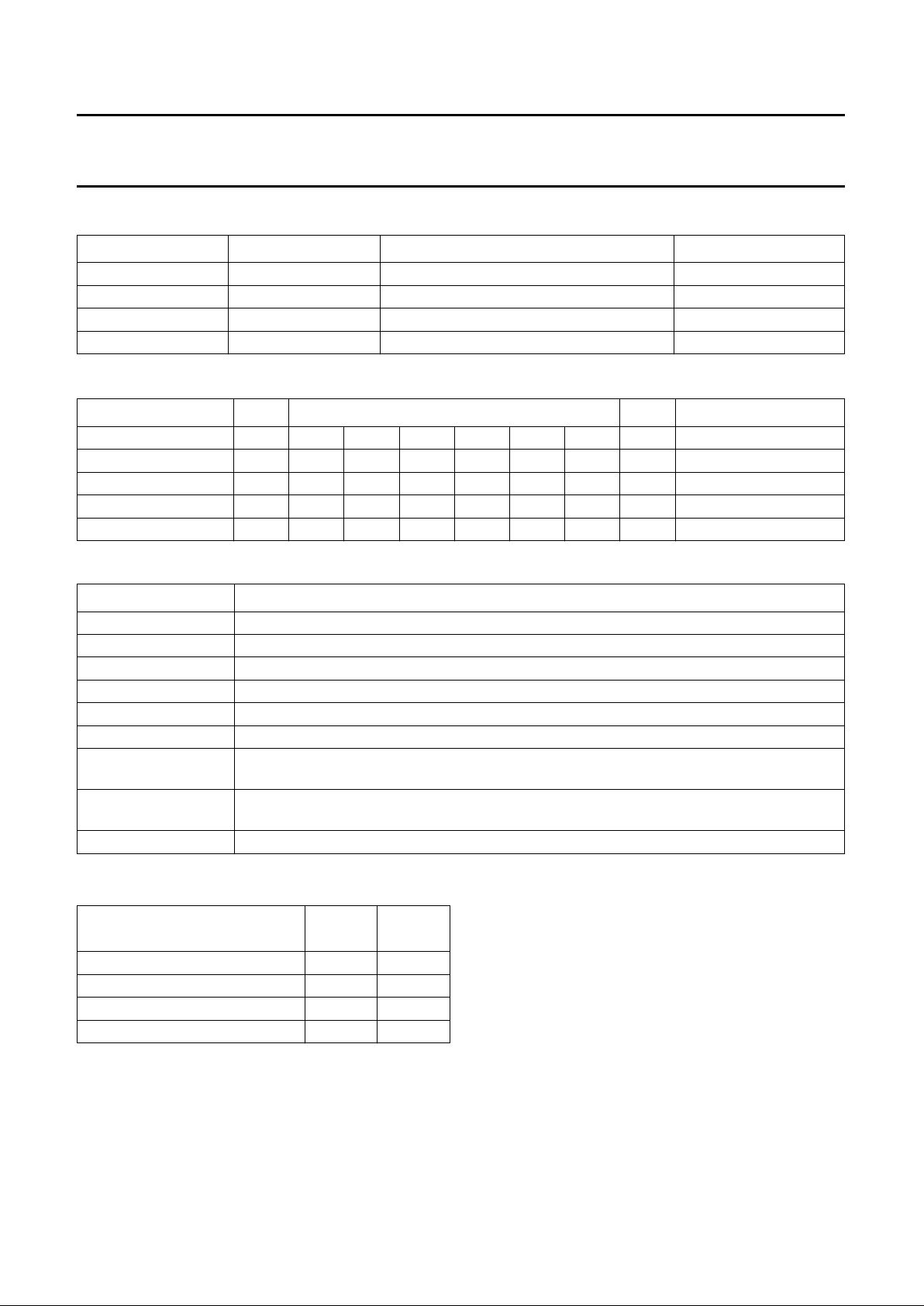

Table 2 Bus format selection

Table 3 I

2

C-bus data format

Table 4 Description of Table 3

PIN NAME 3-WIRE BUS MODE I

2

C BUS MODE

11 SW open or HIGH LOW

13 SCL clock input SCL input

14 SDA data input SDA input/output

15 CE chip enable input address selection input

BYTE MSB DATA BYTE LSB SLAVE ANSWER

Address Byte (ADB) 1 1 0 0 0 MA1 MA0 0 A

Divider Byte 1 (DB1) 0 N14 N13 N12 N11 N10 N9 N8 A

Divider Byte 2 (DB2) N7 N6 N5 N4 N3 N2 N1 N0 A

Control Byte (CB) 1 CP T2 T1 T0 RSA RSB OS A

Band switch Byte (BB) XXXXBS4BS3BS2BS1 A

SYMBOL DESCRIPTION

A acknowledge

MA1 and MA0 programmable address bits (see Table 5)

N14 to N0 programmable divider bits; N = N14 × 2

14

+ N13 × 213+ ... + N1 × 2+N0

CP charge-pump current; CP = 0 = 60 µA; CP = 1 = 280 µA

T2 to T0 test bits (see Table 6); for normal operation T2 = 0, T1 = 0 and T0 = 1

RSA and RSB reference divider ratio select bits (see Table 7)

OS tuning amplifier control bit; for normal operation OS = 0 and tuning voltage is ON;

when OS = 1 tuning voltage is OFF (high impedance)

BS4 to BS1 PNP band switch buffers control bits; when BS

n

= 0 buffer n is OFF;

when BSn= 1 buffer n is ON

X don’t care

Table 5 I2C-bus address selection

VOLTAGE APPLIED TO THE

CE INPUT (SW = LOW)

MA1 MA0

0 to 0.1V

CC1

00

Always valid 0 1

0.4V

CC1

to 0.6V

CC1

10

0.9V

CC1

to V

CC1

11

1996 Oct 10 8

Philips Semiconductors Product specification

1.3 GHz universal bus-controlled

TV synthesizer

TSA5520; TSA5521

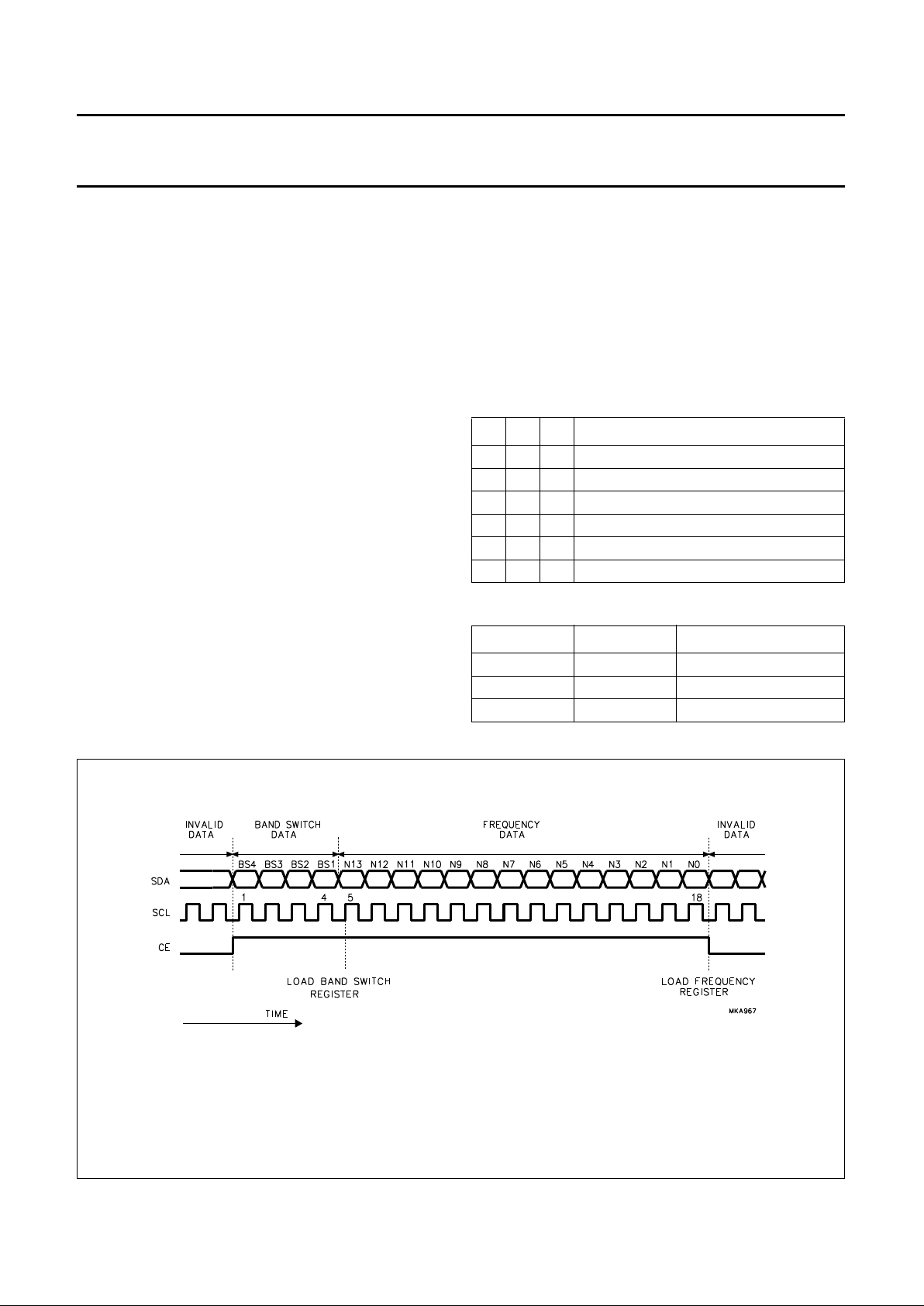

3-wire bus mode (SW = open-circuit or V

CC1

);

see Figs 3, 4 and 5

During a HIGH level on the CE input, the data is clocked

into the data register at the HIGH-to-LOW transition of the

clock pulse. The first four bits control the band switch

buffers and are loaded into the internal band switch

register on the 5th rising edge of the clock pulse.

The frequency bits are loaded into the frequency register

at the HIGH-to-LOW transition of the chip enable line when

an 18-bit or 19-bit data word is transmitted.

At power-on the charge-pump current is set to 280 µA, the

tuning voltage output is disabled (V

tune

= 33 V in

application; see Fig.12), the test bits T2, T1 and T0 are set

to the normal mode and RSB is set to 1 (TSA5520) or 0

(TSA5521). When an 18-bit data word is transmitted, the

most significant bit of the divider N14 is internally set to 0

and bit RSA is set to 1. When a 19-bit data word is

transmitted, bit RSA is set to 0.

When a 27-bit word is transmitted, the frequency bits are

loaded into the frequency register on the 20th rising edge

of the clock pulse and the control bits at the HIGH-to-LOW

transition of the chip enable line. In this mode, the

reference divider is given by the RSA and RSB bits (see

Table 7). The test bits T2, T1 and T0, the charge-pump

bit CP, the ratio select bit RSB and the OS bit can only be

selected or changed with a 27-bit transmission. They

remain programmed if an 18-bit or a 19-bit transmission

occurs. Only RSA is controlled by the transmission length

when the 18-bit or 19-bit format is used.

A data word of less than 18 bits will not affect the

frequency register of the device. The definition of the bits

is unchanged compared to the I2C bus mode.

The power-on detection threshold voltage V

POR

is fixed to

V

CC1

= 2 V at room temperature. Below this threshold, the

device is reset to the power-on state described above.

Table 6 Test bits

Table 7 Ratio select bits

T2 T1 T0 DEVICE OPERATION

0 0 1 normal mode

0 1 X charge-pump is OFF

1 1 0 charge-pump is sinking current

1 1 1 charge-pump is sourcing current

100f

ref

is available at LOCK output

101

1

⁄2f

div

is available at LOCK output

RSA RSB REFERENCE DIVIDER

X 0 640

0 1 1024

1 1 512

Fig.3 Normal mode; 18-bit data format (RSA = 1).

For TSA5520 bit RSB =1 at power-on; the reference divider is 512 or 1024.

For TSA5521 bit RSB = 0 at power-on; the reference divider is 640.

For TSA5520/TSA5521 the value of RSB can also be programmed by using the 27-bit data format. When returning to the normal mode, bit RSB remains

as programmed with the 27-bit data word.

Loading...

Loading...