INTEGRATED CIRCUITS

DATA SH EET

TDA9873H

Multistandard dual carrier stereo

sound decoder

Product specification

File under Integrated Circuits, IC02

1999 Apr 26

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

FEATURES

• Low power consumption

• Alignment-free multistandard FM sound demodulation

• No external intercarrier sound band-pass filters required

• Auto mute switchable via I2C-bus

• Multistandard A2 stereo sound decoder

• No adjustment for reduced channel separation

requirement

• De-emphasis time constant related to standard

• Very reliable digital identification of sound transmission

mode via I

• No external filter for pilot input required

• I2C-bus transceiver with MAD (Module ADdress)

• I2C-bus control for all functions

• Stabilizer circuit for ripple rejection and constant output

level

• Additional mono output

• Pin aligned with TDA9874AH

• ESD protection on all pins.

2

C-bus, alignment-free

GENERAL DESCRIPTION

The TDA9873H is an economic multistandard dual FM

demodulator and analog carrier stereo decoder with

2

I

C-bus control.

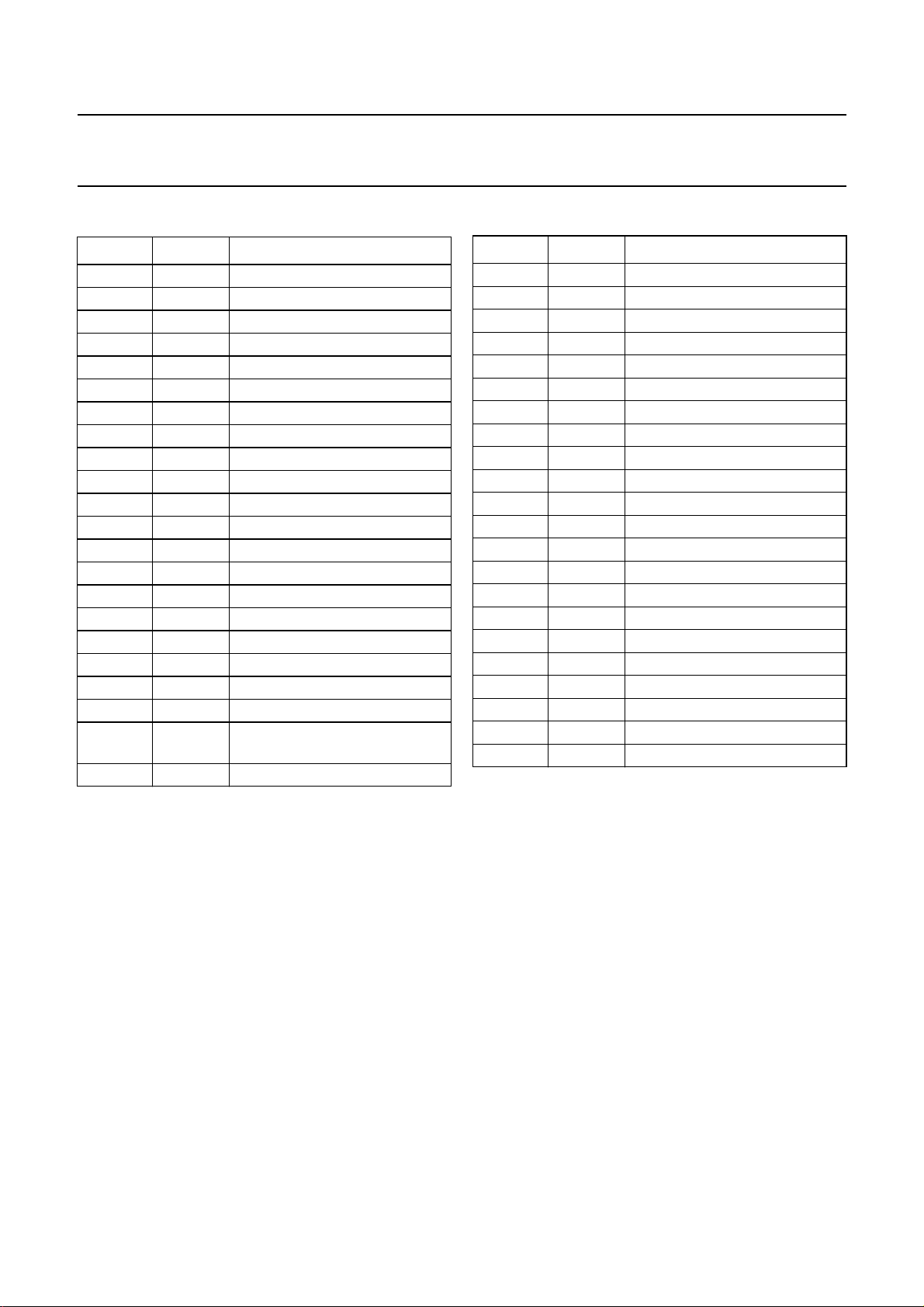

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

TDA9873H QFP44 plastic quad flat package; 44 leads (lead length 2.35 mm);

body 14 × 14 × 2.2 mm

SOT205-1

1999 Apr 26 2

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

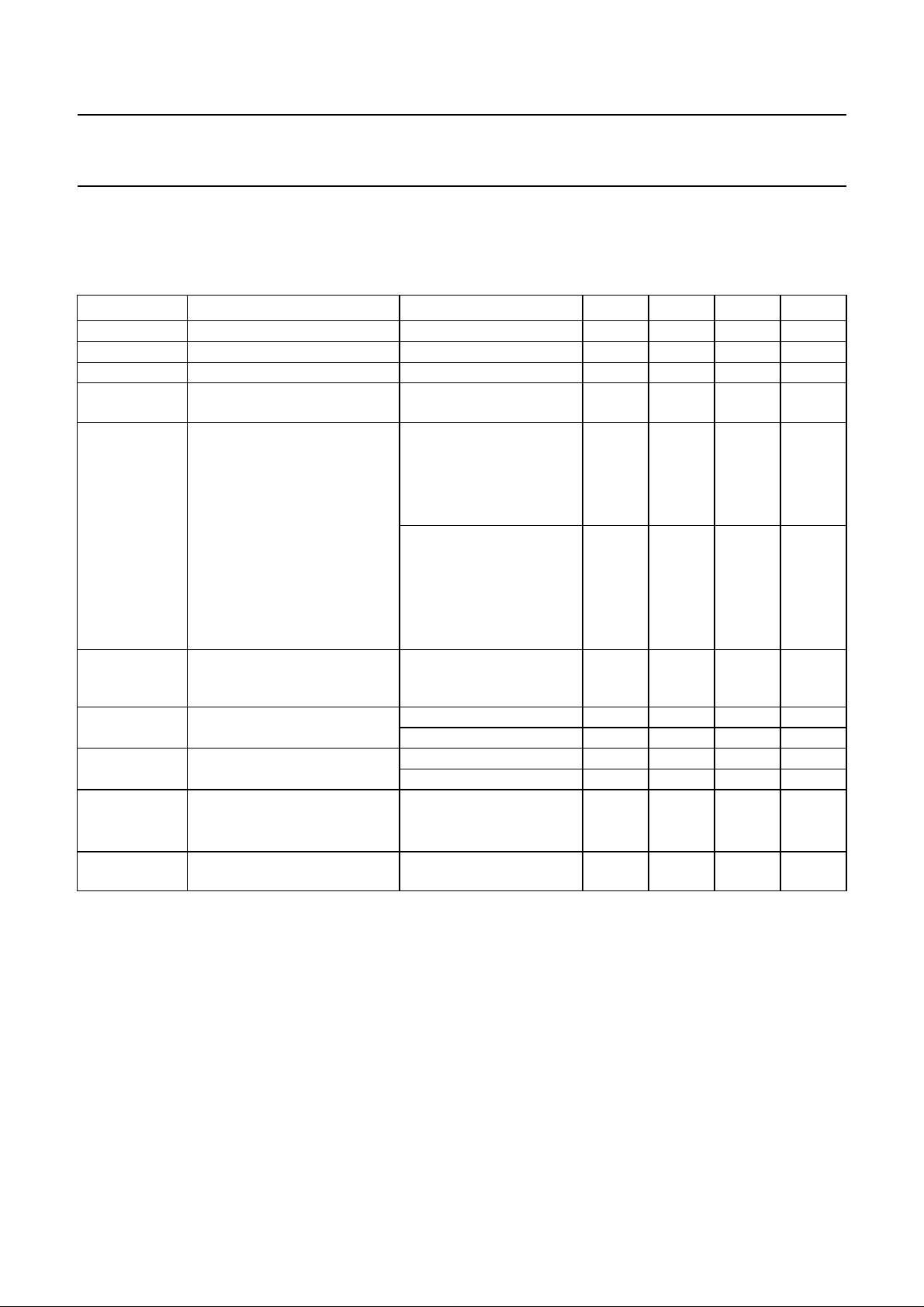

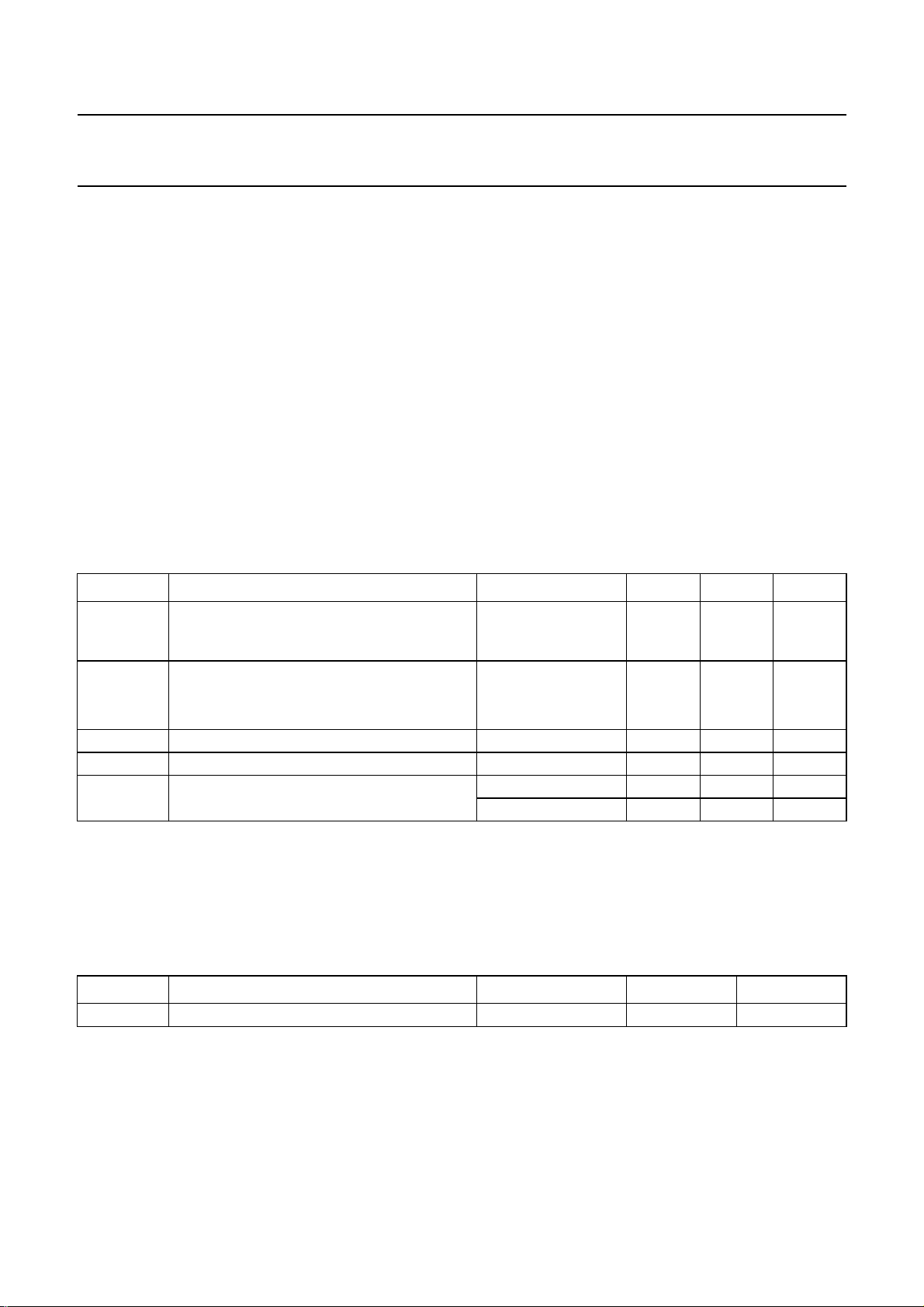

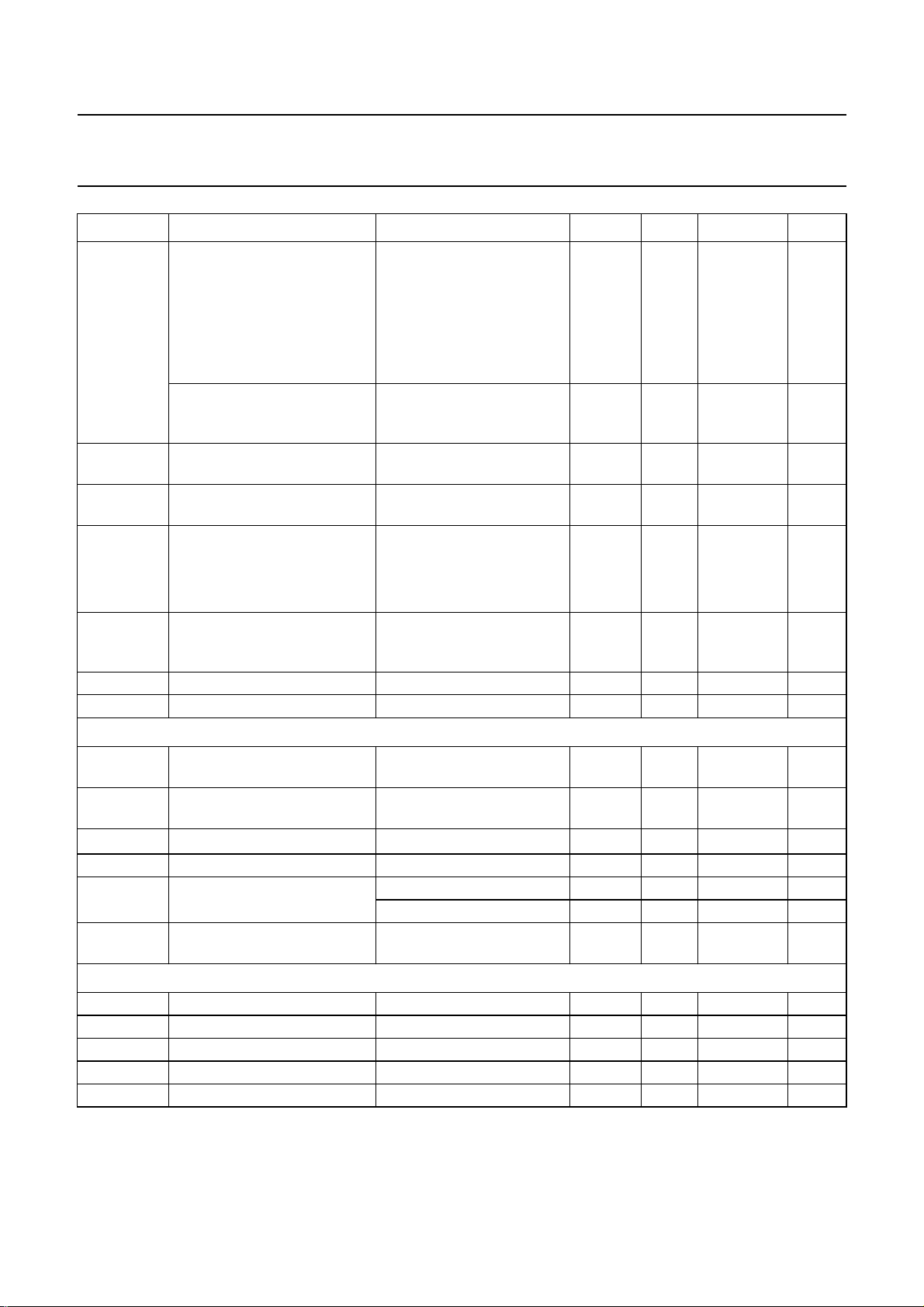

QUICK REFERENCE DATA

V

=5V; T

CC

f

= 1 kHz, L = R, stereo mode); input level for first SC V

mod

of Figs 7 and 8; unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

I

CC

V

o(rms)

V

o(cl)(rms)

f

i(FM)

S/N

W

t

ident(on)

V

i(FM)(rms)

α

cs(AF)(stereo)

α

ct(AF)(dual)

=25°C; B/G standard (f

amb

= 5.5 MHz, f

SC1

= 5.742 MHz, SC1/SC2= 7 dB, ∆fAF= 27 kHz,

SC2

i(FM)(rms)

=50mV; f

= 4.000 MHz; measured in test circuit

ref

supply voltage 4.5 5 6.6 V

supply current 40 60 75 mA

AF output level (RMS value) 54% modulation; note 1 400 500 600 mV

clipping level of the output

THD < 1.5% 1400 −−mV

signal level (RMS value)

FM-PLL operating frequencies

(switchable)

1st sound carrier

M standard − 4.5 − MHz

B/G standard − 5.5 − MHz

I standard − 6.0 − MHz

D/K standard − 6.5 − MHz

2nd sound carrier

M standard − 4.72 − MHz

B/G standard − 5.74 − MHz

D/K (1) standard − 6.26 − MHz

D/K (2) standard − 6.74 − MHz

D/K (3) standard − 5.74 − MHz

weighted signal-to-noise ratio

(complete signal path)

CCIR 468-4 weighted;

quasi peak; dual mode;

52 56 − dB

B/G standard; note 1

total identification time on for

identification mode change

FM-PLL input sensitivity for

pull-in (RMS value)

AF channel separation (stereo

mode; complete signal path)

AF crosstalk attenuation (dual

normal mode; note 2 0.35 − 2s

fast mode; note 2 0.1 − 0.5 s

1st carrier −−6mV

2nd carrier −−1mV

B/G standard; note 3

without alignment 25 30 − dB

2

I

C-bus alignment 40 45 − dB

65 70 − dB

mode; complete signal path)

Notes

1. Condition for B/G, I and D/K standard: V

= 5 V and ∆f = 27 kHz (m = 54%).

CC

Condition for M standard: VCC= 5 V and ∆f = 13.5 kHz; 6 dB gain added internally, to compensate smaller deviation.

2. The maximum total system identification time on for a channel change is equal to maximum value of t

t

I2C read-out

identification time off for a channel change is equal to maximum value of t

(

see also “The I2C-bus and how to use it”

(order number 9398 393 40011)). The maximum total system

plus t

ident(off)

I2C read-out

ident(on)

. The fast mode is

proposed mainly during search tuning, program or channel select. If the channel is selected, the identification

response should be switched to normal mode for improved reliability. However due to the transition from fast to

normal mode, the identification bits are not valid for one integrator period. Therefore the transmitter mode detected

during the fast mode has to be stored before changing to normal mode. The storage has to be kept for two seconds

(maximum value of t

in the normal mode) from the moment of transition. The identification can now operate in

ident(on)

the normal mode until the next tuning action.

3. R modulated, L monitored.

1999 Apr 26 3

plus

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Apr 26 4

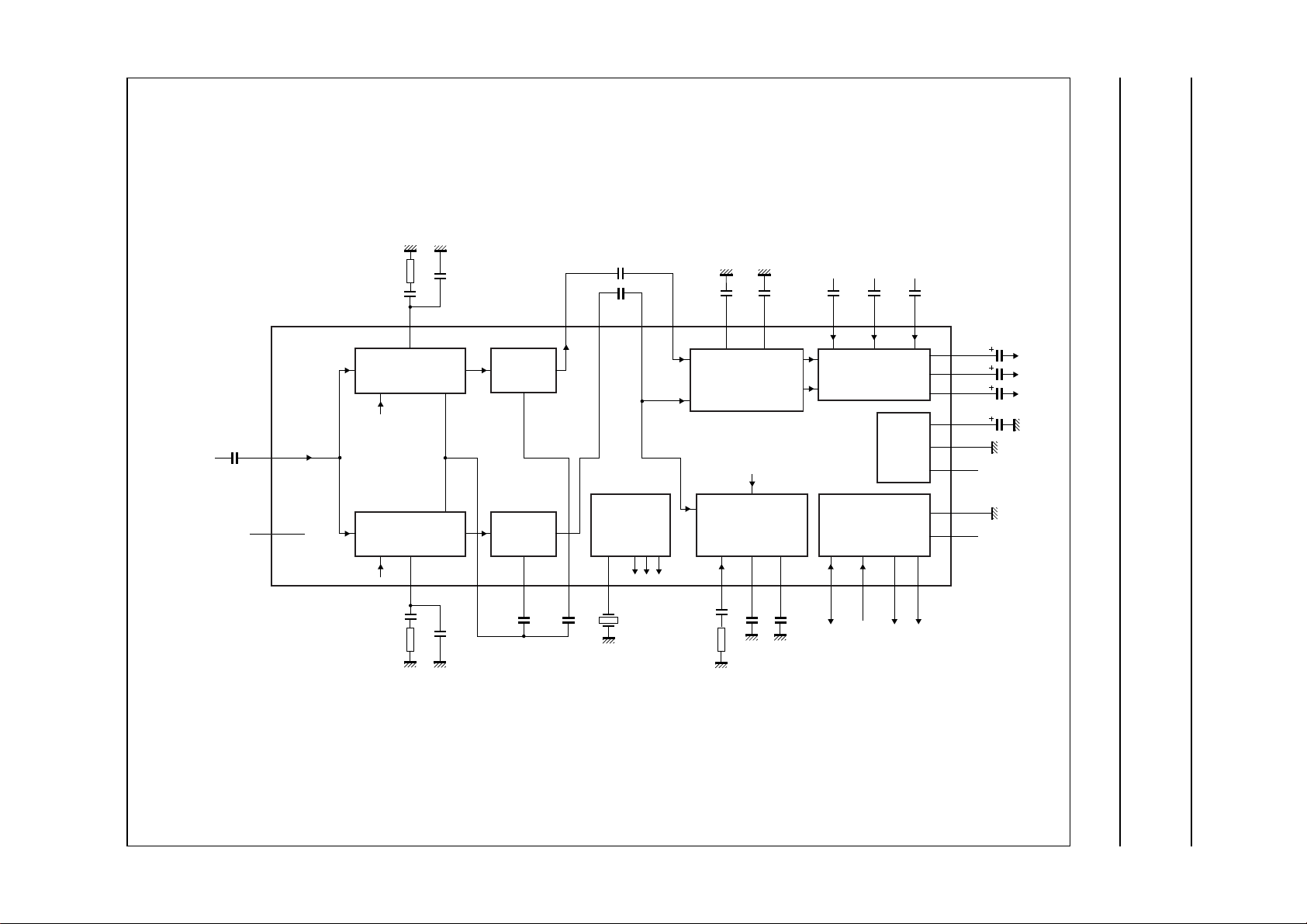

handbook, full pagewidth

BLOCK DIAGRAM

Multistandard dual carrier stereo sound decoder TDA9873H

Philips Semiconductors Product specification

IF

intercarrier

input

4.5, 5.5, 6.0, 6.5

4.72, 5.74, 6.26,

6.74 MHz

IFINT

n.c.

25

4, 5, 9, 11, 12,

16, 17, 19, 20,

22, 23, 36, 44

loop filter

LF1

14

FM DEMODULATOR

NARROW-BAND PLL

SC1

FM DEMODULATOR

NARROW-BAND PLL

SC2

18

LF2

loop filter

AF

AMPLIFIER

1

AF

AMPLIFIER

2

26

AFR13CAF2

AF1O AF2O

32

10

DIGITAL

ACQUISITION

OSCILLATOR

CLOCK

15

24

XTAL

CAF1

4 MHz

external AF

mono stereo

M

R

L

AF1IAF2I

8

33

CDE16CDE2

3

STEREO DECODER

STEREO ADJUST

B/G, D/K, I, M (Korea)

STANDARD

TDA9873H

DIGITAL

IDENTIFICATION

PILOT

NARROW-BAND PLL

34

LPF31CID35CTRIG

pilot

loop

EXTM

EXTR

EXTL

38

39

40

AF SWITCH

POWER

SUPPLY

2

C-BUS

I

TRANSCEIVER

SDA30SCL29P137P2

1

OUTL

2

OUTR

43

OUTM

V

41

ref

AGND

7

V

CC

28

DGND27

MAD21

42

MHB429

Fig.1 Block diagram.

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

PINNING

SYMBOL PIN DESCRIPTION

OUTL 1 left audio output

OUTR 2 right audio output

CDE1 3 de-emphasis 1 capacitor

n.c. 4 not connected

n.c. 5 not connected

CDE2 6 de-emphasis 2 capacitor

AGND 7 analog ground

AF1I 8 audio 1 input

n.c. 9 not connected

AF1O 10 audio 1 output

n.c. 11 not connected

n.c. 12 not connected

AFR 13 AF1/2 signal return

LF1 14 loop filter 1

XTAL 15 4 MHz reference input

n.c. 16 not connected

n.c. 17 not connected

LF2 18 loop filter 2

n.c. 19 not connected

n.c. 20 not connected

MAD 21 programmable address bit

(module address)

n.c. 22 not connected

SYMBOL PIN DESCRIPTION

n.c. 23 not connected

CAF1 24 audio 1 (AF1) capacitor

IFINT 25 IF intercarrier input

CAF2 26 audio 2 (AF2) capacitor

DGND 27 digital ground

V

CC

SCL 29 serial clock input (I

28 supply voltage (+5 V)

2

C-bus)

SDA 30 serial data input/output (I

LPF 31 pilot loop filter

AF20 32 audio 2 output

AF2I 33 audio 2 input

CTRIG 34 trigger capacitor

CID 35 identification capacitor

n.c. 36 not connected

P1 37 output port 1

EXTM 38 external audio input mono

EXTR 39 external audio input right

EXTL 40 external audio input left

V

ref

41 reference voltage (1⁄2VCC)

P2 42 output port 2

OUTM 43 mono output

n.c. 44 not connected

2

C-bus)

1999 Apr 26 5

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

handbook, full pagewidth

ref

n.c.

44

OUTM

43

P2

42

V

41

EXTL

EXTR

403938

EXTM

P1

37

n.c.

36

CID

35

CTRIG

34

OUTL

OUTR

CDE1

n.c.

n.c.

CDE2

AGND

AF1I

n.c.

AF1O

n.c.

22

n.c.

33

32

31

30

29

28

27

26

25

24

23

MHB430

AF2I

AF2O

LPF

SDA

SCL

V

CC

DGND

CAF2

IFINT

CAF1

n.c.

1

2

3

4

5

6

7

8

9

10

11

12

13

n.c.

AFR

14

LF1

TDA9873H

15

16

n.c.

XTALI

17

n.c.

18

LF2

19

n.c.

20

n.c.

21

MAD

Fig.2 Pin configuration.

1999 Apr 26 6

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

FUNCTIONAL DESCRIPTION

FM demodulators

The FM demodulators are Narrow-Band PLLs (NBPLLs)

with external loop filters, to provide the required selectivity.

To achieve good selectivity, linear Phase Detectors (PDs)

and constant input levels are required. The intercarrier

signal from the input terminal is fed via high-pass filters

and gain controlled amplifiers to the phase detectors.

A carrier cancellation circuit placed before the amplifier for

the second PLL is used to reduce the first sound carrier.

The PD output signals control the integrated relaxation

oscillators via the loop filters. The frequency range is

approximately 4 to 7 MHz. As a result of locking, the

oscillator frequency tracks with the modulation of the input

signal and the oscillator control voltages are

superimposed by the AF voltages. Using this method, the

FM-PLLs operate as FM demodulators. The AF voltages

are present at the loop filters and fed via buffers with 0 dB

gain to the audio amplifiers. The supported standards and

their characteristics are given in Table 1.

Digital acquisition help

A narrow-band PLL requires a measure to lock to the

wanted input signal. Each relaxation oscillator of the three

integrated PLLs (1st and 2nd sound carriers and pilot

carrier) has a wide frequency range. To guarantee correct

locking of the PLL with respect to the catching range, the

digital acquisition help provides individual control until the

VCO frequency is within the standard and PLL dependent

lock-in window, related to the standard dependent carriers.

It ensures that the oscillator frequency of the FM-PLL is

within ±225 kHz of the sound carrier to be demodulated.

The pilot carrier frequency window is ±150 Hz.

The working principal of the digital acquisition help is as

follows: The VCOs are connected, one at a time, to a

down-counter. The counter start value is standard

dependent and predefined for each of the three PLLs.

After a given counting time the stop value of the

down-counter is probed.

In an endless circle the VCO of the next PLL will be

connected to the down-counter and the described

procedure starts again.

The whole tracing as well as the counting time itself is

derived from the external frequency reference. The cycle

time is 256 µs.

Auto mute

If a sound carrier is missed, acquisition pulses are

generated when the NBPLL frequency leaves the window

edges. To avoid noise at the audio output, an I2C-bus

switchable mute-enable stage is built in. If auto mute is

enabled via the I

after the first acquisition pulse. If a sound carrier occurs

(no further acquisition pulses), the mute stage

automatically returns to active mode after 40 ms.

If the 1st sound carrier is not present, the 2nd audio

channel will also be muted.

Audio preamplifier

The AF preamplifiers are operational amplifiers with

internal feedback, high gain and high common mode

rejection. The AF voltages from the PLL demodulators

(small output signals) are amplified by approximately

34 dB. Using a DC operating point control circuit, the AF

amplifiers are decoupled from the PLL DC voltage.

The amplified AF signals are available at the output

terminals and fed via external decoupling capacitors to the

stereo decoder input terminals.

Stereo decoder

The input circuit incorporates a soft-mute stage which is

controlled by the FM-PLL acquisition circuit. The auto

mute function can be disabled via the I

The AF output voltage is 500 mV (RMS) for 54%

modulation, clipping therefore may occur at high

over-modulation. If more headroom is required the input

signal can be attenuated by 6 dB via the I2C-bus.

2

C-bus, the circuit mutes immediately

2

C-bus.

If the stop value is lower (higher) than the expected value

range, the VCO frequency is higher (lower) than the lock-in

window. A negative (positive) control current is injected

into the loop filter for a short time, thereby decreasing

(increasing) the VCO frequency by a proportional value.

If the stop value meets the expected value range, the VCO

frequency is within the defined lock-in window and no

control current is injected into the loop filter.

1999 Apr 26 7

A stereo adjustment (see Fig.6) is incorporated to correct

the FM demodulator output voltage spread, see Table 19.

If no I2C-bus adjustment is required (potentiometer

adjustment or no adjustment) the default value should be

0 dB for B/G, M and D/K (2) standard. For the standards

D/K (1) and D/K (3) the 2nd sound carrier frequency is

below the1st sound carrier which results in a lower AF

output level for the 2nd sound carrier. In this state, a gain

of +0.1 dB for D/K (1) and +0.2 dB for D/K (3) is preferred.

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

In the following dematrix, the modes stereo, mono and

dual are processed for the different standards. The 6 dB

level difference between B/G and M standard is

automatically compensated in the dematrix, therefore no

further level adaption is needed.

De-emphasis is performed by two RC low-pass filter

networks with internal resistors and external capacitors.

The time constant is automatically switched to 50 µs or

75 µs according to the chosen standard.

Due to some frequency response peaking of the FM

demodulation, compensation is necessary. This is done by

having a slightly larger time constant for the de-emphasis.

All other settings such as AF switch, stereo channel

adjustment values or default corrections have to be

controlled via the I2C-bus depending on the identification

or user definition.

AF switch

The circuit incorporates a single stereo and mono AF

output. Using rail-to-rail operational amplifiers, the clipping

level is set to 1.4 V (RMS) for V

CC

=5V.

As well as the internal stereo decoder output signal, one

external stereo and one mono input can be switched to the

AF outputs. Both the mono and stereo outputs can be

switched independent of the internal or external sources,

see Tables 15 and 25. Fig.6 shows the switch

configurations.

A nominal gain of 0 dB for the signals from the external

inputs to the outputs is built-in.

Stereo/dual sound identification

The pilot signal is fed to the input of a NBPLL. The PLL

circuit generates the synchronized pilot carrier. This carrier

is used for the synchronous AM-demodulation to get the

low-pass filtered identification signal.

A Schmitt trigger circuit performs pulse shaping of the

identification signal when the signal level is higher than the

Schmitt trigger threshold. For smaller signal levels there is

no AC output signal, thus protecting against

mis-identification caused by spurious signal components.

The identification stages consist of two digital PLL circuits

and digital integrators to generate the stereo or dual sound

identification bits, which can be read out via the I

2

C-bus.

A 4 MHz crystal oscillator provides the reference clock

frequency. The corresponding detection bandwidth is

larger than ±50 Hz for the pilot carrier signal, so that f

pilot

variations from the transmitter can be tracked in the event

of missing synchronization with the horizontal frequency

fH. However, the detection bandwidth for the identification

signal is limited to approximately ±1 Hz for high

identification reliability.

2

C-bus transceiver

I

The TDA9873H is microcontroller controlled via a 2-wire

I2C-bus.

Two wires, serial data (SDA) and serial clock (SCL) carry

information between the devices connected to the bus.

The TDA9873H has an I2C-bus slave transceiver with

auto-increment.

To avoid conflicts in applications with other ICs providing

similar or complementary functions, two slave addresses

are available, selected on the pin MAD. A slave address is

sent from the master to the slave receiver.

In the TV sound processor family several devices are

available. To identify the TDA9873H device, the master

sends a slave address with R/W bit = 0. The slave then

generates an acknowledge and the master sends the data

subaddress 254 to the slave, followed by an acknowledge

from the slave to the master. The master then sends the

slave address with R/W bit = 1. The slave then transmits

the device identification code 80H to the master, followed

by an acknowledge NOT and a STOP condition generated

by the master.

Control ports

Two digital open-collector output ports P1 and P2 provide

external switching functions in the receiver front-end or

IF demodulators. The ports are controlled by the I

2

C-bus

(see Tables 22 and 23) and are freely programmable.

1999 Apr 26 8

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

Power supply

The different supply voltages and currents required for the

analog and digital circuits are derived from two internal

band gap reference circuits. One of the band gap circuits

internally generates a voltage of approximately 2.4 V,

independent of the supply voltage and temperature.

A voltage regulator circuit, connected to this voltage,

produces a constant voltage of 3.55 V which is used as an

internal reference voltage. The AF reference voltage V

1

⁄2VCC. Good ripple rejection is achieved with the external

capacitor C

= 100 µF (16 V) in combination with an

ref

ref

internal resistor at pin 6. No additional DC load for1⁄2V

Power-on reset

When a power-on reset is activated by switching on the

supply voltage or because of a supply voltage breakdown,

the 117/274 Hz DPLL, 117/274 Hz integrator and the

registers will be reset. Both AF channels (main and mono)

are muted. The ports are in position HIGH. Gain stereo

adjustment is 0 dB. Auto mute is active. For detailed

information see Table 12.

is

CC

is allowed.

Analog ground (AGND, pin 7) and digital ground

(DGND, pin 27) should be connected directly to the IC.

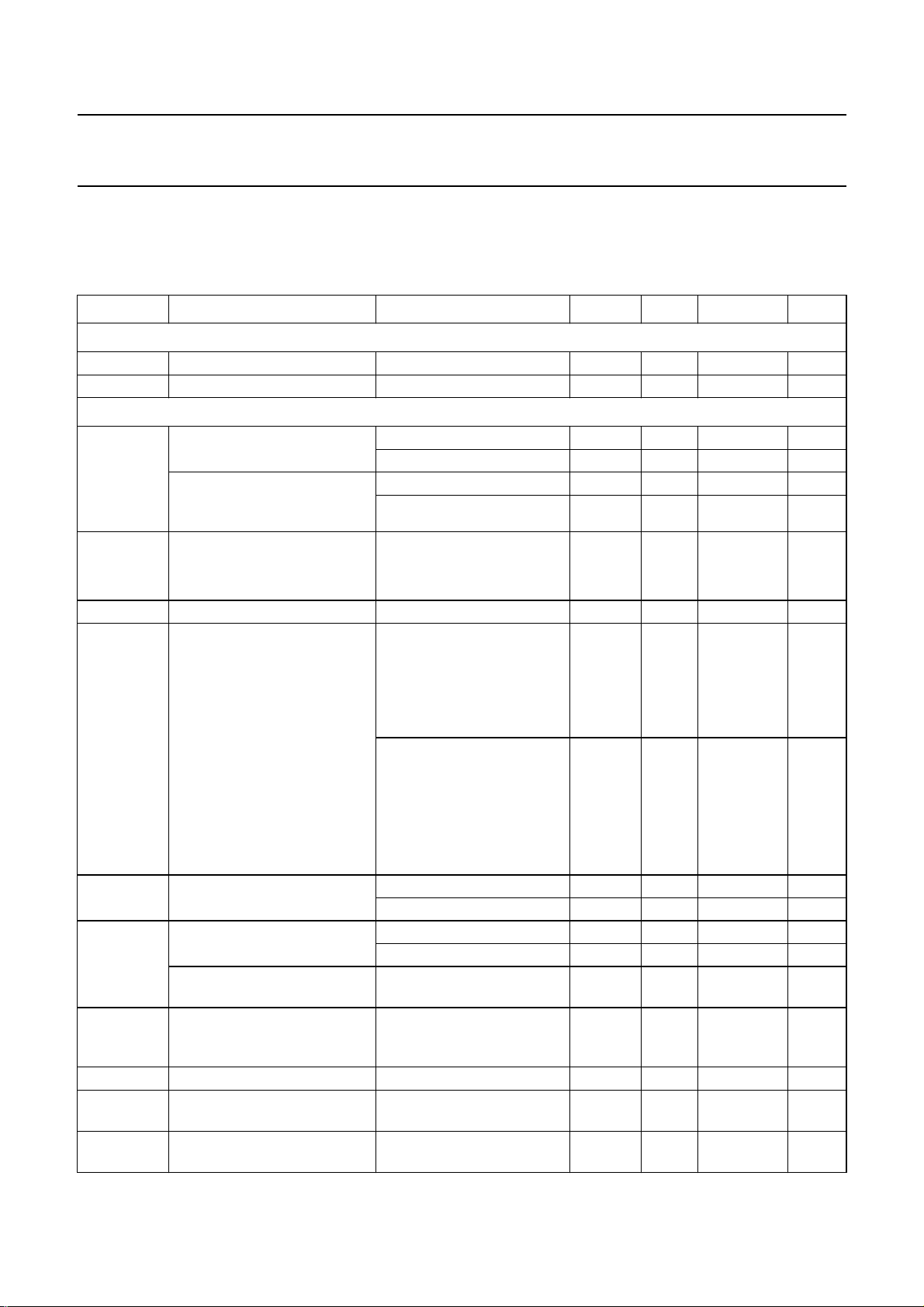

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

CC

supply voltage (pin 28) maximum chip

0 6.8 V

temperature of

125 °C; note 1

V

T

T

V

i

stg

amb

es

input voltage at:

pins 1 to 28 and 31 to 44 0 V

pins 29 to 30 −0.3 V

CC

CC

V

V

storage temperature −25 +150 °C

operating ambient temperature −20 +70 °C

electrostatic handling note 2 −150 +150 V

note 3 −2500 +2500 V

Notes

1. I

= 60 mA; T

CC

=70°C; R

amb

th(j-a)

= 70 K/W.

2. Machine model class B: C = 200 pF; L = 0.75 µH; R = 0 Ω.

3. Human body model class B: C = 100 pF; R = 1.5 kΩ.

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air 70 K/W

1999 Apr 26 9

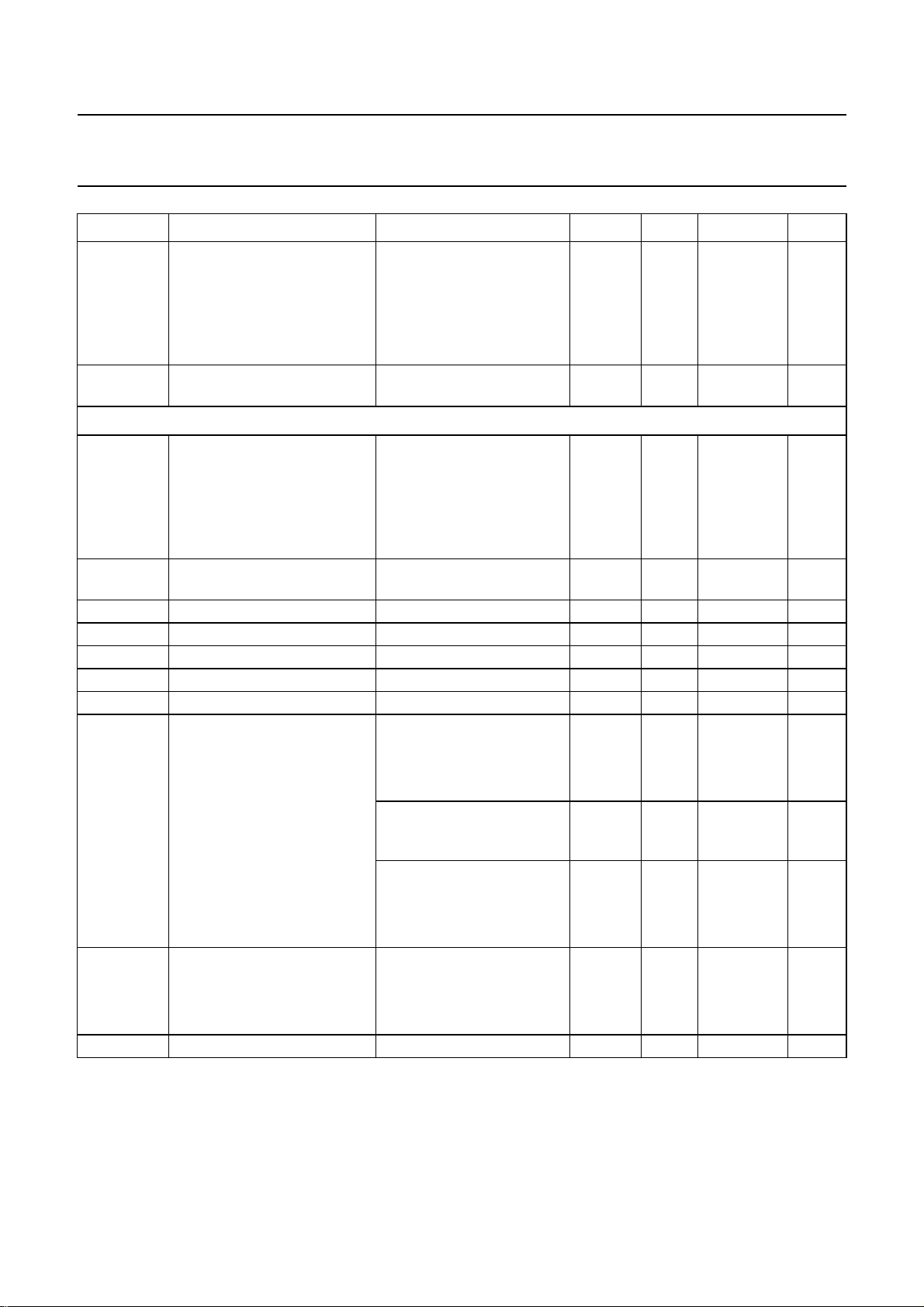

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

CHARACTERISTICS

V

=5V; T

CC

f

= 1 kHz, L = R, stereo mode); input level for first SC V

mod

of Figs 7 and 8; unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply (pin 28)

V

CC

I

CC

FM-PLL demodulator (pin 25); notes 1 to 5

V

i(FM)(rms)

V

i(vid)(p-p)

R

i

f

i(FM)

∆f

FM

∆f

AF

α

AM

K

O(FM)

K

D(FM)

V

CAF

=25°C; B/G standard (f

amb

= 5.5 MHz, f

SC1

= 5.742 MHz, SC1/SC2= 7 dB, ∆fAF= 27 kHz,

SC2

i(FM)(rms)

=50mV; f

= 4.000 MHz; measured in test circuit

ref

supply voltage 4.5 5 6.6 V

supply current 40 60 75 mA

FM-PLL input sensitivity for

pull-in (RMS value)

FM-PLL input level for gain

controlled operation

1st sound carrier −−6mV

2nd sound carrier −−1mV

1st sound carrier; note 2 6 − 150 mV

2nd sound carrier; note 2 1 − 100 mV

(RMS value)

allowable interference video

level (peak-to-peak value)

see Fig.5

V

i(FM1)(rms)

V

i(FM1)(rms)

=6mV −−160 mV

= 150 mV −−2V

input resistance 4 5 6 kΩ

FM-PLL operating

frequencies (switchable)

1st sound carrier

M standard − 4.5 − MHz

B/G standard − 5.5 − MHz

I standard − 6.0 − MHz

D/K standard − 6.5 − MHz

2nd sound carrier

M standard − 4.72 − MHz

B/G standard − 5.74 − MHz

D/K (1) standard − 6.26 − MHz

D/K (2) standard − 6.74 − MHz

D/K (3) standard − 5.74 − MHz

frequency windows of digital

acquisition help

narrow; note 3 −±225 − kHz

wide; note 3 −±450 − kHz

frequency deviation THD < 1.5%; normal gain −−±62 kHz

THD < 1.5%; reduced gain −−±124 kHz

frequency deviation for safe

identification

AM suppression AM: f

VCC= 5 V; stereo: 1 kHz L,

400 Hz R

= 1 kHz; m = 0.3

mod

−−±125 kHz

40 46 − dB

referenced to 27 kHz

FM deviation

VCO steepness ∆fFM/∆V

phase detector steepness

∆I

/∆ϕ(VFM)

LF1,2

DC voltage at CAF1 and

CAF2

LF1,2

note 5 − 3.3 − MHz/V

note 5 − 4 −µA/rad

dependent on intercarrier

frequency f

FM

1.5 − 3.3 V

1999 Apr 26 10

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

B

AF(−3dB)

V

o(FM)(rms)

Audio processing (pins 1, 2, 8 and 33)

V

o(rms)

V

o(cl)(rms)

R

L

C

L

R

L(DC)

R

o

THD total harmonic distortion V

α

cs(AF)(stereo)

α

ct(AF)(dual)

α

mute(AF)

−3 dB audio frequency

bandwidth

measured at AF1O and

AF2O; see Figs 7 and 8

upper limit dependent on

65 80 − kHz

loop filter; note 5

lower limit dependent on

−−20 Hz

CAF; CAF= 470 nF; note 4

output level (RMS value) measured at

− 250 − mV

AF1O and AF2O

AF output level (RMS value) f

mod

= 300 Hz;

54% modulation;

switchable by I2C-bus;

note 6

normal gain 400 500 600 mV

reduced gain 200 250 300 mV

AF output clipping level

VCC= 5 V; THD = 1.5% 1400 −− mV

(RMS value)

allowable load resistor AC coupled 10 −− kΩ

allowable load capacitor −−1.5 nF

allowable DC load resistor 100 −− kΩ

output resistance 70 150 300 Ω

= 0.5 V; fAF= 1 kHz − 0.2 0.5 %

o(rms)

AF channel separation (stereo

mode; complete signal path)

without alignment; note 7

B/G or M (Korea)

25 30 − dB

standard

D/K standard 23 27 − dB

potentiometer alignment;

35 40 − dB

B/G, M and D/K standard;

notes 7 and 8

I2C-bus alignment;

notes 7 and 9

B/G and D/K standard 40 45 − dB

M standard 35 40 − dB

AF crosstalk attenuation

(dual mode; complete signal

path)

A = 1 kHz; B = 400 Hz;

∆f=±50 kHz

complete signal path 65 70 − dB

stereo decoder only 70 75 − dB

mute attenuation of AF signal 75 80 − dB

1999 Apr 26 11

Philips Semiconductors Product specification

Multistandard dual carrier stereo sound decoder TDA9873H

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

S/N

W

t

DEP(B/G)

t

DEP(M)

f

ro

PSRR power supply ripple rejection

R

i(AF1)

R

i(AF2)

External additional inputs (pins 38 to 40)

V

i(nom)(rms)

V

i(cl)(rms)

G

v

R

i

f

ro

α

ct(ext)

weighted signal-to-noise ratio

(complete signal path)

CCIR 468-4 weighted;

quasi peak; dual mode;

note 6

50 µs de-emphasis;

52 56 − dB

B/G, I and D/K standard

75 µs de-emphasis;

48 52 − dB

M standard

signal-to-noise ratio at

external AF with stereo

decoder only

de-emphasis time constant for

CCIR 468-4 weighted;

70 75 − dB

quasi peak;

V

= 500 mV

o(rms)

note 10; see Fig.3 − 50 −µs

B/G, D/K and I standard

de-emphasis time constant for

note 10; see Fig.3 − 75 −µs

M standard

roll-off frequency 470 nF at AF1I and AF2I;

without de-emphasis

low frequency (−3 dB) −−20 Hz

high frequency (−0.5 dB) 20 −− kHz

f

at OUTL and OUTR (overall

performance)

= 70 Hz;

ripple

V

ripple(p-p)

= 100 mV;

dual mode; see Fig.4

20 26 − dB

AF1I input resistance 32 40 48 kΩ

AF2I input resistance 32 40 48 kΩ

nominal input signal voltage

− 0.5 − V

(RMS value)

clipping voltage level

THD ≤ 1.5%; VCC= 5 V 1.4 −− V

(RMS value)

AF signal voltage gain

G=V

o/Vi

−1 0 +1 dB

input resistance 40 50 60 kΩ

roll-off frequency low frequency (−3 dB) −−20 Hz

high frequency (−0.5 dB) 20 −− kHz

AF crosstalk attenuation

(external input)

EXTL = 1 kHz;

EXTR = 400 Hz

70 75 − dB

Mono output OUTM (pin 43)

R

o

R

L

R

L(DC)

C

L

α

mute

output resistance 70 200 350 Ω

load resistor AC coupled 10 −− kΩ

allowable DC load resistor 100 −− kΩ

load capacitor −−1.5 nF

mute attenuation 60 −− dB

1999 Apr 26 12

Loading...

Loading...