Philips TDA9870A Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TDA9870A

Digital TV Sound Processor

(DTVSP)

Product specification

Supersedes data of 1998 Aug 10

File under Integrated Circuits, IC02

1999 Dec 20

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

CONTENTS

1 FEATURES

1.1 Demodulator and decoder section

1.2 DSP section

1.3 Analog audio section

2 GENERAL DESCRIPTION

2.1 Supported standards

3 ORDERING INFORMATION

4 BLOCK DIAGRAM

5 PINNING

6 FUNCTIONAL DESCRIPTION

6.1 Demodulator and decoder section

6.2 Description of the DSP

6.3 Analog audio section

7 LIMITING VALUES

8 THERMAL CHARACTERISTICS

9 CHARACTERISTICS

10 I2C-BUS CONTROL

10.1 Introduction

10.2 Power-up state

10.3 Slave receiver mode

10.4 Slave transmitter mode

10.5 Expert mode

11 I2S-BUS DESCRIPTION

12 APPLICATION INFORMATION

13 PACKAGE OUTLINES

14 SOLDERING

14.1 Introduction

14.2 Through-hole mount packages

14.3 Surface mount packages

14.4 Suitability of IC packages for wave,reflow and

dipping soldering methods

15 DEFINITIONS

16 LIFE SUPPORT APPLICATIONS

17 PURCHASE OF PHILIPS I2C COMPONENTS

1999 Dec 20 2

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

1 FEATURES

1.1 Demodulator and decoder section

• Sound IF (SIF) input switch e.g. to select between

terrestrial TV SIF and SAT SIF sources

• SIF AGC with 24 dB control range

• SIF 8-bit Analog-to-Digital Converter (ADC)

• Two-carrier multistandard FM demodulation

(B/G, D/K and M standard)

• Decoding for three analog multi-channel systems

(A2, A2+ and A2*) and satellite sound

• Programmableidentification(B/G, D/K and M standard)

and different identification times.

1.2 DSP section

• Digital crossbar switch for all digital signal sources and

destinations

• Control of volume, balance, contour, bass, treble,

pseudo stereo, spatial, bass boost and soft mute

• Plop-free volume control

• Automatic Volume Level (AVL) control

• Adaptive de-emphasis for satellite

• Programmable beeper

• Monitor selection for FM/AM DC values and signals,

with peak detection option

• I2S-bus interface for a feature extension (e.g. Dolby

surround) with matrix, level adjust and mute.

1.3 Analog audio section

• Analog crossbar switch with inputs for mono and stereo

(also applicable as SCART 3 input), SCART 1

input/output, SCART 2 input/output and line output

• User defined full-level/−3 dB scaling for SCART outputs

• Output selection of mono, stereo, dual A/B, dual A or

dual B

• 20 kHz bandwidth for SCART-to-SCART copies

• Standby mode with functionality for SCART copies

• DualaudioDigital-to-AnalogConverter (DAC)fromDSP

to analog crossbar switch, bandwidth of 15 kHz

• Dual audio ADC from analog inputs to DSP

• Two dual audio DACs for loudspeaker (Main) and

headphone (Auxiliary) outputs; also applicable for

L, R, C and S in the Dolby Pro Logic mode with feature

extension.

2 GENERAL DESCRIPTION

The TDA9870A is a single-chip Digital TV Sound

Processor (DTVSP) for analog multi-channel sound

systems in TV sets and satellite receivers.

2.1 Supported standards

The multistandard/multi-stereo capability of the

TDA9870A is mainly of interest in Europe, but also in

Hong Kong/Peoples Republic of China and South East

Asia.This includesB/G, D/K, I, M and Lstandard.Inother

application areas there exists only subsets of those

standard combinations otherwise only single standards

are transmitted.

M standard is transmitted in Europe by the American

Forces Network (AFN) with European channel spacing

(7 MHz VHF, 8 MHz UHF) and monaural sound.

Korea has a stereo sound system similar to Europe and is

supported by the TDA9870A. Differences include

deviation, modulation contents and identification. It is

based on M standard.

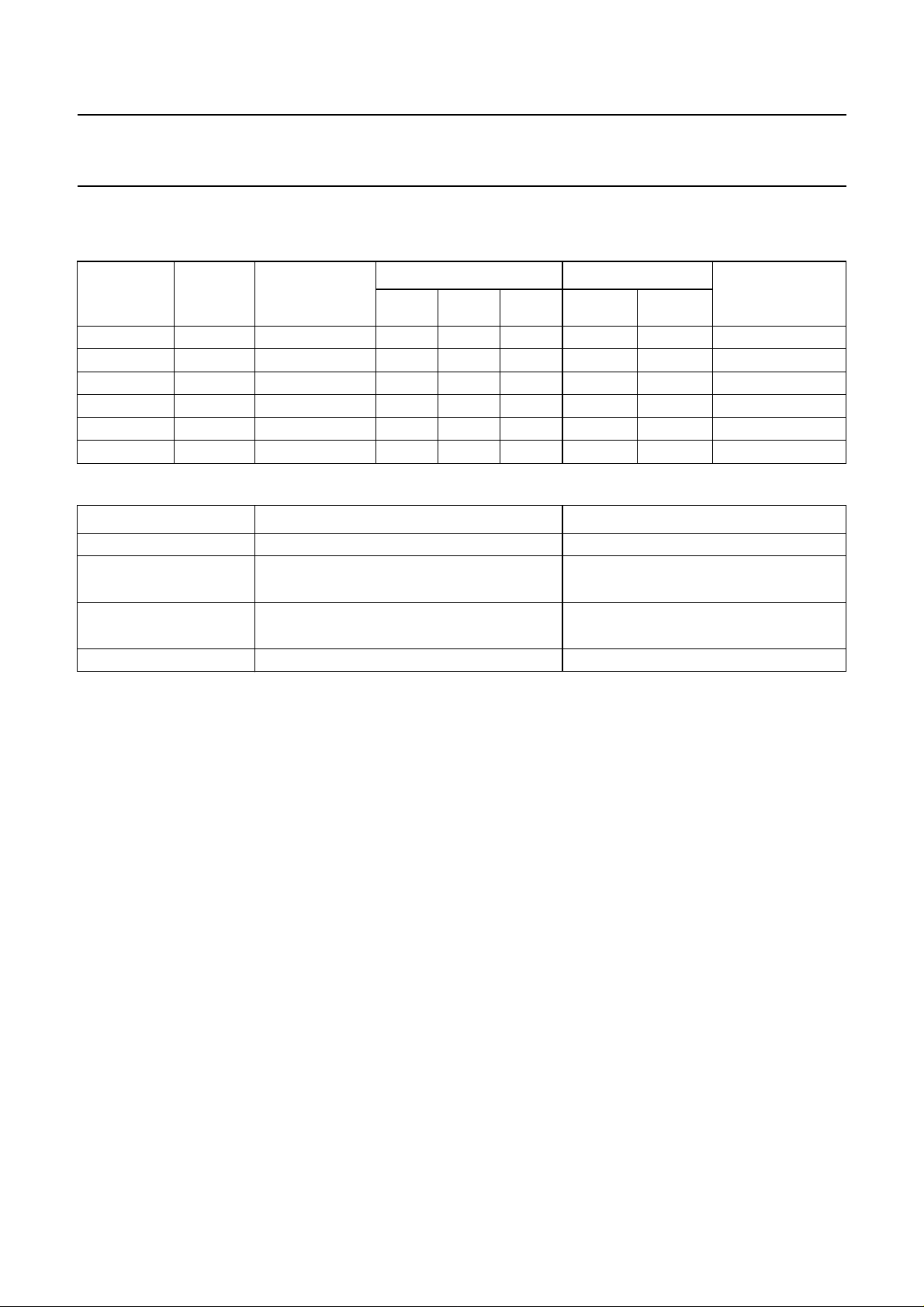

An overview of the supported standards and sound

systems and their key parameters is given in Table 1.

The analog multi-channel sound systems (A2, A2+

and A2*) are 2-Carrier Systems (2CS).

1999 Dec 20 3

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

2.1.1 ANALOG 2-CARRIER SYSTEMS

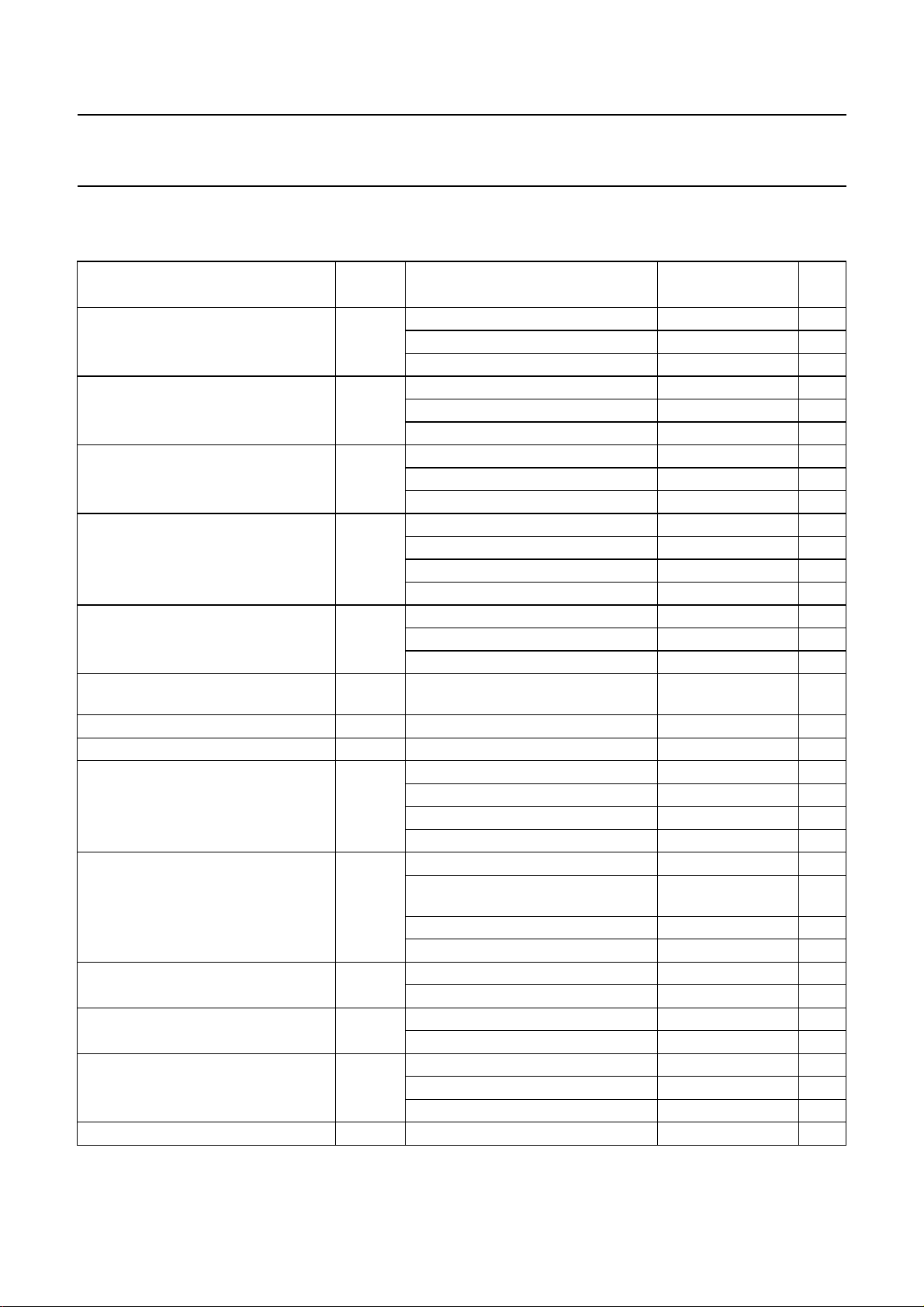

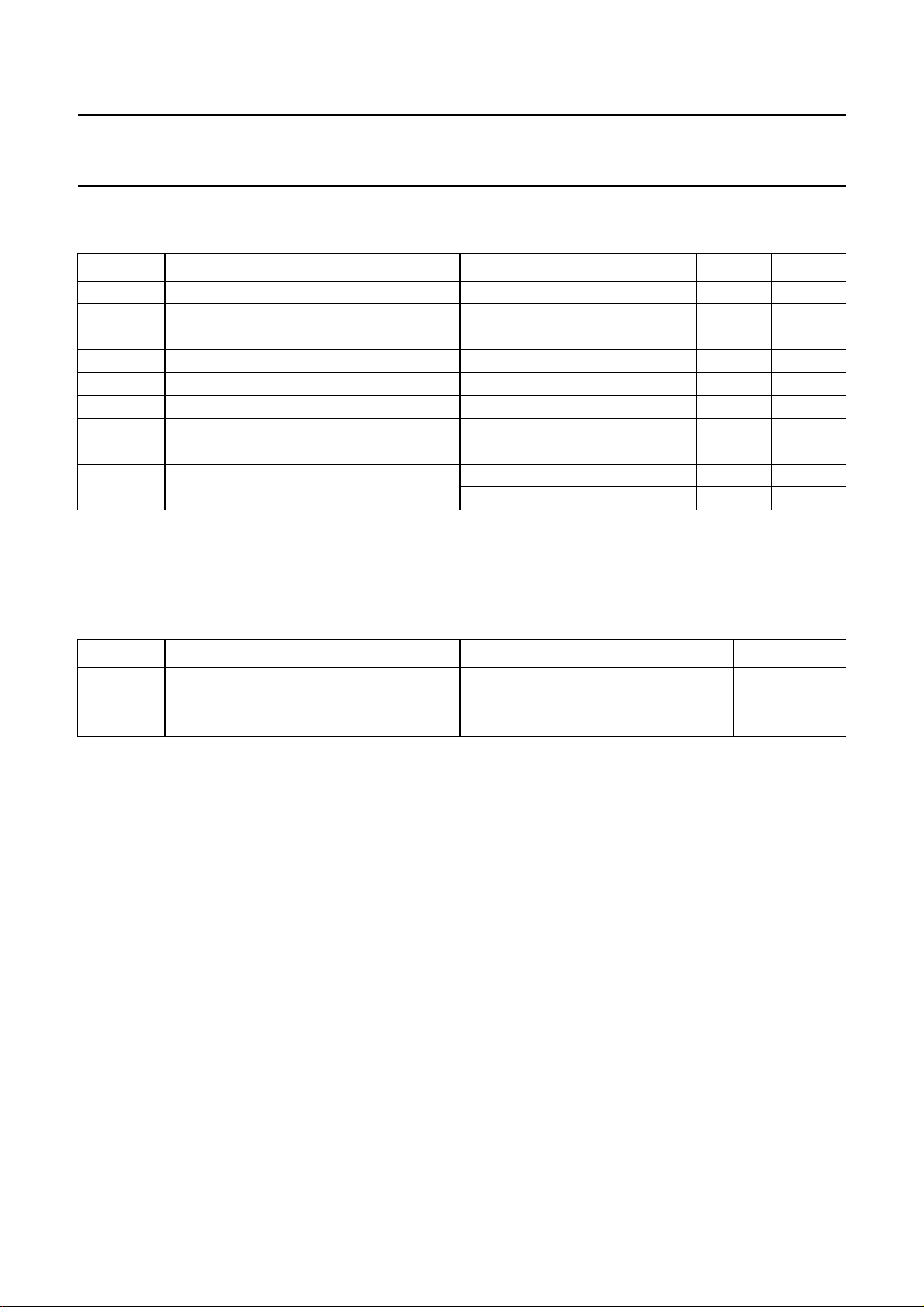

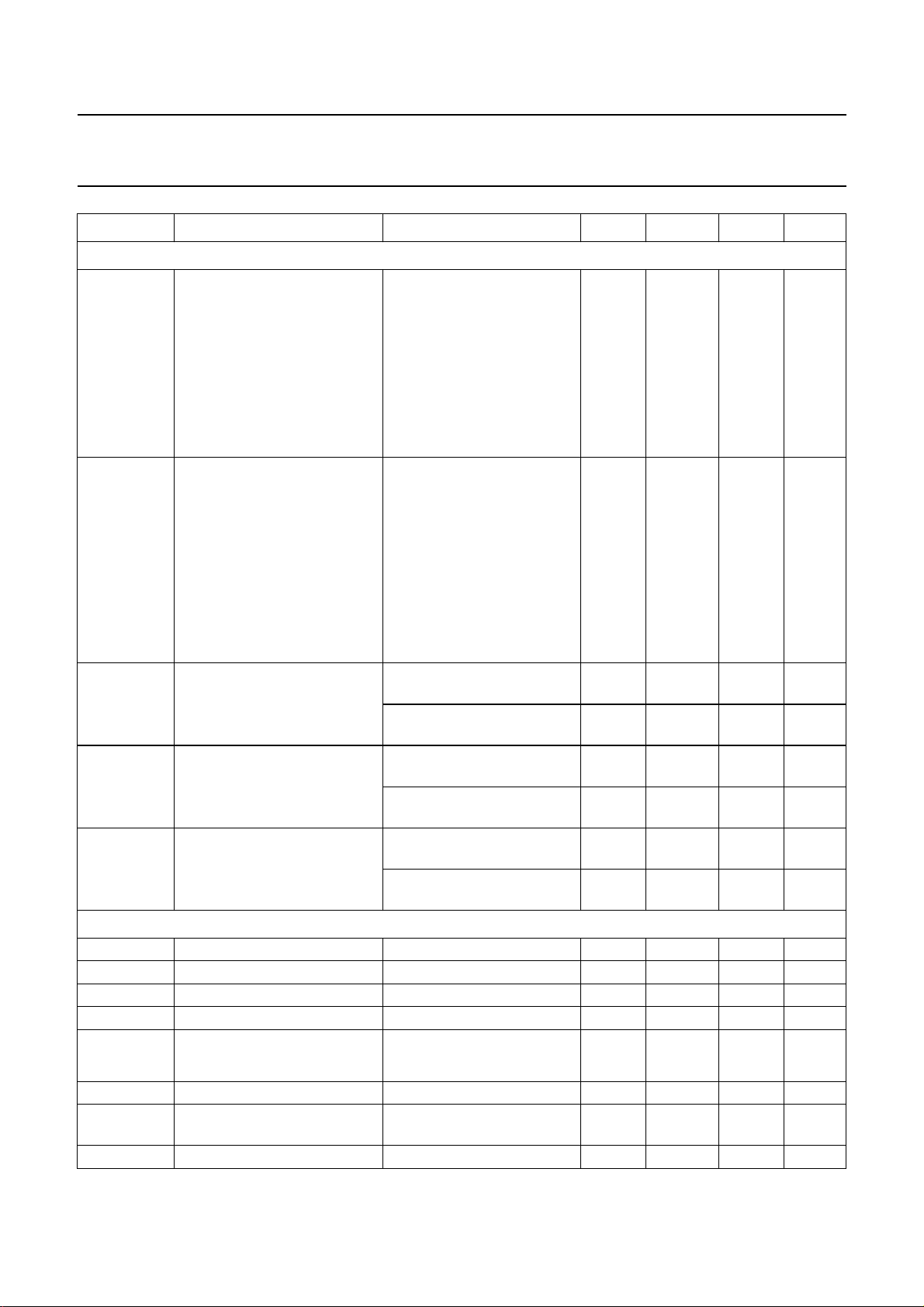

Table 1 Frequency modulation

STANDARD

SOUND

SYSTEM

CARRIER

FREQUENCY

(MHz)

FM DEVIATION (kHz) MODULATION BANDWIDTH/

DE-EMPHASIS

NOM. MAX. OVER SC1 SC2

(kHz/µs)

M mono 4.5 15 25 50 mono − 15/75

M A2+ 4.5/4.724 15 25 50

B/G A2 5.5/5.742 27 50 80

1

⁄2(L+R)1⁄2(L − R) 15/75 (Korea)

1

⁄2(L + R) R 15/50

I mono 6.0 27 50 80 mono − 15/50

D/K A2 6.5/6.742 27 50 80

D/K A2* 6.5/6.258 27 50 80

1

⁄2(L + R) R 15/50

1

⁄2(L + R) R 15/50

Table 2 Identification for A2 systems

PARAMETER A2/A2* A2+ (KOREA)

Pilot frequency 54.6875 kHz = 3.5 × line frequency 55.0699 kHz = 3.5 × line frequency

Stereo identification

frequency

Dual identification

frequency

117.5 Hz

274.1 Hz

line frequency

= 149.9 Hz

------------------------------------133

line frequency

= 276.0 Hz

-------------------------------------

57

line frequency

=

------------------------------------105

line frequency

=

------------------------------------57

AM modulation depth 50% 50%

1999 Dec 20 4

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

2.1.2 SATELLITE SYSTEMS

An important specification for satellite TV reception is the

“Astra specification”

. The TDA9870A is suited for the reception

of Astra and other satellite signals.

Table 3 FM satellite sound

CARRIER

CARRIER TYPE

FREQUENCY

(MHz)

Main 6.50

(1)

MODULATION

INDEX

0.26 85 mono 15/50

Sub 7.02/7.20 0.15 50 m/st/d

MAXIMUM

FM DEVIATION

(kHz)

MODULATION

(3)

BANDWIDTH/

DE-EMPHASIS

(kHz/µs)

(2)

15/adaptive

Sub 7.38/7.56

Sub 7.74/7.92

Sub 8.10/8.28

Notes

1. For other satellite systems, frequencies of, for example, 5.80, 6.60 or 6.65 MHz can also be received.

2. A de-emphasis of 60 µs, or in accordance with J17, is available.

3. m/st/d = mono, stereo or dual language sound.

4. Adaptive de-emphasis is compatible to transmitter specification.

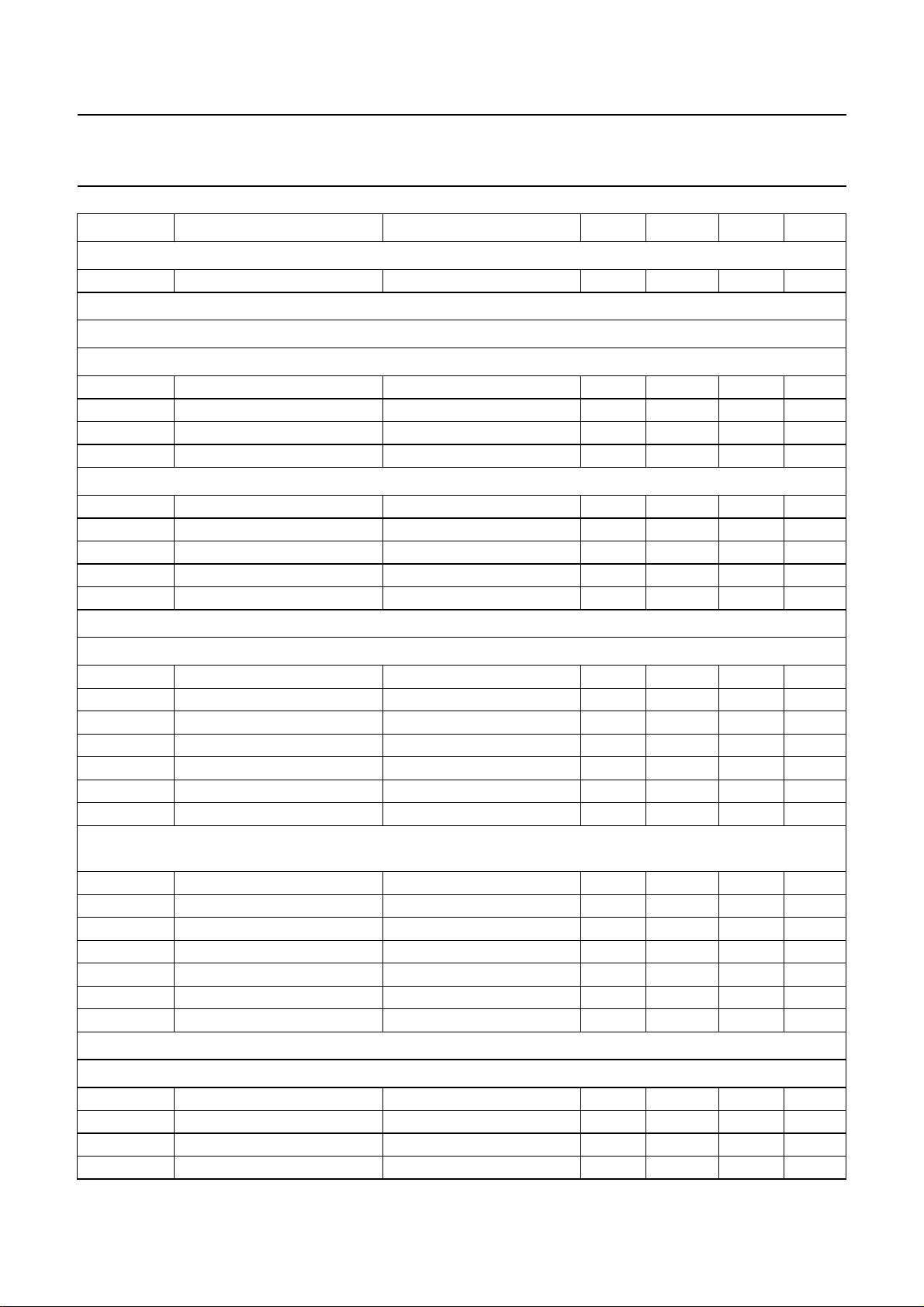

3 ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

TDA9870A SDIP64 plastic shrink dual in-line package; 64 leads (750 mil) SOT274-1

TDA9870AH QFP64 plastic quad flat package; 64 leads (lead length 1.6 mm);

SOT393-1

body 14 × 14 × 2.7 mm

(4)

1999 Dec 20 5

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

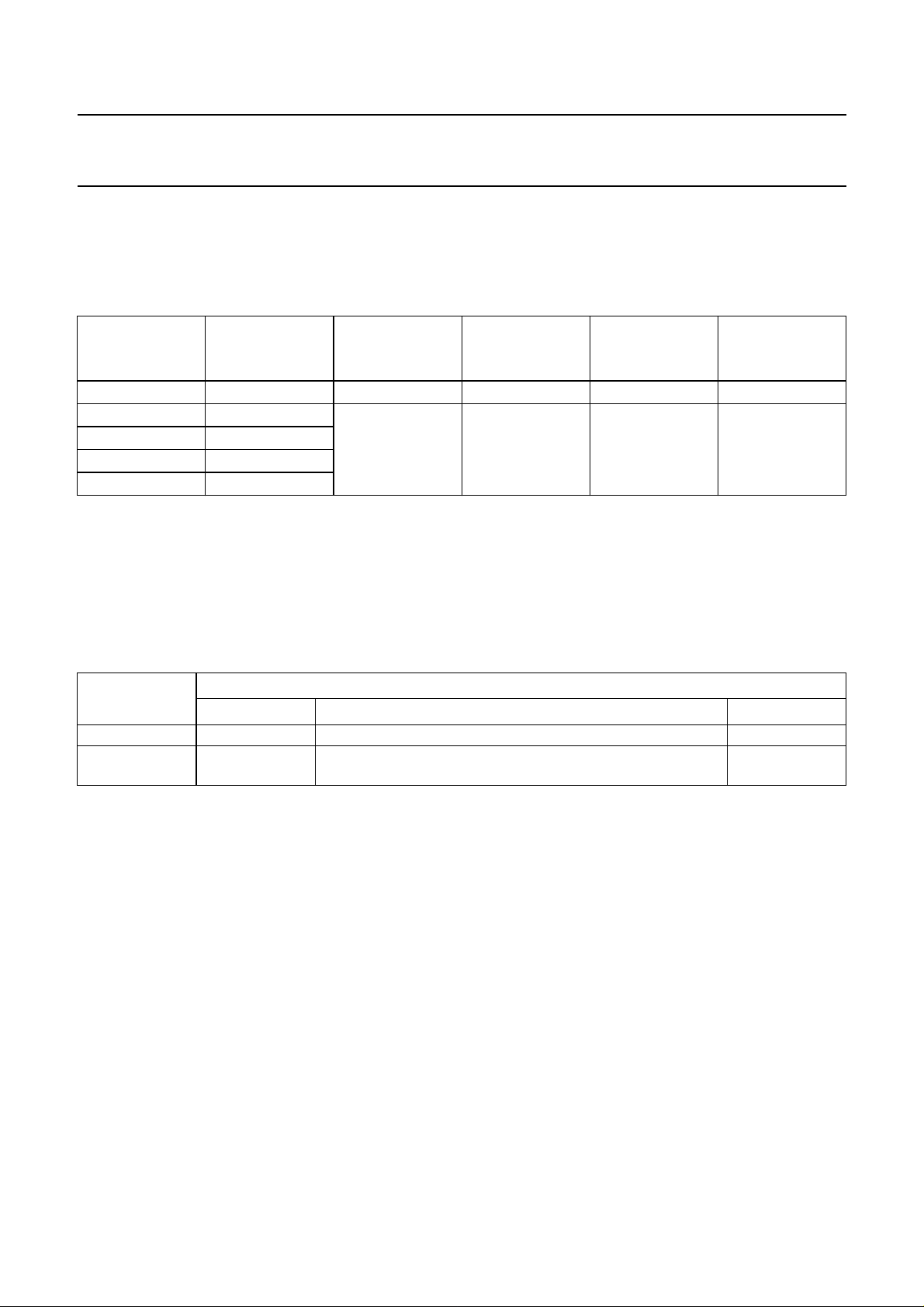

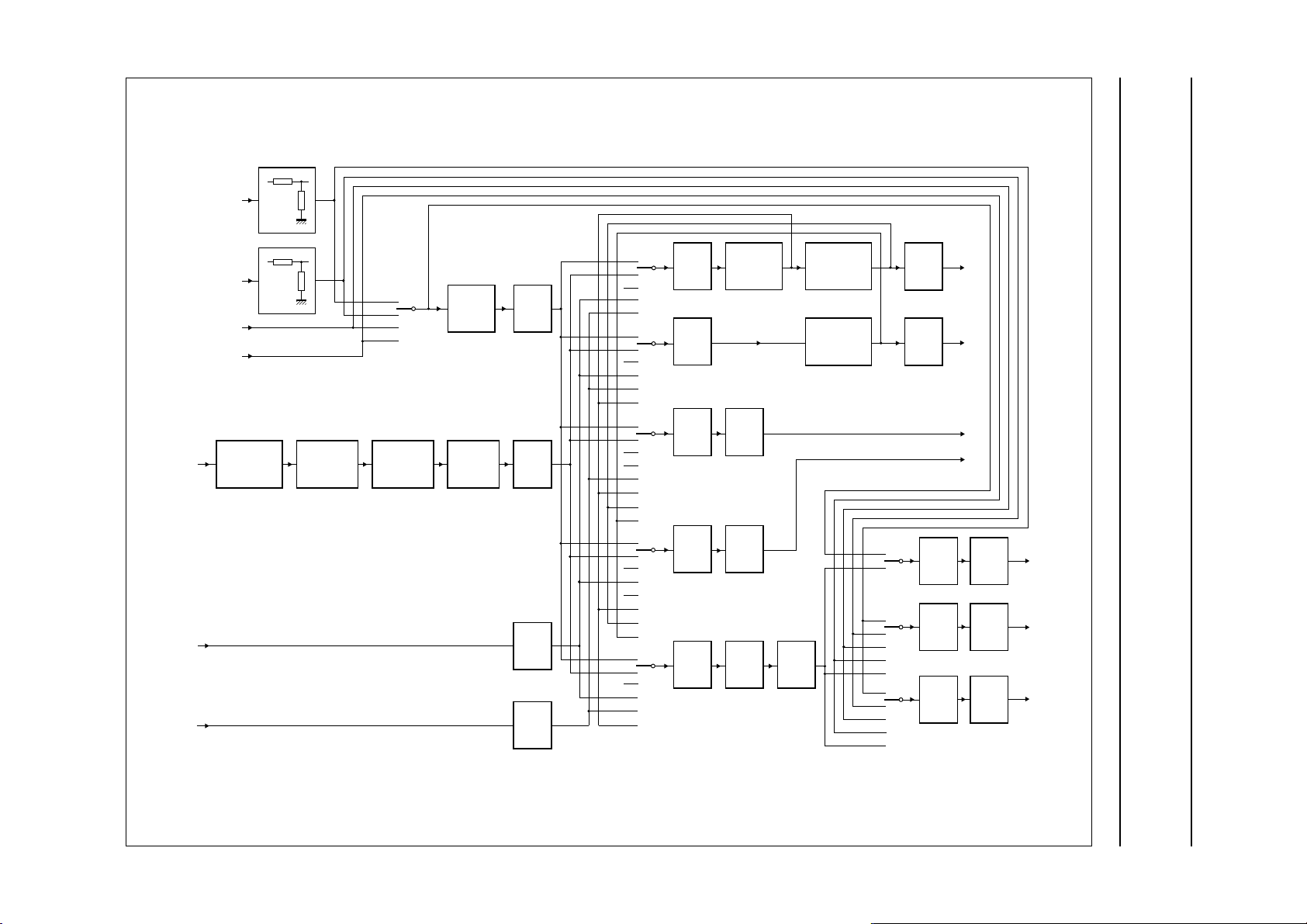

4 BLOCK DIAGRAM

handbook, full pagewidth

9 (1)

P1

20 (12)

P2

SCL

SDA

SDI1

SDI2

SCK

WS

3 (59)

13 (5)

4 (60)

5 (61)

18 (10)

19 (11)

21 (13)

27 (19)

26 (18)

25 (17)

24 (16)

22 (14)

23 (15)

15 (7)

64 (56)

14 (6)

49 (41)

35 (27)

17 (9)

16 (8)

28 (20)

30 (22)

I2C-BUS

INTERFACE

IDENTIFICATION

CLOCK

PEAK

DETECTION

I2S-BUS

INTERFACE

DIGITAL

SUPPLY

TEST

MOL

ADDR1

ADDR2

XTALI

XTALO

SYSCLK

SDO1

SDO2

V

DDD1

V

DDD2

V

SSD1

V

SSD2

V

SSD3

V

SSD4

CRESET

TEST1

TEST2

The pin numbers given in parenthesis refer to the TDA9870AH version.

SIF2 SIF1

10 (2) 12 (4)

INPUT SWITCH

AGC, ADC

FM (AM)

DEMODULATION

A2/SATELLITE

DECODER

LEVEL

ADJUST

DIGITAL

SELECT

AUDIO PROCESSING

DAC (2)

(52)

(53)

60

61

MOR

AUXOL

ADC (2)

DAC (2)

DAC (2)

(50)

58

(49)

57

AUXOR

SUPPLY

SOUND IF

(SIF)

TDA9870A

(

TDA9870AH

ANALOG

CROSSBAR

SWITCH

SUPPLY

SCART,

DAC,

ADC

(63) 7

V

V

V

I

ref

DEC1

SSA1

ref1

(62) 6

(3) 11

(64) 8

)

(25) 33

(26) 34

(28) 36

(29) 37

(23) 31

(24) 32

(21) 29

(39) 47

(40) 48

(43) 51

(44) 52

(55) 63

(54) 62

(33) 41

(34) 42

(36) 44

(37) 45

(46) 54

(47) 55

(51) 59

(30) 38

(31) 39

(32) 40

(38) 46

(45) 53

(35) 43

(48) 56

(42) 50

MHB593

(57) 1

(58) 2

SCIR1

SCIL1

SCIR2

SCIL2

EXTIR

EXTIL

MONOIN

SCOR1

SCOL1

SCOR2

SCOL2

LOR

LOL

i.c.

i.c.

i.c.

i.c.

i.c.

i.c.

PCAPR

PCAPL

V

DDA

V

DEC2

V

ref(p)

V

ref(n)

V

ref2

V

ref3

V

SSA2

V

SSA3

V

SSA4

Fig.1 Block diagram.

1999 Dec 20 6

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

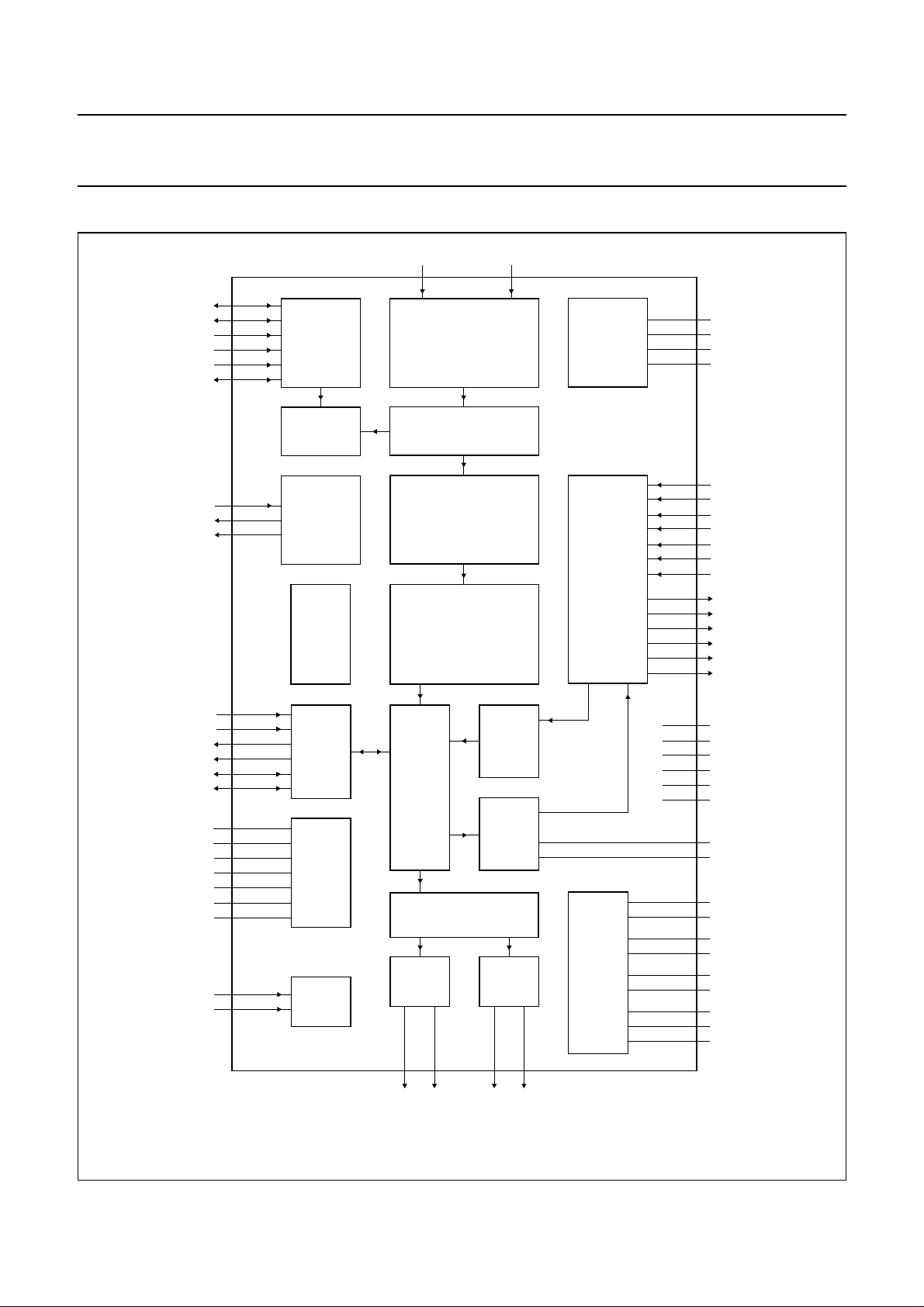

5 PINNING

SYMBOL

PIN

TDA9870A TDA9870AH

PIN

TYPE

(1)

DESCRIPTION

i.c. 1 57 − internally connected; note 2

i.c. 2 58 − internally connected; note 2

ADDR1 3 59 I I

SCL 4 60 I I

SDA 5 61 I/O I

V

V

I

ref

SSA1

DEC1

6 62 S supply ground 1; analog front-end circuitry

763−supply voltage decoupling 1; analog front-end circuitry

864−resistor for reference current generator; analog front-end circuitry

2

C-bus slave address input 1

2

C-bus clock input

2

C-bus data input/output

P1 9 1 I/O general purpose input/output pin 1

SIF2 10 2 I sound IF input 2

V

ref1

11 3 − reference voltage 1; analog front-end circuitry

SIF1 12 4 I sound IF input 1

ADDR2 13 5 I I

V

V

SSD1

DDD1

14 6 S supply ground 1; digital circuitry

15 7 S digital supply voltage 1; digital circuitry

2

C-bus slave address input 2

CRESET 16 8 − capacitor for Power-on reset

V

SSD4

17 9 S supply ground 4; digital circuitry

XTALI 18 10 I crystal oscillator input

XTALO 19 11 O crystal oscillator output

P2 20 12 I/O general purpose input/output pin 2

SYSCLK 21 13 O system clock output

SCK 22 14 I/O I

WS 23 15 I/O I

SDO2 24 16 O I

SDO1 25 17 O I

SDI2 26 18 I I

SDI1 27 19 I I

TEST1 28 20 I test pin 1; connected to V

2

S-bus clock input/output

2

S-bus word select input/output

2

S-bus data output 2 (I2S2 output)

2

S-bus data output 1 (I2S1 output)

2

S-bus data input 2 (I2S2 input)

2

S-bus data input 1 (I2S1 input)

for normal operation

SSD1

MONOIN 29 21 I audio mono input

TEST2 30 22 I test pin 2; connected to V

for normal operation

SSD1

EXTIR 31 23 I external audio input right channel

EXTIL 32 24 I external audio input left channel

SCIR1 33 25 I SCART 1 input right channel

SCIL1 34 26 I SCART 1 input left channel

V

SSD3

35 27 S supply ground 3; digital circuitry

SCIR2 36 28 I SCART 2 input right channel

SCIL2 37 29 I SCART 2 input left channel

V

DEC2

38 30 − supply voltage decoupling 2; audio analog-to-digital converter

circuitry

1999 Dec 20 7

Philips Semiconductors Product specification

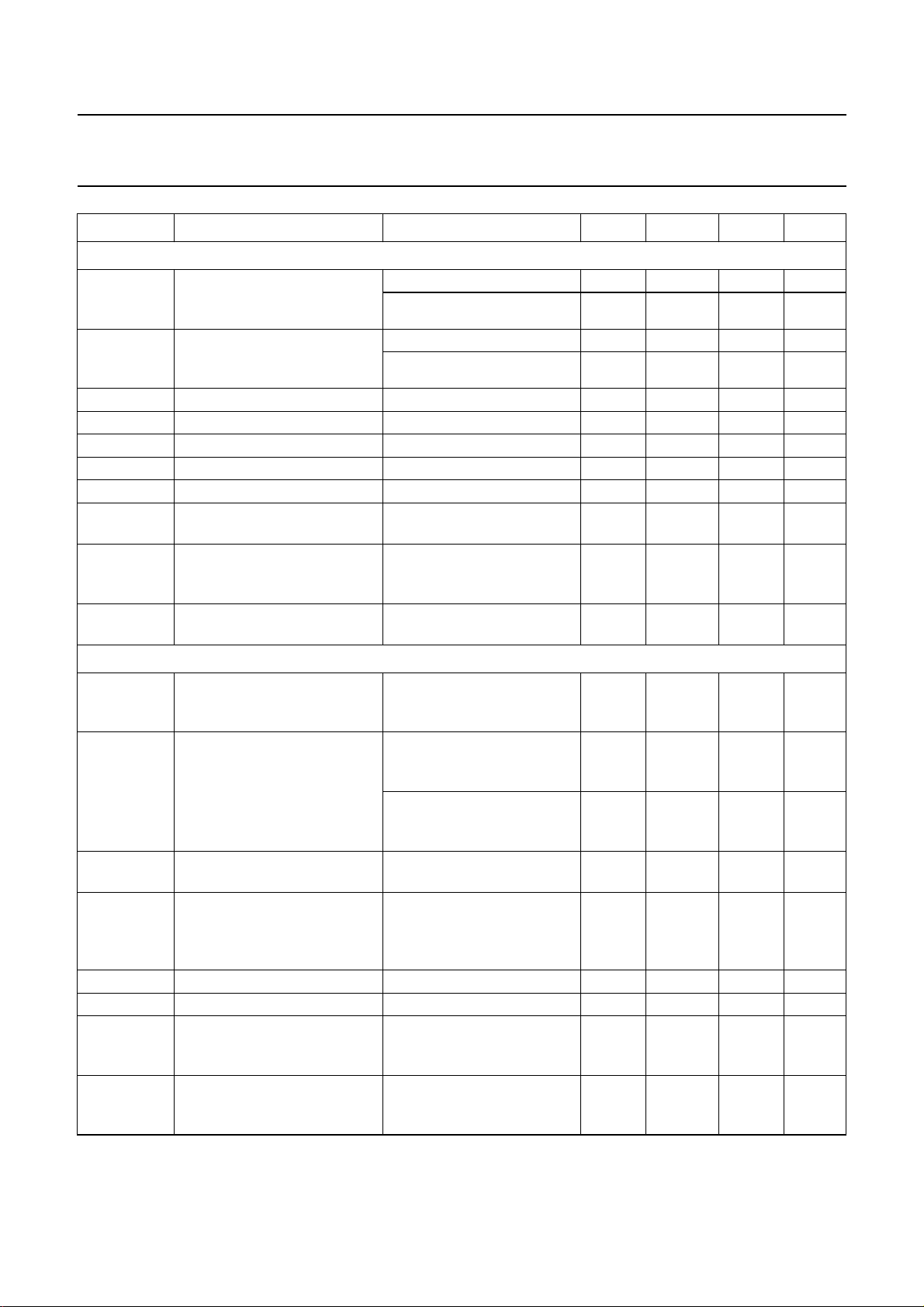

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL

V

ref(p)

PIN

TDA9870A TDA9870AH

39 31 − positive reference voltage; audio analog-to-digital converter

PIN

TYPE

(1)

DESCRIPTION

circuitry

V

ref(n)

40 32 − reference voltage ground; audio analog-to-digital converter

circuitry

i.c. 41 33 − internally connected; note 3

i.c. 42 34 − internally connected; note 4

V

SSA2

43 35 S supply ground 2; audio analog-to-digital converter circuitry

i.c. 44 36 − internally connected; note 4

i.c. 45 37 − internally connected; note 3

V

ref2

46 38 − reference voltage 2; audio analog-to-digital converter circuitry

SCOR1 47 39 O SCART 1 right channel output

SCOL1 48 40 O SCART 1 left channel output

V

V

SSD2

SSA4

49 41 S supply ground 2; digital circuitry

50 42 S supply ground 4; audio operational amplifier circuitry

SCOR2 51 43 O SCART 2 right channel output

SCOL2 52 44 O SCART 2 left channel output

V

ref3

53 45 − reference voltage 3; audio digital-to-analog converter and

operational amplifier circuitry

PCAPR 54 46 − post-filter capacitor pin right channel, audio digital-to-analog

converter

PCAPL 55 47 − post-filter capacitor pin left channel, audio digital-to-analog

converter

V

SSA3

56 48 S supply ground 3; audio digital-to-analog converter circuitry

AUXOR 57 49 O headphone (Auxiliary) right channel output

AUXOL 58 50 O headphone (Auxiliary) left channel output

V

DDA

59 51 S analog power supply voltage; analog circuitry

MOR 60 52 O loudspeaker (Main) right channel output

MOL 61 53 O loudspeaker (Main) left channel output

LOL 62 54 O line output left channel

LOR 63 55 O line output right channel

V

DDD2

64 56 S digital supply voltage 2; digital circuitry

Notes

1. Pin type: I = Input; O = Output; S = Supply.

2. Test pin: CMOS 3-state stage, pull-up resistor, can be connected to VSS.

3. Test pin: CMOS level input, pull-up resistor, can be connected to VSS.

4. Test pin: CMOS 3-state stage, can be connected to VSS.

1999 Dec 20 8

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

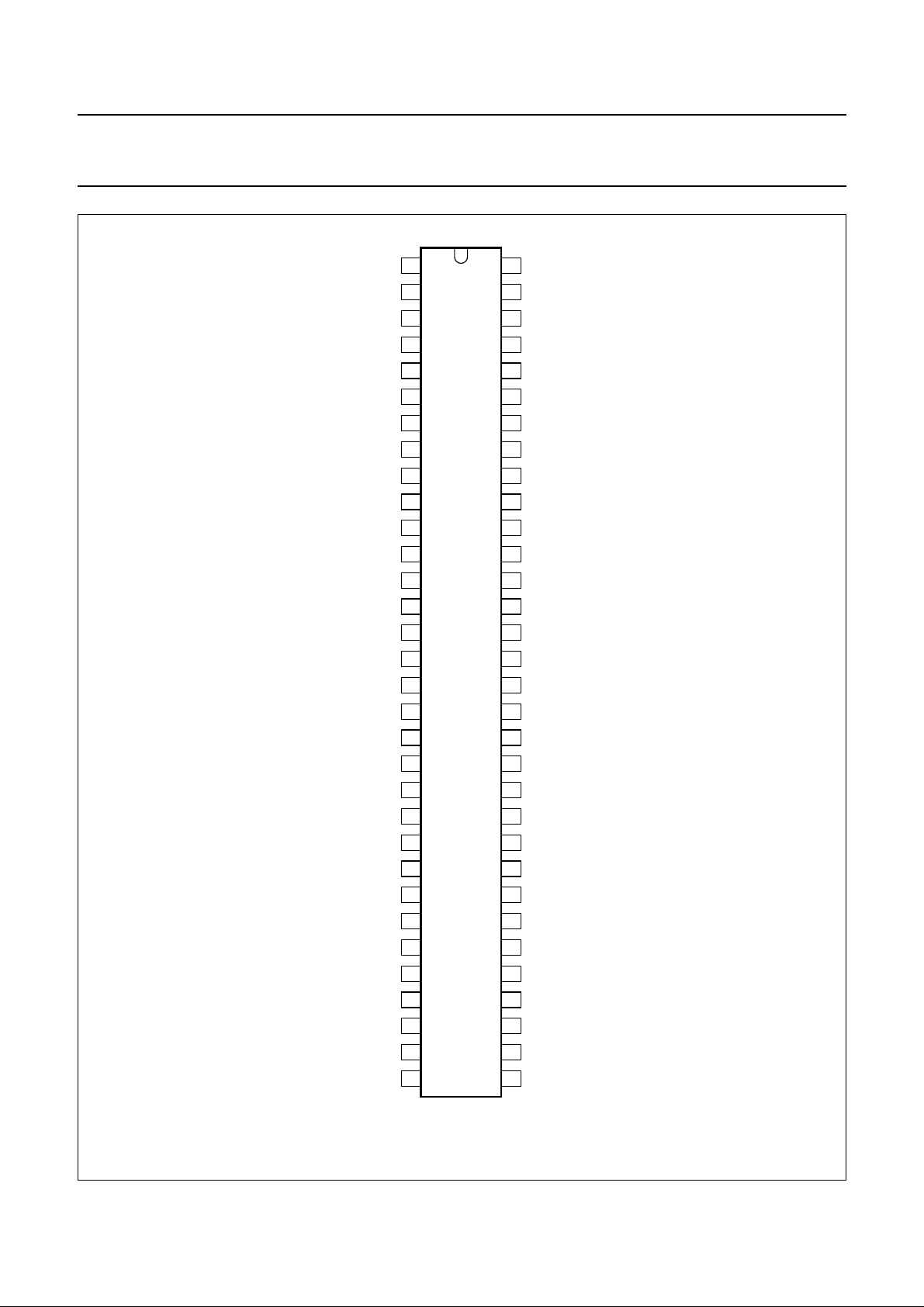

handbook, halfpage

i.c.

i.c.

ADDR1

SCL

SDA

V

SSA1

V

DEC1

I

ref

P1

SIF2

V

ref1

SIF1

ADDR2

V

SSD1

V

DDD1

CRESET

V

SSD4

XTALI

XTALO

P2

SYSCLK

SCK

WS

SDO2

SDO1

SDI2

SDI1

TEST1

MONOIN

TEST2

EXTIR

EXTIL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TDA9870A

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

MHB111

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

V

DDD2

LOR

LOL

MOL

MOR

V

DDA

AUXOL

AUXOR

V

SSA3

PCAPL

PCAPR

V

ref3

SCOL2

SCOR2

V

SSA4

V

SSD2

SCOL1

SCOR1

V

ref2

i.c.

i.c.

V

SSA2

i.c.

i.c.

V

ref(n)

V

ref(p)

V

DEC2

SCIL2

SCIR2

V

SSD3

SCIL1

SCIR1

Fig.2 Pin configuration (TDA9870A).

1999 Dec 20 9

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

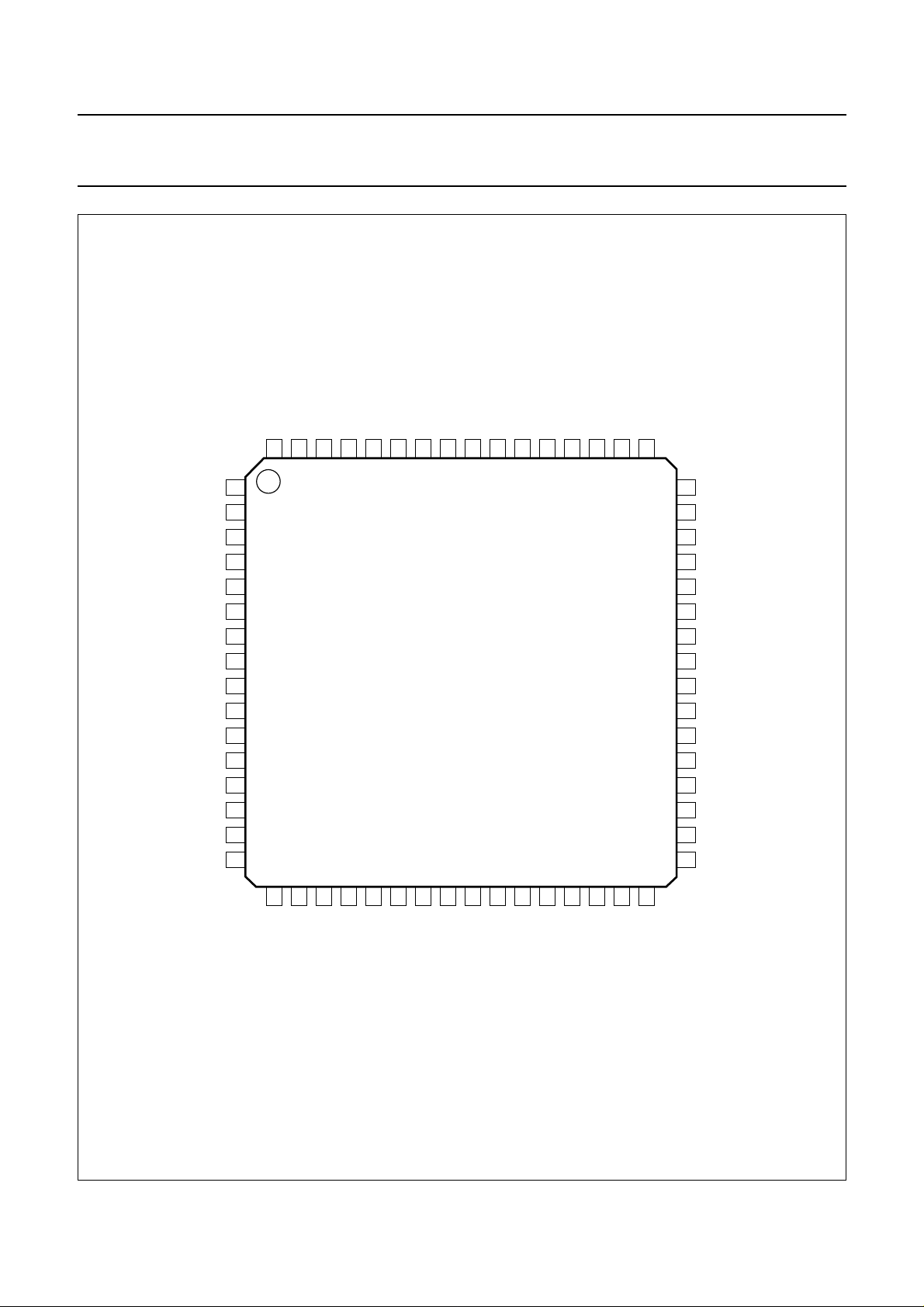

handbook, full pagewidth

ref

I

64

DEC1VSSA1

V

63

62

SDA

61

SCL

60

ADDR1

i.c.

59

58

i.c.

57

DDD2

V

56

LOR

55

LOL

54

MOL

53

MOR

52

DDA

V

51

AUXOL

AUXOR

50

49

P1

1

SIF2

2

V

3

ref1

SIF1

4

ADDR2

V

V

CRESET

V

XTALO

SYSCLK

5

6

SSD1

7

DDD1

8

9

SSD4

XTALI

10

11

P2

12

13

SCK

14

WS

15

SDO2 33

16

17

SDO1

18

SDI2

19

SDI1

20

TEST1

21

22

TEST2

MONOIN

TDA9870AH

23

24

25

EXTIL

EXTIR

SCIR1

26

SCIL1

27

SSD3

V

28

SCIR2

29

SCIL2

30

DEC2

V

31

ref(p)Vref(n)

V

V

48

SSA3

PCAPL

47

PCAPR

46

V

45

ref3

SCOL2

44

SCOR2

43

V

42

SSA4

V

41

SSD2

SCOL1

40

SCOR1

39

V

38

ref2

i.c.

37

i.c.

36

V

35

SSA2

i.c.

34

i.c.

32

MHB594

Fig.3 Pin configuration (TDA9870AH).

1999 Dec 20 10

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

6 FUNCTIONAL DESCRIPTION

6.1 Demodulator and decoder section

6.1.1 SIF INPUT

Two input pins are provided: SIF1 e.g. for terrestrial TV

and SIF2 e.g. for a satellite tuner. For higher SIF signal

levels the SIF input can be attenuated with an internally

switchable−10 dB resistor divider. As nospecificfiltersare

integrated, both inputs have the same specification giving

flexibility in application. The selected signal is passed

through an AGC circuit and then digitized by an 8-bit ADC

operating at 24.576 MHz.

6.1.2 AGC

The gain of the AGC amplifier is controlled from the ADC

output by means of a digital control loop employing

hysteresis. The AGC has a fast attack behaviour to

prevent ADC overloads and a slow decay behaviour to

prevent AGC oscillations. For AM demodulation the AGC

must be switched off. When switched off, the control loop

is reset and fixed gain settings can be chosen

(see Table 14; subaddress 0).

The AGC can be controlled via the I2C-bus. Details can be

found in the I2C-bus register definitions (see Chapter 10).

6.1.3 MIXER

The digitized input signal is fed to the mixers, which mix

one or both input sound carriers down to zero IF. A 24-bit

control word for each carrier sets the required frequency.

Access to the mixer control word registers is via the

I2C-bus.

6.1.5 FM IDENTIFICATION

The identification of the FM sound mode is performed by

AM synchronous demodulation of the pilot signal and

narrow-band detection of the identification frequencies.

Theresultisavailableviathe I2C-businterface.Aselection

can be made via the I2C-bus for B/G, D/K and M standard

and for three different modes that represent different

trade-offs between speed and reliability of identification.

6.1.6 CRYSTAL OSCILLATOR

The circuitry of the crystal oscillator is fully integrated, only

the external 24.576 MHz crystal is needed (see Fig.10).

6.1.7 TEST PINS

Test pins TEST1 and TEST2 are active HIGH and in

normal operating mode of the device they are connected

to V

and are not available to customers. Without external

circuitry these pins are pulled down to LOW level with

internal resistors.

6.1.8 POWER FAIL DETECTOR

The power fail detector monitors the internal power supply

for the digital part of the device. If the supply has

temporarily been lower than the specified lower limit, the

Power-onreset bit POR (see Section 10.4.1), will be set to

logic 1. Bit CLRPOR (see Section 10.3.2) resets the

Power-on reset flip-flop to LOW. If this is detected, an

initialization of the TDA9870A has to be carried out to

ensure reliable operation.

. Test functions are for manufacturing tests only

SSD1

6.1.4 FM AND AM DEMODULATION

An FM or AM input signal is fed via a band-limiting filter to

a demodulator that can be used for either FM or AM

demodulation. Apart from the standard (fixed)

de-emphasis characteristic, an adaptive de-emphasis is

availableforencodedsatelliteprograms.Astereodecoder

recovers the left and right signal channels from the

demodulated sound carriers. Both the European and

Korean stereo systems are supported.

1999 Dec 20 11

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

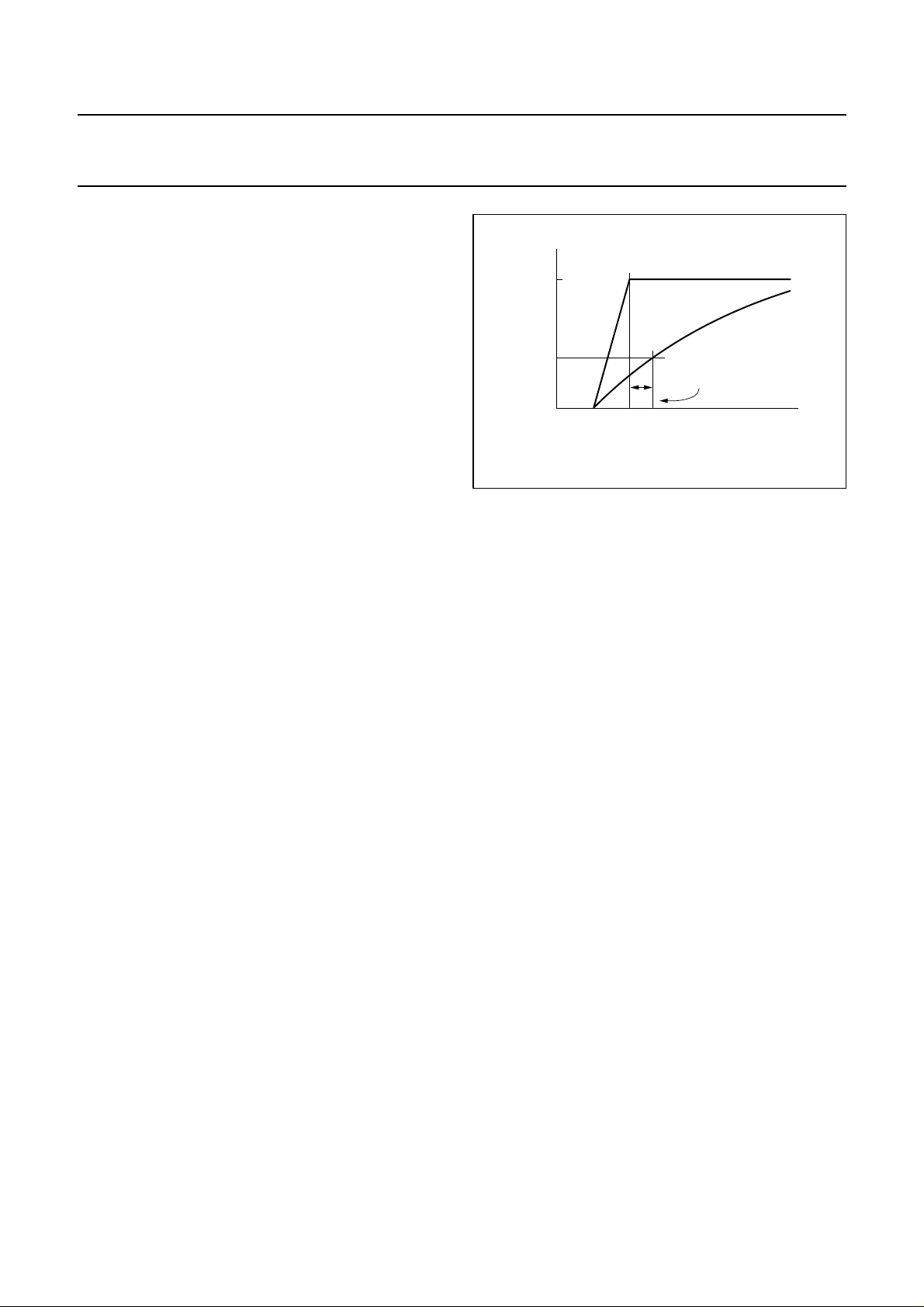

6.1.9 POWER-ON RESET

The reset is active LOW. In order to perform a reset at

power-up, a simple RC circuit may be used which consists

of the integrated passive pull-up resistor and an external

capacitor connected to ground. The pull-up resistor has a

nominal value of 50 kΩ, which can easily be measured

between pins CRESET and V

. Before the supply

DDD2

voltage has reached a certain minimum, the state of the

circuit is completely undefined, and it remains in this

undefined state unless a reset is applied.

The reset is guaranteed to be active when:

• The power supply is within the specified limits

(4.75 and 5.5 V)

• The crystal oscillator is functioning

• The voltage at pin CRESET is below 0.3V

V

= 5.0 V, typically below 1.8 V).

DDD

DDD

(1.5 V if

The required capacitor value depends on the gradient of

the rising power supply voltage. The time constant of the

RC circuit should be clearly larger than the rise time of the

power supply, to make sure that the reset condition is

always satisfied (see Fig.4), even considering the

tolerance spread. To avoid problems with a too slow

discharging of the capacitor at power-down, it may be

helpful to add a diode from pin CRESET to V

. It should

DDD

be noted that the internal ESD protection diode does not

help here as it only conducts at higher voltages. Under

difficult power supply conditions (e.g. very slow or

non-monotonic ramp-up), it is recommended to drive the

reset line from a microcontroller port or the like.

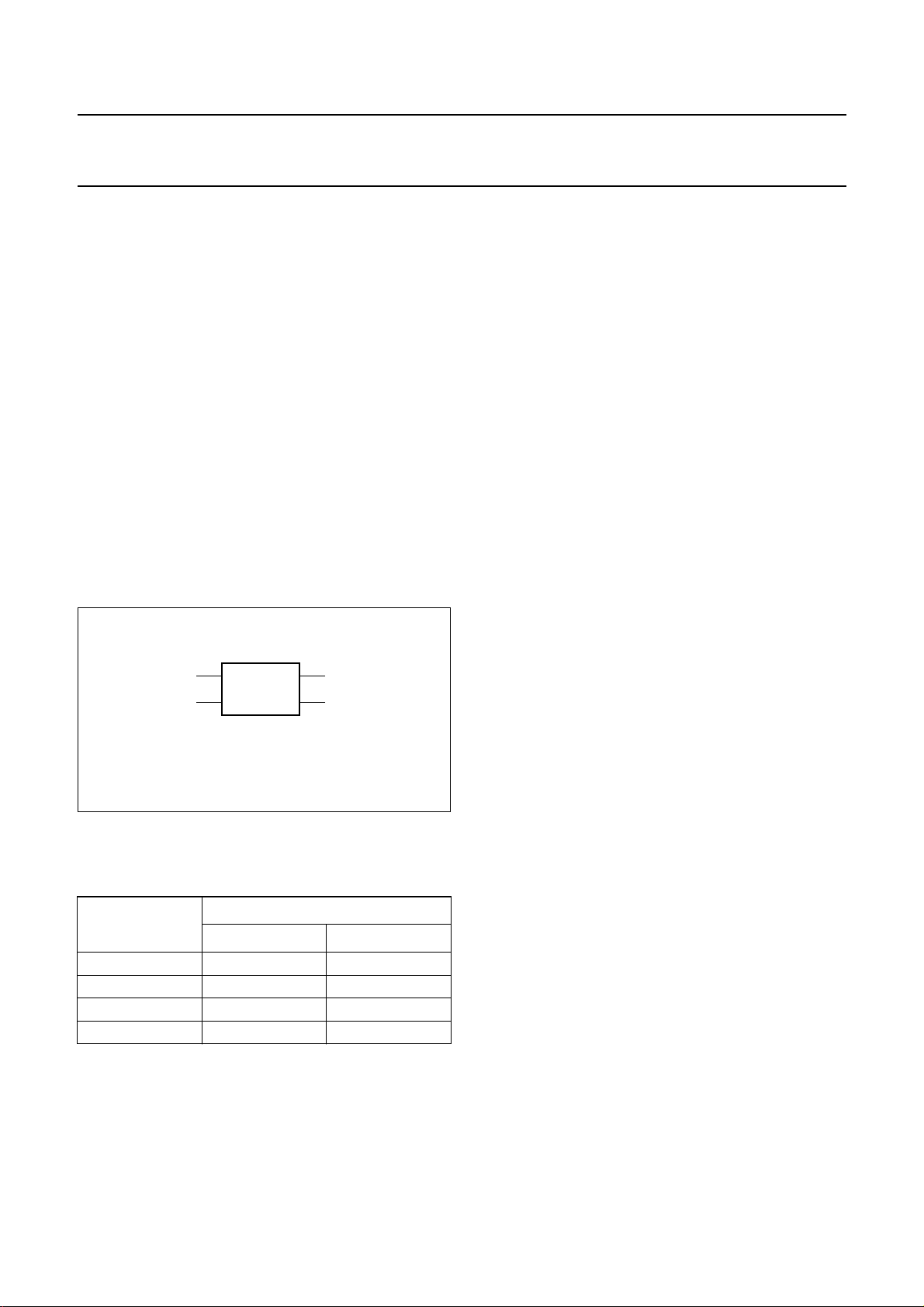

handbook, halfpage

5

voltage

(V)

1.5

V

> 4.75 V

DDD

V

CRESET

reset active

guaranteed

Fig.4 Reset at power-on.

MHB595

< 0.3V

DDD

t

1999 Dec 20 12

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

ha

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Dec 20 13

from ADC

2

S1

I

2

S2

I

2 2 2

LEVEL ADJUST

2

FILTER

2

2

DC

LEVEL ADJUST

LEVEL ADJUST

2

2

4

6

8

ndbook, full pagewidth

DIGITAL

CROSSBAR

SELECT

2

2

2

2

MATRIX

MATRIX

MATRIX

MATRIX

AUTOMATIC

VOLUME

LEVEL

VOLUME

SOFT-MUTE

BASS/TREBLE

BEEPER

LEVEL ADJUST AND MUTE

LEVEL ADJUST AND MUTE

BASS/TREBLE

BASS BOOST

SPATIAL

PSEUDO

VOLUME

CONTOUR

SOFT-MUTE

BEEPER

2

2

2

2

Main

Auxiliary

I

I

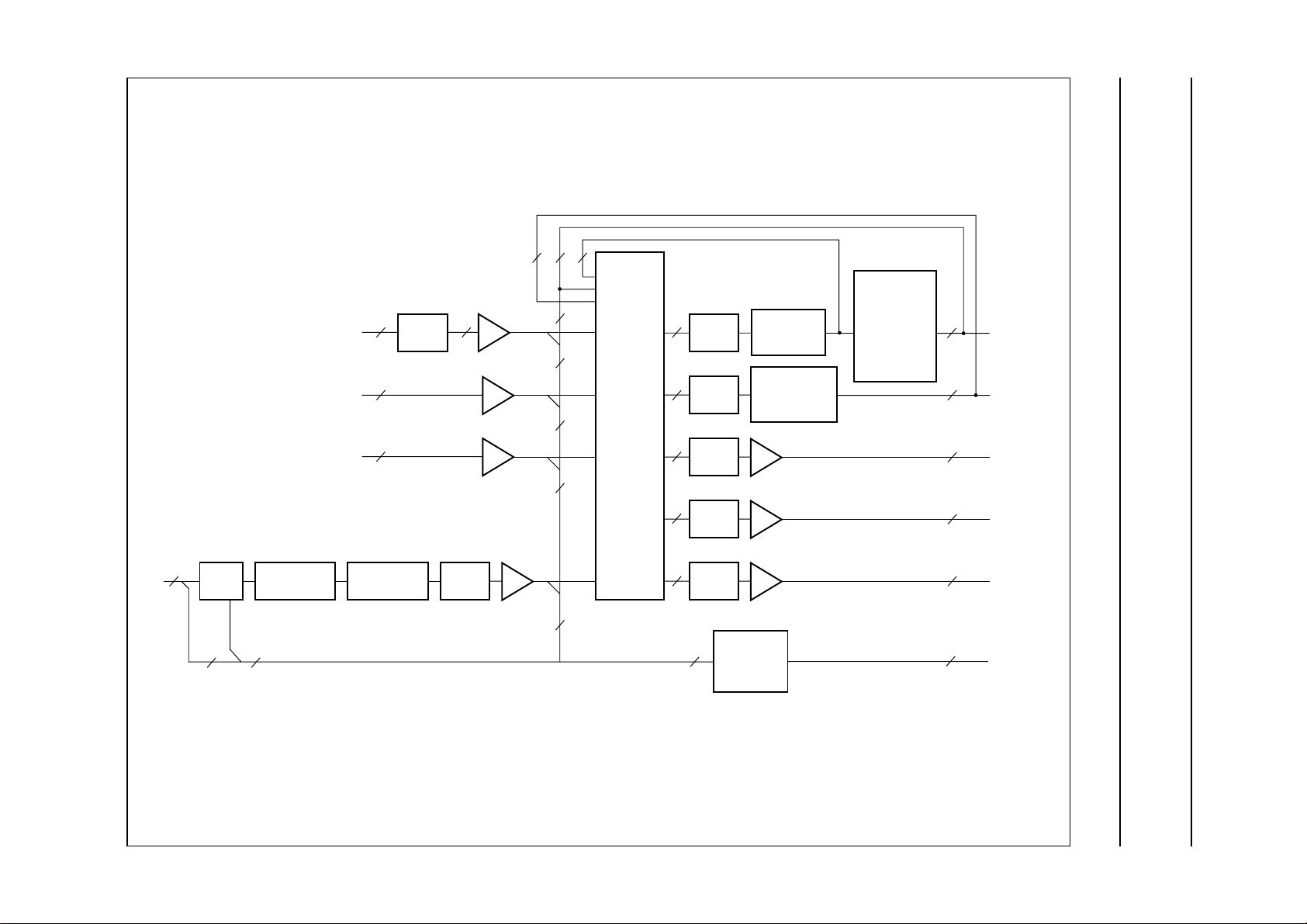

6.2 Digital signal processing

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

2

S1

2

S2

FM

2

DC

FILTER

2 4

ADAPTIVE

DE-EMPHASIS

FIXED

DE-EMPHASIS

LEVEL ADJUST

MATRIX

2

10

14

Fig.5 DSP data flow diagram.

MATRIX

DETECTION

MONITOR

SELECT

PEAK

LEVEL ADJUST

2

1

I

MHB112

DAC

2

C-bus

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

6.2.1 LEVEL SCALING

All input channels to the digital crossbar switch (except for

the loudspeaker feedback path) are equipped with a level

adjust facility to change the signal level in a range from

+15 to −15 dB (see Fig.5). It is recommended to scale all

input channels to be 15 dB below full-scale (−15 dB

full-scale) under nominal conditions.

6.2.2 FM (AM) PATH

A high-pass filter suppresses DC offsets from the

FM demodulator, due to carrier frequency offsets, and

supplies the monitor/peak function with DC values and an

unfiltered signal, e.g. for the purpose of carrier detection.

The de-emphasis function offers fixed settings for the

supported standards (50, 60 and 75 µs).

An adaptive de-emphasis is available for

Wegener-Panda 1 encoded programs.

A matrix performs the dematrixing of the A2 stereo, dual

and mono signals.

6.2.3 MONITOR

This function provides data words from a number of

locations of the signal processing paths to the I2C-bus

interface (2 data bytes). Signal sources include the

FM demodulator outputs, most inputs to the digital

crossbar switch and the outputs of the ADC. Source

selection and data read-out is performed via the I2C-bus.

Optionally, the peak value can be measured instead of

simply taking samples. The internally stored peak value is

reset to zero when the data is read via the I2C-bus.

The monitor function may be used, for example, for signal

level measurements or carrier detection.

6.2.4 LOUDSPEAKER (MAIN) CHANNEL

Volume is controlled individually for each channel ranging

from +24 to −83 dB with 1 dB resolution. There is also a

muteposition.Forthepurposeofasimplecontrolsoftware

in the microcontroller, the decimal number that is sent as

an I2C-bus data byte for volume control is identical to the

volume setting in dBs (e.g. the I2C-bus data byte +10 sets

the new volume value to +10 dB).

Balance can be realized by independent control of the left

and right channel volume settings.

Contour is adjustable between 0 and +18 dB with 1 dB

resolution. This function is linked to the volume setting by

means of microcontroller software.

Bass is adjustable between +15 and −12 dB with 1 dB

resolution and treble is adjustable between

+12 and −12 dB with 1 dB resolution.

For the purpose of a simple control software in the

microcontroller, the decimal number that is sent as an

I2C-bus data byte for contour, bass or treble is identical to

the new contour, bass or treble setting in dBs (e.g. the

I2C-bus data byte +8 sets the new value to +8 dB).

Extra bass boost is provided up to 20 dB with 2 dB

resolution. The implemented coefficient set serves merely

as an example on how to use this filter.

The beeper provides tones in a range from approximately

400 Hz to 30 kHz. The frequency can be selected via the

I2C-bus. The beeper output signal is added to the

loudspeaker and headphone channel signals. The beeper

volume is adjustable with respect to full-scale between

0 and −93 dB with 3 dB resolution. The beeper is not

effected by mute.

Soft mute provides a mute ability in addition to volume

control with a well defined time (32 ms) after which thesoft

mute is completed. A smooth fading is achieved by a

cosine masking.

The matrix provides the following functions: forced mono,

stereo, channel swap, channel 1, channel 2 and spatial

effects.

There are fixed coefficient sets for spatial settings of 30%,

40% and 52%.

The Automatic Volume Level (AVL) function provides a

constant output level of −23 dB full-scale for input levels

between 0 and −29 dB full-scale. There are some fixed

decay time constants to choose from, i.e. 2, 4 and 8 s.

Pseudostereoisbasedonaphaseshiftinonechannelvia

a second-order all-pass filter. There are fixed coefficient

sets to provide 90 degrees phase shift at frequencies of

150, 200 and 300 Hz.

1999 Dec 20 14

6.2.5 HEADPHONE (AUXILIARY) CHANNEL

The matrix provides the following functions: forced mono,

stereo, channel swap, channel 1 and channel 2

(or C and S in Dolby Surround Pro Logic mode).

Volume is controlled individually for each channel in a

range from +24 to −83 dB with 1 dB resolution. There is

also a mute position.

For the purpose of a simple control software in the

microcontroller, the decimal number that is sent as an

I2C-bus data byte for volume control is identical to the

volume setting in dB (e.g. the I2C-bus data byte +10 sets

the new volume value to +10 dB).

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

Balance can be realized by independent control of the left

and right channel volume settings.

Bass is adjustable between +15 and −12 dB with 1 dB

resolution and treble is adjustable between

+12 and −12 dB with 1 dB resolution.

For the purpose of a simple control software in the

microcontroller, the decimal number that is sent as an

I2C-bus data byte for bass or treble is identical to the new

bass or treble setting in dB (e.g. the I2C-bus data byte +8

sets the new value to +8 dB).

The beeper provides tones in a range from approximately

400 Hz to 30 kHz. The frequency can be selected via the

I2C-bus. The beeper output signal is added to the

loudspeaker and headphone channel signals. The beeper

volume is adjustable with respect to full-scale between

0 and −93 dB with 3 dB resolution. The beeper is not

effected by mute.

Soft mute provides a mute ability in addition to volume

control with a well defined time (32 ms) after which thesoft

mute is completed. A smooth fading is achieved by a

cosine masking.

6.2.6 FEATURE INTERFACE

The feature interface comprises two I2S-bus input/output

ports and a system clock output. Each I2S-bus port is

equipped with level adjust facilities that can change the

signal level in a range from +15 to −15 dB with 1 dB

resolution. Outputs can be disabled to improve EMC

performance.

TheI2S-busoutputmatrixprovidesthefollowingfunctions:

forced mono, stereo, channel swap, channel 1 and

channel 2.

One example of how the feature interface can be used in

a TV set is to connect an external Dolby Surround Pro

Logic DSP, such as the SAA7710, to the I2S-bus ports.

Outputs must be enabled and a suitable master clock

signal for the DSP can be taken from pin SYSCLK.

A stereo signal from any source will be output on one of

the I2S-bus serial data outputs and the four processed

signal channels will be entered at both I2S-bus serial data

inputs. Left and right could then be output to the power

amplifiers via the Main channel, centre and surround via

the Auxiliary channel.

6.2.8 CHANNEL TO THE ANALOG CROSSBAR PATH

Level adjust with control positions 0, +3, +6 and +9 dB.

6.2.9 DIGITAL CROSSBAR SWITCH

Input channels to the crossbar switch are from the audio

ADC, I2S1, I2S2, FM path and from the loudspeaker

channel path after matrix and AVL (see Fig.6).

Outputchannelscomprise loudspeaker, headphone, I2S1,

I2S2 and the audio DACs for line output and SCART.

TheI2S1andI2S2outputsalsoprovidedigitaloutputsfrom

the loudspeaker and headphone channels, but without the

beeper signals.

6.2.10 SIGNAL GAIN

There are a number of functions that can provide signal

gain, e.g. volume, bass and treble control. Great care has

to be taken when using gain with large input signals in

order not to exceed the maximum possible signal swing,

which would cause severe signal distortion. The nominal

signal level of the various signal sources to the digital

crossbar switch should be 15 dB below digital full-scale

(−15 dB full-scale). This means that a volume setting of,

say, +15 dB would just produce a full-scale output signal

and not cause clipping, if the signal level is nominal.

Sending illegal data patterns via the I2C-bus will not cause

any changes of the current setting for the volume, bass,

treble, bass boost and level adjust functions.

6.2.11 EXPERT MODE

The TDA9870A provides a special expert mode that gives

directwriteaccesstotheinternalCoefficientRAM(CRAM)

of the DSP. It can be used to create user-defined

characteristics, such as a tone control with different corner

frequencies or special boost/cut characteristics to correct

the low-frequency loudspeaker and/or cabinet frequency

responsesby means of the bass boost filter. However, this

mode must be used with great care.

More information on the functions of this device, such as

the number of coefficients per function, their default

values, memory addresses etc., can be made available on

request.

6.2.7 CHANNEL FROM THE AUDIO ADC

The signal level at the output of the ADC can be adjusted

in a range from +15 to −15 dB with 1 dB resolution.

The audio ADC itself is scaled to a gain of −6 dB.

1999 Dec 20 15

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

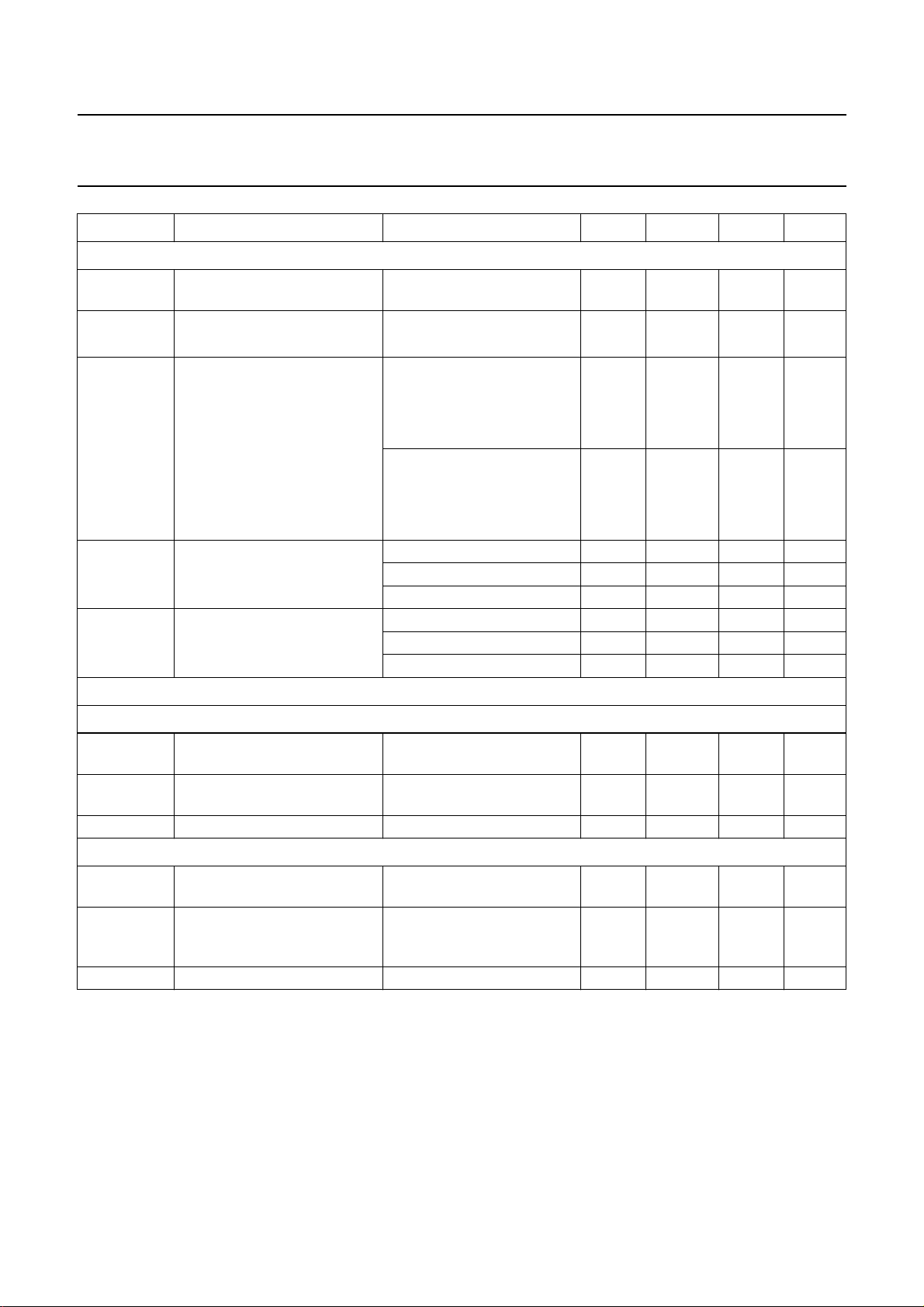

6.2.12 DSP FUNCTIONS

Table 4 Overview of DSP functions

FUNCTION

Bass control for loudspeaker and

headphone output

Treble control for loudspeaker and

headphone output

Contour for loudspeaker output yes control range 0 to +18 dB

Bass boost for loudspeaker output yes control range 0 to +20 dB

Volume control for each separate

channel in loudspeaker and

headphone output

Soft mute for loudspeaker and

headphone output

Spatial effects yes anti-phase crosstalk positions 30, 40 and 52 %

Pseudo stereo yes 90 degrees phase shift at frequency 150, 200 and 300 Hz

Beeper additional to the signal in the

loudspeaker and headphone channel

Automatic Volume Level (AVL) yes step width quasi continuously

General no −3 dB lower corner frequency of DSP 10 Hz

Level adjust I

Level adjust I2S1 and I2S2 outputs yes control range −15 to +15 dB

Level adjust analog crossbar path no control positions 0, 3, 6 and 9 dB

2

S1 and I2S2 inputs yes control range −15 to +15 dB

EXPERT

MODE

yes control range −12 to +15 dB

resolution 1 dB

resolution at frequency 40 Hz

yes control range −12 to +12 dB

resolution 1 dB

resolution at frequency 14 kHz

resolution 1 dB

resolution at frequency 40 Hz

resolution 2 dB

resolution at frequency 20 Hz

corner frequency 350 Hz

no control range −83 to +24 dB

resolution 1 dB

mute position at step 10101100

no processing time 32 ms

yes beep frequencies see Section 10.3.38

control range 0 to −93 dB

resolution 3 dB

mute position at step 00100000

AVL output level for an input level

between 0 and −29 dB full-scale

attack time 10 ms

decay time constant 2, 4 and 8 s

−1 dB bandwidth of DSP 14.5 kHz

resolution 1 dB

resolution 1 dB

mute position at step 00010000

PARAMETER VALUE UNIT

−23 dB

1999 Dec 20 16

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

FUNCTION

EXPERT

MODE

PARAMETER VALUE UNIT

Level adjust audio ADC outputs yes control range +15 to −15 dB

resolution 1 dB

Level adjust FM path yes control range +15 to −15 dB

resolution 1 dB

6.3 Analog audio section

handbook, full pagewidth

SCART 1

SCART 2

external

mono

2

−3 dB

2

−3 dB

2

2

D

2

2

2

A

ANALOG

CROSSBAR

SWITCH

2

2

2

2

ANALOG

MATRIX

ANALOG

MATRIX

ANALOG

MATRIX

A

D

3 dB

2 2

0 dB

3 dB

2

0 dB

3 dB

2

0 dB

2

SCART 1

2

SCART 2

2

Line output

FM

2

I

S1

2

S2

I

2

S1

I

2

S2

I

2

2

2

2

2

DSP

AND

DIGITAL

CROSSBAR

SWITCH

2

D

A

2

D

A

2

Main

2

Auxiliary

MHB113

Fig.6 Block diagram for the audio section.

1999 Dec 20 17

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

6.3.1 ANALOG CROSSBAR SWITCH AND ANALOG MATRIX

There are a number of analog input and output ports with

the TDA9870A (see Figs 6 and 8). Analog source selector

switches are employed to provide the desired analog

signal routing capability. The analog signal routing is

performed by the analog crossbar switch section. A dual

audio ADC provides the connection to the DSP section

and a dual audio DAC provides the connection from the

DSP section to the analog crossbar switch. The digital

signal routing is performed by a digital crossbar switch.

The basic signal routing philosophy of the TDA9870A is

that each switch handles two signal channels at the same

time, e.g. left and right, language A and B, directly at the

source.

Each source selector switch is followed by an analog

matrix to perform further selection tasks, such as putting a

signal from one input channel, say language A, to both

output channels or for swapping left and right channels

(see Fig.7).

handbook, halfpage

left input

right input

ANALOG

MATRIX

left output

right output

MGK110

Fig.7 Analog matrix.

The analog matrix provides the functions given in Table 5.

6.3.2 SCART INPUTS

The SCART specification allows for a signal level of up to

2 V (RMS). Because of signal handling limitations, due to

the 5 V supply voltage of the TDA9870A, it is necessary to

have fixed 3 dB attenuators at the SCART inputs to obtain

a 2 V input. This results in a −3 dB SCART-to-SCART

copy gain. If 0 dB copy gain is preferred (with maximum

1.4 V input), there are 3 and 0 dB amplifiers at the outputs

of SCART 1 and SCART 2 and at the line output.

The input attenuator is realized by an external series

resistor in combination with the input impedance, both of

which form a voltage divider. With this voltage divider the

maximum SCART signal level of 2 V (RMS) is scaled

down to 1.4 V (RMS) at the input pin.

6.3.3 EXTERNAL AND MONO INPUTS

The3 dB input attenuators are not requiredfortheexternal

and mono inputs, because those signal levels are under

control of the TV designer. The maximum allowed input

level is 1.4 V (RMS). By adding external series resistors,

the external inputs can be used as an additional SCART

input.

6.3.4 SCART OUTPUTS

The SCART outputs employ amplifiers with two gain

settings. The gain can be set to 3 or 0 dB via the I2C-bus.

The 3 dB position is needed to compensate for the 3 dB

attenuation at the SCART inputs should

SCART-to-SCART copies with 0 dB gain be preferred

[under the condition of 1.4 V (RMS) maximum input level].

The 0 dB position is needed, for example, for an

external-to-SCART copy with 0 dB gain.

Table 5 Analog matrix functions

MATRIX OUTPUT

MODE

LEFT OUTPUT RIGHT OUTPUT

1 left input right input

2 right input left input

3 left input left input

4 right input right input

All switches and matrices are controlled via the I2C-bus.

1999 Dec 20 18

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

6.3.5 LINE OUTPUT

The line output can provide an unprocessed copy of the

audio signal in the loudspeaker channels. This can be

either an external signal that comes from the dual audio

ADC, or a signal from an internal digital audio source that

comes from the dual audio DAC. The line output employs

amplifiers with two gain settings. The 3 dB position is

needed to compensate for the attenuation at the SCART

inputs, while the 0 dB position is needed, for example, for

non-attenuated external or internal digital signals

(see Section 6.3.4).

6.3.6 LOUDSPEAKER (MAIN) AND HEADPHONE

(AUXILIARY) OUTPUTS

Signals from any audio source can be applied to the

loudspeakerandtotheheadphoneoutput channels via the

digital crossbar switch and the DSP.

6.3.7 DUAL AUDIO DAC

The TDA9870A contains three dual audio DACs, one for

theconnectionfromtheDSPtotheanalogcrossbarswitch

section and two for the loudspeaker and headphone

outputs. Each of the three dual low-noise high-dynamic

range DACs consists of two 15-bit DACs with current

outputs, followed by a buffer operational amplifier.

The audio DACs operate with four-fold oversampling and

noise shaping.

6.3.8 DUAL AUDIO ADC

There is one dual audio ADC in the TDA9870A for the

connection of the analog crossbar switch section to the

DSP. The dual audio ADC consists of two bitstream

3rd-order sigma-delta audio ADCs and a high-order

decimation filter.

6.3.9 STANDBY MODE

The standby mode, selected by setting bit STDBY to

logic 1 (see Section 10.3.2) disables most functions and

reduces power dissipation. The analog crossbar switch

and the SCART section remain operational and can be

controlled by the I2C-bus to support copying of analog

signals from SCART-to-SCART.

Unused internal registers may lose their information in the

standby mode. Therefore, the device needs to be

initialized on returning to the normal operating mode. This

can be accomplished in the same way as after a Power-on

reset.

6.3.10 SUPPLY GROUND

The different supply grounds VSSare internally connected

via the substrate. It is recommended to connect all ground

pins by a copper plane close to the pins.

1999 Dec 20 19

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

a

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Dec 20 20

SCART 1

ndbook, full pagewidth

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

FM/AM

part

I2S1

2

I

S2

SCART 2

external

mono

FM/AM

DEMODULATOR

ADAPTIVE

DE-EMPHASIS

FIXED

DE-EMPHASIS

ADC

−6 dB

STEREO

DECODER

ADC

LEVEL

ADJUST

FM

LEVEL

ADJUST

I2S1

INPUT

LEVEL

ADJUST

I2S2

INPUT

LEVEL

ADJUST

DIGITAL

MATRIX

DIGITAL

MATRIX

DIGITAL

MATRIX

DIGITAL

MATRIX

DIGITAL

MATRIX

AUTOMATIC

VOLUME

LEVEL

I2S1

OUTPUT

LEVEL

ADJUST

I2S2

OUTPUT

LEVEL

ADJUST

DAC

GAIN

LOUDSPEAKER

PROCESSING

HEADPHONE

PROCESSING

DAC

CHANNEL

CHANNEL

DAC

DAC

ANALOG

MATRIX

ANALOG

MATRIX

ANALOG

MATRIX

Main

Auxiliary

2

I

S1

2

S2

I

BUFFER

0/+3 dB

BUFFER

0/+3 dB

BUFFER

0/+3 dB

Line

SCART 1

SCART 2

MHB114

Fig.8 Audio signal flow diagram.

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

7 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

∆V

DD

V

n

I

DDD,ISSD

I

lu(prot)

P

tot

T

stg

T

amb

V

es

Notes

1. Human body model: C = 100 pF; R = 1.5 kΩ.

2. Machine model: C = 200 pF; L = 0.75 µH; R = 0 Ω.

DC supply voltage −0.5 +6.0 V

voltage differences between two VDD pins − 550 mV

voltage on any other pin −0.5 VDD+ 0.5 V

DC current per digital supply pin −±180 mA

latch-up protection current 100 − mA

total power dissipation − 1.0 W

storage temperature −55 +125 °C

ambient temperature −20 +70 °C

electrostatic handling voltage note 1 −2000 +2000 V

note 2 −200 +200 V

8 THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air

TDA9870A (SDIP64) 40 K/W

TDA9870AH (QFP64) 50 K/W

1999 Dec 20 21

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

9 CHARACTERISTICS

V

V

parameters in accordance with system A2; 1 kΩ measurement source resistance for AF inputs; with external

components of Fig.10; unless otherwise specified.

Supplies

V

V

I

V

V

I

V

V

V

I

V

V

V

V

Demodulator supply decoupling and references

V

V

I

Audio supply decoupling and references

V

V

Z

Z

V

Z

Z

= 300 mV; AGCOFF= 0; AGCSLOW = 0; AGCLEV = 0; level and gain settings in accordance with note 1;

SIF(p-p)

=5V; T

DD

=25°C; settings in accordance with B/G standard; FM deviation ±50 kHz; f

amb

= 1 kHz; FM sound

mod

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

DDD1

SSD1

DDD1

DDD2

SSD2

DDD2

digital supply voltage 1 4.75 5.0 5.5 V

digital supply ground 1 note 2 − 0.0 − V

digital supply current 1 V

=5.0V 5368 83mA

DDD1

digital supply voltage 2 4.75 5.0 5.5 V

digital supply ground 2 note 2 − 0.0 − V

digital supply current 2 V

= 5.0 V; system clock

DDD2

0.1 0.4 2 mA

output disabled

SSD3

SSD4

DDA

DDA

digital supply ground 3 note 2 − 0.0 − V

digital supply ground 4 note 2 − 0.0 − V

analog supply voltage 4.75 5.0 5.5 V

analog supply current for

V

= 5.0 V; digital silence 44 56 68 mA

DDA

DACpart

SSA1

analog ground for analog

note 2 − 0.0 − V

front-end

SSA2

analog ground for audio ADC

note 2 − 0.0 − V

part

SSA3

analog ground for audio DAC

note 2 − 0.0 − V

part

SSA4

DEC1

analog ground for SCART − 0.0 − V

analog supply decoupling

3.0 3.3 3.6 V

voltage for demodulator part

ref1

analog reference voltage for

− 2 − V

demodulator part

ref1(sink)

DEC2

sink current at pin V

ref1

analog supply decoupling

− 200 −µA

3.0 3.3 3.6 V

voltage for audio ADC part

ref2

Vref2-VDEC2

Vref2-VSSA2

ref3

reference voltage ratio for

audio ADCs

impedance pins V

impedance pins V

ref2

ref2

to V

to V

reference voltage ratio for

audio DAC and operational

referenced to V

V

DEC2

SSA2

referenced to V

V

SSA2

SSA3

DEC2

DDA

and

and

− 50 − %

− 20 − kΩ

− 20 − kΩ

− 50 − %

amplifier

Vref3-VDDA

Vref3-VSSA3

impedance pins V

impedance pins V

ref3

ref3

to V

to V

DDA

SSA3

− 20 − kΩ

− 20 − kΩ

1999 Dec 20 22

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Power fail detector

V

th(pf)

Digital inputs and outputs

INPUTS

CMOS level input, pull-down (pins TEST1 and TEST2)

V

IL

V

IH

C

i

Z

i

CMOS level input, hysteresis, pull-up (pin CRESET)

V

IL

V

IH

V

hys

C

i

Z

i

INPUTS/OUTPUTS

power fail threshold voltage − 3.9 − V

LOW-level input voltage −− 0.3V

HIGH-level input voltage 0.7V

−−V

DDD

DDD

V

input capacitance −− 10 pF

input impedance − 50 − kΩ

LOW-level input voltage −− 0.3V

HIGH-level input voltage 0.7V

−−V

DDD

DDD

V

hysteresis voltage − 1.3 − V

input capacitance −− 10 pF

input impedance 30 50 − kΩ

I2C-bus level input with Schmitt trigger, open-drain output stage, 400 kHz I2C-bus operation (pins SCL and SDA)

V

IL

V

IH

V

hys

I

LI

C

i

V

OL

C

L

LOW-level input voltage −− 0.3V

HIGH-level input voltage 0.7V

hysteresis voltage − 0.05V

−−V

DDD

− V

DDD

DDD

V

input leakage current −− ±10 µA

input capacitance −− 10 pF

LOW-level output voltage −− 0.6 V

load capacitance −− 400 pF

TTL/CMOS level, 4 mA 3-state output stage, pull-up (pins ADDR1, ADDR2, P1, P2, SCK, WS, SDO1, SDO2, SDI1

and SDI2)

V

IL

V

IH

C

i

V

OL

V

OH

C

L

Z

i

LOW-level input voltage −− 0.8 V

HIGH-level input voltage 2.0 −−V

input capacitance −− 10 pF

LOW-level output voltage −− 0.4 V

HIGH-level output voltage 2.4 −−V

load capacitance −− 100 pF

input impedance − 50 − kΩ

OUTPUTS

CMOS level output, 4 mA 3-state output stage, slew rate controlled (pin SYSCLK)

V

OL

V

OH

C

L

I

LIZ

LOW-level output voltage −− 0.3V

HIGH-level output voltage 0.7V

−−V

DDD

DDD

V

load capacitance −− 100 pF

3-state leakage current Vi= 0 to V

DDD

−− ±10 µA

1999 Dec 20 23

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

SIF1 and SIF2 analog inputs

V

SIF(max)(p-p)

maximum composite SIF input

voltage for clipping

(peak-to-peak value)

V

SIF(min)(p-p)

minimum composite SIF input

voltage for lower limit of AGC

(peak-to-peak value)

AGC AGC range − 24 − dB

f

i

R

i

C

i

∆f

FM

∆f

FM(FS)

C/N

FM

α

ct

input frequency 4 − 9.2 MHz

input resistance AGCLEV = 0 10 −−kΩ

input capacitance − 7.5 11 pF

FM deviation B/G standard; THD < 1% ±100 −−kHz

FM deviation full-scale level terrestrial FM; level adjust

FM carrier-to-noise ratio NFM bandwidth = 6 MHz;

crosstalk attenuation

SIF1 to SIF2

Demodulator performance

THD + N total harmonic distortion plus

noise

S/N signal-to-noise ratio SC1 from FM source to any

B

f

−3dB

res

−3 dB bandwidth from FM source to any

frequency response

20 Hz to 14 kHz

α

cs(dual)

α

cs(stereo)

α

AM

S/N

AM

dual signal channel separation note 4 65 70 − dB

stereo channel separation note 5 40 45 − dB

AM suppression for FM AM:1 kHz, 30% modulation;

AM demodulation SIF level 100 mV (RMS);

SIF input level adjust 0 dB − 941 − mV

SIF input level adjust −10 dB − 2976 − mV

SIF input level adjust 0 dB − 59 − mV

SIF input level adjust −10 dB − 188 − mV

±150 −−kHz

0dB

white noise for S/N = 40 dB;

“CCIR468”

; quasi peak

− 77 −

dB

------ Hz

fi= 4 to 9.2 MHz; note 3 50 −−dB

from FM source to any

output; V

= 1 V (RMS) with

o

− 0.3 0.5 %

low-pass filter

64 70 − dB

output; V

“CCIR468”

SC2 from FM source to any

output; V

“CCIR468”

= 1 V (RMS);

o

; quasi peak

= 1 V (RMS);

o

; quasi peak

60 66 − dB

14.5 15 − kHz

output

from FM to any output;

f

= 1 kHz; inclusive

ref

−±2−dB

pre-emphasis and

de-emphasis

50 −−dB

reference: 1 kHz, 50 kHz

deviation

36 45 − dB

54% AM; 1 kHz AF;

“CCIR468”

; quasi peak

1999 Dec 20 24

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IDENTIFICATION FOR FM SYSTEMS

mod

p

C/N

p

f

ident

t

ident(on)

t

ident(off)

Analog audio inputs

pilot modulation for

25 50 75 %

identification

pilot sideband carrier-to-noise

ratio for identification start

− 27 −

dB

------ Hz

identification window B/G stereo

slow mode 116.85 − 118.12 Hz

medium mode 116.11 − 118.89 Hz

fast mode 114.65 − 120.46 Hz

B/G dual

slow mode 273.44 − 274.81 Hz

medium mode 272.07 − 276.20 Hz

fast mode 270.73 − 277.60 Hz

total identification time ON slow mode −− 2s

medium mode −− 1s

fast mode −− 0.5 s

total identification time OFF slow mode −− 2s

medium mode −− 1s

fast mode −− 0.5 s

MONO INPUT AND EXTERNAL INPUT

V

i(nom)(rms)

nominal level input voltage

(RMS value)

V

i(clip)(rms)

clipping level input voltage

(RMS value)

R

i

input resistance note 6 28 35 42 kΩ

SCART INPUTS

V

i(nom)(rms)

nominal level input voltage at

input pin (RMS value)

V

i(clip)(rms)

clipping level input voltage at

input pin (RMS value)

R

i

input resistance note 6 28 35 42 kΩ

− 500 − mV

THD < 3%; note 6 1250 1400 − mV

−3 dB divider with external

− 350 − mV

15 kΩ resistor; note 7

−3 dB divider with external

1250 1400 − mV

15 kΩ resistor; THD < 3%;

notes 6 and 7

1999 Dec 20 25

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Analog audio outputs

LOUDSPEAKER (MAIN) AND HEADPHONE (AUXILIARY) OUTPUTS

V

o(clip)(rms)

R

o

R

L(AC)

R

L(DC)

C

L

V

offset(DC)

α

mute

G

ro(main,aux)

PSRR

main,aux

SCART OUTPUTS AND LINE OUTPUT

V

o(nom)(rms)

V

o(clip)(rms)

R

o

R

L(AC)

R

L(DC)

C

L

V

offset(DC)

α

mute

B bandwidth from SCART, external and

PSRR power supply ripple rejection f

clipping level output voltage

THD < 3% 1250 1400 − mV

(RMS value)

output resistance 150 250 375 Ω

AC load resistance 10 −−kΩ

DC load resistance 10 −−kΩ

load capacitance − 10 12 nF

static DC offset voltage − 30 70 mV

mute suppression nominal input signal from

80 −−dB

any source; fi= 1 kHz

roll-off gain at 14.5 kHz for

from any source −3 −2 − dB

Main and Auxiliary channels

power supply ripple rejection

for Main and Auxiliary

channels

f

= 70 Hz;

ripple

V

= 100 mV (peak);

ripple

C

=47µF;

Vref

40 45 − dB

signal from I2S-bus

nominal level output voltage

3 dB amplification − 500 − mV

(RMS value)

clipping level output voltage

THD < 3% 1250 1400 − mV

(RMS value)

output resistance 150 250 375 Ω

AC load resistance 10 −−kΩ

DC load resistance 10 −−kΩ

load capacitance −− 2.5 nF

static DC offset voltage output amplifiers at 3 dB

− 30 50 mV

position

mute suppression nominal input signal from

80 −−dB

any source; fi= 1 kHz

20 −−kHz

mono sources;

−3 dB bandwidth

from DSP sources;

14.5 −−kHz

−3 dB bandwidth

= 70 Hz;

ripple

V

= 100 mV (peak);

ripple

C

=47µF;

Vref

40 45 − dB

signal from I2S-bus

1999 Dec 20 26

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Audio performance

THD + N total harmonic distortion plus

noise

V

fi= 1 kHz; bandwidth

20 Hz to 15 kHz; note 8

S/N signal-to-noise ratio reference voltage

V

“CCIR468”

note 8

α

ct

crosstalk attenuation between any analog input

pairs; fi= 1 kHz

between any analog output

pairs; f

α

cs

channel separation between left and right of any

input pair

between left and right of any

output pair

G

A

gain from SCART-to-SCART

with −3 dB input voltage

divider

output amplifier in 3 dB

position; R

output amplifier in 0 dB

position; R

Crystal specification (fundamental mode)

f

xtal

C

L

C

1

C

0

Φ

pull

crystal frequency − 24.576 − MHz

load capacitance − 20 − pF

series capacitance − 20 − fF

parallel capacitance −− 7pF

pulling sensitivity CLchanged from

18 to 16 pF

R

R

R

N

equivalent series resistance at nominal frequency −− 30 Ω

equivalentseries resistance of

unwanted mode

∆T temperature range −20 +25 +70 °C

= 1 V (RMS);

i=Vo

from any analog audio

input to I

fromI

2

S-bus

2

S-bustoanyanalog

− 0.1 0.3 %

− 0.1 0.3 %

audio output

SCART-to-SCART copy − 0.1 0.3 %

SCART-to-Main copy − 0.2 0.5 %

= 1.4 V (RMS);fi= 1 kHz;

o

; quasi peak;

from any analog audio

input to I

fromI

2

S-bus

2

S-bustoanyanalog

73 77 − dB

78 85 − dB

audio output

SCART-to-SCART copy 78 85 − dB

SCART-to-Main copy 73 77 − dB

70 −−dB

65 −−dB

=10kHz

i

65 −−dB

60 −−dB

−1.5 0 +1.1 dB

=15kΩ±10%

ext

−4.5 −3.0 −1.9 dB

=15kΩ±10%

ext

− 25 −

2R

−−Ω

R

10

----------pF

6–

1999 Dec 20 27

Philips Semiconductors Product specification

Digital TV Sound Processor (DTVSP) TDA9870A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

X

J

X

D

X

A

adjustment tolerance −− ±30 10

drift across temperature range −− ±30 10

ageing −− ±5

Notes

1. Definitions of levels and level setting:

a) The full-scale level for analog audio signals is 1.4 V (RMS).

b) The nominal level at the digital crossbar switch is defined at −15 dB (full-scale).

c) Nominal audio input levels for external and mono: 500 mV (RMS) at −9 dB (full-scale).

d) See also Tables 6 and 7.

2. All analog and digital supply ground pins are connected internally.

3. Set demodulator to AM mode. Apply an AM carrier (with 1 kHz and 100%) to one channel. Check AGC step. Switch

AGCoffandset AGC to the gain step found. Measure the 1 kHz signal level of this channel and take it as a reference.

Switch to the other SIF input to which no signal is connected and which is terminated with 50 Ω. Now measure the

1 kHz crosstalk signal level. The SIF source resistance should be low (50 Ω).

4. FM source; in dual mode only A (respectively B) signal modulated; measured at B (respectively A) channel output;

Vo= 1 V (RMS) of modulated channel.

5. FM source; in stereo mode only L (respectively R) signal modulated; measured at R (respectively L) channel output;

Vo= 1 V (RMS) of modulated channel. The stereo channel separation may be limited by adjustment tolerances of

the transmitter.

6. If the supply voltage for the TDA9870A is switched off, because of the ESD protection circuitry, all audio input pins

are short-circuited. To avoid a short-circuit at the SCART inputs a 15 kΩ resistor (−3 dB divider) has to be used.

7. The SCART specification allows a signal level of up to 2 V (RMS). Because of signal handling limitations due to the

5 V supply voltage for the TDA9870A, there is a need for fixed 3 dB attenuators at the SCART inputs. To achieve

SCART-to-SCART copies with 0 dB gain, there are 3 and 0 dB amplifiers at the outputs of SCART 1 and SCART 2

and at the line output. The attenuator is realized by an internal resistor that works together with an external series

resistor as a voltage divider. With this voltage divider the maximum SCART input signal level of 2 V (RMS) is scaled

down to 1.4 V (RMS) at the input pin. To avoid clipping, the 3 dB gain must not be used if the SCART input signal is

larger than 1.4 V (RMS).

8. ADC level adjust is 6 dB, all other level adjusts are 0 dB. If an external −3 dB divider is used set output buffer gain

to 3 dB, tone control to 0 dB, AVL off and volume control to 0 dB.

−6

−6

10

----------year

6–

1999 Dec 20 28

Loading...

Loading...