Philips tda8005a DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

TDA8005A

Low-power (3 V/5 V) smart card

coupler

Preliminary specification

File under Integrated Circuits, IC17

1998 Mar 20

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

FEATURES

• Smart card supply (5 and 3 V ±5%, 20 mA maximum

with controlled rise and fall times)

• Smart card clock generation (up to 8 MHz), with two

times synchronous frequency doubling

• Clock STOP HIGH, clock STOP LOW or 1.25 MHz (from

internal oscillator) for cards power-down mode

• Specific UART on I/O for automatic direct/inverse

convention settings and error management at

character level

• Automatic activation and deactivation sequences

through an independent sequencer

• Supports the protocol T = 0 in accordance with

ISO 7816 GSM11.11 requirements (Global System for

Mobile communication); approved for Final GSM11.11

Test Approval (FTA)

• Several analog options are available for different

applications: doubler or tripler DC-to-DC converter, card

presence, active HIGH or LOW, threshold voltage

supervisor, etc.

• Overloads and take-off protections

• Current limitations in the event of short-circuit

• Special circuitry for killing spikes during power-on or off

• Supply supervisor

• Step-up converter (supply voltage from 2.5 to 6 V)

• Power-down and sleep mode for low power

consumption

• Enhanced ElectroStatic Discharge (ESD) protections on

card side (6 kV minimum)

• Control and communication through a standard RS232

full-duplex interface

• Optional additional I/O ports for:

– keyboard

– LEDs

– display

– etc.

• P80CL51 microcontroller core with 4-kbyte ROM and

256-byte RAM.

APPLICATIONS

• Portable smart card readers for protocol T = 0

• GSM mobile phones.

GENERAL DESCRIPTION

The TDA8005A is a low-cost card interface for portable

smart card readers. Controlled through a standard serial

interface, it takes care of all ISO 7816 and GSM11.11

requirements for both 5 and 3 V cards. It gives the card

and the set a very high level of security, due to its special

hardware against ESD, short-circuiting, power failure, etc.

Its integrated step-up converter allows operation within a

supply voltage range of 2.5 to 6 V.

The very low power consumption in power-down and sleep

modes saves battery power.

Development tools, application report and support

(hardware and software) are available.

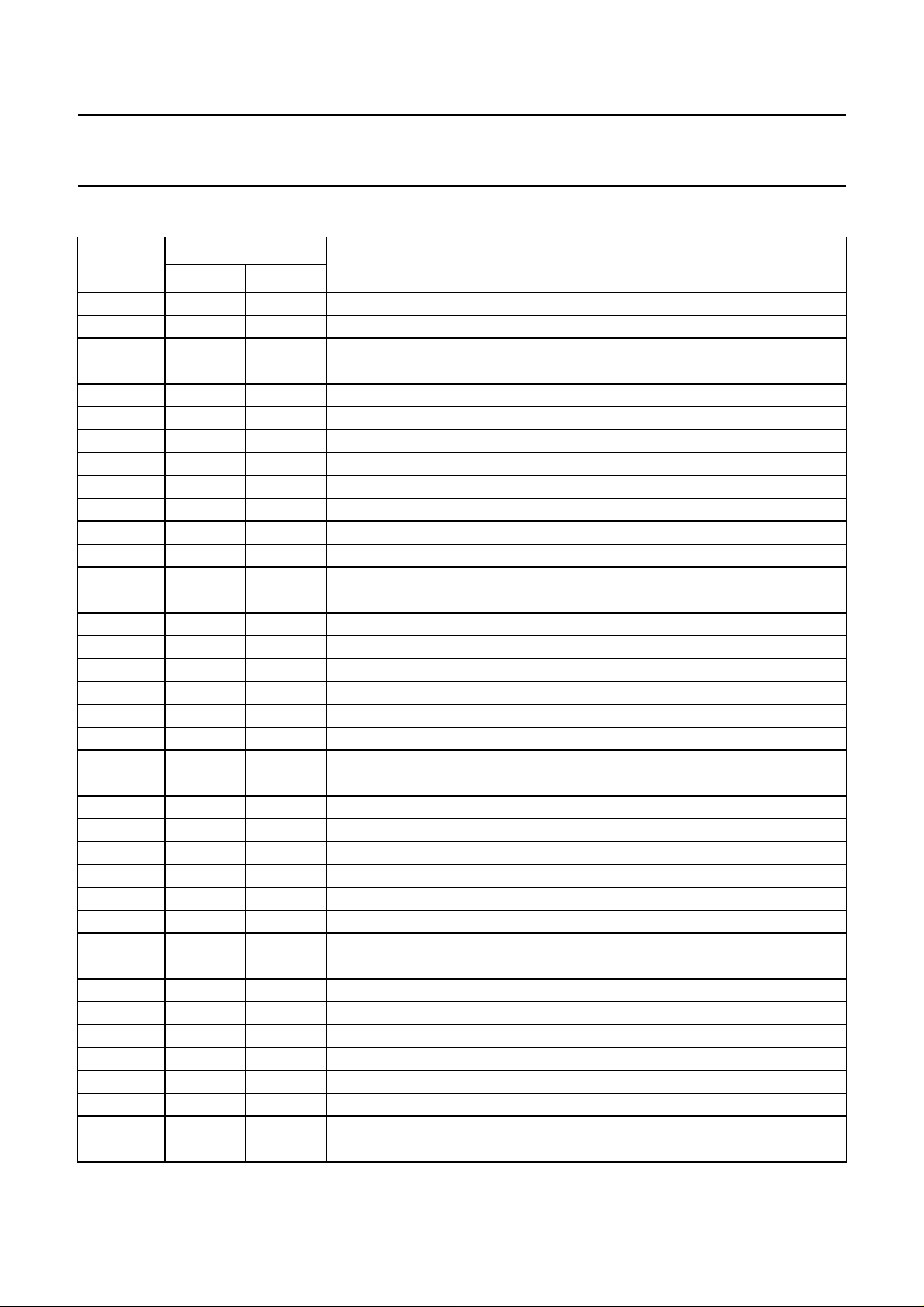

ORDERING INFORMATION

TYPE

NUMBER

TDA8005AG LQFP64 plastic low profile quad flat package; 64 leads; body 10 × 10 × 1.4 mm SOT314-2

TDA8005AH QFP44 plastic quad flat package; 44 leads (lead length 1.3 mm);

1998 Mar 20 2

NAME DESCRIPTION VERSION

body 10 × 10 × 1.75 mm

PACKAGE

SOT307-2

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

I

DD(pd)

I

DD(sm)

I

DD(om)

V

CC

I

CC

SR slew rate on V

t

de

t

act

f

XTAL

T

amb

supply voltage doubler and tripler option 2.5 − 6.0 V

supply current in power-down mode VDD= 5 V; card inactive − 100 −µA

supply current in sleep mode card powered but clock

stopped; no load

doubler option − 500 −µA

tripler option − 700 −µA

supply current in operating mode unloaded; f

= 6.5 MHz; f

f

µC

XTAL

= 13 MHz;

= 3.25 MHz

card

− 5.5 − mA

card supply voltage 5 V card

no load 4.85 5.05 5.25 V

static load 4.75 5.0 5.25 V

dynamic load on 200 nF

4.5 − 5.4 V

capacitor

3 V card

no load 2.9 3.03 3.15 V

static load 2.79 3 3.21 V

dynamic load on 200 nF

2.75 − 3.25 V

capacitor

card supply current operating −−20 mA

limitation −−note 1 mA

(rise and fall) maximum load capacitor

CC

0.04 0.1 0.16 V/µs

250 nF (including typical

200 nF decoupling)

deactivation sequence duration −−225 µs

activation sequence duration −−150 µs

crystal frequency 2 − 16 MHz

operating ambient temperature −25 − +85 °C

Note

1. See Table 3 for mask options.

1998 Mar 20 3

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

BLOCK DIAGRAM

handbook, full pagewidth

V

DDA

2.5 to 6 V

100 nF

ALARM

DELAY

RESET

RxD

TxD

AUX1

AUX2

INT1

P00

to

P37

V

63 (43)

44

46 (31)

22 (17)

DDD

100 nF

10 (7)

SUPPLY

INTERNAL

REFERENCE

VOLTAGE SENSE

2.3 to 2.7 V

alarm

ref

TDA8005AG

47 nF

S1 S2

64 (44) 61 (41) 3 (2) 62 (42)

STEP-UP CONVERTER

INTERNAL OSCILLATOR

2.5 MHz

V

DDD

47 nF

S3 S4

osc ref

60 (40)

V

UP

S5

47 nF

(TDA8005AH)

V

DDD

28 (18)

29 (19)

32 (22)

33 (23)

30 (20)

(1)

CONTROLLER

CL51

4 kbytes ROM

256-byte RAM

OPTIONAL

PORTS

data clk EN S0 S1 R/W

skill

start

RST

off

SEQUENCER

INT

SECURITY

EN1

EN2

EN3

V

CC

GENERATOR

RST

BUFFER

I/O

BUFFER

59 (39)

58 (38)

56 (36)

55 (35)

V

LIS

CC

100 nF

RST

I/O

PERIPHERAL

INTERFACE

micro-

controller

clock

XTAL1 XTAL2

Pin numbers in parenthesis represent the TDA8005AH.

(1) For details see Chapter “Pinning” and Table 3.

ISO 7816 UART

CLOCK CIRCUITRY

osc

36 (26) 35 (25) 37 (27) 2 (1) 53

DGND AGND

Fig.1 Block diagram.

1998 Mar 20 4

I/O

EN4

CLOCK

BUFFER

OUTPUT PORT

EXTENSION

52 51 50 49

K0 K1 K2 K3 K4 K5

57 (37)

47 (32)

4

MGL330

CLK

PRES

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

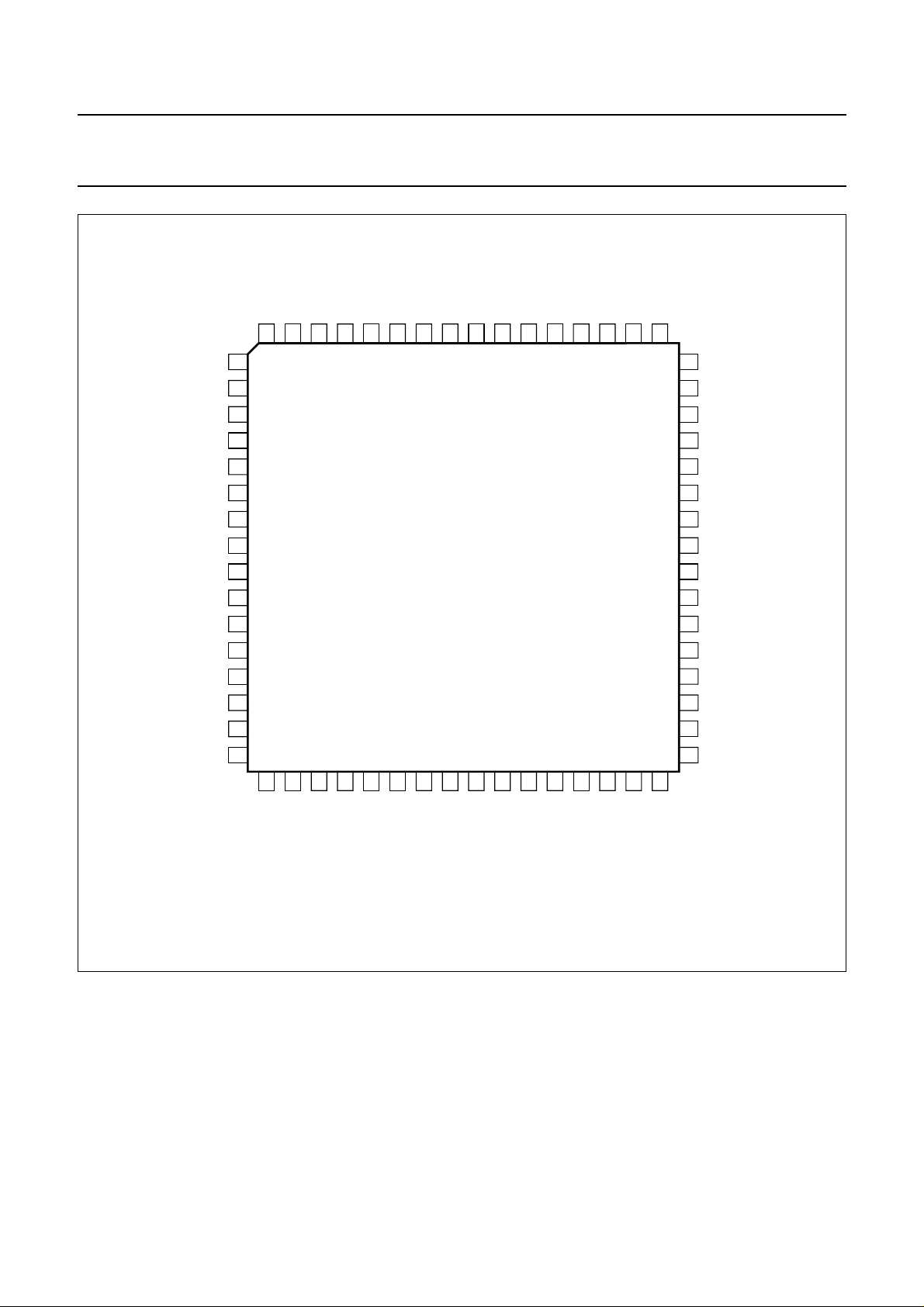

PINNING

SYMBOL

n.c. 1 − not connected

AGND 2 1 analog ground

S3 3 2 contact 3 for the step-up converter

K5 4 − output port from port extension

P03 5 3 general purpose I/O port (connected to port P03)

P02 6 4 general purpose I/O port (connected to port P02)

P01 7 5 general purpose I/O port (connected to port P01)

n.c. 8 − not connected

P00 9 6 general purpose I/O port (connected to port P00)

V

DDD

n.c. 11 − not connected

TEST1 12 8 test pin 1 (connected to port P10; must be left open-circuit in the application)

P11 13 9 general purpose I/O port or interrupt (connected to port P11)

P12 14 10 general purpose I/O port or interrupt (connected to port P12)

P13 15 11 general purpose I/O port or interrupt (connected to port P13)

P14 16 12 general purpose I/O port or interrupt (connected to port P14)

n.c. 17 − not connected

P15 18 13 general purpose I/O port or interrupt (connected to port P15)

P16 19 14 general purpose I/O port or interrupt (connected to port P16)

TEST2 20 15 test pin 2 (connected to PSEN; must be left open-circuit in the application)

P17 21 16 general purpose I/O port or interrupt (connected to port P17)

RESET 22 17 input for resetting the microcontroller (active HIGH)

n.c. 23 − not connected

n.c. 24 − not connected

n.c. 25 − not connected

n.c. 26 − not connected

n.c. 27 − not connected

RxD 28 18 serial interface receive line

TxD 29 19 serial interface transmit line

INT1 30 20 general purpose I/O port or interrupt (connected to port P33)

T0 31 21 general purpose I/O port (connected to port P34)

AUX1 32 22 push-pull auxiliary output (±5 mA; connected to timer T1 e.g. port P35)

AUX2 33 23 push-pull auxiliary output (±5 mA; connected to timer; port P36)

P37 34 24 general purpose I/O port (connected to port P37)

XTAL2 35 25 crystal connection

XTAL1 36 26 crystal connection or external clock input

DGND 37 27 digital ground

n.c. 38 − not connected

LQFP64 QFP44

PIN

DESCRIPTION

10 7 digital supply voltage

1998 Mar 20 5

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

SYMBOL

n.c. 39 − not connected

P20 40 28 general purpose I/O port (connected to port P20)

P21 41 − general purpose I/O port (connected to port P21)

P22 42 29 general purpose I/O port (connected to port P22)

P23 43 30 general purpose I/O port (connected to port P23)

ALARM 44 − open-drain output for power-on reset (active HIGH or LOW by mask option)

n.c. 45 − not connected

DELAY 46 31 external capacitor connection for delayed reset signal

PRES 47 32 card presence contact input (active HIGH or LOW by mask option)

TEST3 48 33 test pin 3 (must be left open-circuit in the application)

K4 49 − output port from port extension

K3 50 − output port from port extension

K2 51 − output port from port extension

K1 52 − output port from port extension

K0 53 − output port from port extension

TEST4 54 34 test pin 4 (must be left open-circuit in the application)

I/O 55 35 data line to/from the card (ISO C7 contact)

RST 56 36 card reset output (ISO C2 contact)

CLK 57 37 clock output to the card (ISO C3 contact)

V

CC

LIS 59 39 supply for low-impedance on cards contacts

S5 60 40 contact 5 for the step-up converter

S2 61 41 contact 2 for the step-up converter

S4 62 42 contact 4 for the step-up converter

V

DDA

S1 64 44 contact 1 for the step-up converter

LQFP64 QFP44

PIN

DESCRIPTION

58 38 card supply output voltage (ISO C1 contact)

63 43 analog supply voltage

1998 Mar 20 6

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

handbook, full pagewidth

V

n.c.

AGND

S3

K5

P03

P02

P01

n.c.

P00

DDD

n.c.

TEST1

P11

P12

P13

P14

DDA

VS1S4

64

63

1

2

3

4

5

6

7

8

S2

S5.

62

61

60

LIS

59

CC

V

CLK

RST

I/O

TEST4K0K1

54

58

57

56

55

53

K2

K3

K4

50

52

51

49

TEST3

48

47

PRES

46

DELAY

45

n.c.

ALARM

44

43

P23

42

P22

41

P21

TDA8005AG

P20

9

10

11

12

13

14

15

16

40

39

n.c.

38

n.c.

37

DGND

36

XTAL1

35

XTAL2

34

P37

33

AUX2

17

n.c.

18

P15

19

P16

20

TEST2

21

P17

22

RESET

23

n.c.

Fig.2 Pin configuration (LQFP64).

1998 Mar 20 7

24

n.c.

25

n.c.

26

n.c.

27

n.c.

28

RxD

29

TxD

30

INT1

31

T0

32

AUX1

MGL331

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

handbook, full pagewidth

AGND

S3

P03

P02

P01

P00

V

DDD

TEST1

P11

P12

P13

DDA

S1

V

S4

S2

S5

44

43

42

41

40

1

2

3

4

5

14

P16

TDA8005AH

15

16

P17

TEST2

6

7

8

9

10

11

12

13

P14

P15

LIS

39

17

RESET

CC

V

38

18

RxD

CLK

37

19

TxD

RST

36

20

INT1

I/O

35

21

T0

TEST4

34

22

AUX1

33

32

31

30

29

28

27

26

25

24

23

MGL332

TEST3

PRES

DELAY

P23

P22

P20

DGND

XTAL1

XTAL2

P37

AUX2

Fig.3 Pin configuration (QFP44).

1998 Mar 20 8

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

FUNCTIONAL DESCRIPTION

Microcontroller

The microcontroller is a P80CL51 with 256 bytes of RAM

instead of 128. The baud rate of the UART has been

multiplied by four in modes 1, 2 and 3. This means that the

division factor of 32 in the formula is replaced by 8 in both

reception and transmission mode and that in the reception

modes only four samples per bit are taken with decision on

the majority of samples 2, 3 and 4; the delay counter has

been reduced from 1536 to 24 as well.

Remark: this has an impact when getting out of

power-down mode. It is recommended to switch to

internal clock before entering power-down mode.

All the other functions remain unchanged. Refer to the

P80CL51 data sheet for any further information. Internal

ports INT0 (P32), P10, P04 to P07 and P24 to P27 are

used for controlling the smart card interface.

Mode 0 is unchanged. The baud rate for modes 1 and 3 is:

SMOD

2

---------------- 8

×

---------------------------------------------- 12 256 TH1–()×

f

clk

The baud rate for mode 2 is:

SMOD

2

---------------- 16

f

×

clk

For mode 3 timing see Table 1.

Supply

The circuit operates within a supply voltage range of

2.5 to 6 V. The supply pins are V

AGND. Pins V

and AGND supply the analog drivers to

DDA

DDD

, V

DDA

, DGND and

the card and have to be externally decoupled because of

the large current spikes that the card and the step-up

converter can create. An integrated spike killer ensures

the contacts to the card remain inactive during power-up or

power-down. An internal voltage reference is generated

which is used within the step-up converter, the voltage

supervisor and the V

generator.

CC

The voltage supervisor generates an internal alarm pulse,

whose length is defined by an external capacitor tied to the

DELAY pin, when V

is too low to ensure proper

DDD

operation (1 ms per 1 nF typical). This pulse is used as a

reset pulse by the controller, in parallel with an external

reset input, which can be tied to the system controller.

It is also used in order to either block any spurious card

contacts during controllers reset, or to force an automatic

deactivation of the contacts in the event of supply dropout;

see Sections “Activation sequence” and “Deactivation

sequence”.

In the 64 pin version, this reset pulse is output to the open

drain ALARM pin, which may be selected active HIGH or

active LOW by mask option and may be used as a reset

pulse for other devices within the application.

Table 1 Mode 3 timing

BAUD

= 6.5 MHz;

f

clk

VDD=5V

f

= 3.25 MHz;

clk

VDD=5or3V

RATE

SMOD TH1 SMOD TH1

135416 1 255 −−

67708 0 255 1 255

45139 1 253 −−

33854 0 254 0 255

27083 1 251 −−

22569 0 253 1 253

16927 −−0 254

13542 −−1 251

11285 0 250 0 253

1998 Mar 20 9

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

handbook, full pagewidth

V

th(VDD)

+ V

hys(VthVDD)

V

th(DELAY)

V

th(VDD)

V

DELAY

ALARM

V

DD

Fig.4 Supply supervisor.

Low impedance supply (pin LIS)

For some applications, it is mandatory that the contacts to

the card (VCC, RST, CLK and I/O) are low impedance while

the card is inactive and also when the coupler is not

powered. An auxiliary supply voltage on pin LIS ensures

this condition where I

≤ 5 µA for V

LIS

= 5 V. This low

LIS

impedance situation is disabled when VCC starts rising

during activation, and re-enabled when the step-up

converter is stopped during deactivation. If this feature is

not required, the LIS pin must be tied to V

DDD

.

Step-up converter

Except for the V

buffers, the whole circuit is powered by V

generator and the other cards contacts

CC

and V

DDD

DDA

.

If the supply voltage is 3 or 5 V, then a higher voltage is

needed for the ISO contacts supply. When a card session

is requested by the controller, the sequencer first starts the

step-up converter, which is a switched capacitors type,

clocked by an internal oscillator at a frequency of

approximately 2.5 MHz. The output voltage V

regulated at approximately 6.5 V and then fed to the V

step-up

is

CC

generator. VCC and DGND are used as a reference for all

other cards contacts.

MGL333

The step-up converter may be chosen as a doubler or a

tripler by mask option, depending on the voltage and the

current needed on the card.

ISO 7816 security

The correct sequence during activation and deactivation of

the card is ensured through a specific sequencer, clocked

by a division ratio of the internal oscillator.

Activation (START signal P05; see Table 3) is only

possible if the card is present (PRES HIGH or LOW

according to mask option), and if the supply voltage is

correct (ALARM signal inactive); CLK and RST are

controlled by RSTIN (internal signal; port P04), allowing

the correct count of CLK pulses during answer-to-reset

from the card.

The presence of the card is signalled to the controller by

the OFF signal (port P10; see Table 3).

During a session, the sequencer performs an automatic

emergency deactivation in the event of card take-off,

supply voltage drop, or hardware problems. The OFF

signal falls thereby warning the controller.

1998 Mar 20 10

Philips Semiconductors Preliminary specification

Low-power (3 V/5 V) smart card coupler TDA8005A

Clock circuitry

The clock to the microcontroller and the clock to the card

are derived from the main clock signal (XTAL from

2 to 16 MHz, or an external clock signal).

Directly after reset and during power reduction modes the

microcontroller clock frequency f

equals1⁄8f

clk

INT

; f

is

INT

always present because it is derived from the internal

oscillator and gives the lowest power consumption.

When required (for card session, serial communication or

anything else) the microcontroller may choose to clock

itself with

XTAL

,1⁄4f

XTAL

or1⁄2f

. All frequency changes

INT

1

⁄2f

are synchronous, thereby ensuring no hang-up due to

short spikes etc.

Cards clock: the microcontroller may select to send the

card a card clock frequency of1⁄2f

1

⁄2f

(≈1.25 MHz), or to stop the clock HIGH or LOW.

INT

XTAL

,1⁄4f

XTAL

,1⁄8f

XTAL

or

All transitions are synchronous, ensuring correct pulse

length during start or change in accordance with

ISO 7816.

After power on, CLK is set at STOP LOW and f

1

⁄8f

.

INT

is set at

clk

Power-down and sleep modes

The TDA8005A offers a large flexibility for defining power

reduction modes by software. Some configurations are

described below.

In the power-down mode, the microcontroller is in

power-down and the supply and the internal oscillator are

active. The card is not active; this is the smallest power

consumption mode. Any change on P1 ports or on PRES

will wake-up the circuit (for example, a key pressed on the

keyboard, the card inserted or taken off).

In the sleep mode, the card is powered but configured in

the idle or sleep mode. The step-up converter will only be

active when it is necessary to reactivate V

step-up

. When the

microcontroller is in power-down mode any change on P1

ports or on PRES will wake up the circuit.

In both power reduction modes the sequencer is active,

allowing automatic emergency deactivation in the event of

card take-off, hardware problems, or supply dropout.

The TDA8005A is set into power-down or sleep mode by

software. There are several ways to return to normal

mode: insertion or extraction of the card, detection of a

change on P1 (which can be a key pressed) or a command

from the system microcontroller. For example, if the

system monitors the clock signal on XTAL1, it may stop

this clock after setting the device into power-down mode

and then wake it up when sending the clock signal again.

In this situation, the internal clock should have been used

before the f

clk

.

Peripheral interface

This block allows synchronous serial communication with

the three peripherals (ISO 7816 UART, clock circuitry and

output port extension); see Figs 1 and 5.

handbook, full pagewidth

RESET

CC0 CC1 CC2 CC3 CC4 CC5 CC6 CC7

UC0

UT0

PE0

P24

DATA

clock configuration

UART configuration

UC1 UC2 UC3 UC4 UC5 UC6 UC7

UART transmit

UT1 UT2 UT3 UT4 UT5 UT6 UT7

ports extension

PE1 PE2 PE3 PE4 PE5 PE6 PE7

P06

STROBE

P07

ENABLE

PERIPHERAL CONTROL

P27

REG0

Fig.5 Peripheral interface diagram.

1998 Mar 20 11

P26

REG1

P25

R/W

UR1 UR2 UR3 UR4 UR5 UR6 UR7

UR0

US1 US2 US3 US4 US5 US6 US7

US0

P32

INT

UART receive

UART status register

MGL334

Loading...

Loading...