Philips TDA8004AT Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TDA8004AT

IC card interface

Preliminary specification

File under Integrated Circuits, IC02

2000 Feb 29

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

FEATURES

• 3 or 5 V supply for the IC (GND and VDD)

• Step-up converter for VCC generation (separately

powered with a 5 V ±10% supply, V

and PGND)

DDP

• 3 specificprotectedhalfduplexbidirectionalbufferedI/O

lines (C4, C7 and C8)

• VCC regulation (5 or 3 V ±5% on 2 × 100 nF or

1 × 100 nF and 1 × 220 nF multilayer ceramic

capacitors with low ESR, ICC< 65 mA at

4.5V<V

< 6.5 V, current spikes of 40 nAs up to

DDP

20 MHz, with controlled rise and fall times, filtered

overload detection approximately 90 mA)

• Thermal and short-circuit protections on all card

contacts

• Automatic activation and deactivation sequences

(initiated by software or by hardware in the event of a

short-circuit, card take-off, overheating or supply

drop-out)

• Enhanced ESD protection on card side (>6 kV)

• 26 MHz integrated crystal oscillator

• Clock generation for the card up to 20 MHz (divided by

1, 2, 4 or 8 through CLKDIV1 and CLKDIV2 signals)

with synchronous frequency changes

• Non-inverted control of RST via pin RSTIN

• ISO 7816, GSM11.11 and EMV (payment systems)

compatibility

• Supply supervisor for spikes killing during power-on

and power-off

• One multiplexed status signal OFF.

APPLICATIONS

• IC card readers for banking

• Electronic payment

• Identification

• Pay TV.

GENERAL DESCRIPTION

The TDA8004AT is a complete low cost analog interface

for asynchronous 3 or 5 V smart cards. It can be placed

between the card and the microcontroller with very few

external components to perform all supply protection and

control functions.

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

TDA8004AT SO28 plastic small outline package; 28 leads; body width 7.5 mm SOT136-1

2000 Feb 29 2

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

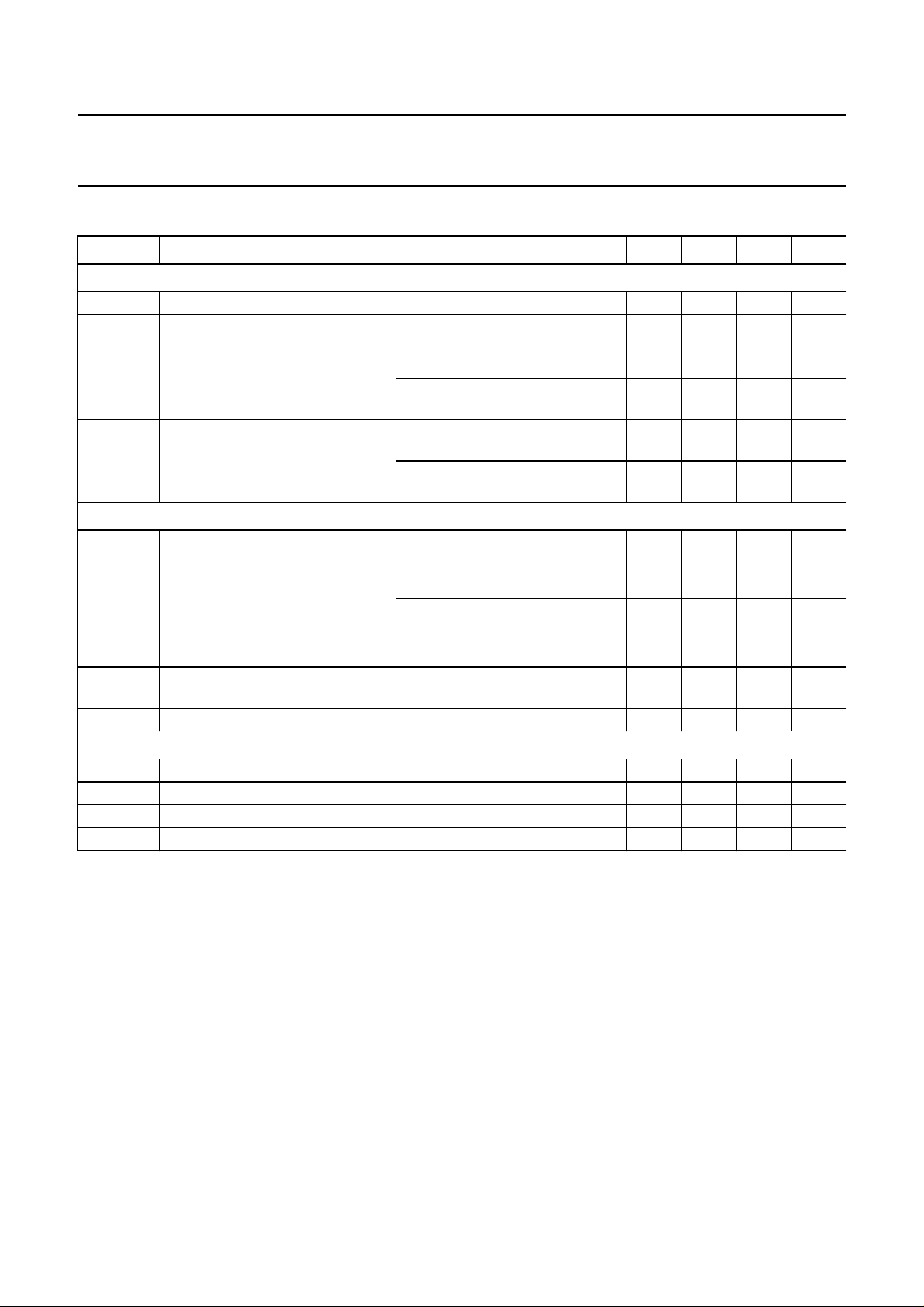

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DD

V

DDP

I

DD

I

DDP

Card supply

V

CC

V

i(ripple)(p-p)

card supply current VCC from 0 to 5 or to 3 V −−65 mA

I

CC

General

f

CLK

t

de

P

tot

T

amb

supply voltage 2.7 − 6.5 V

step-up supply voltage 4.5 5 6.5 V

supply current inactive mode; VDD= 3.3 V;

f

=10MHz

XTAL

active mode; V

f

= 10 MHz; no load

XTAL

step-up supply current inactive mode; V

f

=10MHz

XTAL

active mode; V

f

= 10 MHz; no load

XTAL

card supply voltage including

ripple

5 V card

DC I

< 65 mA 4.75 − 5.25 V

CC

DD

DDP

DDP

= 3.3 V;

=5V;

=5V;

−−1.2 mA

−−1.5 mA

−−0.1 mA

−−18 mA

AC current spikes of 40 nAs 4.65 − 5.25 V

3 V card

DC I

< 65 mA 2.85 − 3.15 V

CC

AC current spikes of 40 nAs 2.76 − 3.20 V

ripple voltage on V

CC

from 20 kHz to 200 MHz −−350 mV

(peak-to-peak value)

card clock frequency 0 − 20 MHz

deactivation cycle duration 60 80 100 µs

continuous total power dissipation T

= −25 to +85 °C −−0.56 W

amb

ambient temperature −25 − +85 °C

2000 Feb 29 3

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

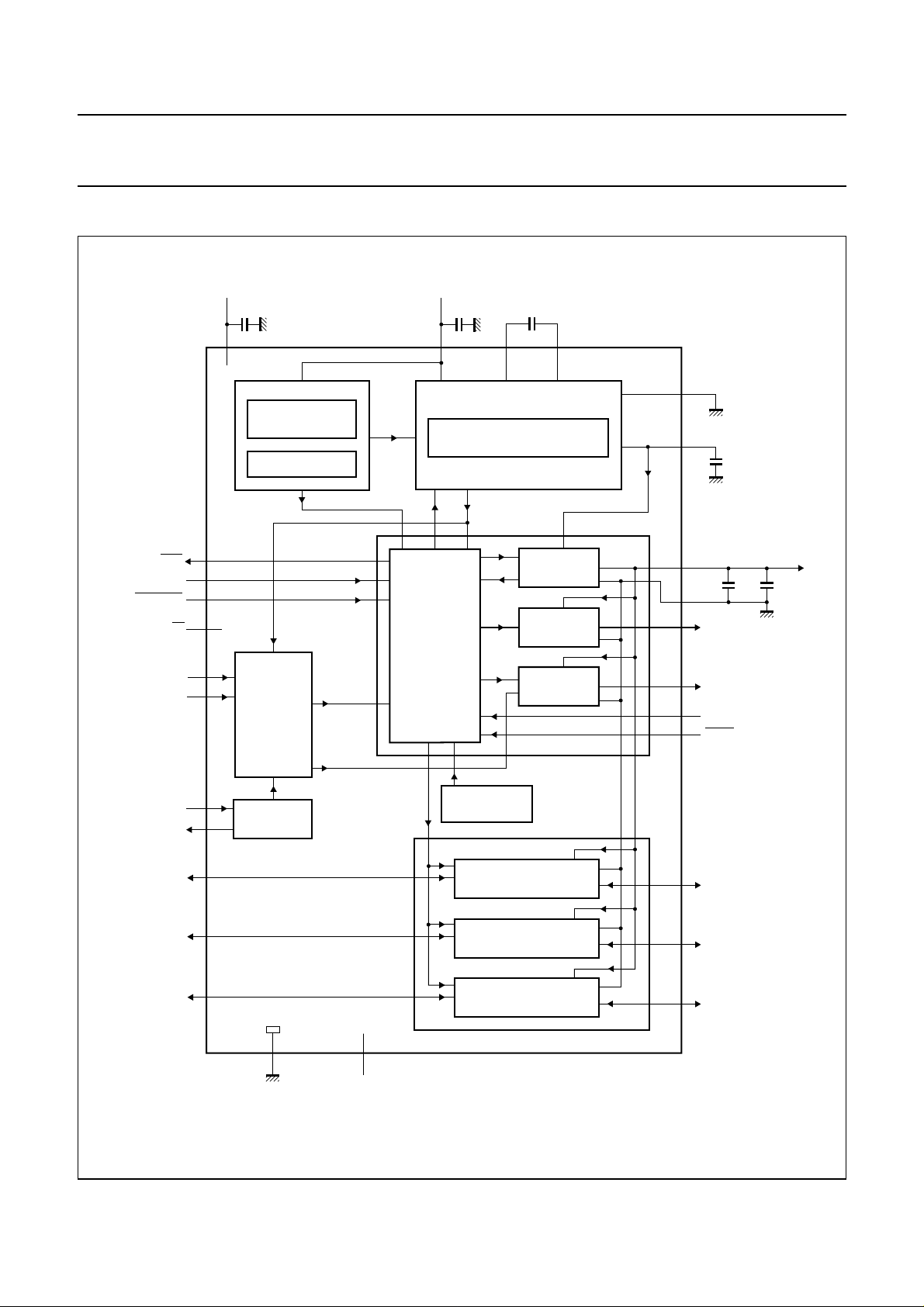

BLOCK DIAGRAM

handbook, full pagewidth

OFF

RSTIN

CMDVCC

5V/3V

CLKDIV1

CLKDIV2

V

DD

23

20

19

3

1

2

100 nF

21

CIRCUITRY

SUPPLY

INTERNAL

REFERENCE

VOLTAGE SENSE

HORSEQ

CLOCK

CLK

V

ALARM

V

DDP

ref

SEQUENCER

100 nF

6

STEP-UP CONVERTER

INTERNAL OSCILLATOR

EN1 CLKUP

100 nF

S1 S2

75

2.5 MHz

EN2

PV

CC

GENERATOR

EN5

EN4

V

CC

RST

BUFFER

CLOCK

BUFFER

PGND

4

VUP

8

100 nF

V

17

CC

100

100

nF

14

CGND

16

15

10

9

nF

RST

CLK

PRES

PRES

XTAL1

XTAL2

AUX1UC

24

OSCILLATOR

25

27

EN3

PROTECTION

TDA8004AT

AUX2UC

I/OUC

All capacitors are mandatory.

28

26

22

GND

18

n.c.

Fig.1 Block diagram.

2000 Feb 29 4

THERMAL

TRANSCEIVER

TRANSCEIVER

TRANSCEIVER

I/O

I/O

I/O

13

12

11

FCE658

AUX1

AUX2

I/O

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

PINNING

SYMBOL PIN I/O DESCRIPTION

CLKDIV1 1 I control with CLKDIV2 for choosing CLK frequency

CLKDIV2 2 I control with CLKDIV1 for choosing CLK frequency

5V/

3V 3 I control signal for selecting VCC= 5 V (HIGH) or VCC= 3 V (LOW)

PGND 4 supply power ground for step-up converter

S2 5 I/O capacitance connection for step-up converter (a 100 nF capacitor with ESR < 100 mΩ

must be connected between pins S1 and S2)

V

DDP

S1 7 I/O capacitance connection for step-up converter (a 100 nF capacitor with ESR < 100 mΩ

VUP 8 O output of step-up converter (a 100 nF capacitor with ESR < 100 mΩ must be connected

PRES 9 I card presence contact input (active LOW); if PRES or PRES is true, then the card is

PRES 10 I card presence contact input (active HIGH); if PRES or

I/O 11 I/O data line to and from card (C7) (internal 10 kΩ pull-up resistor connected to V

AUX2 12 I/O auxiliary line to and from card (C8) (internal 10 kΩ pull-up resistor connected to V

AUX1 13 I/O auxiliary line to and from card (C4) (internal 10 kΩ pull-up resistor connected to V

CGND 14 supply ground for card signals

CLK 15 O clock to card (C3)

RST 16 O card reset (C2)

V

CC

n.c. 18 − not connected

CMDVCC 19 I start activation sequence input from microcontroller (active LOW)

RSTIN 20 I card reset input from microcontroller (active HIGH)

V

DD

GND 22 supply ground

OFF 23 O NMOS interrupt to microcontroller (active LOW) with 20 kΩ internal pull-up resistor

XTAL1 24 I crystal connection or input for external clock

XTAL2 25 O crystal connection (leave open circuit if an external clock source is used)

I/OUC 26 I/O microcontroller data I/O line (internal 10 kΩ pull-up resistor connected to V

AUX1UC 27 I/O auxiliary line to and from microcontroller (internal 10 kΩ pull-up resistor connected to

AUX2UC 28 I/O auxiliary line to and from microcontroller (internal 10 kΩ pull-up resistor connected to

6 supply power supply voltage for step-up converter

must be connected between pins S1 and S2)

to PGND)

considered as present

PRES is true, then the card is

considered as present

)

CC

CC

CC

17 O supply for card (C1); decouple to CGND with 2 × 100 nF or 1 × 100nF and 1 × 220 nF

capacitors with ESR < 100 mΩ (with 220 nF, the noise margin on VCC will be higher)

21 supply supply voltage

connected to VDD(refer section “Fault detection”)

)

DD

V

)

DD

V

)

DD

)

)

2000 Feb 29 5

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

FUNCTIONAL DESCRIPTION

Throughout this document,it is assumed that thereader is

familiar with ISO7816 norm terminology.

Power supply

The supply pins for the IC are VDDand GND. VDD should

be in the range from 2.7 to 6.5 V. All interface signals with

the microcontroller are referenced to VDD; therefore be

sure the supply voltage of the microcontroller is also at

VDD. All card contacts remain inactive during powering up

handbook, halfpage

CLKDIV1

CLKDIV2

5V/3V

PGND

S2

V

DDP

S1

VUP

PRES

PRES

I/O

AUX2

AUX1

CGND

1

2

3

4

5

6

7

TDA8004AT

8

9

10

11

12

13

FCE659

28

27

26

25

24

23

22

21

20

19

18

17

16

1514

AUX2UC

AUX1UC

I/OUC

XTAL2

XTAL1

OFF

GND

V

DD

RSTIN

CMDVCC

n.c.

V

CC

RST

CLK

or powering down. The sequencer is not activated until

VDD reaches V

below V

, an automatic deactivation of the contacts is

th2

th2+Vhys(th2)

(see Fig.3). When VDD falls

performed.

For generating a 5 V ±5% VCC supply to the card, an

integrated voltage doubler is incorporated. This step-up

converter should be separately supplied by V

DDP

and

PGND (from 4.5 to 6.5 V). Due to large transient currents,

the 2 × 100 nF capacitors of the step-up converter should

have an ESR of less than 100 mΩ,and belocated as near

as possible to the IC.

The supply voltages VDDand V

may be applied to the

DDP

IC in any time sequence.

If a voltage between 7 and 9 V is available within the

application, this voltage may be tied to pin VUP, thus

blocking the step-up converter. In this case, V

DDP

must be

tiedto VDDandthe capacitor between pinsS1 and S2may

be omitted.

Voltage supervisor

This block surveys the VDD supply. A defined reset pulse

of approximately 10 ms (tW) is used internally for

maintainingthe IC in the inactivemodeduring powering up

or powering down of VDD (see Fig.3)).

Fig.2 Pin configuration.

2000 Feb 29 6

As long as VDD is less than V

th2+Vhys(th2)

, the IC will

remaininactive whatever the levelson the command lines.

This also lasts for the duration of tWafter VDDhas reached

a level higher than V

th2+Vhys(th2)

.

The system controller should not attempt to start an

activation sequence during this time.

When VDDfalls below V

, a deactivation sequence of the

th2

contacts is performed.

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

handbook, full pagewidth

V

+ V

th2

V

DD

hys(th2)

V

th2

t

W

ALARM

(internal signal)

Fig.3 Alarm as a function of VDD (tW= 10 ms).

Clock circuitry

The clock signal (CLK) to the card is either derived from a

clock signal input on pin XTAL1 or from a crystal up to

26 MHz connected between pins XTAL1 and XTAL2.

The frequency may be chosen at f

or1⁄8f

via pins CLKDIV1 and CLKDIV2.

XTAL

XTAL

,1⁄2f

XTAL

,1⁄4f

XTAL

The frequency change is synchronous, which means that

during transition, no pulse is shorter than 45% of the

smallest period and that the first and last clock pulse

around the change has the correct width.

In the case of f

, the duty factors are dependent on the

XTAL

signal at XTAL1.

t

W

FCE660

Inthe other cases, itisguaranteed between 45% and 55%

of the period.

The crystal oscillator runs as soon as the IC is

powered-up. If the crystal oscillator is used, or if the clock

pulse on XTAL1 is permanent, then the clock pulse will be

applied to the card according to the timing diagram of the

activation sequence (see Fig.5).

If the signal applied to XTAL1 is controlled by the

microcontroller, then the clock pulse will be applied to the

card by the microcontroller after completion of the

activation sequence.

Table 1 Clock circuitry definition

In order to reach a 45% to 55% duty factor on pin CLK the

input signal on XTAL1 should have a duty factor of

48% to 52% and transition times of less than 5% of the

input signal period.

If a crystal is used with f

, the duty factor on pin CLK

XTAL

may be 45% to 55% depending on the layout and on the

crystal characteristics and frequency.

2000 Feb 29 7

CLKDIV1 CLKDIV2 CLK

00

01

11

10f

1

⁄

f

8

XTAL

1

⁄

f

4

XTAL

1

⁄

f

2

XTAL

XTAL

Philips Semiconductors Preliminary specification

IC card interface TDA8004AT

I/O circuitry

The three data lines I/O, AUX1 and AUX2 are identical.

TheIdle state isrealized by data linesI/O and I/OUC being

pulled HIGH via a 10 kΩ resistor (I/O to VCCand I/OUC to

VDD).

I/O is referenced to VCC, and I/OUC to VDD, thus allowing

operation with VCC≠ VDD.

The first line on which a falling edge occurs becomes the

master.Ananti-latchcircuit disables the detection of falling

edges on the other line, which then becomes the slave.

After a time delay t

(approximately 200 ns), the

d(edge)

N transistoron the slave line isturnedon, thus transmitting

the logic 0 present on the master line.

When the masterline returns to logic 1, the P transistor on

the slave line is turned on during the time delay t

d(edge)

and

then both lines return to their Idle states.

This active pull-up feature ensures fast LOW-to-HIGH

transitions; it is able to deliver more than 1 mA up to an

output voltage of 0.9VCCon a 80 pF load. Atthe end of the

active pull-up pulse, the output voltage only depends on

the internal pull-up resistor, and on the load current

(see Fig.4).

The maximum frequency on these lines is 1 MHz.

FCE661

12

(mA)

8

I

o

V

(V)

6

o

4

handbook, halfpage

(1)

(2)

Inactive state

After power-on reset, the circuit enters the inactive state.

A minimum number of circuits are active while waiting for

the microcontroller to start a session.

• All card contacts are inactive (approximately 200 Ω

to GND)

• I/OUC, AUX1UC and AUX2UC are high impedance

(10 kΩ pull-up resistor connected to VDD)

• Voltage generators are stopped

• XTAL oscillator is running

• Voltage supervisor is active.

Activation sequence

After power-on and, after the internal pulse width delay,

the microcontroller may check the presence of the card

withthe signal OFF(OFF = HIGHwhile CMDVCC isHIGH

means that the card is present; OFF = LOW while

CMDVCC is HIGH means that no card is present).

If the card is in the reader (which is the case if PRES or

PRESis true), the microcontrollermay start a cardsession

by pulling CMDVCC LOW.

The following sequence then occurs (see Fig.5):

• CMDVCC is pulled LOW (t0)

• The voltage doubler is started (t1~t0)

• VCC rises from 0 to 5 or 3V with a controlled slope

(t2=t1+1⁄23T) (I/O, AUX1 and AUX2 follow VCC with a

slight delay); T is 64 times the period of the internal

oscillator, approximately 25µs

• I/O, AUX1 and AUX2 are enabled (t3=t1+ 4T)

• CLK is applied to the C3 contact (t4)

• RST is enabled (t5=t1+ 7T).

2

0

0

(1) Current.

(2) Voltage.

20 40

t (ns)

4

0

60

Fig.4 I/O, AUX1 and AUX2 output voltage and

current as a function of time during a

LOW-to-HIGH transition.

2000 Feb 29 8

The clock may be applied to the card in the following way:

Set RSTIN HIGH before setting CMDVCC LOW, and

reset it LOW between t3and t5; CLK will start at this

moment. RST will remain LOW until t5, where RST is

enabledto be thecopy of RSTIN. After t5,RSTIN has no

further action on CLK. This is to allow a precise count of

CLK pulses before toggling RST.

If this feature is not needed, then CMDVCC may be set

LOW with RSTIN LOW. In this case, CLK will start at t3,

and after t5, RSTIN may be set HIGH in order to get the

Answer To Request (ATR) from the card.

Loading...

Loading...