Philips tda1310 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

TDA1310A

Stereo Continuous Calibration DAC

(CC-DAC)

Preliminary specification

Supersedes data of TDA1310; TDA1310T July 1993

File under Integrated Circuits, IC01

Philips Semiconductors

May 1994

Philips Semiconductors Preliminary specification

Stereo Continuous Calibration DAC

(CC-DAC)

FEATURES

• Space saving package DIL8 or SO8

• Low power consumption

• Wide dynamic range (16-bit resolution)

• Continuous Calibration (CC) concept

• Easy application:

– Single 3 to 5 V supply rail

– Output current and bias current are proportional to

the supply voltage

• Fast settling time permits 2×, 4× and 8× oversampling

(serial input) or double speed operation at 4×

oversampling

• Internal bias current ensures maximum dynamic range

• Wide operating temperature range (-40 t +85 °C)

• Compatible with most current Japanese input formats:

– Time multiplexed

– Two’s complement

– TTL

• No zero-crossing distortion.

TDA1310A

GENERAL DESCRIPTION

The TDA1310A is a device of a new generation of

Digital-to-Analog Converters (DACs) which embodies the

innovative technique of Continuous Calibration. The

largest bit-currents are repeatedly generated by one single

current reference source. This duplication is based upon

an internal charge storage principle having an accuracy

insensitive to ageing, temperature and process variations.

The TDA1310A is fabricated in a 1.0 µm CMOS process

and features an extremely low power dissipation, small

package size and easy application. Furthermore, the

accuracy of the intrinsic high coarse-current combined

with the implemented symmetrical offset decoding method

precludes zero-crossing distortion and ensures high

quality audio reproduction. Therefore, the CC-DAC is

eminently suitable for use in (portable) digital audio

equipment.

ORDERING INFORMATION

TYPE NUMBER

PINS PIN POSITION MATERIAL CODE

TDA1310A 8 DIL8 plastic SOT97DE

TDA1310AT 8 SO8 plastic SOT96AG

PACKAGE

May 1994 2

Philips Semiconductors Preliminary specification

Stereo Continuous Calibration DAC

TDA1310A

(CC-DAC)

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

I

DD

I

FS

(THD+N)/S total harmonic distortion

S/N signal-to-noise ratio at

t

CS

BR input bit rate at data input −− 18.4 Mbits/s

f

clk

TC

FS

T

amb

P

tot

supply voltage 3 5.0 5.5 V

supply current VDD= 5 V at code 0000H − 3.0 4.0 mA

full scale output current VDD= 5 V 0.9 1.0 1.1 mA

V

=3V − 0.6 − mA

DD

at 0 dB signal level −−65 −61 dB

plus noise-to-signal ratio

− 0.05 0.08 %

at −60 dB signal level −−30 −24 dB

− 36%

at −60 dB signal level;

A-weighted

at −60 dB signal level;

−−33 − dB

− 2.2 − %

− 1.7 − %

A-weighted;

R3=R4=11kΩ;

(see Fig.1); I

=2mA

FS

A-weighted at code 0000H 86 92 − dB

bipolar zero

A-weighted; I

= 2 mA;

FS

− 95 − dB

R3=R4=11kΩ; see Fig.1

current settling time to

− 0.2 −µs

±1 LSB

clock frequency at clock

−− 18.4 MHz

input BCK

full scale temperature

−±400 × 10−6−

coefficient at analog

outputs (IOL; IOR)

operating ambient

−40 − +85 °C

temperature

total power dissipation VDD= 5 V at code 0000H − 15 20 mW

= 3 V at code 0000H − 6.0 − mW

V

DD

May 1994 3

May 1994 4

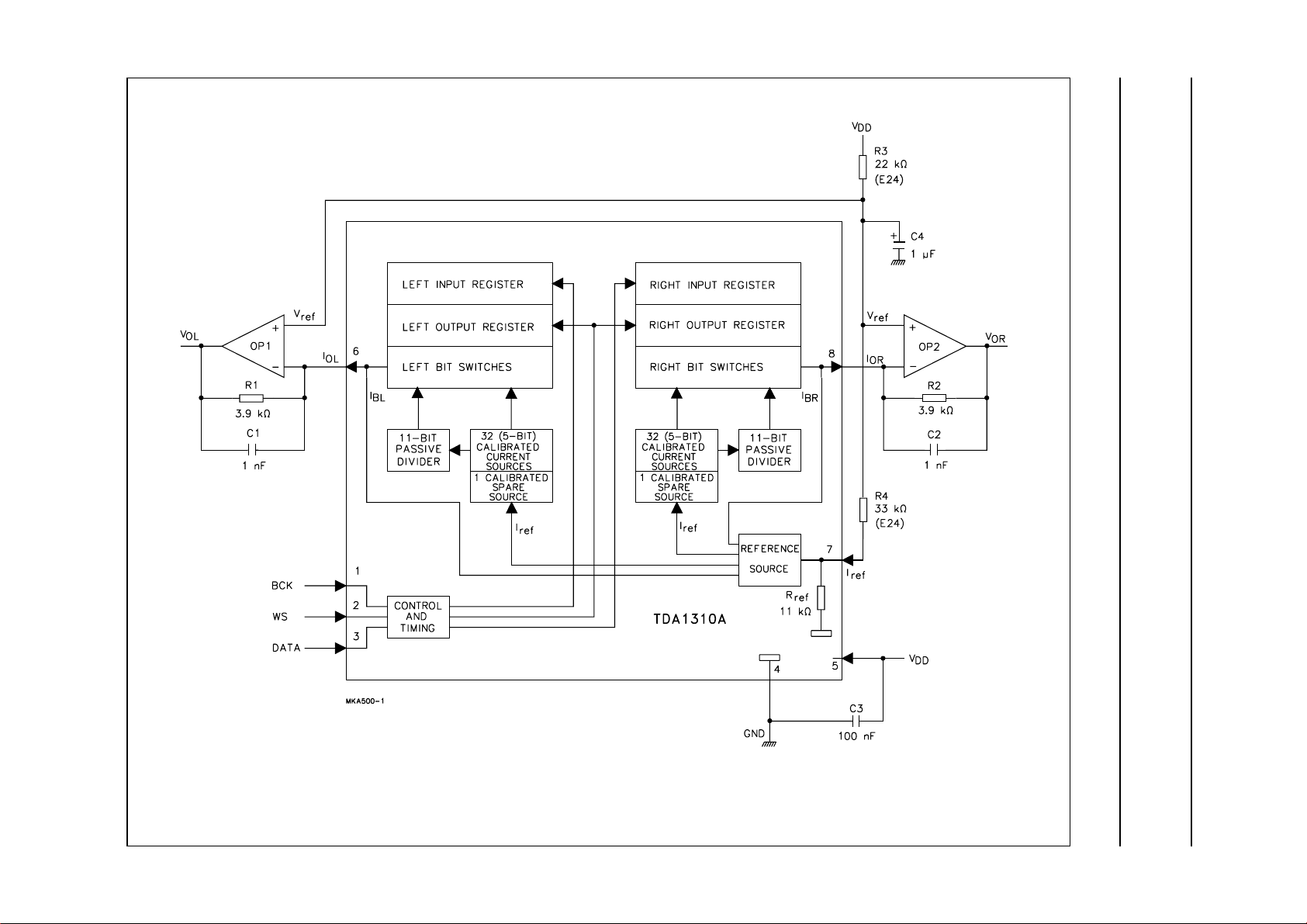

BLOCK DIAGRAM

(CC-DAC)

Philips Semiconductors Preliminary specification

Stereo Continuous Calibration DAC

Fig.1 Block diagram.

TDA1310A

Philips Semiconductors Preliminary specification

Stereo Continuous Calibration DAC

(CC-DAC)

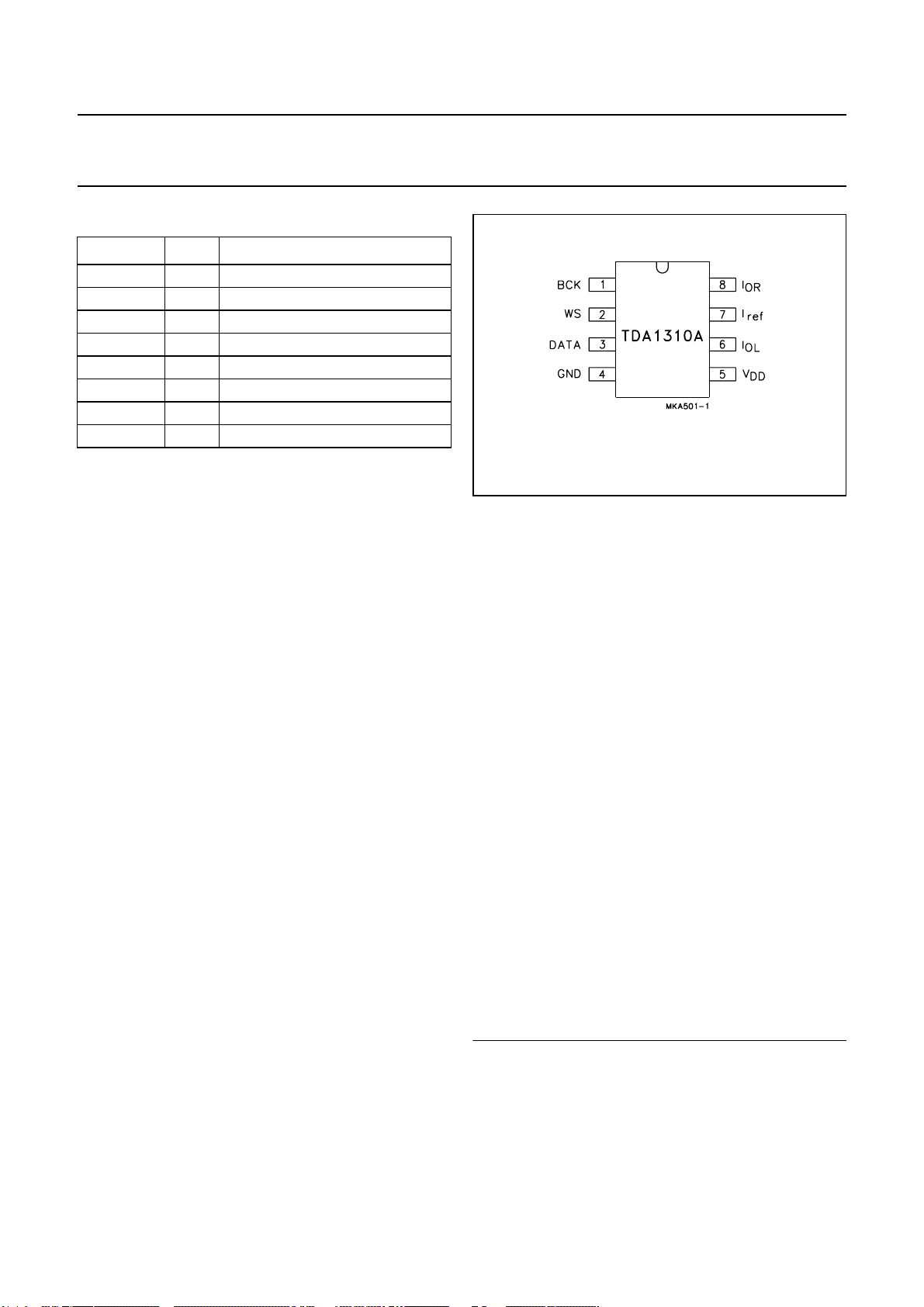

PINNING

SYMBOL PIN DESCRIPTION

BCK 1 bit clock input

WS 2 word select input

DATA 3 data input

GND 4 ground

V

DD

I

OL

I

ref

I

OR

FUNCTIONAL DESCRIPTION

The basic operation of the continuous calibration DAC is

illustrated in Fig.3. The figure shows the calibration and

operation cycle. During calibration of the MOS current

source (Fig.3a) transistor M1 is connected as a diode by

applying a reference current. The voltage Vgs on the

intrinsic gate-source capacitance Cgs of M1 is then

determined by the transistor characteristics. After

calibration of the drain current to the reference value I

the switch S1 is opened and S2 is switched to the other

position (Fig.3b). The gate-to-source voltage Vgs of M1 is

not changed because the charge on Cgs is preserved.

Therefore, the drain current of M1 will still be equal to I

and this exact duplicate of I

terminal.

The 32 current sources and the spare current source of the

TDA1310A are continuously calibrated (see Fig.1). The

spare current source is included to allow continuous

converter operation. The output of one calibrated source is

connected to an 11-bit binary current divider consisting of

2048 transistors. A symmetrical offset decoding principle

is incorporated and arranges the bit switching in such a

way that the zero-crossing is performed only by switching

the LSB currents.

5 supply voltage

6 left channel output

7 reference input

8 right channel output

is now available at the OUT

ref

ref

ref

TDA1310A

Fig.2 Pin configuration.

An internal bias current I

output current IFS in order to achieve the maximum

dynamic range at the outputs OP1 and OP2 in Fig.1.

The reference input current I

current IFS which is a sink current and with gain G

I

which is a source current

bias

,

The current I

is proportional to VDD so the IFS and the I

ref

will be proportional to VDD as well

are constant.

The reference voltage V

maximum dynamic range is achieved over the entire

power supply voltage range.

The tolerance of the reference input current in Fig.1

depends on the tolerance of the resistors R3, R4

ref

(3)

.

and R

is added to the full scale

bias

controls with gain GFS, the

ref

(1)

.

(2)

because GFS and G

in Fig.1 is2⁄3VDD. In this way

ref

bias

the

bias

bias

The TDA1310A (CC-DAC) accepts serial input data

formats of 16-bit word length. Left and right data words are

time multiplexed. The most significant bit (bit 1) must

always be first. The input data format is shown in

Figs 4 and 5.

With a HIGH level on the word select input (WS), data is

placed in the left input register, with a LOW level on the

WS input, data is placed in the right input register

(see Fig.1). The data in the input registers are

simultaneously latched in the output registers which

control the bit switches.

May 1994 5

(1) IFS=GFSxI

(2)

(3)

V

------------V

∆I

I

DD1

==

---------I

DD2

refIref

and I

ref

bias=GbiasxIref

I

FS1

FS2

bias1

------------- I

bias2

V

–=

------------------------------------------------------------------------------------------------R3 ∆R3 R4 ∆R4 R

+++++

DD

ref

∆R

ref

Loading...

Loading...