Philips SAA7335GP-M0, SAA7335GP-M1, SAA7335HL-M1A, SAA7335HL-M2 Datasheet

DATA SH EET

Preliminary specification

File under Integrated Circuits, IC01

1997 Aug 11

INTEGRATED CIRCUITS

SAA7335

DSP for CD and DVD-ROM

systems

1997 Aug 11 2

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

FEATURES

• Compatibility with CD-I, CD-ROM, MPEG-video

DVD-ROM and DVD-video applications

• Designed for very high playback speeds

• Typical CD-ROM operation up to n = 12, DVD-ROM to

n = 1.9, maximum rates (tbf)

• Matched filtering, quad-pass error correction

(C1-C2-C1-C2), overspeed audio playback function

included (up to 3 kbytes buffer)

• Lock-to-disc playback, Constant Angular Velocity

(CAV), pseudo-Constant Linear Velocity (CLV) and CLV

motor control loops

• Interface to 32 kbytes SRAM for DVD error correction

and de-interleave

• Sub-code/ header processing for DVD and CD formats

• Programmable HF equalizer

• In DVD mode it is still compatible with Philips block

decoders

• Sub-CPU interface can be parallel or fast I

2

C-bus

• On-chip clock multiplier.

GENERAL DESCRIPTION

This device is a high-end combined Compact Disc (CD)

and Digital Versatile Disc (DVD) compatible decoding

device. The device operates with an external 32 kbytes

S-RAM memory for de-interleaving operations. The device

provides quad-pass error correction for CD-ROM

applications (C1-C2-C1-C2) and operates in lock-to-disk,

CAV, pseudo CLV and CLV modes.

In DVD modes double-pass C1-C2 error correction is used

which is capable of correcting up to 5 C1 frame errors and

16 C2 frame errors.

The SAA7335 contains all the functions required to

decode an EFM or EFM+ HF signal directly from the laser

pre-amplifier, including analog front-end, PLL data

recovery, demodulation and error correction. The spindle

motor interface provides both motor control signals from

the demodulator and, in addition, contains a tachometer

loop that accepts tachometer pulses from the motor unit.

The SAA7335 has two independent microcontroller

interfaces. The first is a serial I

2

C-bus and the second is a

standard 8-bit multiplexed parallel interface. Both of these

interfaces provide access to a total of 32 × 8-bit registers

for control and status.

This data sheet contains an descriptive overview of the

device together with electrical and timing characteristics.

For a detailed description of the device refer to the user

guide

“SAU/UM96018”

.

Supply of this CD/DVD IC does not convey an implied

license under any patent right to use this IC in any CD or

DVD application.

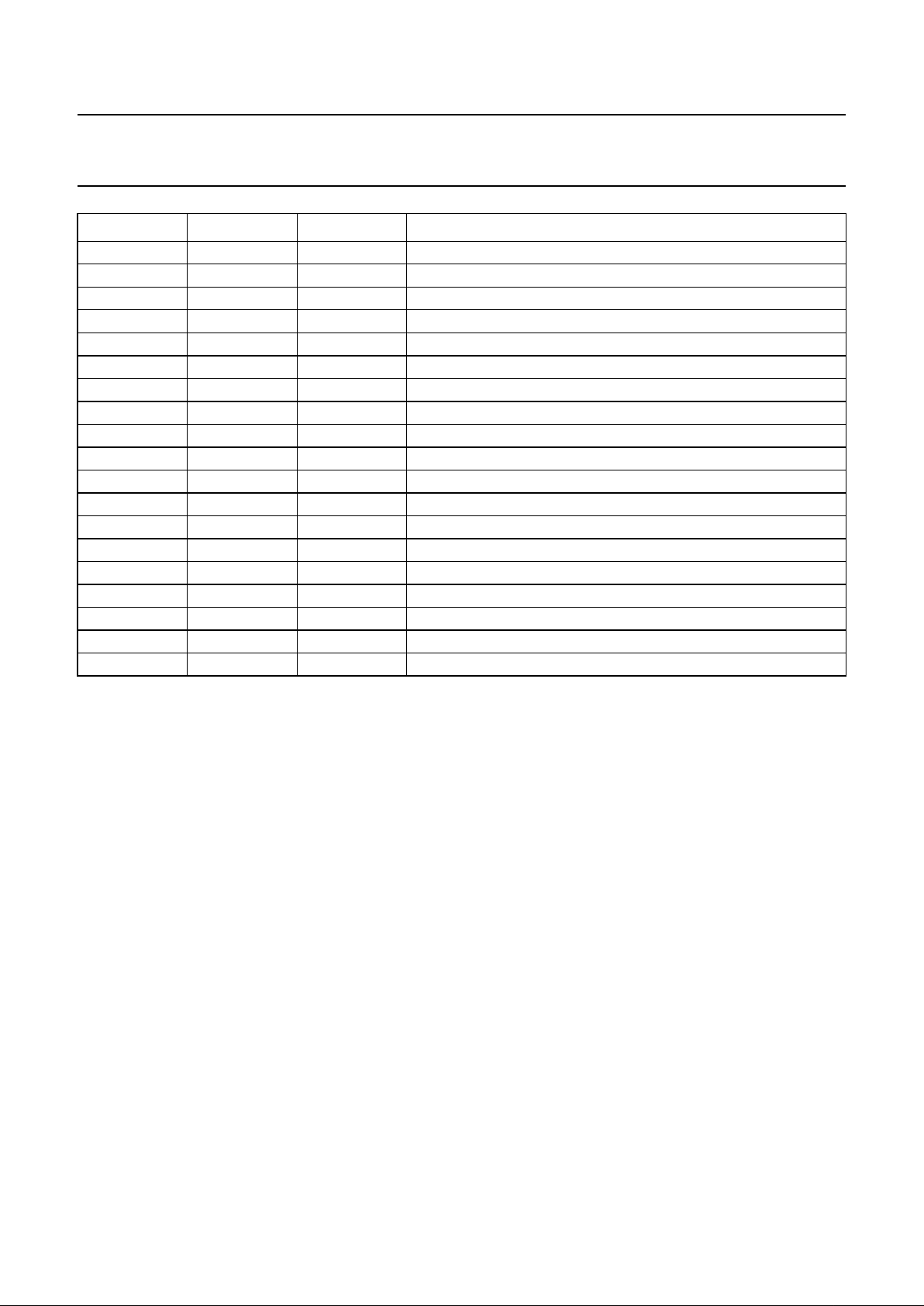

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DDD

digital supply voltage 4.5 5.0 5.5 V

I

DDD

digital supply current − 70 300 mA

V

DDA

analog supply voltage 4.5 5.0 5.5 V

I

DDA

analog supply current − 70 300 mA

f

xtal

crystal input frequency 4 25 tbf MHz

T

amb

operating ambient temperature −20 − +70 °C

T

stg

storage temperature −55 − +125 °C

1997 Aug 11 3

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

ORDERING INFORMATION

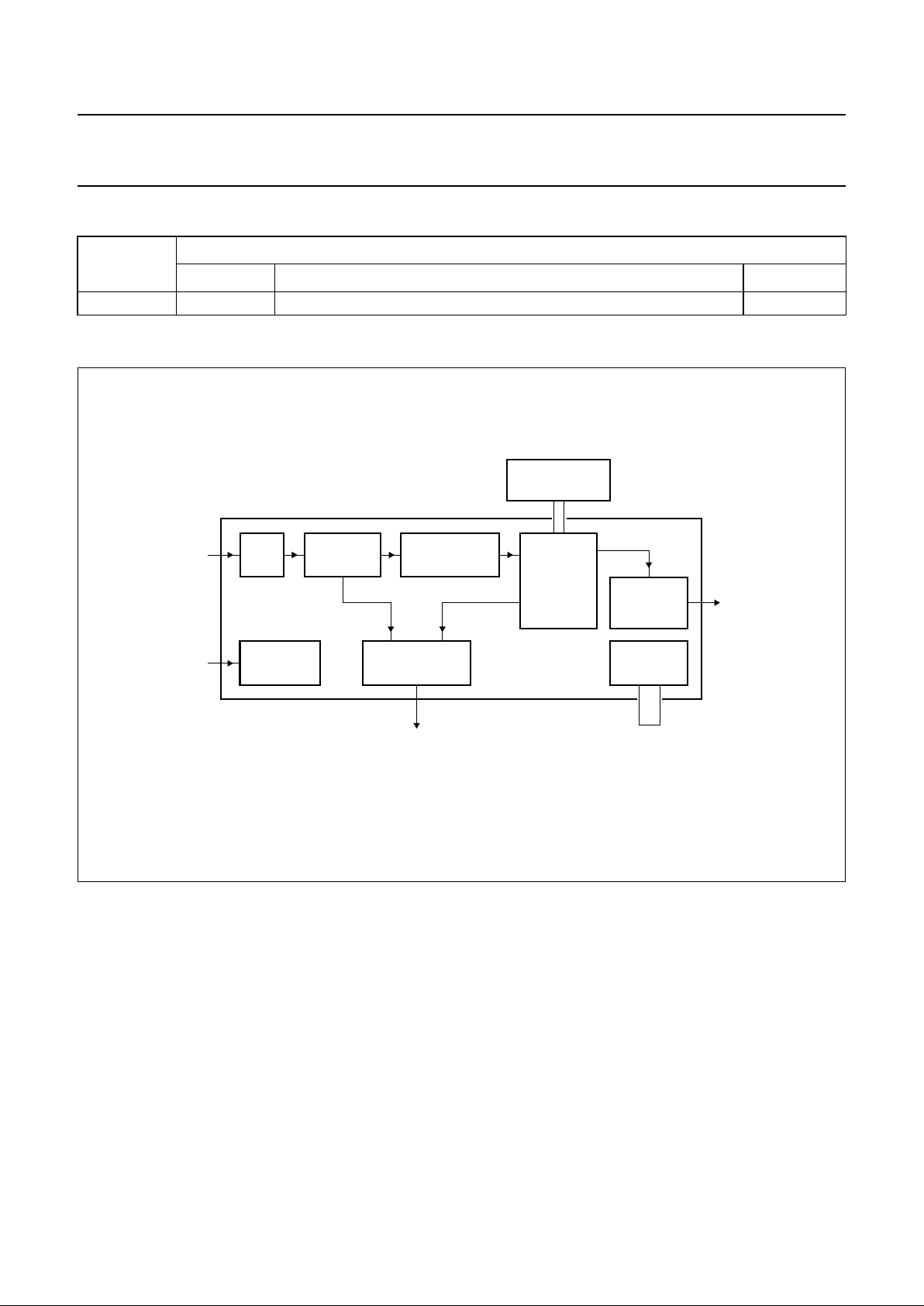

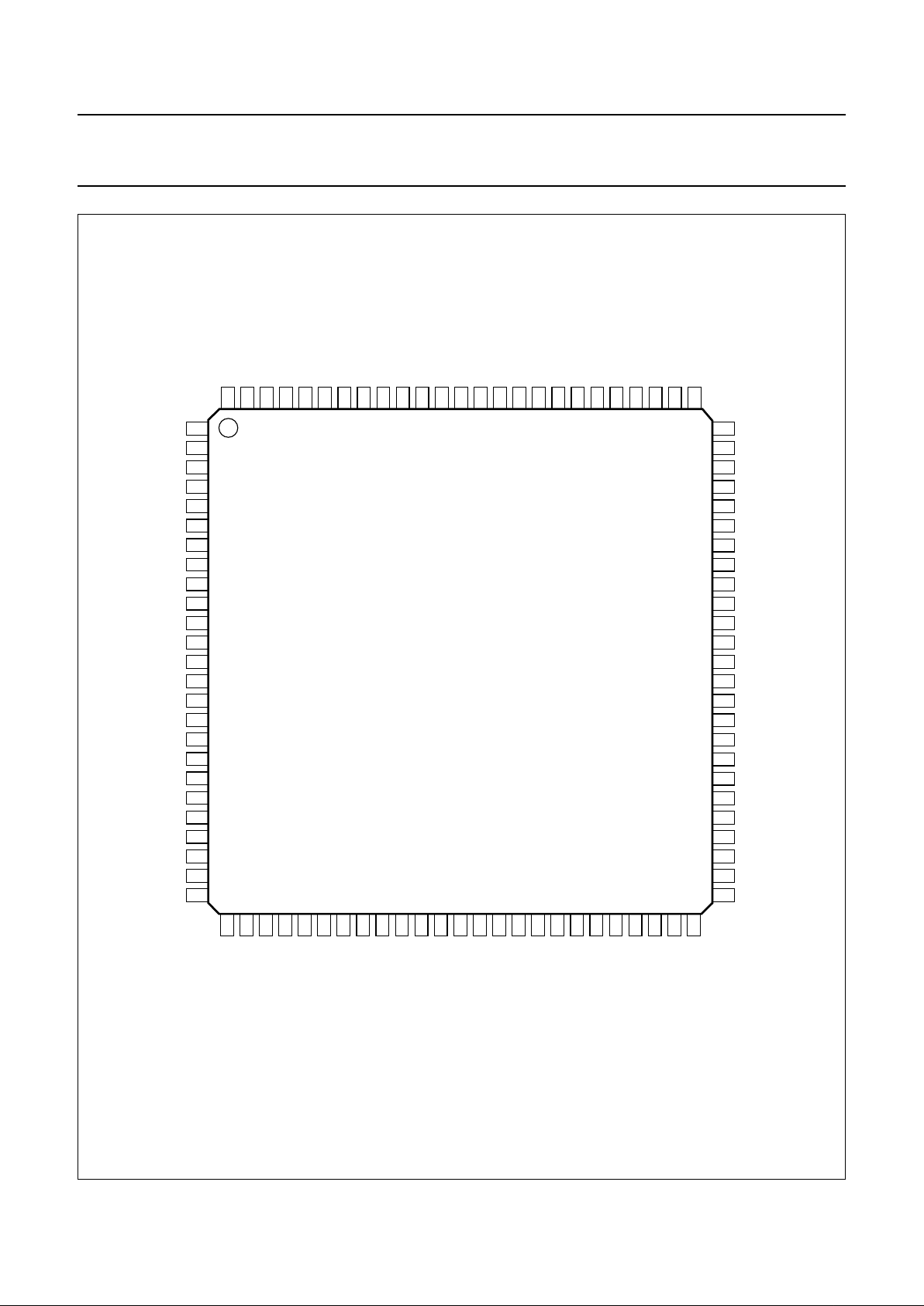

BLOCK DIAGRAM

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

SAA7335GP LQFP100 plastic low profile quad flat package; 100 leads; body 14 × 14 × 1.4 mm SOT407-1

Fig.1 Simplified block diagram.

handbook, full pagewidth

MGK242

DEMODULATOR

EFM/EFM+

PLL BIT

DETECTOR

SRAM

32 KBYTES

SPINDLE

MOTOR CONTROL

motor control

SAA7335

CLOCK

GENERATOR

SUB-CPU

INTERFACE

ADCHF input

clock input

DECODER

block

decoder

output

I2S-BUS

OUTPUT

INTERFACE

1997 Aug 11 4

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

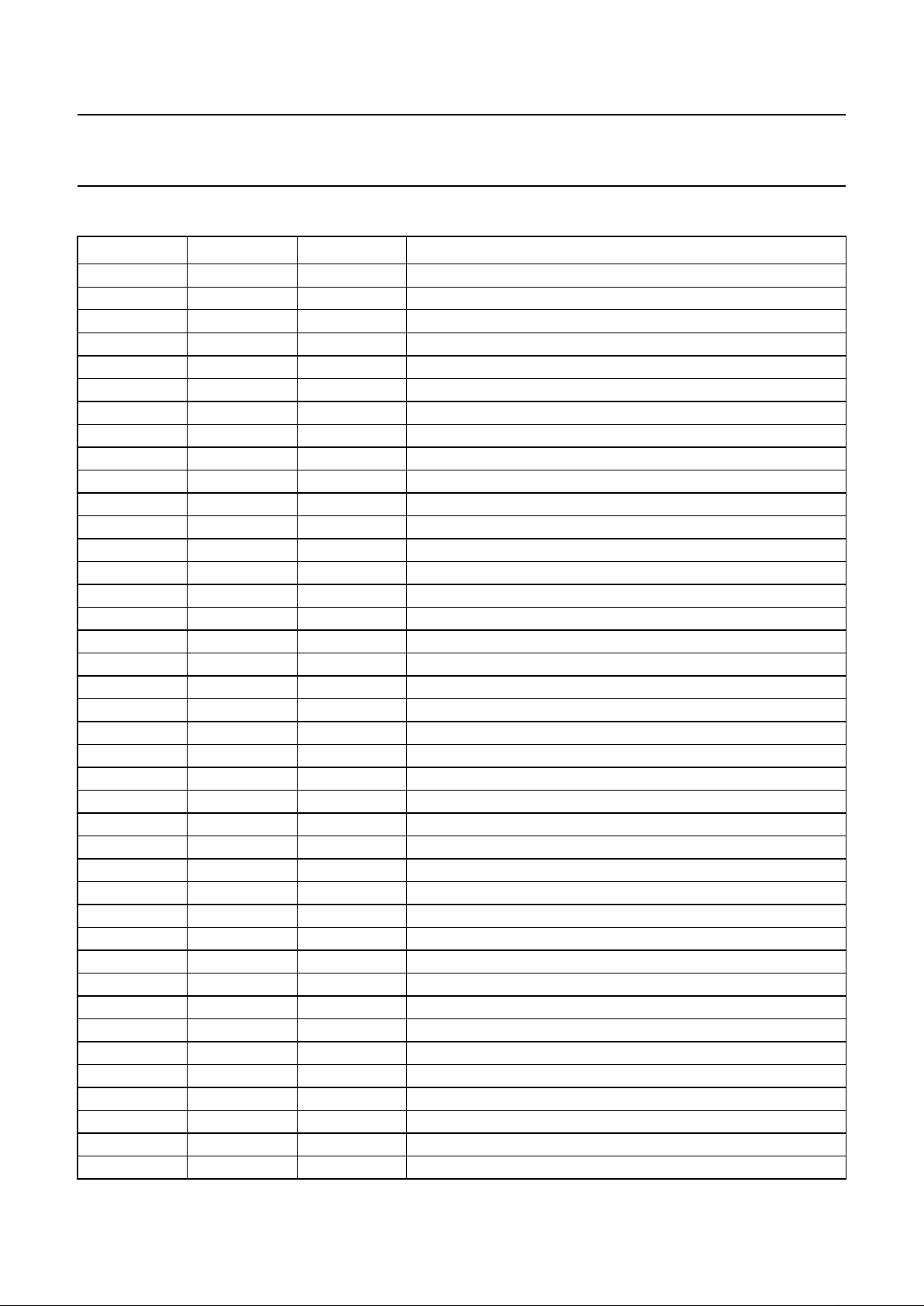

PINNING

SYMBOL PIN TYPE DESCRIPTION

V

SSA1

1 supply analog ground 1

I

ref

2 I analog current reference input for ADC

REFLo 3 I analog low reference input for ADC

REFHi 4 I analog high reference input for ADC

VREF 5 I analog negative input

HFIN 6 I analog positive input

V

SSA2

7 supply analog ground 2

AGCOUT 8 O analog test pin output

V

DDA2

9 supply analog supply voltage 2

V

DDD1

10 supply digital supply voltage 1

V

SSD1

11 supply digital ground 1

OTD 12 I off track detect input

MOTO1 13 O 3-state motor control output

n.c. 14 − not connected, reserved

MOTO2/T3 15 I/O motor control output/tachometer 3 input

n.c. 16 − not connected, reserved

T1 17 I tachometer 1 input

T2 18 I tachometer 2 input

V

DDD2

19 supply digital supply voltage 2

V

SSD2

20 supply digital ground 2

TEST1 21 I test input 1

TEST2 22 I test input 2

POR 23 I power-on reset input

MUXSWICH 24 I use clock multiplier input

n.c. 25 − not connected, reserved

CL1 26 O divided clock output

BCAIN 27 I BCA input

SDA 28 I/O sub-CPU I

2

C-bus serial data input/output

SCL 29 I sub-CPU I

2

C-bus serial clock input

INT 30 O sub-CPU interrupt output (open-drain)

V

DDD3

31 supply digital supply voltage 3

V

SSD3

32 supply digital ground 3

da7 33 I/O sub-CPU data bus bit 7 input/output (parallel)

da6 34 I/O sub-CPU data bus bit 6 input/output (parallel)

da5 35 I/O sub-CPU data bus bit 5 input/output (parallel)

n.c. 36 − not connected, reserved

da4 37 I/O sub-CPU data bus bit 4 input/output (parallel)

n.c. 38 − not connected, reserved

da3 39 I/O sub-CPU data bus bit 3 input/output (parallel)

da2 40 I/O sub-CPU data bus bit 2 input/output (parallel)

1997 Aug 11 5

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

da1 41 I/O sub-CPU data bus bit 1 input/output (parallel)

n.c. 42 − not connected, reserved

da0 43 I/O sub-CPU data bus bit 0 input/output (parallel)

V

DDD4

44 supply digital supply voltage 4

V

SSD4

45 supply digital ground 4

WRi 46 I sub-CPU write enable input (active LOW)

RDi 47 I sub-CPU read enable input (active LOW)

ALE 48 I sub-CPU address latch enable input

CSi 49 I sub-CPU chip select input (active HIGH)

STOPCLOCK 50 O stop clock output

n.c. 51 − not connected, reserved

V4 52 O serial subcode output (for CD)

EBUOUT 53 O digital audio output

SYNC 54 O I

2

S-bus sector sync output

FLAG 55 O I

2

S-bus correction flag output

DATA 56 O I

2

S-bus serial data output

BCLK 57 I/O I

2

S-bus bit serial clock input/output

WCLK 58 I/O I

2

S-bus word clock input/output

V

DDD5

59 supply digital supply voltage 5

V

SSD5

60 supply digital ground 5

RAMRW 61 O RAM read/write control output

n.c. 62 − not connected, reserved

RAMDA7 63 I/O RAM data bus bit 7 input/output

RAMDA6 64 I/O RAM data bus bit 6 input/output

RAMDA5 65 I/O RAM data bus bit 5 input/output

RAMDA4 66 I/O RAM data bus bit 4 input/output

RAMDA3 67 I/O RAM data bus bit 3 input/output

RAMDA2 68 I/O RAM data bus bit 2 input/output

n.c. 69 − not connected, reserved

RAMDA1 70 I/O RAM data bus bit 1 input/output

RAMDA0 71 I/O RAM data bus bit 0 input/output

V

DDD6

72 supply digital supply voltage 6

V

SSD6

73 supply digital ground 6

RAMAD0 74 O RAM address bit 0 output

RAMAD1 75 O RAM address bit 1 output

RAMAD2 76 O RAM address bit 2 output

RAMAD3 77 O RAM address bit 3 output

RAMAD4 78 O RAM address bit 4 output

RAMAD5 79 O RAM address bit 5 output

RAMAD6 80 O RAM address bit 6 output

V

DDD7

81 supply digital supply voltage 7

SYMBOL PIN TYPE DESCRIPTION

1997 Aug 11 6

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

V

SSD7

82 supply digital ground 7

RAMAD7 83 O RAM address bit 7 output

RAMAD8 84 O RAM address bit 8 output

RAMAD9 85 O RAM address bit 9 output

n.c. 86 − not connected, reserved

RAMAD10 87 O RAM address bit 10 output

RAMAD11 88 O RAM address bit 11 output

RAMAD12 89 O RAM address bit 12 output

RAMAD13 90 O RAM address bit 13 output

RAMAD14 91 O RAM address bit 14 output

V

DDD8

92 supply digital supply voltage 8

V

SSD8

93 supply digital ground 8

CRIN 94 I analog crystal input

CROUT 95 O analog crystal output

CFLG 96 O correction statistics output

MEAS1 97 O front-end telemetry output

V

DDD9

98 supply digital supply voltage 9

V

SSD9

99 supply digital ground 9

V

DDA1

100 supply analog supply voltage 1

SYMBOL PIN TYPE DESCRIPTION

1997 Aug 11 7

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

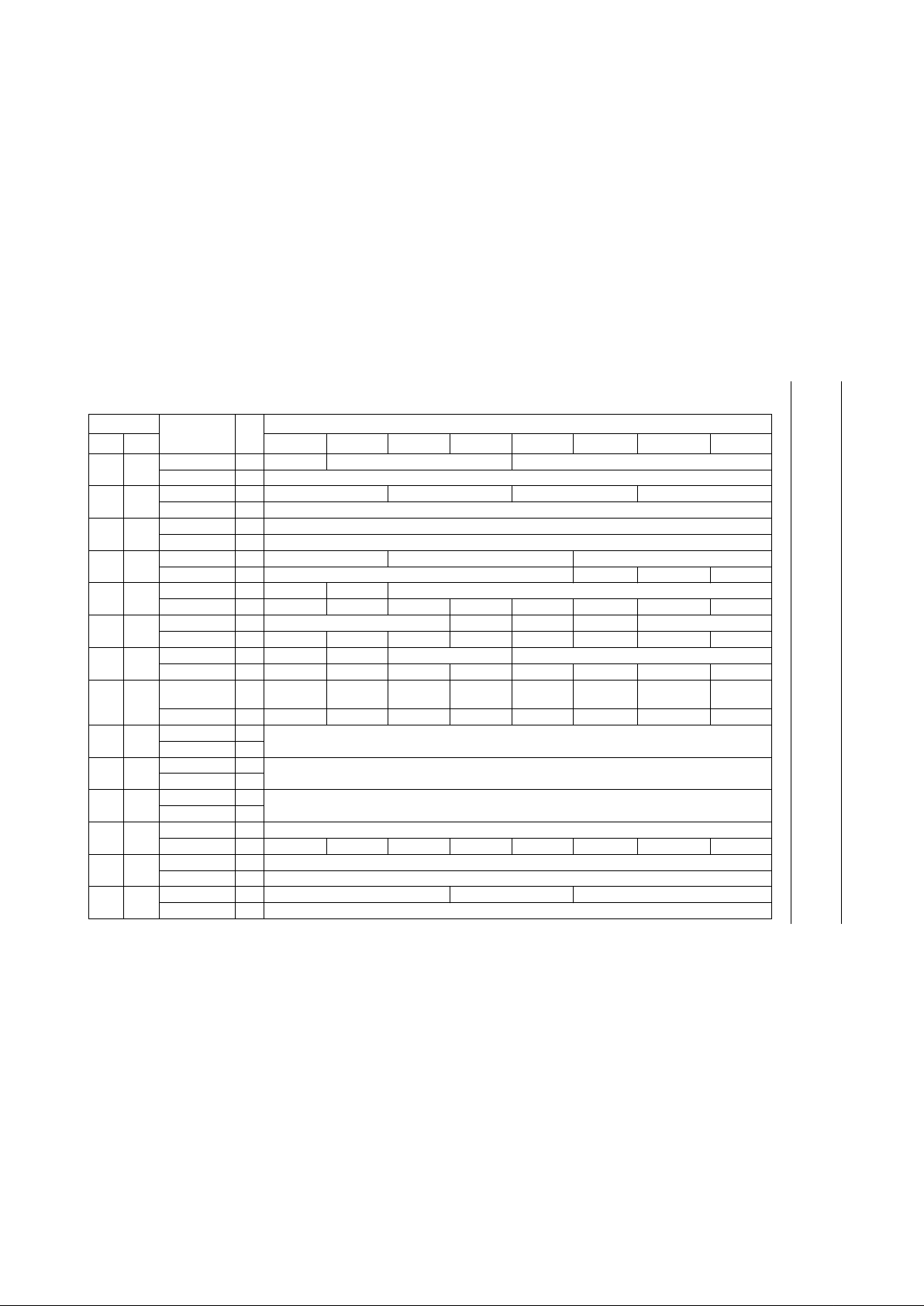

Fig.2 Pin configuration.

handbook, full pagewidth

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

8079787776

RAMAD1

RAMAD0

V

SSD6

V

DDD6

RAMDA0

RAMDA1

n.c.

RAMDA2

RAMDA3

RAMDA4

RAMDA5

RAMDA6

RAMDA7

n.c.

RAMRW

V

SSD5

V

DDD5

WCLK

BCLK

DATA

FLAG

SYNC

EBUOUT

V4

n.c.

MGK241

V

SSA1

I

ref

REFLo

REFHi

VREF

HFIN

V

SSA2

AGCOUT

V

DDA2

V

DDD1

V

SSD1

OTD

MOTO1

n.c.

MOTO2/T3

n.c.

T1

T2

V

DDD2

V

SSD2

TEST1

TEST2

POR

MUXSWICH

n.c.

RAMAD6

RAMAD5

RAMAD4

RAMAD3

RAMAD2

V

DDA1VSSD9VDDD9

MEAS1

CFLG

CROUT

CRIN

V

SSD8VDDD8

RAMAD14

RAMAD13

RAMAD12

RAMAD11

RAMAD10

n.c.

RAMAD9

RAMAD8

RAMAD7

V

SSD7VDDD7

V

DDD3

V

SSD3

da7

da6

da5

n.c.

da4

n.c.

da3

da2

da1

n.c.

da0

V

DDD4

V

SSD4

WRi

RDi

ALE

CSi

STOPCLOCK

CL1

BCAIN

SDA

SCL

INT

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

100

99989796959493929190898887868584838281

31323334353637383940414243444546474849

50

SAA7335

1997 Aug 11 8

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

FUNCTIONAL DESCRIPTION

Analog front-end

This block converts the HF input to the digital domain using

an 8-bit ADC proceeded by an AGC circuit to obtain the

optimum performance from the convertor. This block is

clocked by ADCCLK which is set by the external crystal

frequency plus a flexible clock multiplier and divider block.

PLL and bit detector

This subsystem recovers the data from the channel

stream. The block corrects asymmetry, performs noise

filtering and equalisation and finally recovers the bit clock

and data from the channel using a digital PLL.

The equalizer and the data slicer are programmable.

Digital logic

All the digital system logic is clocked from the master ADC

clock (ADCCLK) described above.

Advanced bit detector

The advanced bit detector offers improved data recovery

for multi-layer discs and contains two extra detection

circuits to increase the margins in the bit recovery block:

1. Adaptive slicer: adds a second stage slicer with higher

bandwidth

2. Run length 2 push-back: all T2 run lengths are pushed

back to T3, thereby automatically determining the

erroneous edge and shifting the transitions on that

edge.

Demodulator

F

RAME SYNC PROTECTION CD MODE

This circuit detects the frame synchronization signals.

Two synchronization counters are used in the SAA7335:

1. The coincidence counter: this is used to detect the

coincidence of successive syncs. It generates a sync

coincidence signal if 2 syncs are 588 ±1 EFM clocks

apart.

2. The main counter: this is used to partition the EFM

signal into 17-bit words. This counter is reset when:

a) A sync coincidence is generated

b) A sync is found within ±6 EFM clocks of its

expected position.

The sync coincidence signal is also used to generate the

lock signal which will go active HIGH when 1 sync

coincidence is found. It will reset to LOW when, during

61 consecutive frames, no sync coincidence is found.

FRAME SYNC PROTECTION DVD MODE

This circuit detects the frame synchronization signals.

Two synchronization counters are used in the SAA7335:

1. The coincidence counter: this is used to detect the

coincidence of successive syncs. It generates a sync

coincidence signal if 2 syncs are 1488 ±3 EFM+

clocks apart.

2. The main counter: this is used to partition the EFM+

signal into 16-bit words. This counter is reset when:

a) A sync coincidence is generated

b) A sync is found within ±10 EFM+ clocks of its

expected position.

The sync coincidence signal is also used to generate the

lock signal which will go active HIGH when 1 sync

coincidence is found. It will reset to LOW when, during

61 consecutive frames, no sync coincidence is found.

EFM/EFM+ demodulation

The 14-bit EFM (16-bit EFM+) data and subcode words

are decoded into 8-bit symbols.

1997 Aug 11 9

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

Microcontroller interface

The SAA7335 has two microcontroller interfaces, one

serial I2C-bus and one parallel (8051 microcontroller

compatible).

The two communication modes may be operated at the

same time, the modes are described below:

1. Parallel mode: protocol compatible with 8052

multiplexed bus:

a) da0 to da7 = address/data bus

b) ALE = Address Latch Enable, latches the address

information on the bus

c)

WRi = active LOW write signal for write to

SAA7335

d) RDi = active LOW read signal for read from

SAA7335

e) CSi = active HIGH Chip Select signal (this signal

gates the RDi and WRi signals).

2. I2C-bus mode: I2C-bus protocol where SAA7335

behaves as slave device where:

a) SDA = I2C-bus data

b) SCL = I2C-bus clock

c) I2C-bus slave address (write mode) = 3EH

d) I2C-bus slave address (read mode) = 3FH

e) Maximum data transfer rate = 400 kbits/s.

M

ICROCONTROLLER INTERFACE (I

2

C-BUS MODE)

Bytes are transferred over the interface in single bytes of

which there are two types; write data commands and read

data commands.

The sequence for a write data command (1 data byte) is as

follows:

• Send START condition

• Send address 3EH (write)

• Write command address byte

• Write data byte

• Send STOP condition.

The sequence for a read data command (that reads 1 data

byte) is as follows:

• Send START condition

• Send address 3EH (write)

• Write status address byte

• Send STOP condition

• Send START condition

• Send address 3FH (read)

• Read data byte

• Send STOP condition.

R

EADING AND WRITING DATA TO THE SAA7335

The SAA7335 has 32 × 8-bit configuration and status

registers as shown in Table 1. Not all locations are

currently defined and some remain reserved for future

upgrades. These can be written to or read from via the

microcontroller interface using either the serial or parallel

control bus.

1997 Aug 11 10

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

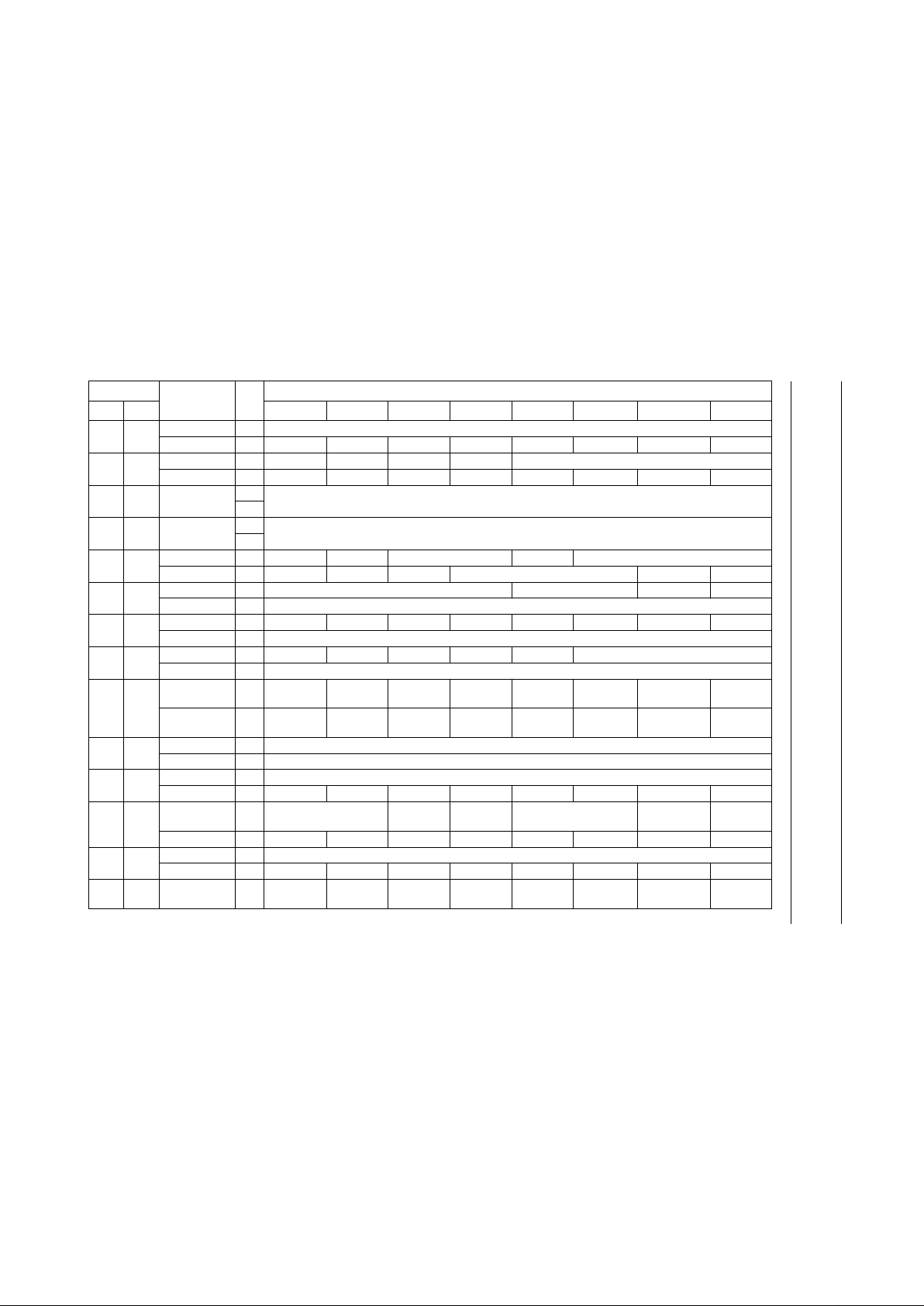

REGISTER MAP

Table 1 SAA7335 microcontroller register map

ADDRESS

NAME R/W

BIT

DEC HEX 7 6 5 4 3 2 1 0

0 0 PLL_LOCK W Lock Oride Pha_Oset PLL_Force_L

PLL_Freq_R R PLL measured frequency (bits 9 to 2)

1 1 PLL_SET W SliceBW Integ_F0 PLLBW_F1 LP_BW_F3

PLL_ASSYM R PLL asymmetry value (8 bits)

2 2 PLL_FREQ W PLL frequency (8 MSBs)

PLL_Jit R jitter value (bits 9 to 2)

3 3 PLL_EQU W PLL frequency (2 LSBs) equalizer tap α 1 equaliser tap α 2

PLL_Lock_In R reserved Long_Symb F_Lock In_Lock

4 4 PLL_F_MEAS W RL3_EN reserved EFM nominal setting (101110)

reserved R −−−−−− − −

5 5 OUTPUT1 W Fmat(3 to 1) WCLK_Op BCLK_Op Fmat (0) SyncSwap (1 and 0)

reserved R −−−−−− − −

6 6 OUTPUT2 W EBU_Valid EBU_On EBU control bits 28, 29 EBU control bits (1 to 4)

reserved R −−−−−− − −

7 7 OUTPUT3 W WCLK_H_

Left

Descr_On Interp_On CD_ROM_

Header_On

Flag_Pin Kill Data On Kill EBU_On CD_ROM_

Scrb_On

reserved R −−−−−− − −

8 8 SEMA1 W general purpose semaphore register

R

9 9 SEMA2 W general purpose semaphore register

R

10 A SEMA3 W general purpose semaphore register

R

11 B INTEN W hardware pin interrupt enable bits (map to status bits)

Status R Fl_S1 Fl_S2 Fl_S3 PLL lock DVD rdy Mot Ov Tacho reserved

12 C MOTOR1 W frequency set point

SLICE1 R slice compensation value

13 D MOTOR2 W G(2 to 0) Ki Kf

EYE_Open R eye opening value

1997 Aug 11 11

Philips Semiconductors Preliminary specification

DSP for CD and DVD-ROM systems

SAA7335

14 E MOTOR3 W FIFO set point

MTR_F R −−−−−− − −

15 F MOTO4 W PWM_PDM OVF_SW SW2 SW1 motor servo control (3 to 0)

reserved R −−−−−− − −

16 10 MTR_INTG_L W motor integrator value (7 to 0)

R

17 11 MTR_INTG_H W motor integrator value (15 to 8)

R

18 12 CLOCKPRE W CL1Div BCLKG_En Div1 (2 to 0) Mux 2 Div2 (2 to 0)

SUB_C_STAT R ready busy CRC_OK err (2 to 0) cor fail reserved

19 13 DECMODE W mode reserved read TOC reserved

SUB_C_DATA R subcode data (7 to 0)

20 14 reserved W −−−−−− − −

SUB_C_End R no meaning (register read used as a signal)

21 15 ANASET W AGC_En gain set gain up gain down AGC_On reserved

FIFOFILL_L R number of C1 frames in FIFO

22 16 VITSET W slice ON AdDet ON FEndAutoS

ON

BCA_STAT R Buff_

Loaded

sync Buff_ORun

23 17 TACHO1 W tachometer multiplier frequency KTacho (7to0)

BCA_DATA R BCA data (7 to 0)

24 18 TACHO2 W tachometer interrupt trip frequency tachometer trip (7 to 0)

reserved R −−−−−− − −

25 19 TACHO3 W servo control source Tacho

FRes

Moto2_T3 Fsam TachoInt_LF reserved

reserved R −−−−−− − −

26 1A BCASET W BCA_Freq (7 to 0)

reserved R −−−−−− − −

27 to311B to1Freserved −−−−−− − −

ADDRESS

NAME R/W

BIT

DEC HEX 7 6 5 4 3 2 1 0

Loading...

Loading...