Philips saa7283 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA7283

Terrestrial Digital Sound Decoder

(TDSD3)

Preliminary specification

File under Integrated Circuits, IC02

1996 Oct 24

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder

(TDSD3)

FEATURES

• Single-chip solution including FM and vision filters,

analog demodulator and audio switching

• Dual standard with automatic selection between PAL

system I and BGH including French NICAM L system)

• Single low-radiation crystal oscillator for improved EMC

• Stereo bitstream audio DACs

• Programmable attenuator for matching levels of NICAM

and FM audio sources at the output of the device

• Full EBU NICAM 728 specification demodulation and

decoding

• Digital Audio Interface conforming with EBU/IEC 958

• Automatic mute function which switches from NICAM to

FM sound when NICAM fails

• Compatible with either single-ended or differential

DQPSK input signals

2

• Microcomputer controlled via I

specification).

APPLICATIONS

• Television receivers

• Video cassette recorders.

GENERAL DESCRIPTION

The SAA7283 is a NICAM receiver solution, developing

the well established high quality Terrestrial Digital Sound

decoder family from Philips Semiconductors.

This innovative IC with analog front-end, offers more

impressive features and flexibility with minimum external

circuitry.

C-bus (up to 400 kHz

SAA7283

The SAA7283 takes, as input, a second IF (intercarrier)

Terrestrial TV PAL signal, and performs all the Differential

Quadrature Phase Shift Keying (DQPSK) demodulation,

digital decoding and digital-to-analog conversion

necessary to produce a complete NICAM receiver on a

single integrated circuit.

The demodulator function includes integrated baseband

filters for pulse shaping and unwanted signal rejection,

automatic gain control, a low jitter integrated VCO, digital

monostable for precise data sampling points and a

multi-standard controller to enable automatic locking to

either a PAL system I or PAL system BGH input signal

(including French NICAM L system).

The decoder function performs the descrambling,

de-interleaving and reformatting operations required to

recover the original data words.

The data words are processed through a stereo digital

filter, digital de-emphasis network, second order noise

shaper and 256 times oversampling Bitstream audio DAC.

The SAA7283 then provides a switching output buffer for

selecting between FM, NICAM and daisy-chain inputs, and

a programmable level attenuation matrix for matching

levels of the FM and NICAM audio sources at the output of

the device. An additional feature is the inclusion of a Digital

Audio Interface (DAI) output IEC 958, which may be

disabled if required.

ORDERING INFORMATION

TYPE

NUMBER

SAA7283ZP SDIP52 plastic shrink dual in-line package; 52 leads (600 mil) SOT247-1

SAA7283GP QFP64 plastic quad flat package; 64 leads (lead length 1.95 mm);

1996 Oct 24 2

NAME DESCRIPTION VERSION

body 14 × 20 × 2.8 mm

PACKAGE

SOT319-2

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DD

I

DD

f

clk

T

amb

supply voltage 4.5 5.0 5.5 V

supply current − 205 − mA

clock frequency − 8.192 − MHz

operating ambient temperature −20 +25 +70 °C

1996 Oct 24 3

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

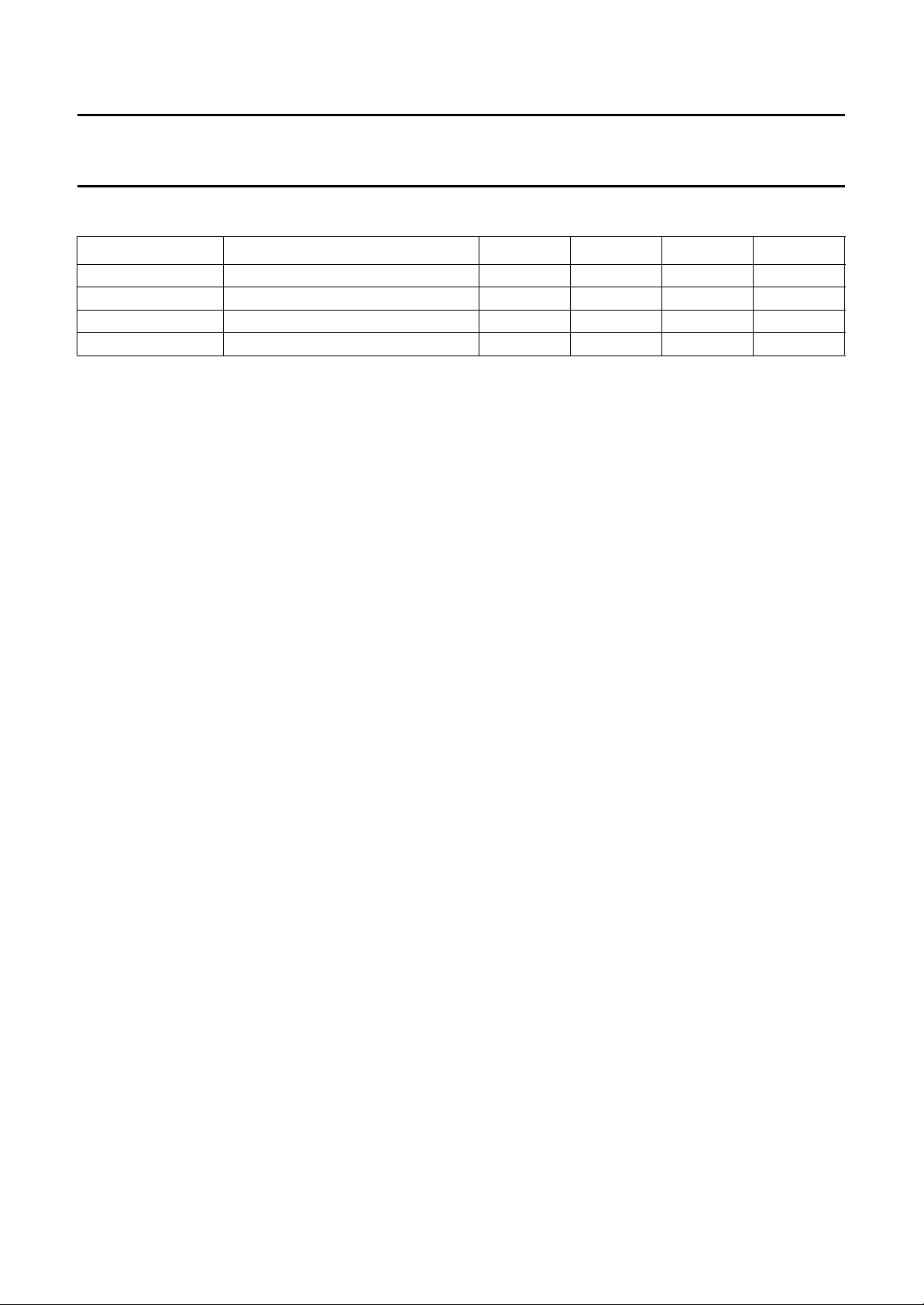

BLOCK DIAGRAM

handbook, full pagewidth

V

DDF1

V

SSF1

COFF

CEYE

V

DDF2

V

SSF2

REMO

REMVE

I

REF

V

ROF

V

RCF

CLKLPF

DATAOUT

DATAIN

XTAL

OSC

V

SSX

SDA

SCL

ADSEL

DQPSK MIXREF

25

23

30

31

38

39

17

16

36

35

37

41

46

45

42

43

44

54

53

55

QUADRATURE MIXERS, BASEBAND FILTERS

CARRIER LOOP

PHASE DETECTOR

AND DATA SLICERS

RECOVERY

CRYSTAL

OSCILLATOR

29 28

AGC GAIN STAGE

COSINE

BITRATE

CLOCK

2

I C

AND

SINE

AGC

CONTROLLER

CARRIER LOOP

QUADRATURE

VCO

NICAM 728 DECODER

AND

DEVICE CONTROLLER

22

SOFF

21

SEYE

34

PKDET

27

VCONT

24

VCLK

47

PCLK

50

RESET

56

PORT2

57

MUTE

14

PORM

15

PORA

DOBM

V

SSDAC

(1) Represents controller bus.

V

DDD

V

SSD

FML

EXTL

V

DDA

V

SSA

V

ROA

V

RCA

SAA7283GP

59

49

48

8

12

13

61

62

7

63

DAI

NOISE SHAPER

(LEFT CHANNEL)

BITSTREAM DAC

(LEFT CHANNEL)

OUTPUT

SWITCHES

AND

BUFFER

(LEFT CHANNEL)

11 4

OPL

DIGITAL FILTER, GAIN,

J17 DE-EMPHASIS

NOISE SHAPER

(RIGHT CHANNEL)

BITSTREAM DAC

(RIGHT CHANNEL)

(1)

OUTPUT

SWITCHES

AND

BUFFER

(RIGHT CHANNEL)

OPR

MGB464

3

FMR

2

EXTR

Fig.1 Block diagram (QFP64).

1996 Oct 24 4

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

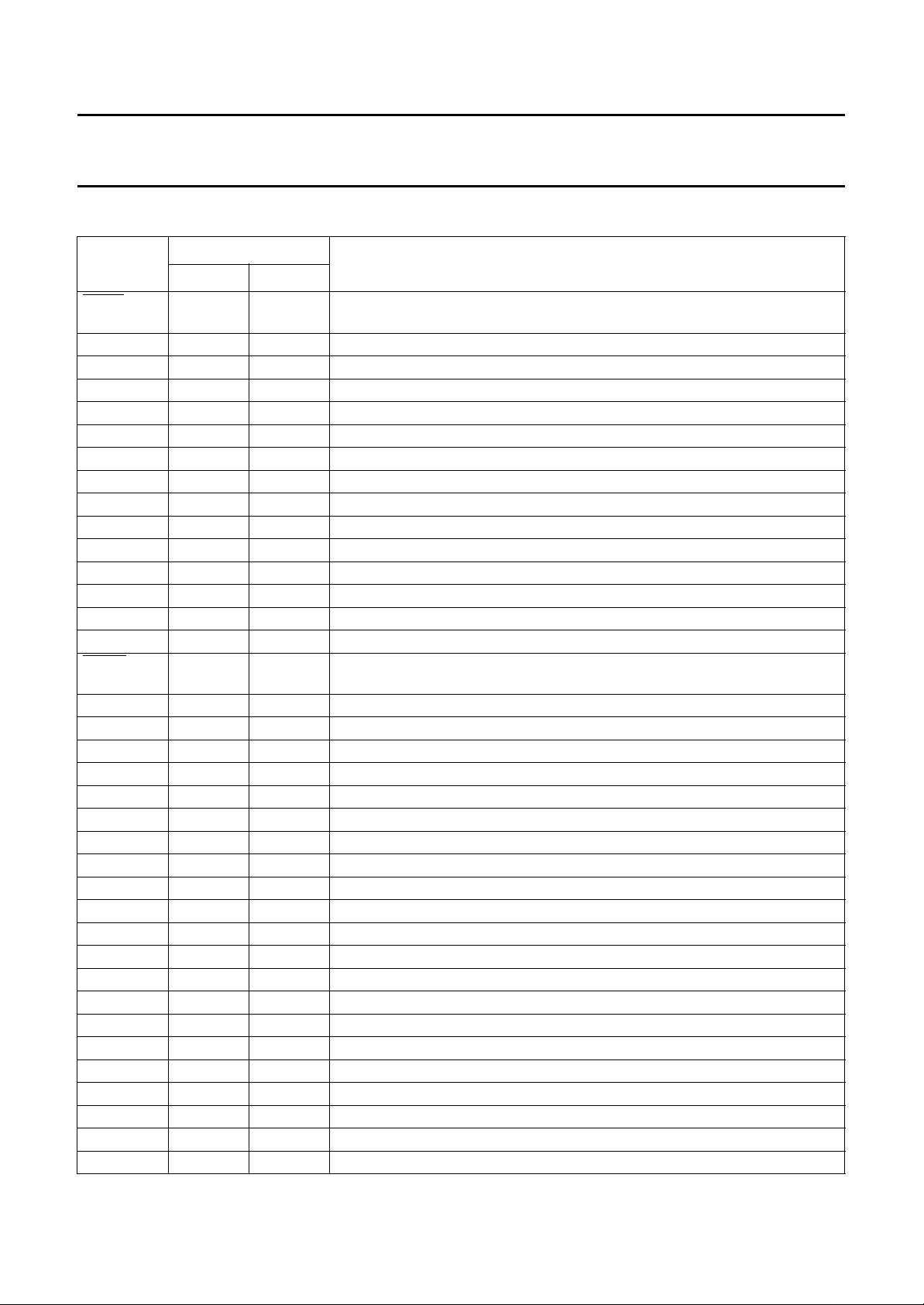

PINNING

SYMBOL

SDIP52 QFP64

(1)

DESCRIPTION

MUTE 1 57 active LOW mute input; function defined by MUTEDEF (control bit in the

I2C-bus register)

PIN

2

DOBM 2 59 digital audio interface output that can be 3-stated via I

V

V

V

DDA

SSA

RCA

3 61 analog supply voltage for the audio channels

4 62 analog ground connection for the audio channels

5 63 internal audio reference voltage buffer (high-impedance node)

C-bus

EXTR 6 2 external analog input to the right audio channel

FMR 7 3 FM sound input to the right audio channel

OPR 8 4 analog output from the right audio channel

n.c. 9 and 10 9 and 10 not connected; left open-circuit in application

V

ROA

V

SSDAC

11 7 internal audio reference voltage buffer output

12 8 quiet ground connection to DACs

n.c. 13 and 14 − not connected; left open-circuit in application

OPL 15 11 analog output from the left audio channel

FML 16 12 FM sound input to the left audio channel

EXTL 17 13 external analog input to the left audio channel

PORM 18 14 active LOW power-on reset mute input; mute cleared by setting silence bit

HIGH in I2C-bus (internal pull-up)

PORA 19 15 power-on reset audio select input (internal pull-up)

REMVE 20 16 carrier loop-filter connection

REMO 21 17 carrier loop-filter output

SEYE 22 21 sine channel eye pattern output for monitoring

SOFF 23 22 sine channel offset compensator capacitor output

V

SSF1

24 23 demodulator ground connection 1

VCLK 25 24 carrier loop VCO clock output for monitoring

V

DDF1

26 25 demodulator supply voltage 1

VCONT 27 27 carrier loop VCO control voltage input

MIXREF 28 28 mixer voltage reference or input when using differential DQPSK signal

DQPSK 29 29 DQPSK input signal

COFF 30 30 cosine channel offset compensator capacitor output

CEYE 31 31 cosine channel eye pattern output for monitoring

PKDET 32 34 AGC peak detector storage capacitor output

V

I

REF

V

V

V

ROF

RCF

DDF2

SSF2

33 35 internal demodulator reference voltage buffered output

34 36 internal demodulator reference current output

35 37 internal demodulator reference voltage unbuffered output

36 38 demodulator supply voltage 2

37 39 demodulator ground connection 2

n.c. 38 40 not connected; left open-circuit in application

CLKLPF 39 41 clock loop-phase comparator output

1996 Oct 24 5

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

SYMBOL

SDIP52 QFP64

(1)

DESCRIPTION

XTAL 40 42 8.192 MHz crystal oscillator input

OSC 41 43 8.192 MHz crystal oscillator output

PIN

V

SSX

42 44 crystal oscillator ground connection

DATAIN 43 45 serial data input at 728 kbits/s to decoder

V

SSD

44 48 digital ground connection

PCLK 45 47 728 kHz output clock to DQPSK demodulator

V

DDD

46 49 digital supply voltage

RESET 47 50 active LOW power-on reset input

DATAOUT 48 46 serial data output at 728 kbits/s from DQPSK demodulator

2

SCL 49 53 serial clock input for I

SDA 50 54 serial data input/output for I

ADSEL 51 55 input that defines I

PORT2 52 56 output that is directly controlled from Port 2 bit in I

C-bus

2

C-bus

2

C-bus address bit 0 (internal pull-up)

2

C-bus

Note

1. Pins 1, 5, 6, 18, 19, 20, 26, 32, 33, 51, 52, 58, 60 and 64 are not connected; left open-circuit in application.

1996 Oct 24 6

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

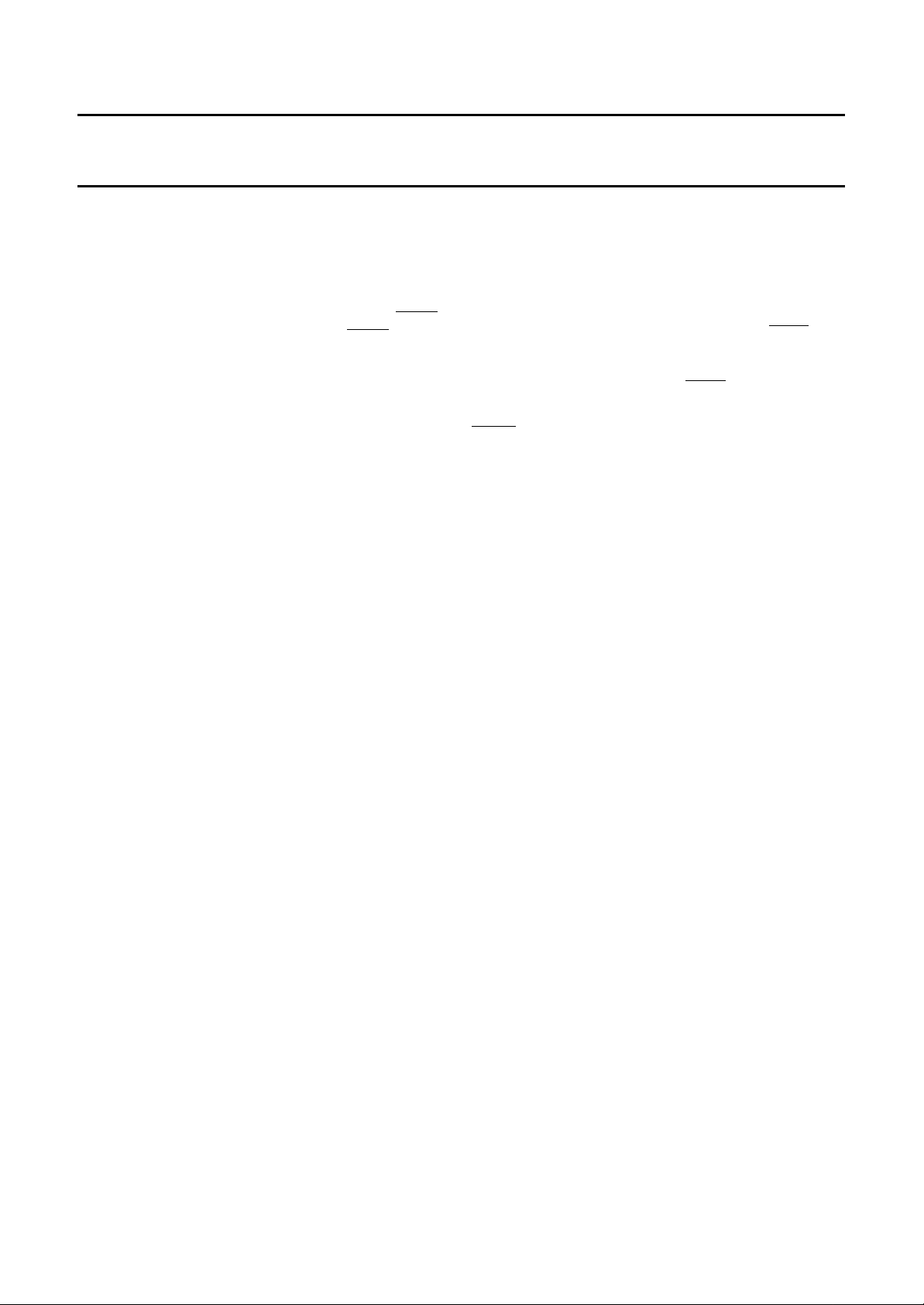

handbook, halfpage

V

SSDAC

REMVE

1

MUTE

2

V

3

DDA

V

4

SSA

V

5

RCA

6

EXTR

7

FMR

8

OPR

n.c.

9

n.c.

10

V

11

ROA

12

n.c.

13 40

n.c.

14

OPL

15

FML

16

EXTL

17

18

PORM

PORA

19

20

21

SAA7283ZP

52

51

50

49

48

47

46

45

44

43

42

41

39

38

37

36

35

34

33

32

PORT2

ADSELDOBM

SDA

SCL

DATAOUT

RESET

V

DDD

PCLK

V

SSD

DATAIN

V

SSX

OSC

XTAL

CLKLPF

n.c.

V

SSF2

V

DDF2

V

RCF

I

REF

V

ROF

PKDETREMO

22

23

V

24

SSF1

25

V

26

DDF1

Fig.2 Pin configuration for SOT247.

1996 Oct 24 7

MGB463

31

30

29

28

27

CEYESEYE

COFFSOFF

DQPSK

MIXREFVCLK

VCONT

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

handbook, full pagewidth

EXTR

V

V

SSDAC

EXTL

PORM

PORA

REMVE

REMO

n.c.

FMR

OPR

n.c.

n.c.

ROA

n.c.

n.c.

OPL

FML

n.c.

n.c.

SSA

RCA

n.c.

V

64

63

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

DDA

V

V

62

61

n.c.

60

DOBM

59

n.c.

58

MUTE

57

SAA7283GP

PORT2

56

ADSEL

55

SDA

54

SCL

53

n.c.

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

n.c.

RESET

V

DDD

V

SSD

PCLK

DATAOUT

DATAIN

V

SSX

OSC

XTAL

CLKLPF

n.c.

V

SSF2

V

DDF2

V

RCF

I

REF

V

ROF

PKDET

n.c.

20

21

n.c.

SEYE

22

SOFF

23

SSF1

V

24

VCLK

25

DDF1

V

Fig.3 Pin configuration for SOT319.

1996 Oct 24 8

26

n.c.

27

28

VCONT

29

DQPSK

MIXREF

30

COFF

31

CEYE

32

n.c.

MGB462

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

FUNCTIONAL DESCRIPTION

DQPSK demodulation

UADRATURE MIXERS, BASEBAND FILTERS AND AUTOMATIC

Q

GAIN CONTROL

(AGC)

The DQPSK signal is fed into two differential input mixers,

where it is mixed with quadrature phases generated by the

carrier-loop quadrature VCO. The quadrature signals

modulated onto the NICAM carrier are thus recovered.

The mixers can be driven by either a single-ended or

differential source. In single-ended mode, the device is

driven directly from the sound IF down-converter into the

DQPSK input pin, with the MIXREF pin decoupled.

In differential mode, the signal is applied between the

DQPSK and MIXREF pins.

The outputs from the mixers are then fed into a

pulse-shaping filter, and FM/vision filter stage which filters

out all interference components, including AM carrier for

French NICAM L system. The signal from the filtering

stages is then fed into the AGC, which ensures that the

phase comparator gain remains constant, irrespective of

the input signal level. This is important to maintain the

stability of Costas loop PLL.

CONTROLLER

AGC

The AGC controller monitors the I and Q channel signals

at the input to the carrier loop-phase comparator and

generates a reference voltage to set the AGC output level.

E

YE BUFFER

A differential to the single-ended converter provides the

baseband signal as an output at the pins CEYE and SEYE

for the I and Q channels respectively for eye-height

monitoring.

IT RATE CLOCK RECOVERY

B

The I and Q channels are processed using edge detectors

and monostables, which generate a signal with a coherent

component at the data symbol rate. The outputs from the

I and Q channel monostables are each compared with the

clock derived from PCLK (364 kHz nominal), the resultant

output is used to derive a 3-state control signal used to

control two current sources at the CLKLPF output.

This error signal is loop filtered and used to control the

master clock oscillator. The bit rate clock, PCLK, and

symbol clock are derived from the master clock.

NICAM 728 decoding

D

ECODING FUNCTIONS

The device performs all decoding functions in accordance

with the EBU NICAM 728 specification. After locking to the

frame alignment word, the data is de-scrambled by

application of the defined pseudo random binary

sequence, and the device synchronizes to the periodic

frame flag bit C0.

The relevant control information and scale factor word is

extracted, and with the integrated RAM the data is

de-interleaved and the scale factor word is extracted, and

expanded to 14 bits. Parity checking on the eleventh bit of

each sample word is carried out to reveal any sound

sample errors, which if detected are flagged, with the last

good sample being held.

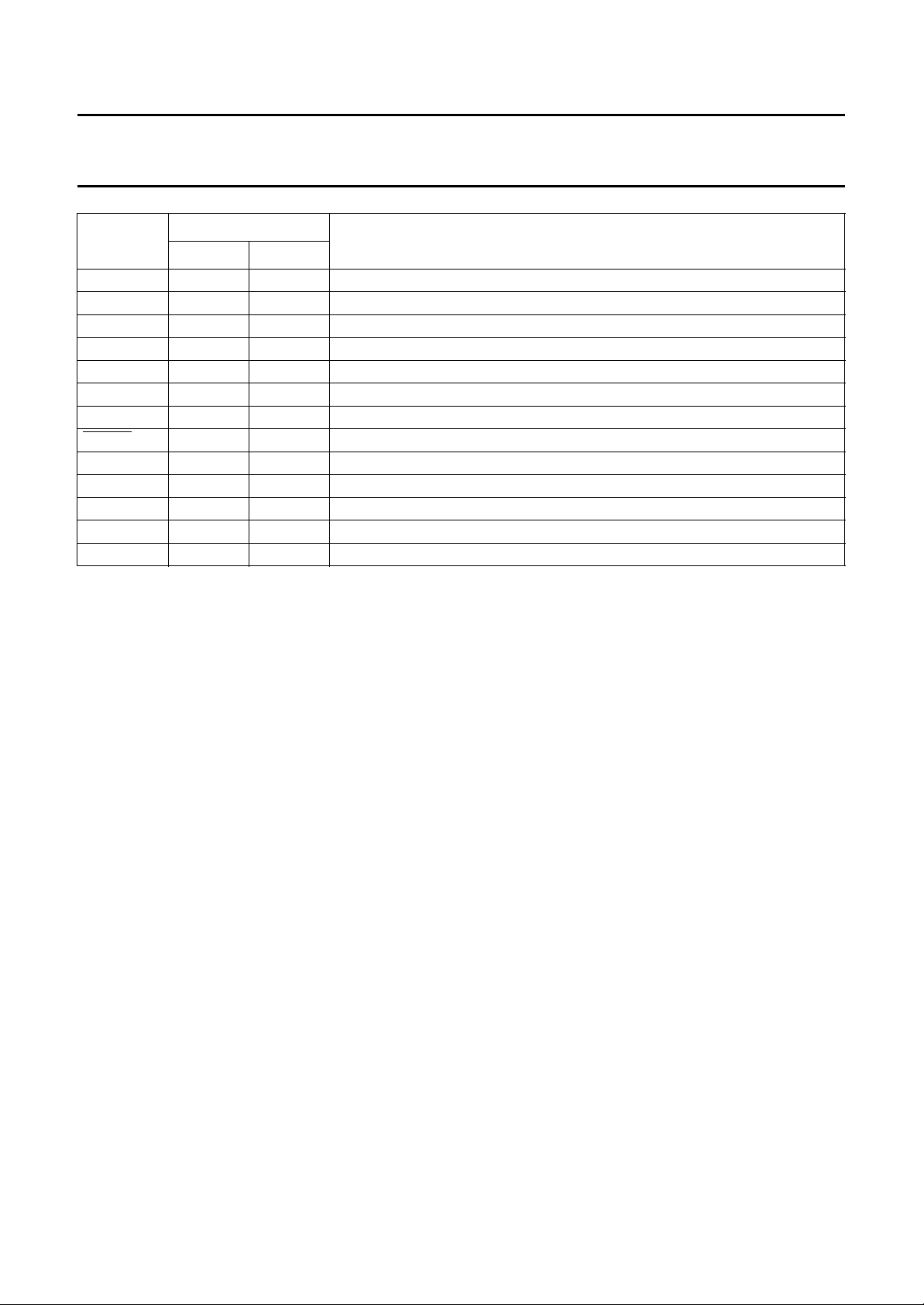

Automatic muting

Enable when AMDIS = LOW. The I

2

C-bus section has two

registers which define an upper and lower limit for the

automatic muting function. When the number of errors

within a 128 ms period exceeds the number stored in the

upper error limit register, then the automatic muting will

switch the device output to the FM input, (dependent on

the relevant control bits in the I2C-bus) and mute

(set to zero) the data input to the filter (in that order).

When the error count in a 128 ms period is less than the

value stored in the lower error limit register then the data

into the filter is uninterrupted, and the device output is

switched back to the DAC (dependent on the value of the

relevant control bits in the I2C-bus). During the muting

operation the open-drain pin MUTE is pulled LOW and the

AM bit in the status-byte is set HIGH. Figure 4 shows the

dependency of the automatic muting function on

error_count, RSSF, C4OV, output state and application

mode. The automatic muting function, if enabled, will

override user mute via the MUTE pin/bit.

When the transmission is DATA format or currently

undefined format (C3 = logic 1) the device will

automatically switch to the FM inputs regardless of

RSSF/C4OV states, and whether the automatic muting

function AMDIS is enabled or disabled.

1996 Oct 24 9

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

User mute

The error counter is an 8-bit counter which locks at

count 255. The counter is reset and its output sent to the

I2C-bus every 128 ms. This enables the user to interrogate

the number of errors occurring within a 128 ms period.

The user can then mute the device by pulling pin MUTE

LOW (this function is also provided by the MUTE bit in the

I2C-bus) or setting SILENCE bit LOW in I2C-bus to switch

input of audio switching buffers to analog ground.

Switching buffers

The analog switches select between the output of the

DACs, the FM input and an external input (EXT).

Switching is controlled by bits in the I

2

C-bus and internal

switching function. The external analog inputs should be

≤1.1 V (RMS) at the input pin, and the output buffers have

a voltage drive of 1 V (RMS).

NICAM/FM audio level matching

Differing audio headroom and alignment levels occur

between systems I and BGH, due to the differing systems

and broadcast standards. In order to match the NICAM

and FM audio output levels without requiring application

changes, the device will automatically switch in 4.6 dB

attenuation network in the NICAM path for system BGH

(this can be disabled by setting the NICLEV bit LOW in

2

C-bus). A programmable attenuation network in the FM

I

path only, controlled by bits in I2C-bus, provides additional

flexibility for user to match FM and NICAM audio levels

(see Table 9).

Power-on reset state

Two pins control the initial set-up of the device during

power-on reset.

PORA (Power-On Reset Audio)

When pulled LOW the device will be configured with a

12 dB gain in the oversampling filter and the

C4OV bit in

the I2C-bus will be set HIGH. This pin when HIGH will

configure the device with a 6 dB gain in the

oversampling filter and will set C4OV bit in the I2C-bus

LOW.

PORM (Power-On Reset Mute)

This pin when LOW will mute the output of the device at

power-on by setting the SILENCE bit in the I2C-bus

LOW. To put the device back into a normal mode of

operation the SILENCE bit in the I2C-bus must be set

HIGH.

1996 Oct 24 10

Philips Semiconductors Preliminary specification

Terrestrial Digital Sound Decoder (TDSD3) SAA7283

handbook, full pagewidth

ERROR_COUNT

ERROR_MAX

YES

RSSF = 1

EXT or FM INPUT

SWITCHED IN

NO

SOUND APPLICATION

DUAL MONO

NO

NO

YES

NO

MUTEB pin = HIGH

YES

MUTEB pin = LOW

DUAL MONO MODE

LEFT = RIGHT = M1

Output is

unchanged

AM bit = LOW

C4ov BIT = 0

YESYES

Output is

unchanged

AM bit = HIGH

SELECTED

YES

NO

(1)

(1)

NO

Output is

unchanged

AM bit = LOW

MUTEB pin = HIGH

When error_count is

less than error_min,

AM bit = LOW,

MUTEB pin = HIGH

Output is

unchanged

AM bit = LOW

MUTEB pin = HIGH

MGB465

Output is switched

to FM input

AM bit = HIGH

MUTEB pin = LOW

(1) Indicating that a mute may occur when user returns to NICAM source.

When error_count is less

than error_min, the output

is switched back to NICAM

and AM bit = LOW,

MUTEB pin = HIGH

Fig.4 Flow diagram showing SAA7283 automatic muting function.

1996 Oct 24 11

Loading...

Loading...