Philips SAA7214 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA7214

Transport MPEG2 source decoder

Preliminary specification

Supersedes data of 1999 Mar 16

File under Integrated Circuits, IC02

2001 Mar 28

Philips Semiconductors Preliminary specification

Transport MPEG2 source decoder SAA7214

FEATURES

General features

• Conditional access descrambling DVB-compliant

• Stream demultiplexing (TS, PES, program and

proprietary streams)

• Internal PR3001 32-bit RISC processor running at

40.5 MHz

• Low-power sleep modes supported across the chip

• Comprehensive driver software and development tool

support

• Package: SQFP208.

The following sections specify the featuresin more detail,

in the form of a feature matrix.

External interfaces

The SAA7214 supports the following external interfaces:

• Versatile compressed stream input at 108 Mbits/s

• A 16-bit microcontroller extension bus supporting

DRAM, Flash, (E)PROM and external memory mapped

• I/O devices. It also supports a synchronous interface to

communicate with the integrated MPEG AVGD decoder

SAA7215 at 40.5 Mbytes.

• an IEEE 1284 interface (Centronics) supporting master

and slave modes. Usable as a general purpose port

• A dedicated interface to IEEE 1394 devices (such as

Philips’ PDI 1394 chip set)

• Two UART (RS232) data ports with DMA capabilities

(≤187.5 kbits/s) including hardware flow control RxD,

TxD, RTS and CTS for modem support

• An elementary UART with DMA capabilities,(e.g.

dedicated to front panel devices for instance)

• Two dedicated smart-card reader interfaces (ISO 7816

compatible) with DMA capabilities

• Two I2C-bus master/slave transceivers supporting the

standard (100 kbit/s) and fast (400 kbits/s) I2C-bus

modes

• 32 general purpose, bidirectional I/O interface pins, the

first 8 bits may also be used as interrupt inputs

• One PWM output (8-bit resolution)

• A GP/HS interface supporting stream recording through

IEEE 1394 IC

• A JTAG interface for board test support.

CPU related features

The SAA7214 contains an embedded RISC CPU, which

incorporates the following features:

• A 32-bit PR3001 core

• 1 kbyte data, and 4 kbytes Instruction caches

(write-through style)

• A programmable low-power mode, including wake-up

on interrupt

• A memory management unit

• Two fully independent 24-bit timers and one 24-bit timer

including watchdog facilities

• A real-time clock unit (active in sleep mode)

• Built-in software debug support

• Anon-chip4 kbytes SRAM for storing code which needs

fast execution.

MPEG2 systems features

MPEG2 systems features of the SAA7214 include the

following

• Parsing of TS, PS (HW) and proprietary (SW) data

streams. Maximum input rate is 108 Mbits/s

• A real-time, DVB compliant descrambler core,

incorporating storage for up to 6 control word pairs

• HW section filtering based on 32 different PIDs with a

flexible number of filter conditions (8 or 4 byte condition

+ 8 or 4 byte mask) per PID and a total filter capacity of

40(8 byte condition checks) orupto80(4 bytecondition

checks) filter conditions.

• 4 TS/PES filters for retrieval for data at TS or PES level

for applications such as subtitling, TXT or retrieval of

private

• Data

• Flexible DMA based storage of the 32 section sub

streams and 4 TS/PES data substreams in the external

memory

2001 Mar 28 2

Philips Semiconductors Preliminary specification

Transport MPEG2 source decoder SAA7214

• System time base management with a double counter

mechanism for clock control and discontinuity handling

• 2 PTS/DTS timers

• A GP/HS filter which can serve as alternate input from

for example EEE1394 devices. It can also output either

scrambled or descrambled TS to IEEE 1394 devices.

APPLICATIONS

• Digital television decoder environment.

GENERAL DESCRIPTION

SAA7214 system overview

The device is part of a comprehensive source decoding kit

which contains all the hardware and software required to

receive and decode MPEG2 transport streams, including

descrambling, demultiplexing. In addition, it includes a

MIPS PR3001 RISC CPU core and several peripheral

interfaces such as UARTs, I2C-bus units, and an

IEEE 1284 (Centronics) interface. The SAA7214 is

therefore capable of performing all controller tasks in

digital television applications such as set-top boxes.

The SAA7214 is compliant to DVB specification.

The SAA7214 receives transport streams through a

versatile stream input interface capable of handling both

byte-parallel and bit-serial streams, in various formats,

supportingdatastreamsuptoand including 13.5 Mbytes/s

(108 Mbits/s).Thestreamdataisfirst applied to an on-chip

descrambler incorporating DVB descrambling algorithm,

onthe basis of 6 control word pairs stored in on-chip RAM.

Demultiplexing is subsequently applied to the stream, to

separate up to 32 individual data streams.

The demultiplexer section includes clock recovery and

timebase management. Program Specific Information

(PSI), Service Information (SI), Conditional Access (CA)

messages and private data are selected and stored in

external memory, for subsequent off-line processing by

the internal PR3001 CPU core.

To support advanced board testing facilities, the SAA7214

includes boundary scan test hardware, in accordance with

the JTAG standard. The device features a low-power

sleep mode, which is capable of sustaining set-top box

standby functionality, thus eliminating the need for a

separate front-panel controller. The SAA7214 requires a

supplyvoltage of 3.3 V and some devices input and output

interfaces are 5 V tolerant. The device is mounted in a

SQFP208 package.

2001 Mar 28 3

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2001 Mar 28 4

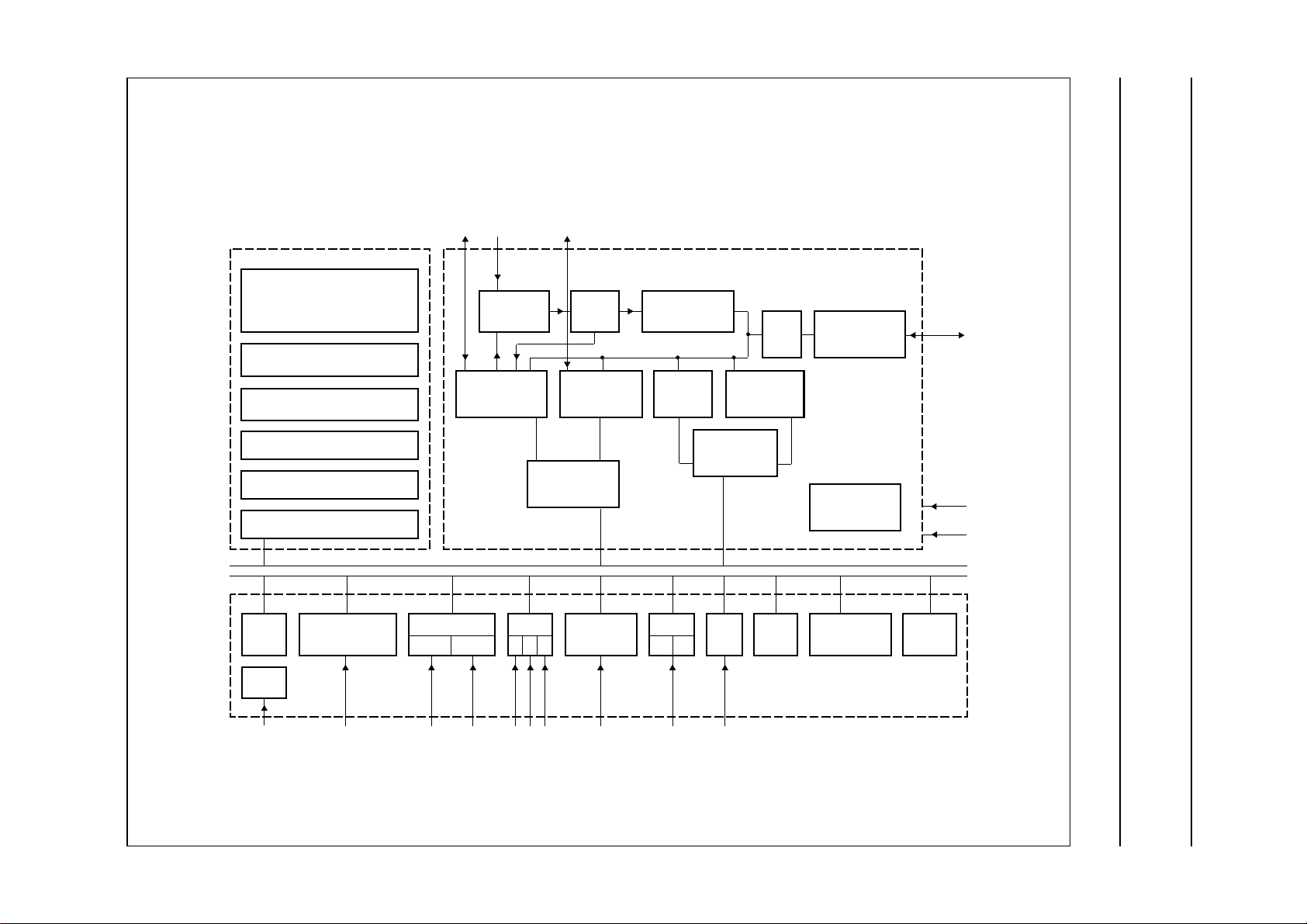

handbook, full pagewidth

BLOCK DIAGRAM

Philips Semiconductors Preliminary specification

Transport MPEG2 source decoder SAA7214

CPU section

MIPS

PR3001

CORE

DATA CACHE

INST. CACHE

TIMER 1

TIMER 2

TIMER-WD 3

PI-bus

SS MM

PI-BUS

CTRL

JTAG

EXTENSION BUS

CONTROLLER

CARDREADER UART

INPUT

INTERFACE

GP/HS

INTERFACE

1394 GATEWAY

MPEG SYSTEM

GATEWAY

01 0 10

12

PWM Demultiplexer Descrambler section

PID

FILTER

PCR

PROCESSING

PIO

INTERFACE

DESCRAMBLER

MPEG system-bus

TS/PES

LTERS

SSM

I2C

SECTION

LTERS

LTER DMA

CONTROLLER

M

1284

RTC

32KHz

AV

LTER

Peripheral section

AUDIO AND

VIDEO

INTERFACE

MPEG SYSTEM

INT.HANDLER

SS S

INTERRUPT

CONTROLLER

Reset

Clock

4 KBYTE

S-RAM

Fig.1 Block diagram.

FCE105

Loading...

Loading...