Philips SAA7212H Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA7212

Integrated MPEG AVG decoder

Preliminary specification

Supersedes data of 1998 Sep 07

File under Integrated Circuits, IC02

2001 Mar 28

Philips Semiconductors Preliminary specification

Integrated MPEG AVG decoder SAA7212

FEATURES

General features

• Single external Synchronous DRAM organized

as1M×16 interfacing at 81 MHz. Due to efficient

memory use in MPEG decoding, more than 1 Mbit

available for graphics

• Fast 16-bit data + 8-bit address interface with external

controller on 27 MHz. Sustained data rate to external

SDRAM ≤9 Mbytes/s in bursts of 128 bytes

• Dedicatedinputforaudio andvideo inPES orES inbyte

wide. Data input rate: ≤9 Mbytes/s in byte mode.

Accompanyingstrobe signalsdistinguishbetween audio

and video data

• Dedicated compressed data input compatible with the

VLSI VES2020/2030 demultiplexers; video is received

in byte format and audio serially

• Audio and/or video can also be input via the CPU

interface inPES/ESin 8 or 16-bit parallel formatup to a

peak data rate of 9 Mbytes/s

• Single 27 MHz external clock for time base reference

and internal processing. Internal system time base at

90 kHz can be synchronized via CPU port. All required

decoding and presentation clocks are generated

internally

• Flexible memoryallocation under controlofthe external

CPU enables optimized partitioning of memory for

different tasks

• Boundary scan testing implemented

• External SDRAM self test

• Supply voltage 3.3 V

• Package QFP160.

CPU related features

• 16 bits data, 8 bits address, or 16 bits multiplexed bus.

Motorola 68xxx and Intel x 86 compatible.

• Support fast DMA transfer

• Flexible bidirectional interface to external SDRAM.

Minimum sustained rate is 9 Mbytes/s

• Enhanced block mover allows 3 D data move in the

external SDRAM. Picture move/Graphic bit maps

construction can be done with minimum CPU support.

MPEG2 system features

• Parsing of MPEG2 PES and MPEG1 packet streams

• Double system time clock counters

• Stand-alone or supervised audio/video synchronization

• Processing of errors flagged by channel decoding

section

• Support for retrieval of PES header.

MPEG2 video features

• Decoding of MPEG2video up to mainlevel, main profile

• Output picture format: CCIR-601 4 : 2 : 2 interlaced

pictures.Picture format720 × 576 at50 Hzor 720 × 480

at 60 Hz

• Support of constant and variable bit rates up to

15 Mbits/s

• Stand-alone or CPU controlled mode for

decoding/display processes

• Stand-alonemode canbeused byapplicationsrequiring

still pictures manipulations

• Output interface at 8-bit wide, 27 MHz UYVY

multiplexed bus

• Horizontal and vertical pan and scan allows the

extraction of a window from the coded picture

• Flexible horizontal scaling from 0.5 up to 4 allows easy

aspect ratio conversion including support

for 2.21 : 1 aspect ratio movies. In case of shrinking an

anti-aliasing pre-filter is applied

• Vertical scalingwith fixed factors0.5, 1 or 2. Factor 0.5,

realizing picture shrink. Factor 2 can be used for

up-conversion of pictures with 288 (240) lines or less.

• Vertical down-scaling with 0.75 factor, realizing letter

box conversion

• Horizontaland verticalscaling canbe combinedto scale

pictures to1⁄4 their original size, thus freeing up screen

space for graphic applications like electronic program

guides

• Nonfull screenMPEG pictureswill bedisplayed ina box

of which position andbackground colour are adjustable

by the external microcontroller

• Nominal video input buffer size for ml@mp 2.7 Mbit

• Video output may be slaved to internally (master)

generated or externally (slave) supplied HV

synchronization signals. The position of active video is

programmable. Display phase is notaffected by MPEG

timebase changes.

2001 Mar 28 2

Philips Semiconductors Preliminary specification

Integrated MPEG AVG decoder SAA7212

• Video output direct connectable to SAA718x encoder

family

• Various trick modes under control of external

microcontroller in stand-alone mode:

– Freeze field/frame on I or P pictures; restart on I

picture

– Freeze field on B pictures; restart on the next I or P

picture.

– Scanning and decoding ofI or I + P pictures in a IBP

sequence

– Single step mode

– Repeat/skip field for time base correction.

MPEG2 audio features

• Decoding of 2 channels, layer I and II MPEG audio.

Support for mono, stereo, intensity stereo and dual

channel mode.

• Constant and variable bit rates up to 448 kbit/s

• Supportedaudio samplingfrequencies: 48,44.1, 32,24,

22.05 and 16 kHz

• CRC error detection

• 3 decoding modes for dual channel streams: decoding

ofCH1only, decodingof CH2only anddecoding ofboth

CH1 and CH2

• Storage of last 54 bytes in ancillary data field

• Dynamic Range Control (DRC) at output

• Independentchannel volumecontroland programmable

inter channel crosstalk through a baseband audio

processing unit

• Muting possibility via external controller. Automatic

muting in case of errors or data lack.

• Generation of ‘beeps’ with programmable tone height,

duration and amplitude

• Serial twochannel digital audiooutput with16, 18, 20or

22 bitsper sample,compatible eitherto I2Sor Japanese

formats. Outputcan be setto high-impedance modevia

the external controller.

• Serial SPDIF audio output. Output can be set to

high-impedance mode.

• Clock output 256 or 384 × fs for external DA converter.

Output can be set to high-impedance mode.

• Audio FIFO in external SDRAM. Programmable buffer

size, at least 64 kbit is available.

• Synchronization modes: PTS controlled, PTS free

running, software controlled, buffer controlled

• PTS register can be set via external controller

• Programmable processing delay compensation

• Software controlled stop and restart functions.

Graphics features

• Graphics are presented in boxes independent of video

format

• Screen arrangement of boxes is determined by display

list mechanism which allows for multiple boxes,

background loading, fastswitching, scrolling and fading

of regions

• Support of 2, 4, 8-bit/pixel in fixed bit maps format or

coded in accordance to the DVB variable/run length

standard for region based graphics

• Display colours are obtained via colour look up tables.

CLUToutput isYUVT at8-bit foreach signalcomponent

thus enabling 16 M different colours and 6-bit for T

which gives 64 mixing levels with video,

(T = transparency).

• Bit-map table mechanismto specify a sub setof entries

if the CLUT is larger than required by the coded bit

pattern. Supported bit-map tables are 16 to 256,

4 to 256 and 4 to 16.

• Graphics boxes may not overlap vertically. If 256 entry

CLUT has to be down loaded, a vertical separation of

1 line is mandatory.

• Optimized memory utilization in MPEG video decoding

allows for a storagecapacityof 1.2 Mbit for graphics bit

maps. Flexibility in memory control enables larger

capacity in a lot of applications. Moreover variable

length/run length encoding makes better use of

available memory capacity for graphics bit maps thus

making full screen graphics at 8-bit/pixel feasible.

• Fast CPU access (9 Mbytes/s) enables full 1.2 Mbit bit

map update within 20 ms

• Internal supportfor fast blockmoves in externalSDRAM

• Graphics mechanism canbe used for signal generation

in the vertical blanking interval. Usefulfor teletext, wide

screen signalling, closed caption, etc.

• Support for a single down loadable cursor of 1k pixel

with programmable shape. Supported shapes are

8 × 128 pixels, 16 × 64 pixels, 32 × 32 pixels,

64 × 16 pixels and 128 × 8 pixels.

• Cursor colours obtainedvia 4 entry CLUT withYUVT at

6,4,4 respectively 2 bits. Mixing of cursor with

video + graphics in 4 levels.

• Cursor can be moved freely across the screen without

overlapping restrictions.

2001 Mar 28 3

Philips Semiconductors Preliminary specification

Integrated MPEG AVG decoder SAA7212

APPLICATIONS

• Tbf.

GENERAL DESCRIPTION

The SAA7212 is an MPEG2sourcedecoder which combines audio decoding and video decoding. Additionally tothese

basic MPEG functions it also provides means for enhanced graphics and/or on-screen display (OSD). Due to an

optimized architecturefor audio and videodecoding, maximum capacityinexternal memory andprocessing power from

the external CPU is available for graphics support.

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DD

I

DD(tot)

f

clk

functional supply voltage 3.0 3.3 3.6 V

total supply current; VDD= 3.3 V − tbf − mA

device clock frequency −30 ppm 27.0 +30 ppm MHz

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

SAA7212H QFP160 plastic quad flat package; 160 leads (lead length 1.95 mm);

body 28 × 28 × 3.4 mm; high stand-off height

SOT322-1

2001 Mar 28 4

Philips Semiconductors Preliminary specification

Integrated MPEG AVG decoder SAA7212

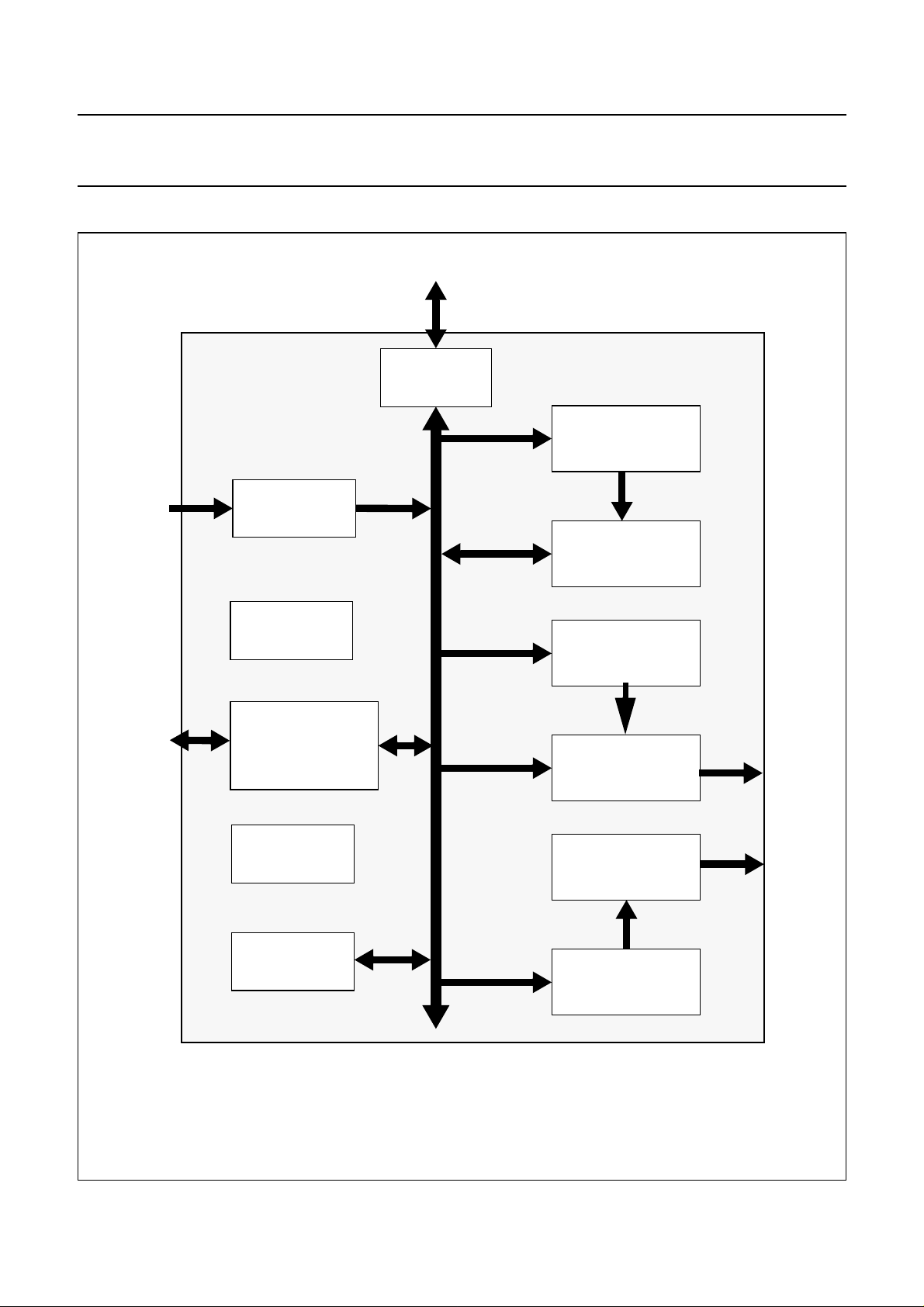

BLOCK DIAGRAM

SDRAM

Memory

interface

Video input

buffer and sync

from

Demux

to/from

external

CPU

Audio/video

interface

System time

base unit

Host interface

SDRAM access

unit

Clock

generation

Video

Decoder

Display

unit

Graphics

unit

Audio

Decoder

to

digital

encoder

to

audio

DAC

JTAG

Fig.1 Block diagram.

2001 Mar 28 5

Audio input

buffer and sync

Philips Semiconductors Preliminary specification

Integrated MPEG AVG decoder SAA7212

PINNING

SYMBOL PIN DESCRIPTION

MUX 1 multiplexed/non multiplexed bus

CPU_TYPE 2 Intel/Motorola selection

DMA_ACK 3 DMA acknowledge

DMA_REQ 4 DMA request

DMA_DONE 5 DMA end

DMA_RDY 6 DMA ready

V

SS

CS 8 chip select.

DS 9 data strobe

AS 10 address strobe

RWN 11 read/write

DTACK 12 data acknowledge

V

DD

IRQ 0 14 individually maskable interrupts

IRQ 1 15 individually maskable interrupts

V_REQ 16 compressed video data request

A_REQ 17 compressed audio data request

V

SS

V

SSCO

V

DDCO

DATA 0 21 CPU data interface

DATA 1 22 CPU data interface

DATA 2 23 CPU data interface

DATA 3 24 CPU data interface

V

DD

DATA 4 26 CPU data interface

DATA 5 27 CPU data interface

DATA 6 28 CPU data interface

DATA 7 29 CPU data interface

V

SS

DATA 8 31 CPU data interface

DATA 9 32 CPU data interface

DATA 10 33 CPU data interface

DATA 11 34 CPU data interface

V

DD

DATA 12 36 CPU data interface

DATA 13 37 CPU data interface

DATA 14 38 CPU data interface

DATA 15 39 CPU data interface

V

SS

7 ground for pad ring

13 3.3 V supply for pad ring

18 ground for pad ring

19 ground for core logic

20 3.3 V supply for core logic

25 3.3 V supply for pad ring

30 ground for pad ring

35 3.3 V supply for pad ring

40 ground for pad ring

2001 Mar 28 6

Loading...

Loading...