Philips saa7192a DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA7192A

Digital Colour Space Converter

(DCSC)

Product specification

Supersedes data of June 1991

File under Integrated Circuits, IC22

1996 Sep 25

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

4 BLOCK DIAGRAM

5 PINNING

6 FUNCTIONAL DESCRIPTION

6.1 Functional modes

6.2 Control

6.2.1 Control signals

6.2.2 Clock

6.2.3 Error condition

6.3 System I/O interfaces

6.3.1 Video data input signals

6.3.2 Video data output signals

6.3.3 Auxiliary data

6.4 System block description

6.4.1 Input formatter with filter

6.4.2 Conversion matrix

6.4.3 Video look-up table and output stage

6.4.4 I2C-bus receiver

7 OPERATING CONDITIONS

7.1 Electrical conditions

7.1.1 Start-up condition

7.1.2 Operating time

7.1.3 Temperature range

7.1.4 Backup

7.1.5 Power-down mode

7.1.6 Handling

8 LIMITING VALUES

9 DC CHARACTERISTICS

10 TIMING CHARACTERISTICS

11 PACKAGE OUTLINE

12 SOLDERING

12.1 Introduction

12.2 Reflow soldering

12.3 Wave soldering

12.4 Repairing soldered joints

13 DEFINITIONS

14 LIFE SUPPORT APPLICATIONS

15 PURCHASE OF PHILIPS I2C COMPONENTS

1996 Sep 25 2

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

1 FEATURES

• Input formatter with:

– multiplexer

– Y-delay line

– Cr and Cb interpolating filters

• Conversion matrix (according to CCIR 601)

• Video look-up tables (provide gamma correction)

• Pipeline delay line (horizontal reference signal)

• I2C-bus interface

2 GENERAL DESCRIPTION

The Digital Colour Space Converter (DCSC) is a digital

matrix which is used to transform 16/24-bit digital input

signals, i.e. Y (luminance), Cr (colour, R-Y) and Cb (colour,

B-Y), into an RGB 24-bit format in accordance with the

“CCIR-601 recommendations”

.

Accepting inputs from the different formats of the MPC-E

decoder family, the device has a constant propagation

delay and a maximum data rate of 16 MHz. A matched

pipeline delay line is available to permit the HREF signal to

be synchronized with the video data at the output.

• All functional blocks are bypassable.

3 ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

SAA7192AWP PLCC68 plastic leaded chip carrier; 68 leads SOT188-2

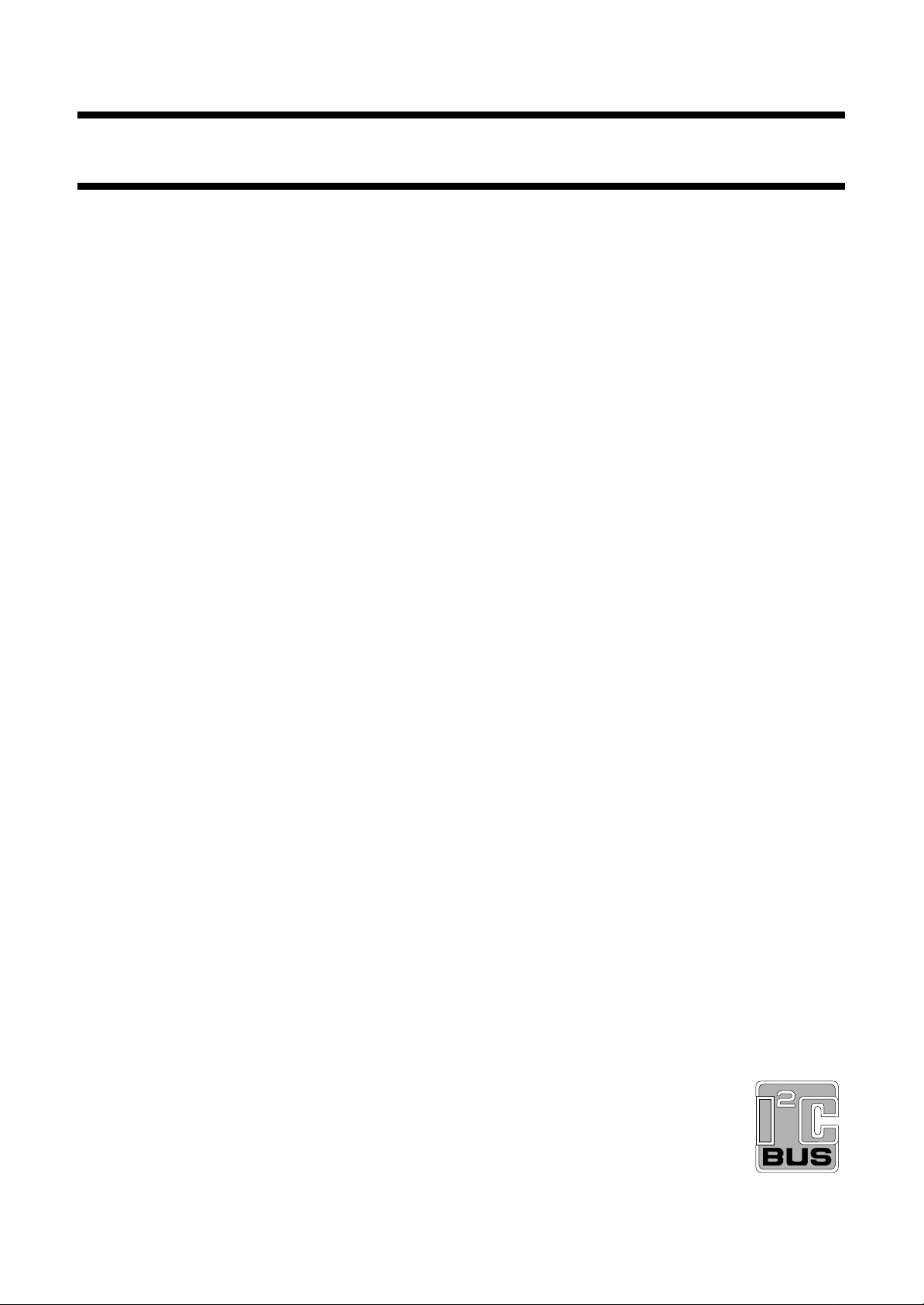

4 BLOCK DIAGRAM

andbook, full pagewidth

DATAIN1

DATAIN2

DATAIN3

HREF

TEST

FORMATTER

8

8

MULTIPLEXER

8

65

60

CLK_MODE CLOCK RESET

SAA7192A

59 63 26 64 28 27 29

Y

DELAY

Cr AND Cb

FILTER

CREF

PIPELINE DELAY LINE

I2C-BUS RECEIVER

SCL

I2C-bus

ADDRESS

Fig.1 Block diagram.

MATRIX

SDA

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

62

VLUTBYPASS

OE

61

8

8

8

58

DATAOUT1

DATAOUT2

DATAOUT3

HREF_OUT

MGE946

1996 Sep 25 3

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

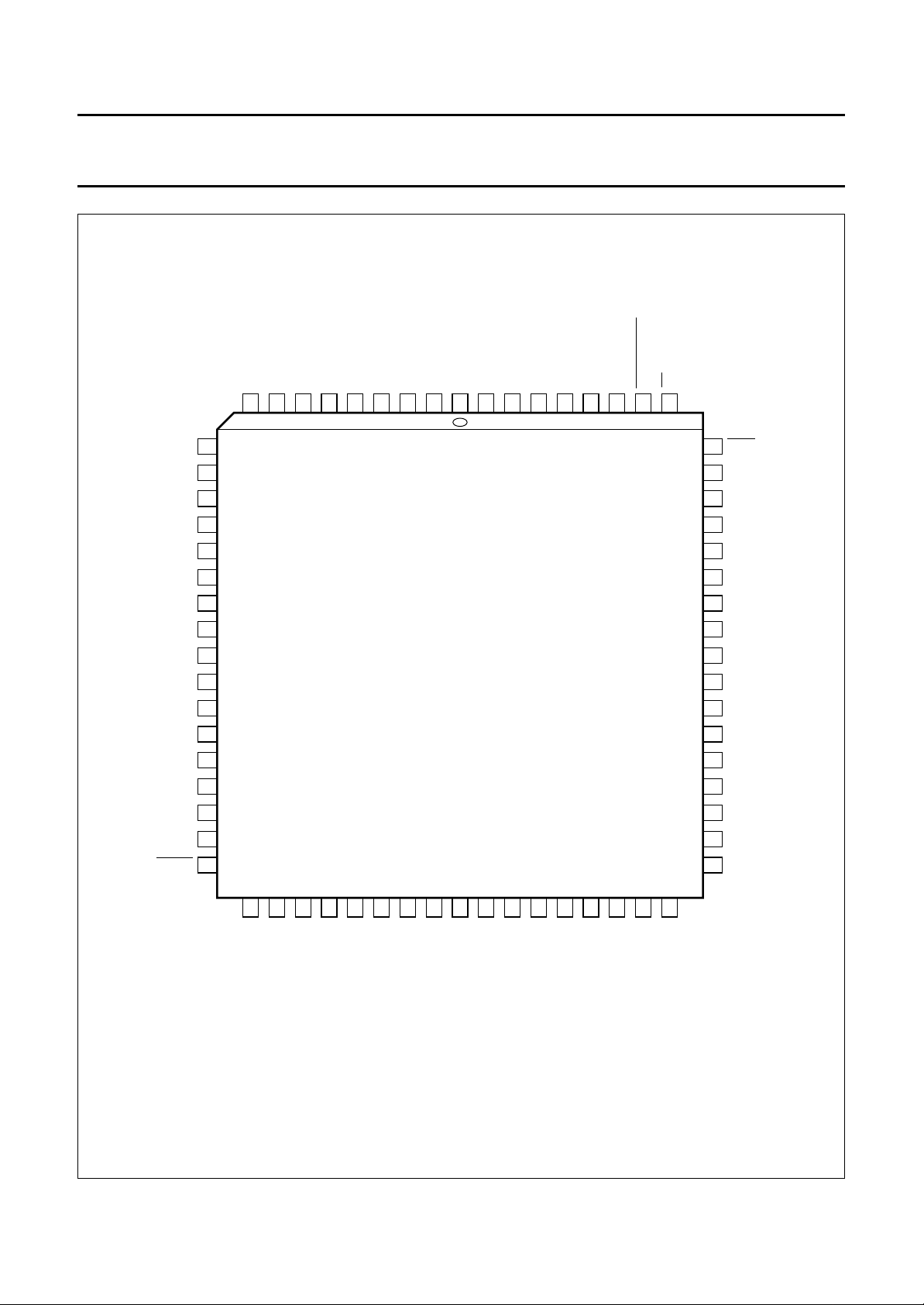

5 PINNING

SYMBOL PIN I/O DESCRIPTION

DATAIN21 1 I colour difference signal Cr1

DATAIN22 2 I colour difference signal Cr2

DATAIN23 3 I colour difference signal Cr3

DATAIN24 4 I colour difference signal Cr4

DATAIN25 5 I colour difference signal Cr5

DATAIN26 6 I colour difference signal Cr6

DATAIN27 7 I colour difference signal Cr7

DATAIN30 8 I colour difference signal Cb0 or multiplexed Cb and Cr

DATAIN31 9 I colour difference signal Cb1 or multiplexed Cb and Cr

DATAIN32 10 I colour difference signal Cb2 or multiplexed Cb and Cr

DATAIN33 11 I colour difference signal Cb3 or multiplexed Cb and Cr

DATAIN34 12 I colour difference signal Cb4 or multiplexed Cb and Cr

DATAIN35 13 I colour difference signal Cb5 or multiplexed Cb and Cr

DATAIN36 14 I colour difference signal Cb6 or multiplexed Cb and Cr

DATAIN37 15 I colour difference signal Cb7 or multiplexed Cb and Cr

DATAIN10 16 I luminance signal Y0

DATAIN11 17 I luminance signal Y1

V

DD

V

SS

DATAIN12 20 I luminance signal Y2

DATAIN13 21 I luminance signal Y3

DATAIN14 22 I luminance signal Y4

DATAIN15 23 I luminance signal Y5

DATAIN16 24 I luminance signal Y6

DATAIN17 25 I luminance signal Y7

RESET 26 I initially resets the functions

2

C-bus ADDRESS 27 I I2C-bus slave address selection

I

SCL 28 I I

SDA 29 I/O I

DATAOUT10 30 O RED0

DATAOUT11 31 O RED1

DATAOUT12 32 O RED2

DATAOUT13 33 O RED3

DATAOUT14 34 O RED4

18 − positive supply, voltage core (+5 V)

19 − negative supply, voltage core (ground)

2

C-bus serial clock

2

C-bus serial data

1996 Sep 25 4

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

SYMBOL PIN I/O DESCRIPTION

V

DD

V

SS

DATAOUT15 37 O RED5

DATAOUT16 38 O RED6

DATAOUT17 39 O RED7

DATAOUT20 40 O GREEN0

DATAOUT21 41 O GREEN1

DATAOUT22 42 O GREEN2

DATAOUT23 43 O GREEN3

DATAOUT24 44 O GREEN4

DATAOUT25 45 O GREEN5

DATAOUT26 46 O GREEN6

DATAOUT27 47 O GREEN7

DATAOUT30 48 O BLUE0

DATAOUT31 49 O BLUE1

DATAOUT32 50 O BLUE2

V

DD

V

SS

DATAOUT33 53 O BLUE3

DATAOUT34 54 O BLUE4

DATAOUT35 55 O BLUE5

DATAOUT36 56 O BLUE6

DATAOUT37 57 O BLUE7

HREF_OUT 58 O delayed horizontal reference signal

CLK_MODE 59 I 16 MHz or DMSD clock mode selection

TEST 60 I test mode, active LOW, usually not connected

OE 61 I output enable (fast switch)

VLUTBYPASS 62 I fast switch to operate the VLUTs in bypass

CLOCK 63 I system clock

CREF 64 I clock reference signal (DMSD mode)

HREF 65 I horizontal reference signal

DATAIN20 66 I colour difference signal Cr0

V

DD

V

SS

35 − positive supply voltage, output stages (+5 V)

36 − negative supply, output stages

51 − positive supply voltage, output stages (+5 V)

52 − negative supply, output stages

67 − positive supply, voltage core (+5 V)

68 − negative supply, voltage core (ground)

1996 Sep 25 5

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

handbook, full pagewidth

DATAIN31

DATAIN30

DATAIN27

DATAIN26

DATAIN25

DATAIN24

DATAIN23

DATAIN22

DATAIN21

VSSVDDDATAIN20

9

8

7

6

5

4

3

2

1

68

67

HREF

CREF

CLOCK

VLUTBYPASS

OE

66

65

64

63

62

61

DATAIN32

DATAIN33

DATAIN34

DATAIN35

DATAIN36

DATAIN37

DATAIN10

DATAIN11

V

DD

V

SS

DATAIN12

DATAIN13

DATAIN14

DATAIN15

DATAIN16

DATAIN17

RESET

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

SAA7192A

60

TEST

59

CLK_MODE

58

HREF_OUT

57

DATAOUT37

56

DATAOUT36

55

DATAOUT35

54

DATAOUT34

53

DATAOUT33

V

52

SS

V

51

DD

50

DATAOUT32

49

DATAOUT31

48

DATAOUT30

47

DATAOUT27

46

DATAOUT26

45

DATAOUT25

44

DATAOUT24

27

28

29

30

31

32

33

34

SCL

SDA

DATAOUT10

DATAOUT11

DATAOUT12

DATAOUT13

DATAOUT14

C-bus ADDRESS

2

I

Fig.2 Pin configuration.

1996 Sep 25 6

35

V

DD

36

SS

V

37

38

DATAOUT15

DATAOUT16

39

40

DATAOUT17

DATAOUT20

41

42

DATAOUT21

DATAOUT22

43

MGE933

DATAOUT23

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

6 FUNCTIONAL DESCRIPTION

6.1 Functional modes

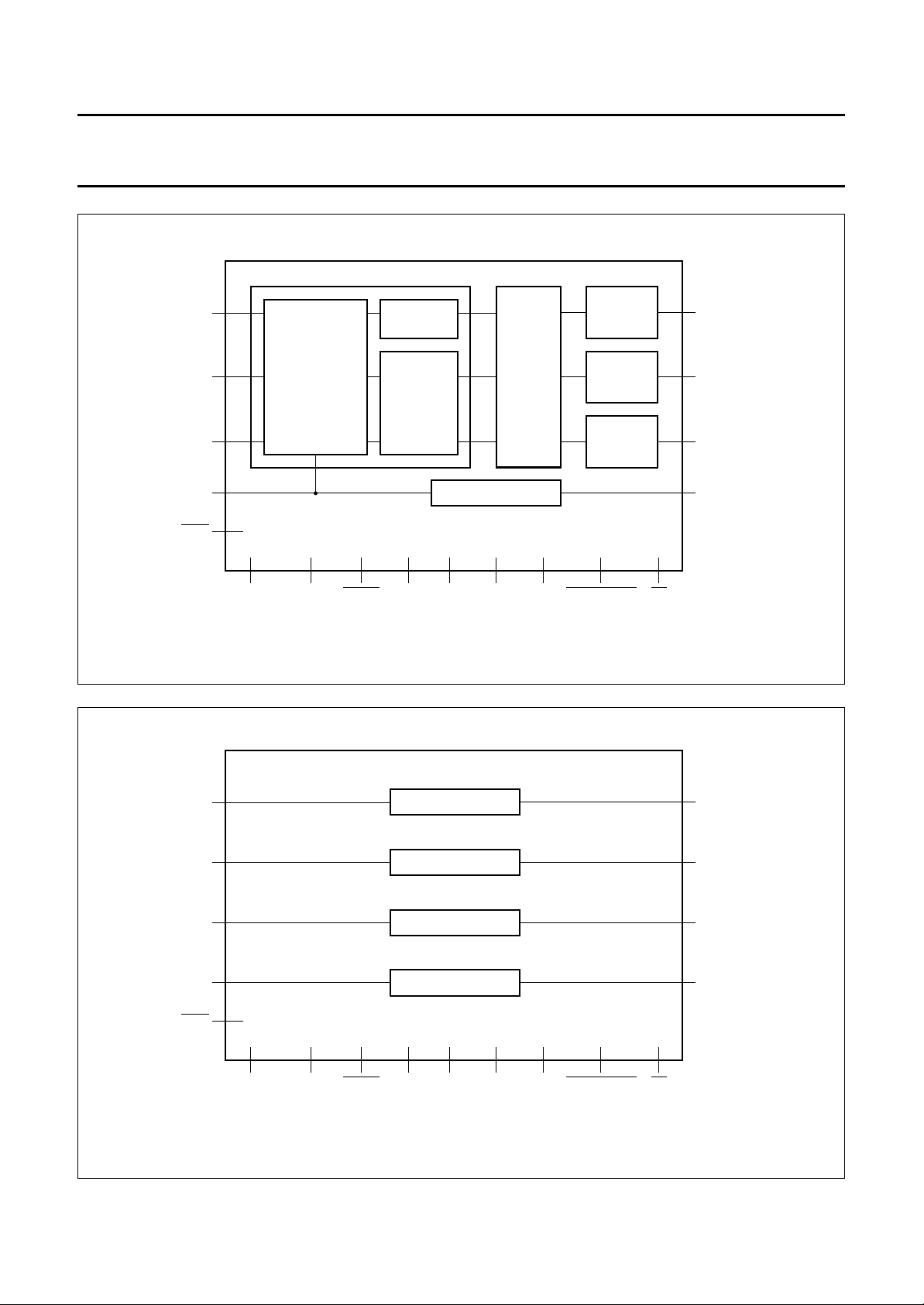

Table 1 Functional modes (note 1)

MODE FUNCTION

1 4:1:1 filter, no matrix, no VLUT; DATAOUT = upsampled DATAIN

2 4:1:1 filter, matrix, no VLUT; DATAOUT = RGB

3 4:1:1 filter, no matrix, VLUT; DATAOUT = upsampled DATAIN multiplied by the factor loaded

into the VLUT

4 4:1:1 filter, matrix, VLUT; DATAOUT = RGB multiplied by the factor loaded into the VLUT

5 4:2:2 filter, no matrix, no VLUT; DATAOUT = upsampled DATAIN

6 4:2:2 filter, matrix, no VLUT; DATAOUT = RGB

7 4:2:2 filter, no matrix, VLUT; DATAOUT = upsampled DATAIN multiplied by the factor loaded

into the VLUT

8 4:2:2 filter, matrix, VLUT; DATAOUT = RGB multiplied by the factor loaded into the VLUT

9 no filter, no matrix, no VLUT; DATAOUT = DATAIN ‘Process Bypass’

10 no filter, matrix, no VLUT; DATAOUT = RGB

11 no filter, no matrix, VLUT; DATAOUT = DATAIN multiplied by the factor loaded into the VLUT

12 no filter, matrix, VLUT; DATAOUT = RGB multiplied by the factor loaded into the VLUT

Note

1. Figures 3 to 10 illustrate the functional modes.

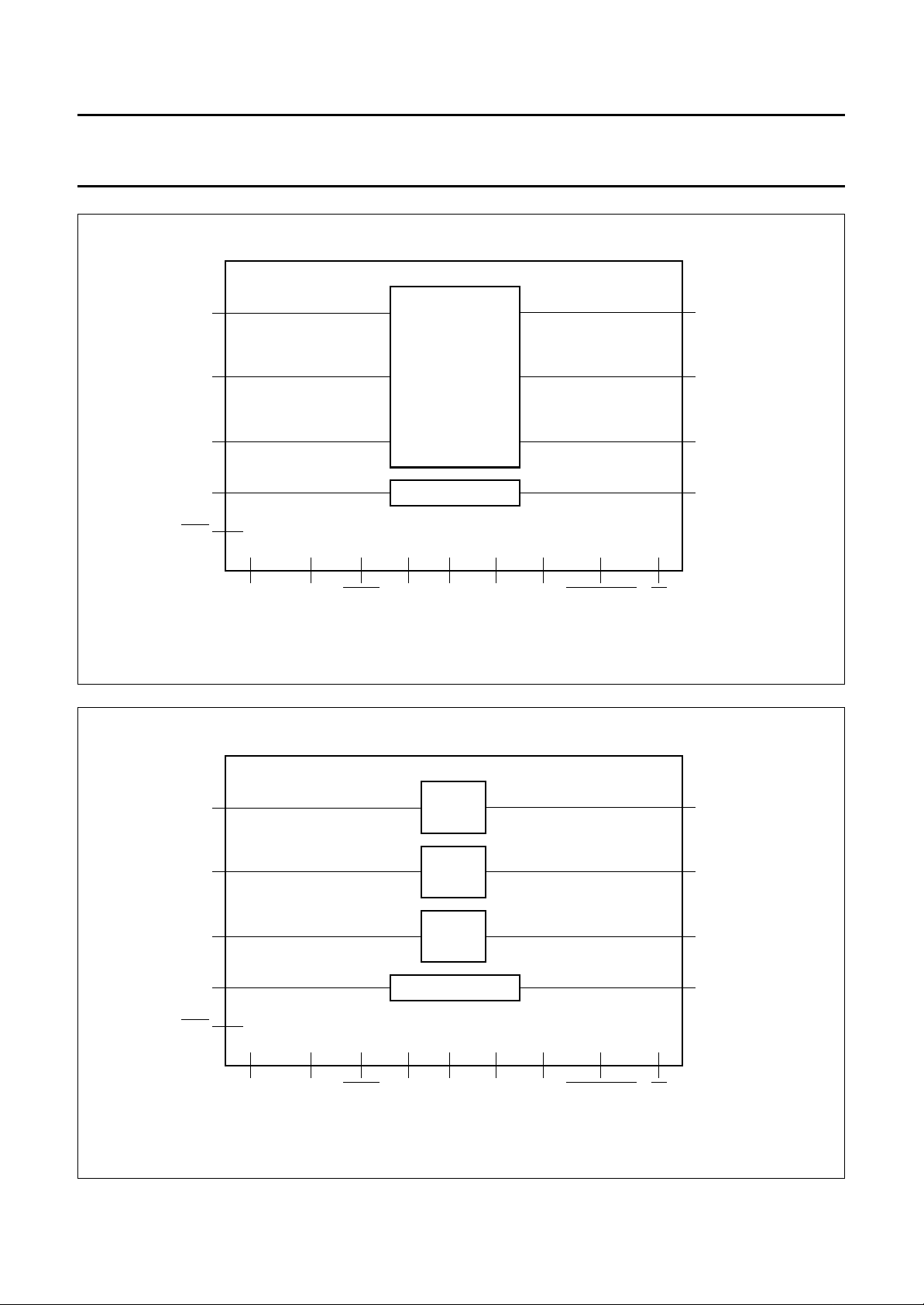

handbook, full pagewidth

DAT AIN1

DAT AIN2

DAT AIN3

MULTIPLEXER

HREF

TEST

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

FORMATTER

Y

DELAY

Cr AND Cb

FILTER

PIPELINE DELAY LINE

CREF

SCL

I2C-bus

ADDRESS

SDA

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE950

Fig.3 Functional modes 1 and 5.

1996 Sep 25 7

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

handbook, full pagewidth

DAT AIN1

DAT AIN2

DAT AIN3

MULTIPLEXER

HREF

TEST

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

FORMATTER

Y

DELAY

Cr AND Cb

FILTER

PIPELINE DELAY LINE

CREF

SCL

I2C-bus

ADDRESS

Fig.4 Functional modes 2 and 6.

MATRIX

SDA

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE949

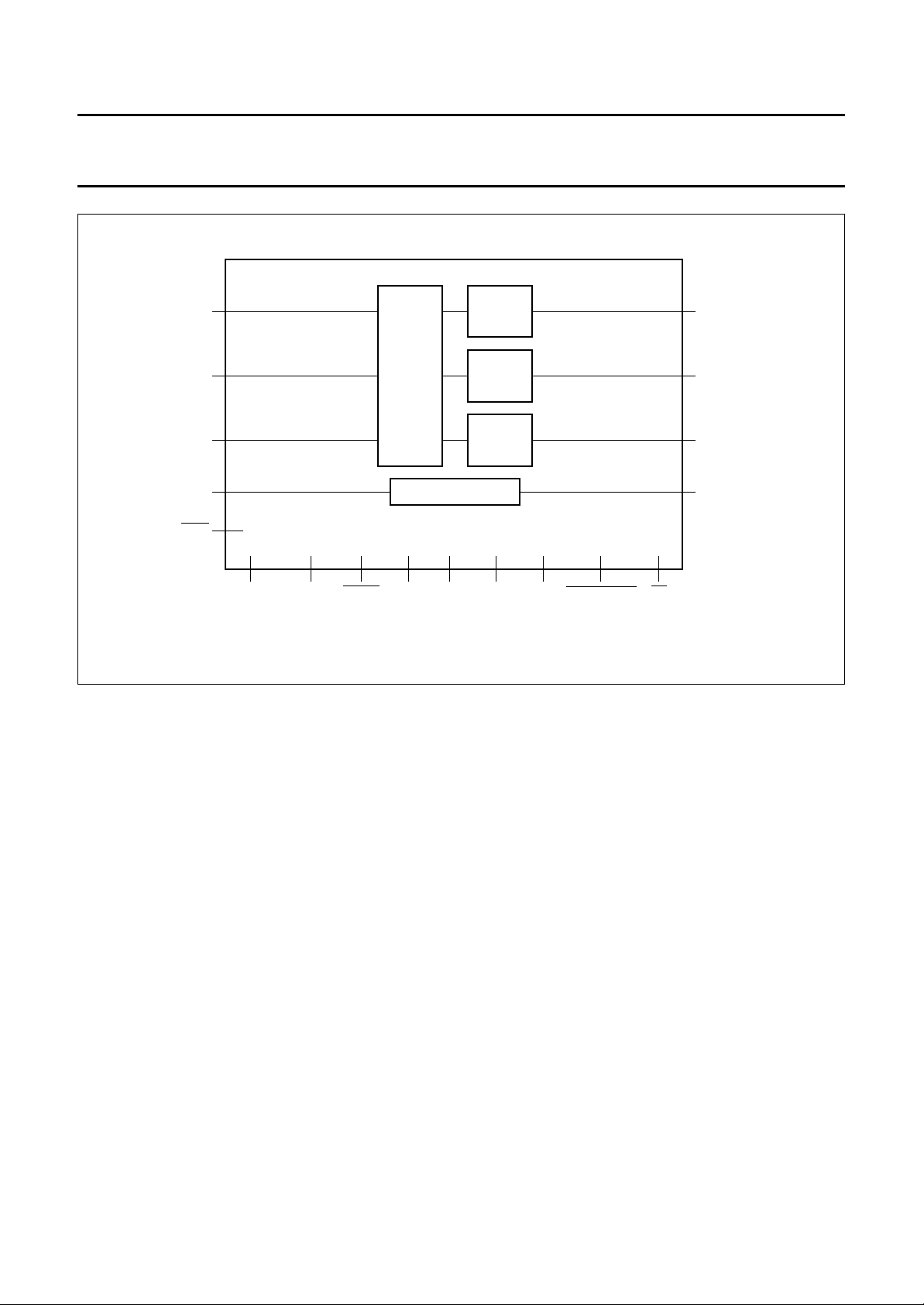

handbook, full pagewidth

DAT AIN1

DAT AIN2

DAT AIN3

MULTIPLEXER

HREF

TEST

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

FORMATTER

Y

DELAY

Cr AND Cb

FILTER

PIPELINE DELAY LINE

CREF

SCL

Fig.5 Functional modes 3 and 7.

1996 Sep 25 8

I2C-bus

ADDRESS

SDA

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE948

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

handbook, full pagewidth

DAT AIN1

DAT AIN2

DAT AIN3

MULTIPLEXER

HREF

TEST

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

FORMATTER

Y

DELAY

Cr AND Cb

FILTER

PIPELINE DELAY LINE

CREF

SCL

I2C-bus

ADDRESS

Fig.6 Functional modes 4 and 8.

MATRIX

SDA

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE947

handbook, full pagewidth

DAT AIN1

DAT AIN2

DAT AIN3

HREF

TEST

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

PIPELINE DELAY LINE

PIPELINE DELAY LINE

PIPELINE DELAY LINE

PIPELINE DELAY LINE

CREF

SCL

Fig.7 Functional mode 9.

1996 Sep 25 9

I2C-bus

ADDRESS

SDA

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE945

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

handbook, full pagewidth

DAT AIN1

DAT AIN2

DAT AIN3

HREF

TEST

MATRIX

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

PIPELINE DELAY LINE

CREF

SCL

I2C-bus

ADDRESS

Fig.8 Functional mode 10.

SDA

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE944

handbook, full pagewidth

VIDEO

DAT AIN1

DAT AIN2

DAT AIN3

HREF

TEST

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

VIDEO

LOOK-UP

TABLES

PIPELINE DELAY LINE

CREF

SCL

Fig.9 Functional mode 11.

1996 Sep 25 10

I2C-bus

ADDRESS

SDA

62

VLUTBYPASS

OE

58

61

DAT AOUT1

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE942

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

handbook, full pagewidth

VIDEO

DAT AIN1

LOOK-UP

TABLES

DAT AOUT1

DAT AIN2

DAT AIN3

HREF

TEST

MATRIX

65

60

59 63 26 64 28 27 29

CLK_MODE CLOCK RESET

PIPELINE DELAY LINE

CREF

SCL

LOOK-UP

LOOK-UP

I2C-bus

ADDRESS

Fig.10 Functional mode 12.

VIDEO

TABLES

VIDEO

TABLES

SDA

62

VLUTBYPASS

OE

58

61

DAT AOUT2

DAT AOUT3

HREF_OUT

MGE943

1996 Sep 25 11

Philips Semiconductors Product specification

Digital Colour Space Converter (DCSC) SAA7192A

6.2 Control

6.2.1 C

ONTROL SIGNALS

After power-up all internal control signals are in undefined states. The I2C-bus receiver must therefore be reset by using

the external RESET signal.

2

Table 2 I

C-bus controls (subaddress 00H)

SIGNAL BIT FUNCTION

FMTCNTRL D0 to D2 000;4:1:1 format, DMSD2 format

001;4:1:1 format, customized format

010;4:2:2 format, from DMSD2

011;4:2:2 format, parallel

100;4:4:4 format, parallel; default

101; not used

110; not used

111; not used

MATBYPASS D3 logic 1; matrix in use

logic 0; matrix bypassed; default state after reset

INRESET D4 logic 1; input latches at the formatter are always transparent

logic 0; at the end of each active video line the input signal will be set to fixed values

(Y to 16; Cr, Cb to 128; if HREF = 0); default state after reset

IICOE D5 logic 1;

OE enabled

logic 0; switches the output to high impedance mode; default state after reset

Table 3 Selection of functional modes and input formats (see Table 1)

FMTCNTRL

(1)

MATBYPASS

(2)

VLUTBYPASS

(3)

000 0 0 mode 1, input format 0

000 1 0 mode 2, input format 0

001 0 0 mode 1, input format 1

001 1 0 mode 2, input format 1

010 0 0 mode 5, input format 2

010 1 0 mode 6, input format 2

011 0 0 mode 5, input format 3 (parallel IN)

011 1 0 mode 6, input format 3 (parallel IN)

100 0 0 mode 9, input format 4 (parallel IN)

100 1 0 mode 10, input format 4 (parallel IN)

XXX X 1 each of the above modes will be multiplied by the factor

loaded into the VLUT

Notes

1. FMTCNTRL: bits D0 to D2 of I

2

C-bus.

2. Bit D3 of I2C-bus.

3. Pin 62.

FUNCTIONAL MODE/INPUT FORMAT

1996 Sep 25 12

Loading...

Loading...