Philips SAA7146AH-00, SAA7146AH-02, SAA7146AHZ-00, SAA7146AHZ-02 Datasheet

DATA SH EET

Product specification

File under Integrated Circuits, IC22

1998 Apr 09

INTEGRATED CIRCUITS

SAA7146A

Multimedia bridge, high

performance Scaler and PCI circuit

(SPCI)

1998 Apr 09 2

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

CONTENTS

1 FEATURES

1.1 Video processing

1.2 Audio processing

1.3 Scaling

1.4 Interfacing

1.5 General

2 GENERAL DESCRIPTION

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

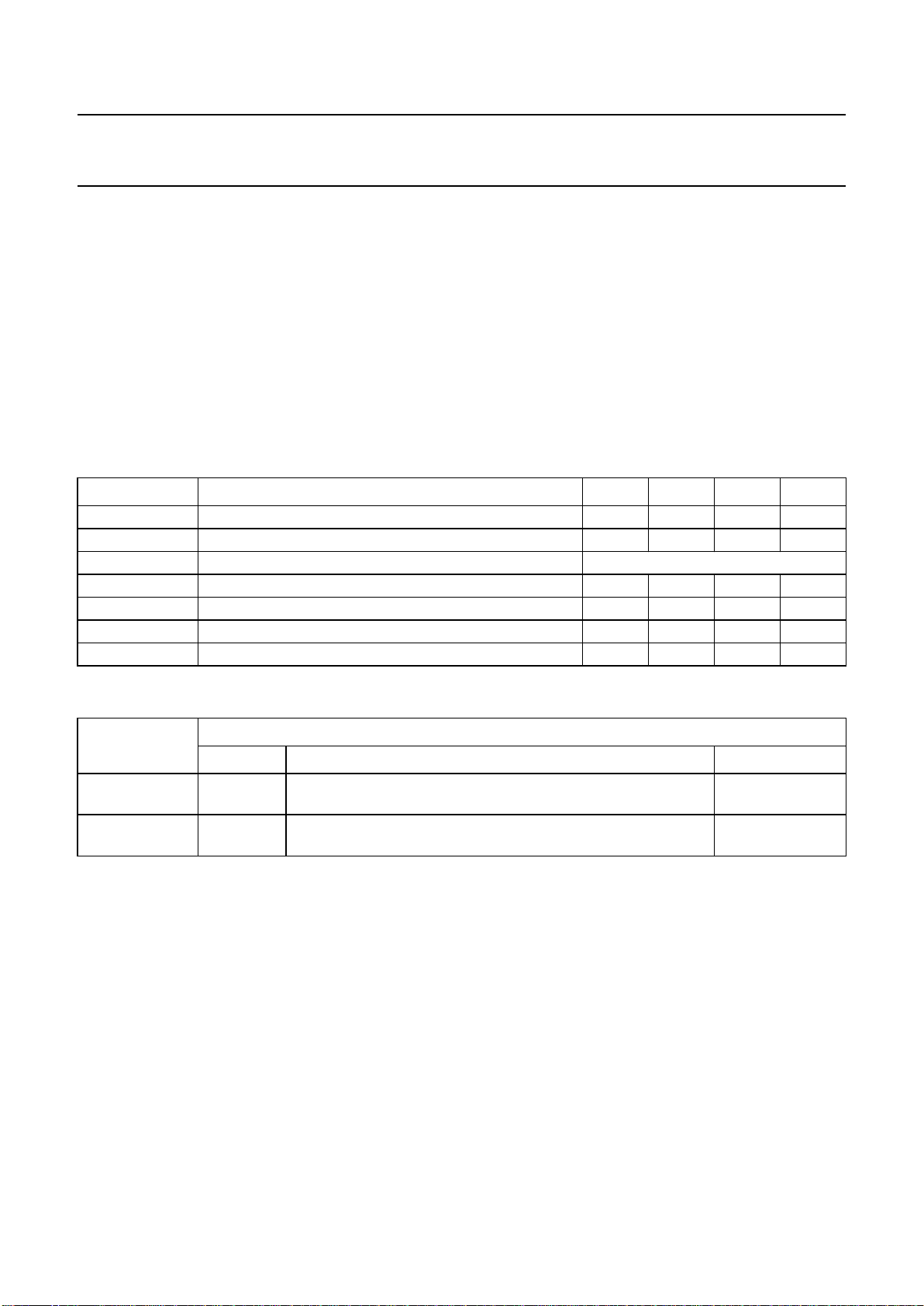

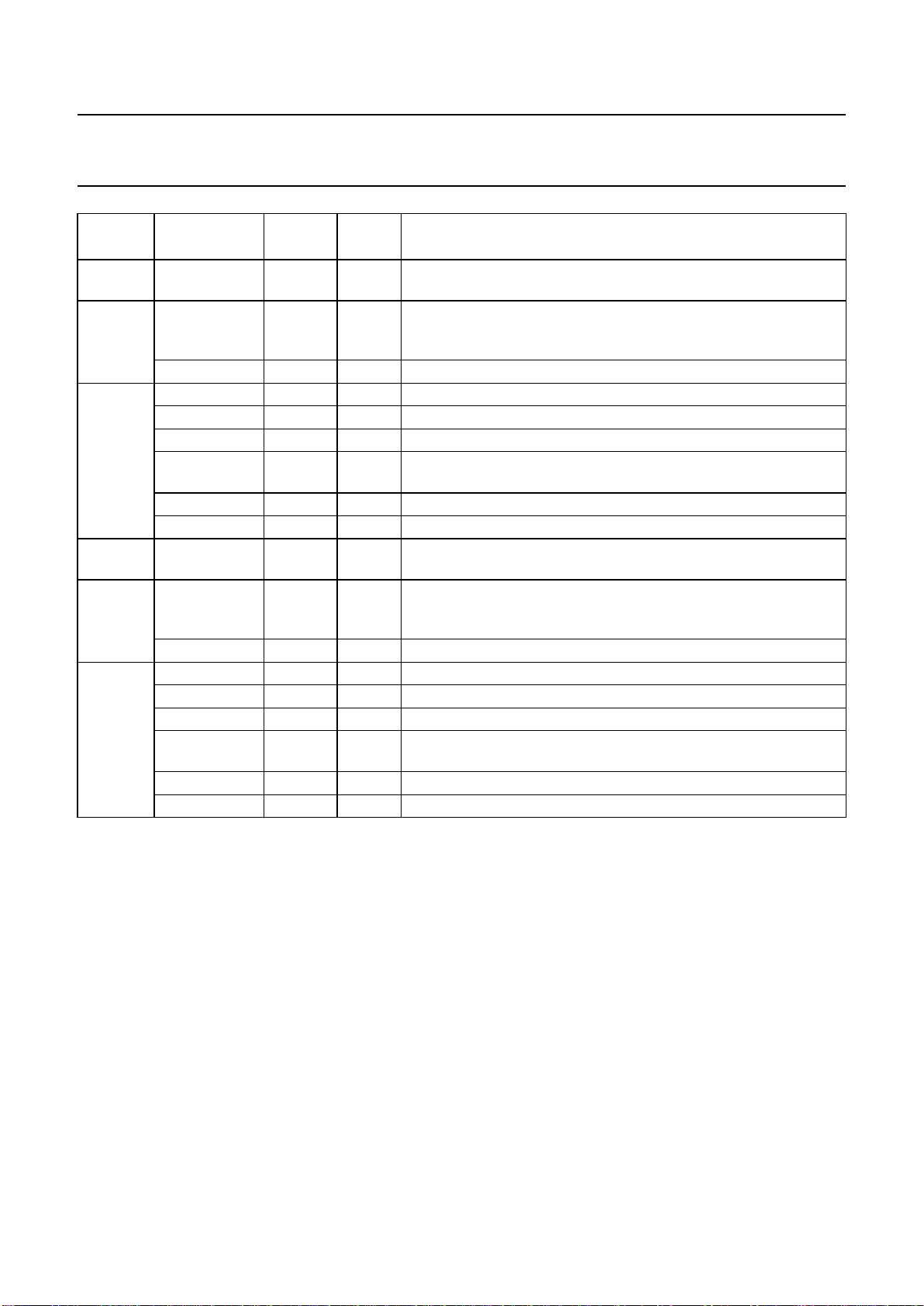

5 BLOCK DIAGRAM

6 PINNING

7 FUNCTIONAL DESCRIPTION

7.1 General

7.2 PCI interface

7.3 Main control

7.4 Register Programming Sequencer (RPS)

7.5 Status and interrupts

7.6 General Purpose Inputs/Outputs (GPIO)

7.7 Event counter

7.8 Video processing

7.9 High Performance Scaler (HPS)

7.10 Binary Ratio Scaler (BRS)

7.11 Video data formats on the PCI-bus

7.12 Scaler register

7.13 Scaler event description

7.14 Clipping

7.15 Data Expansion Bus Interface (DEBI)

7.16 Audio interface

7.17 I2C-bus interface

7.18 SAA7146A register tables

8 BOUNDARY SCAN TEST

8.1 Initialization of boundary scan circuit

8.2 Device identification codes

9 ELECTRICAL OPERATING CONDITIONS

10 CHARACTERISTICS

11 APPLICATION EXAMPLE

12 PACKAGE OUTLINES

13 SOLDERING

13.1 Introduction

13.2 Reflow soldering

13.3 Wave soldering

13.4 Repairing soldered joints

14 DEFINITIONS

15 LIFE SUPPORT APPLICATIONS

16 PURCHASE OF PHILIPS I2C COMPONENTS

1998 Apr 09 3

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

1 FEATURES

1.1 Video processing

• Full size, full speed video delivery to and from the frame

buffer or virtual system memory enables various

processing possibilities for any external PCI device

• Full bandwidth PCI-bus master write and read (up to

132 Mbytes/s)

• Virtual memory support (4 Mbytes per DMA channel)

• Processing of maximum 4095 active samples per line

and maximum 4095 lines per frame

• Vanity picture (mirror) for video phone and video

conferencing applications

• Video flip (upside down picture)

• Colour space conversion with gamma correction for

different kinds of displays

• Chroma Key generation and utilization

• Pixel dithering for low resolution video output formats

• Brightness, contrast and saturation control

• Video and Vertical Blanking Interval (VBI) synchronized

programming of internal registers with Register

Programming Sequencer (RPS), ability to control two

asynchronous data streams simultaneously

• Memory Management Unit (MMU) supports virtual

demand paging memory management (Windows, Unix,

etc.)

• Rectangular clipping of frame buffer areas minimizes

PCI-bus load

• Random shape mask clipping protects selectable areas

of frame buffer

• 3 × 128 Dword video FIFO with overflow detection and

‘graceful’ recovery.

1.2 Audio processing

• Time Slot List (TSL) processing for flexible control of

audio frames up to 256 bits on 2 asynchronous

bidirectional digital audio interfaces simultaneously

(4 DMA channels)

• Video synchronous audio capture, e.g. for sound cards

• Various synchronization modes to support I

2

S and other

different audio and DSP data formats

• Audio input level monitoring enables peak control via

software

• Programmable bit clock generation for master and slave

applications.

1.3 Scaling

• Scaling of video pictures down to randomly sized

windows (vertical down to 1 : 1024; horizontal down to

1 : 256)

• High Performance Scaler (HPS) offers two-dimensional,

phase correct data processing for improved signal

quality of scaled video data, especially for compression

applications

• Horizontal and vertical FIR filters with up to 65 taps

• Horizontal upscaling (zoom) supports e.g. CCIR to

square pixel conversion

• Additional Binary Ratio Scaler (BRS) supports CIF and

QCIF formats, especially for video phone and video

conferencing.

1.4 Interfacing

• Dual D1 (8-bit, CCIR 656) video I/O interface

• DMSD2 compatible (16-bit YUV) video input interface

• Supports various packed (pixel dithering) and planar

video output formats

• Data Expansion Bus Interface (DEBI) for interfacing with

e.g. MPEG or JPEG decoders with Intel (ISA like) and

Motorola (68000 like) protocol style, capability for

immediate and block mode (DMA) transfers with up to

23 Mbytes/s peak data rate

• 5 digital audio I/O ports

• 4 independent user configurable General Purpose I/O

Ports (GPI/O) for interrupt and status processing

• PCI interface (release 2.1)

• I

2

C-bus interface (bus master).

1998 Apr 09 4

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

1.5 General

• Subsystem (board) vendor ID support for board

identification via software driver

• Internal arbitration control

• Diagnostic support and event analysis

• Programmable Vertical Blanking Interval (VBI) data

region for e.g. to support INTERCAST, teletext, closed

caption and similar applications

• 3.3 V supply enables reduced power consumption, 5 V

tolerant I/Os for 5 V PCI signalling environment.

2 GENERAL DESCRIPTION

The SAA7146A, Multimedia PCI-bridge, is a highly

integrated circuit for DeskTop Video (DTV) applications.

The device provides a number of interface ports that

enable a wide variety of video and audio ICs to be

connected to the PCI-bus thus supporting a number of

video applications in a PC. One example of the application

capabilities is shown in Fig.49.

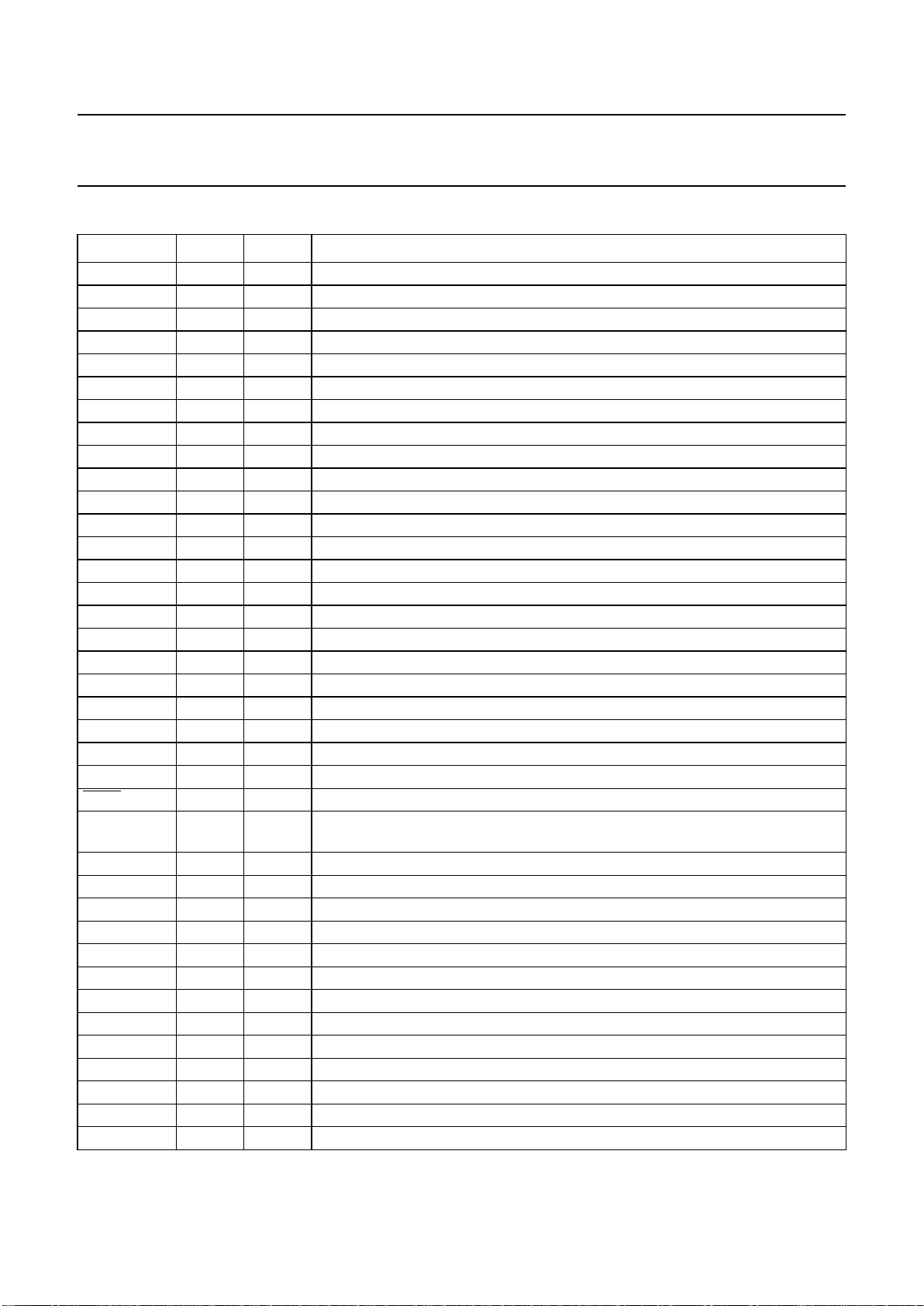

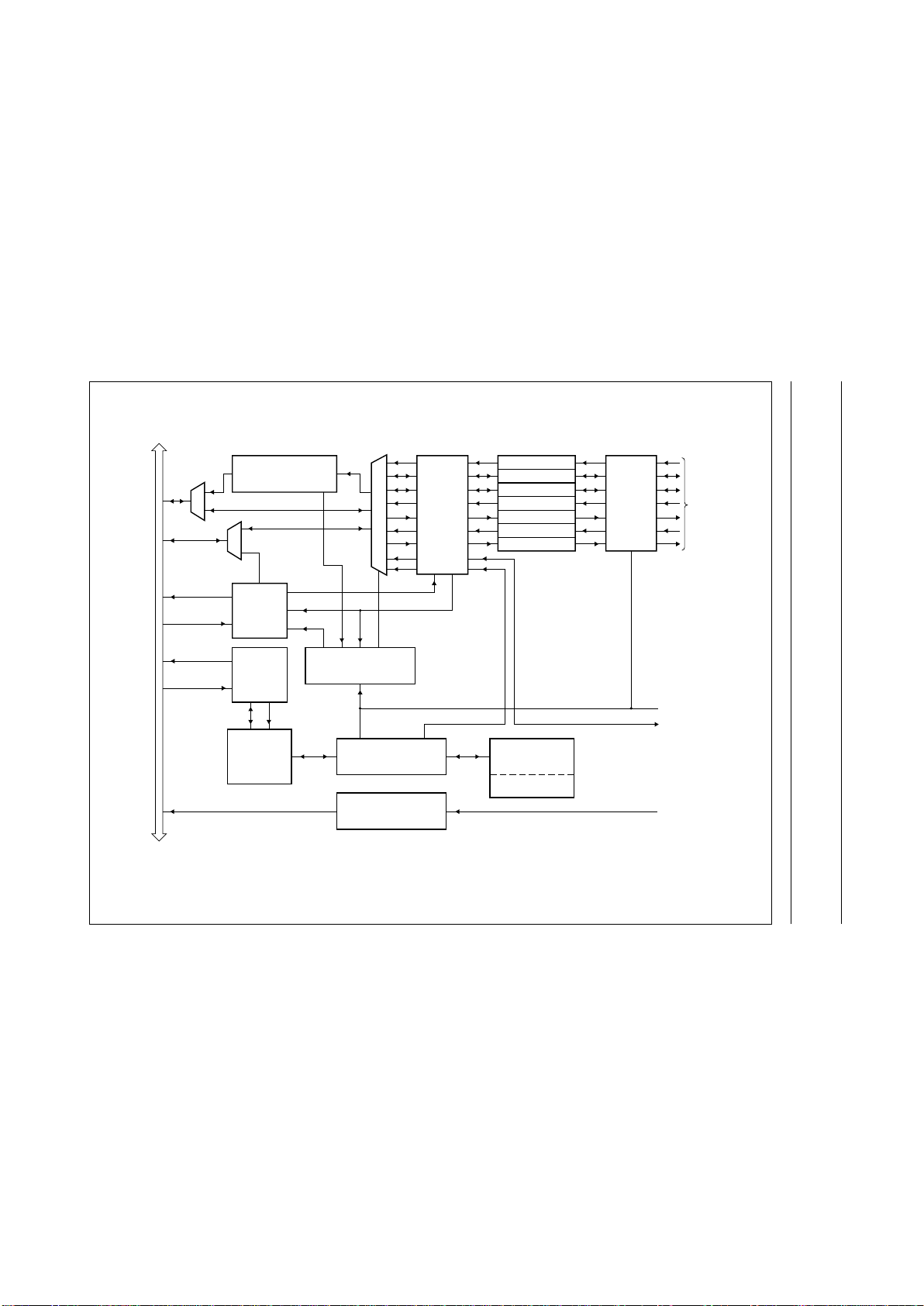

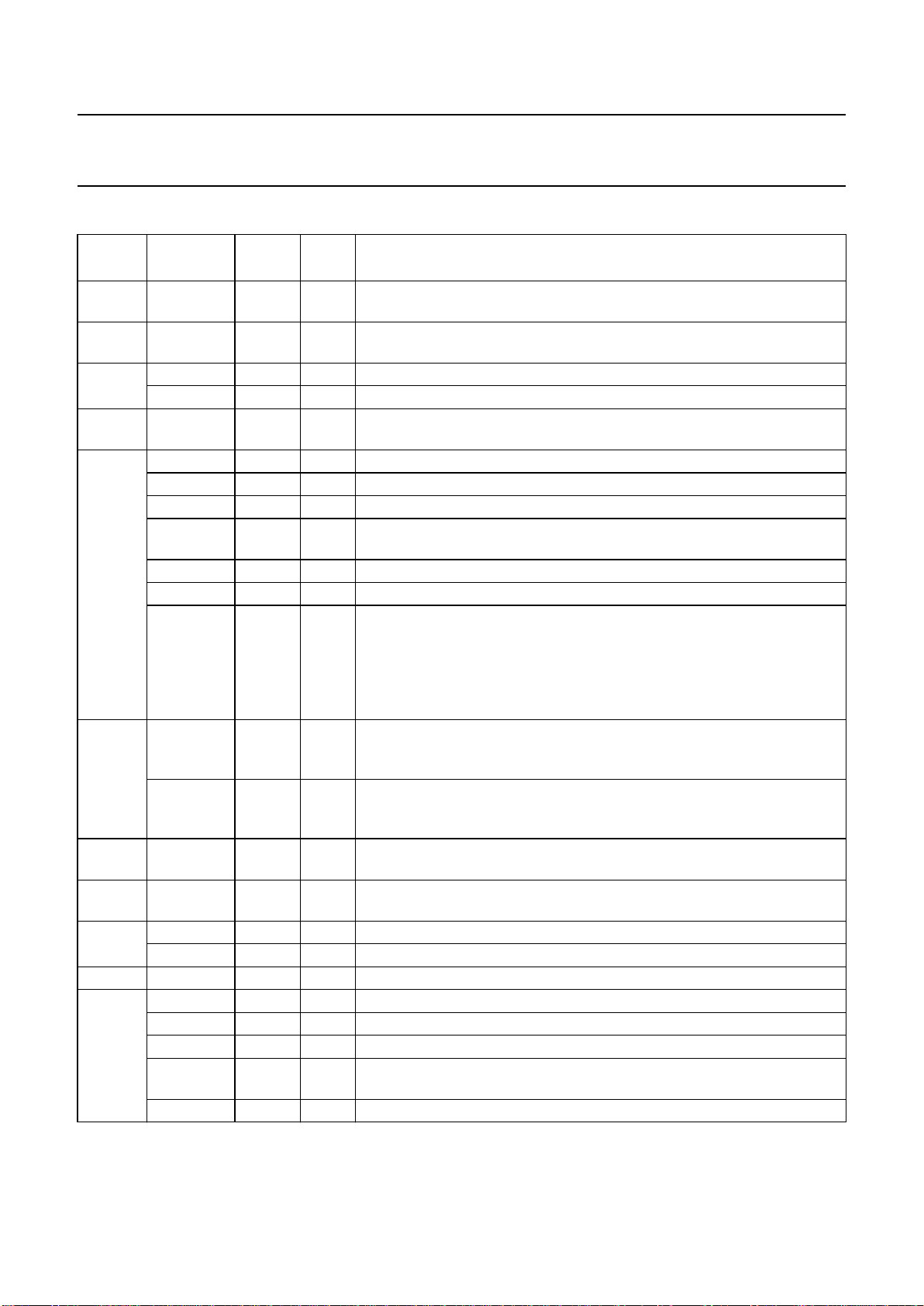

Figure 1 shows the various interface ports and the main

internal function blocks.

3 QUICK REFERENCE DATA

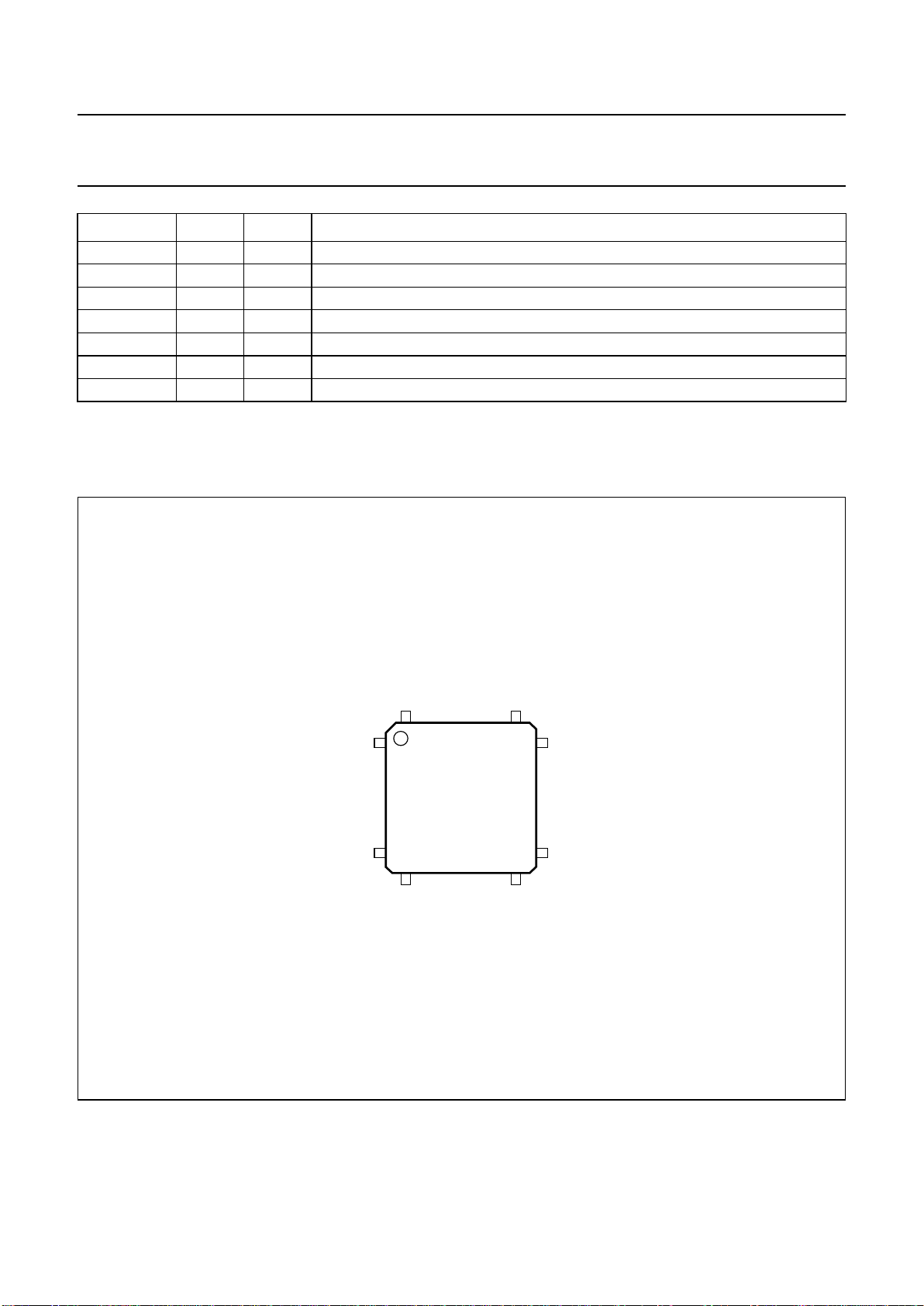

4 ORDERING INFORMATION

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DDD

digital supply voltage 3.0 3.3 3.6 V

I

DDD(tot)

total digital supply current − 400 − mA

V

i;Vo

data input/output levels TTL compatible

f

LLC

LLC input clock frequency −−32 MHz

f

PCI

PCI input clock frequency −−33 MHz

f

I2S

I2S input clock frequency −−12.5 MHz

T

amb

operating ambient temperature 0 − 70 °C

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

SAA7146AH QFP160 plastic quad flat package; 160 leads (lead length 1.95 mm);

body 28 × 28 × 3.4 mm; high stand-off height

SOT322-1

SAA7146AHZ SQFP208 plastic shrink quad flat package; 208 leads (lead length 1.3 mm);

body 28 × 28 × 3.4 mm

SOT316-1

1998 Apr 09 5

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

5 BLOCK DIAGRAM

o

k, full pagewidth

MHB044

GPIO PORTI/O

RPS

SAA7146A

TASK 1

COLOUR SPACE CV. GAMMA CORRECTION

PIXEL-FORMATTER/DITHER

TASK 2

EVENT

MANAGER

I2C-BUS MASTER

control

data

I

2

C-bus

I

2

S1-bus

I

2

S2-bus

DEBI PORT

Intel/

Motorola

DEBI FIFO

AUDIO FIFO

PCI INTERFACE

PCI BUS

DMA AND INTERNAL ARBITRATION CONTROLLERMMU

TSL

AUDIO INPUT/OUTPUT

AUDIO INPUT/OUTPUT

VIDEO

FIFO1

VIDEO

FIFO2

CLIPPING

UNIT

BINARY

RATIO

SCALER

VIDEO

FIFO3

8-BIT D1 INPUT/OUTPUT 8-BIT D1 INPUT/OUTPUT

REAL TIME VIDEO INTERFACE

Dual D1 or 16-bit YUV

16-BIT YUV IN

HIGH PERFORMANCE SCALER

H-FILTER/SCALER

V-FILTER/SCALER

YUV/RGB

YUV

YUV

YUV

VIDEO-FLIP/MIRROR

Fig.1 Block diagram.

1998 Apr 09 6

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

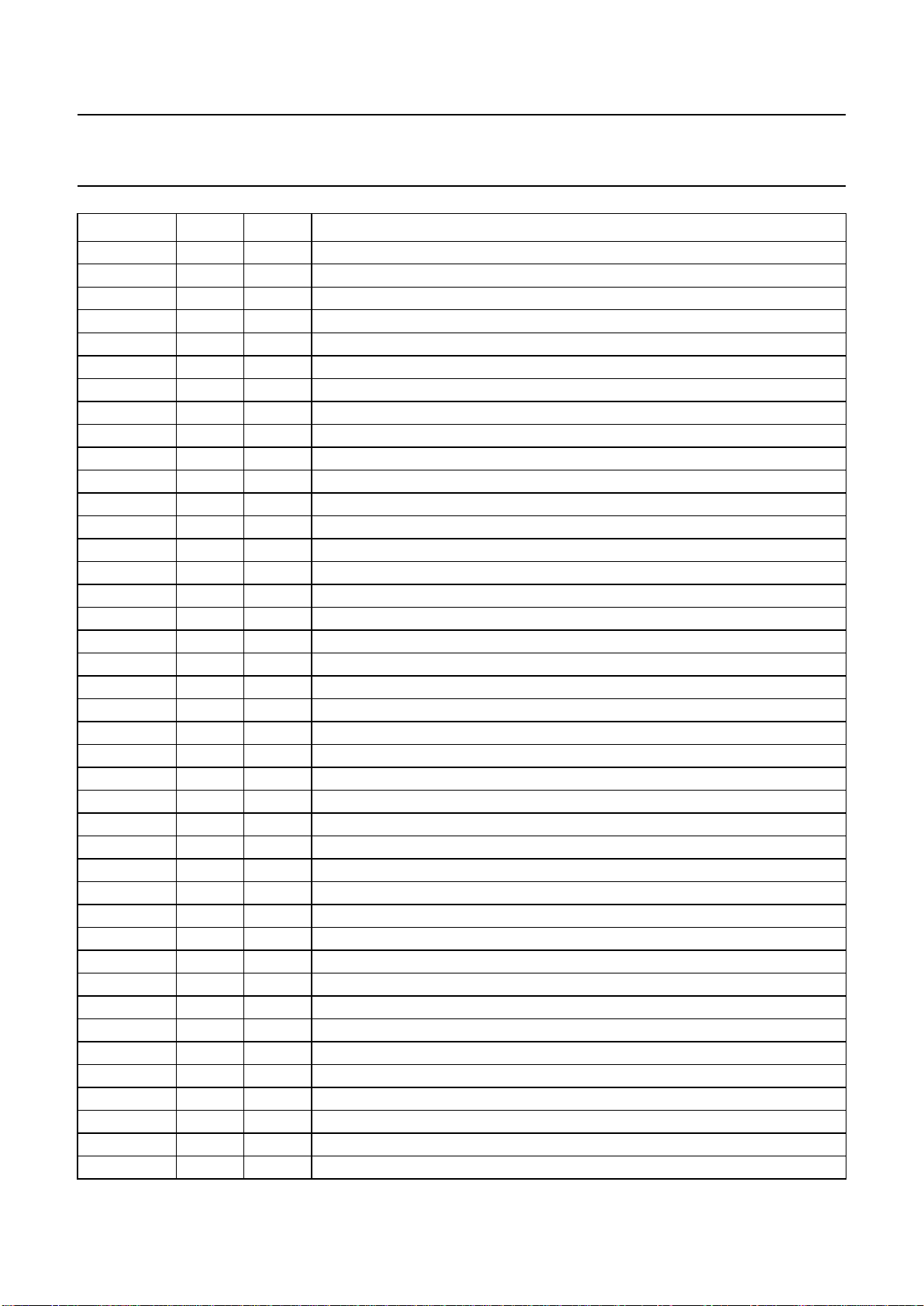

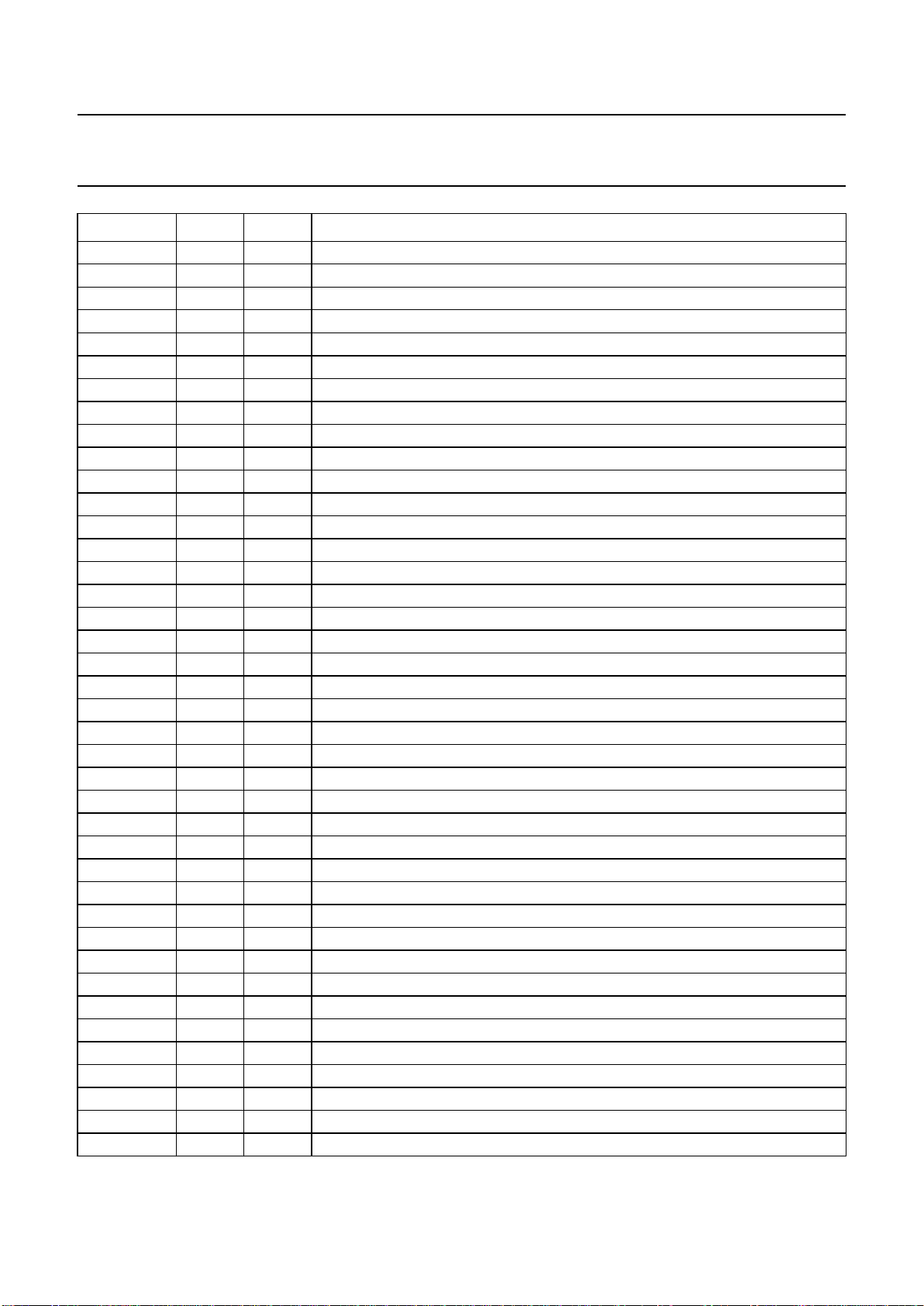

6 PINNING

Pin description for QFP160

SYMBOL PIN STATUS DESCRIPTION

D1_A0 1 I/O bidirectional digital CCIR 656 D1 port A bit 0

D1_A1 2 I/O bidirectional digital CCIR 656 D1 port A bit 1

D1_A2 3 I/O bidirectional digital CCIR 656 D1 port A bit 2

D1_A3 4 I/O bidirectional digital CCIR 656 D1 port A bit 3

V

DDD1

5 P digital supply voltage 1 (3.3 V)

V

SSD1

6 P digital ground 1

D1_A4 7 I/O bidirectional digital CCIR 656 D1 port A bit 4

D1_A5 8 I/O bidirectional digital CCIR 656 D1 port A bit 5

D1_A6 9 I/O bidirectional digital CCIR 656 D1 port A bit 6

D1_A7 10 I/O bidirectional digital CCIR 656 D1 port A bit 7

VS_A 11 I/O bidirectional vertical sync signal port A

HS_A 12 I/O bidirectional horizontal sync signal port A

LLC_A 13 I/O bidirectional line-locked system clock port A

PXQ_A 14 I/O bidirectional pixel qualifier signal to mark valid pixels port A; note 1

V

DDD2

15 P digital supply voltage 2 (3.3 V)

V

SSD2

16 P digital ground 2

TRST 17 I test reset input (JTAG pin must be set LOW for normal operation)

TMS 18 I test mode select input (JTAG pin must be floating or set to HIGH during normal

operation)

TCLK 19 I test clock input (JTAG pin should be set LOW during normal operation)

TDO 20 O test data output (JTAG pin not active during normal operation)

TDI 21 I test data input (JTAG pin must be floating or set to HIGH during normal operation)

V

DDD3

22 P digital supply voltage 3 (3.3 V)

V

SSD3

23 P digital ground 3

INTA# 24 O PCI interrupt line output (active LOW)

RST 25 I PCI global reset input (active LOW)

CLK 26 I PCI clock input

GNT# 27 I bus grant input signal, PCI arbitration signal (active LOW)

REQ# 28 O bus request output signal, PCI arbitration signal (active LOW)

V

DDD4

29 P digital supply voltage 4 (3.3 V)

V

SSD4

30 P digital ground 4

AD PCI31 31 I/O bidirectional PCI multiplexed address/data bit 31

AD PCI30 32 I/O bidirectional PCI multiplexed address/data bit 30

AD PCI29 33 I/O bidirectional PCI multiplexed address/data bit 29

AD PCI28 34 I/O bidirectional PCI multiplexed address/data bit 28

V

DDD5

35 P digital supply voltage 5 (3.3 V)

V

SSD5

36 P digital ground 5

AD PCI27 37 I/O bidirectional PCI multiplexed address/data bit 27

1998 Apr 09 7

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

AD PCI26 38 I/O bidirectional PCI multiplexed address/data bit 26

AD PCI25 39 I/O bidirectional PCI multiplexed address/data bit 25

AD PCI24 40 I/O bidirectional PCI multiplexed address/data bit 24

C/BE# [3] 41 I/O bidirectional PCI multiplexed bus command and byte enable 3 (active LOW)

IDSEL 42 I PCI initialization device select signal input

AD PCI23 43 I/O bidirectional PCI multiplexed address/data bit 23

AD PCI22 44 I/O bidirectional PCI multiplexed address/data bit 22

AD PCI21 45 I/O bidirectional PCI multiplexed address/data bit 21

AD PCI20 46 I/O bidirectional PCI multiplexed address/data bit 20

V

DDD6

47 P digital supply voltage 6 (3.3 V)

V

SSD6

48 P digital ground 6

AD PCI19 49 I/O bidirectional PCI multiplexed address/data bit 19

AD PCI18 50 I/O bidirectional PCI multiplexed address/data bit 18

AD PCI17 51 I/O bidirectional PCI multiplexed address/data bit 17

AD PCI16 52 I/O bidirectional PCI multiplexed address/data bit 16

V

DDD7

53 P digital supply voltage 7 (3.3 V)

V

SSD7

54 P digital ground 7

C/BE# [2] 55 I/O bidirectional PCI multiplexed bus command and byte enable 2 (active LOW)

FRAME# 56 I/O bidirectional PCI cycle frame signal (active LOW)

IRDY# 57 I/O bidirectional PCI initiator ready signal (active LOW)

TRDY# 58 I/O bidirectional PCI target ready signal (active LOW)

DEVSEL# 59 I/O bidirectional PCI device select signal (active LOW)

STOP# 60 I/O bidirectional PCI stop signal (active LOW)

PERR# 61 O PCI parity error signal output (active LOW)

PAR 62 I/O bidirectional PCI parity signal

C/BE# [1] 63 I/O bidirectional PCI-bus command and byte enable 1 (active LOW)

V

DDD8

64 P digital supply voltage 8 (3.3 V)

V

SSD8

65 P digital ground 8

AD PCI15 66 I/O bidirectional PCI multiplexed address/data bit 15

AD PCI14 67 I/O bidirectional PCI multiplexed address/data bit 14

AD PCI13 68 I/O bidirectional PCI multiplexed address/data bit 13

AD PCI12 69 I/O bidirectional PCI multiplexed address/data bit 12

V

DDD9

70 P digital supply voltage 9 (3.3 V)

V

SSD9

71 P digital ground 9

AD PCI11 72 I/O bidirectional PCI multiplexed address/data bit 11

AD PCI10 73 I/O bidirectional PCI multiplexed address/data bit 10

AD PCI9 74 I/O bidirectional PCI multiplexed address/data bit 9

AD PCI8 75 I/O bidirectional PCI multiplexed address/data bit 8

V

DDD10

76 P digital supply voltage 10 (3.3 V)

V

SSD10

77 P digital ground 10

C/BE# [0] 78 I/O bidirectional PCI multiplexed bus command and byte enable 0 (active LOW)

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 8

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

AD PCI7 79 I/O bidirectional PCI multiplexed address/data bit 7

AD PCI6 80 I/O bidirectional PCI multiplexed address/data bit 6

V

SSD11

81 P digital ground 11

AD PCI5 82 I/O bidirectional PCI multiplexed address/data bit 5

AD PCI4 83 I/O bidirectional PCI multiplexed address/data bit 4

AD PCI3 84 I/O bidirectional PCI multiplexed address/data bit 3

AD PCI2 85 I/O bidirectional PCI multiplexed address/data bit 2

V

DDD11

86 P digital supply voltage 11 (3.3 V)

V

SSD12

87 P digital ground 12

AD PCI1 88 I/O bidirectional PCI multiplexed address/data bit 1

AD PCI0 89 I/O bidirectional PCI multiplexed address/data bit 0

V

DDD12

90 P digital supply voltage 12 (3.3 V)

V

SSD13

91 P digital ground 13

AD15 92 I/O bidirectional DEBI multiplexed address data line bit 15

AD14 93 I/O bidirectional DEBI multiplexed address data line bit 14

AD13 94 I/O bidirectional DEBI multiplexed address data line bit 13

AD12 95 I/O bidirectional DEBI multiplexed address data line bit 12

V

DDD13

96 P digital supply voltage 13 (3.3 V)

V

SSD14

97 P digital ground 14

AD11 98 I/O bidirectional DEBI multiplexed address data line bit 11

AD10 99 I/O bidirectional DEBI multiplexed address data line bit 10

AD9 100 I/O bidirectional DEBI multiplexed address data line bit 9

AD8 101 I/O bidirectional DEBI multiplexed address data line bit 8

V

DDD14

102 P digital supply voltage 14 (3.3 V)

V

SSD15

103 P digital ground 15

RWN_SBHE 104 O DEBI data transfer control signal output (read write not/system byte high enable)

AS_ALE 105 O DEBI address strobe and address latch enable output

LDS_RDN 106 O lower data strobe/read not output

UDS_WRN 107 O upper data strobe/write not output

DTACK_RDY 108 I DEBI data transfer acknowledge or ready input

V

DDD15

109 P digital supply voltage 15 (3.3 V)

V

SSD16

110 P digital ground 16

AD0 111 I/O bidirectional DEBI multiplexed address data line bit 0

AD1 112 I/O bidirectional DEBI multiplexed address data line bit 1

AD2 113 I/O bidirectional DEBI multiplexed address data line bit 2

AD3 114 I/O bidirectional DEBI multiplexed address data line bit 3

V

DDD16

115 P digital supply voltage 16 (3.3 V)

V

SSD17

116 P digital ground 17

AD4 117 I/O bidirectional DEBI multiplexed address data line bit 4

AD5 118 I/O bidirectional DEBI multiplexed address data line bit 5

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 9

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

AD6 119 I/O bidirectional DEBI multiplexed address data line bit 6

AD7 120 I/O bidirectional DEBI multiplexed address data line bit 7

WS0 121 I/O bidirectional word select signal for audio interface A1

SD0 122 I/O bidirectional serial data for audio interface A1

BCLK1 123 I/O bidirectional bit clock for audio interface A1

WS1 124 O word select output signal for audio interface A1/A2

SD1 125 I/O bidirectional serial data for audio interface A1/A2

WS2 126 O word select output signal for audio interface A1/A2

SD2 127 I/O bidirectional serial data for audio interface A1/A2

V

DDD17

128 P digital supply voltage 17 (3.3 V)

V

SSD18

129 P digital ground 18

WS3 130 O word select output signal for audio interface A1/A2

SD3 131 I/O bidirectional serial data for audio interface A1/A2

BCLK2 132 I/O bidirectional bit clock for audio interface A2

WS4 133 I/O bidirectional word select signal for audio interface A2

SD4 134 I/O bidirectional serial data for audio interface A2

ACLK 135 I audio reference clock input signal

SCL 136 I/O bidirectional I

2

C-bus clock line

SDA 137 I/O bidirectional I

2

C-bus data line

V

DDD18

138 P digital supply voltage 18 (3.3 V)

V

DDI2C

139 I I2C-bus voltage sense input; see note 3 of “Characteristics”

V

SSD19

140 P digital ground 19

GPIO3 141 I/O general purpose I/O signal 3

GPIO2 142 I/O general purpose I/O signal 2

GPIO1 143 I/O general purpose I/O signal 1

GPIO0 144 I/O general purpose I/O signal 0

D1_B0 145 I/O bidirectional digital CCIR 656 D1 port B bit 0

D1_B1 146 I/O bidirectional digital CCIR 656 D1 port B bit 1

D1_B2 147 I/O bidirectional digital CCIR 656 D1 port B bit 2

D1_B3 148 I/O bidirectional digital CCIR 656 D1 port B bit 3

V

DDD19

149 P digital supply voltage 19 (3.3 V)

V

SSD20

150 P digital ground 20

D1_B4 151 I/O bidirectional digital CCIR 656 D1 port B bit 4

D1_B5 152 I/O bidirectional digital CCIR 656 D1 port B bit 5

D1_B6 153 I/O bidirectional digital CCIR 656 D1 port B bit 6

D1_B7 154 I/O bidirectional digital CCIR 656 D1 port B bit 7

V

DDD20

155 P digital supply voltage 20 (3.3 V)

V

SSD21

156 P digital ground 21

LLC_B 157 I/O bidirectional line-locked system clock port B

VS_B 158 I/O bidirectional vertical sync signal port B

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 10

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

Notes

1. For continuous CCIR 656 format at the D1_A port this pin must be set HIGH.

2. For continuous CCIR 656 format at the D1_B port this pin must be set HIGH.

HS_B 159 I/O bidirectional horizontal sync signal port B

PXQ_B 160 I/O bidirectional pixel qualifier signal to mark valid pixels port B; note 2

SYMBOL PIN STATUS DESCRIPTION

Fig.2 Pin configuration SAA7146AH (QFP160).

handbook, halfpage

SAA7146AH

1

160

121

41

80

40

120

81

MHB045

1998 Apr 09 11

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

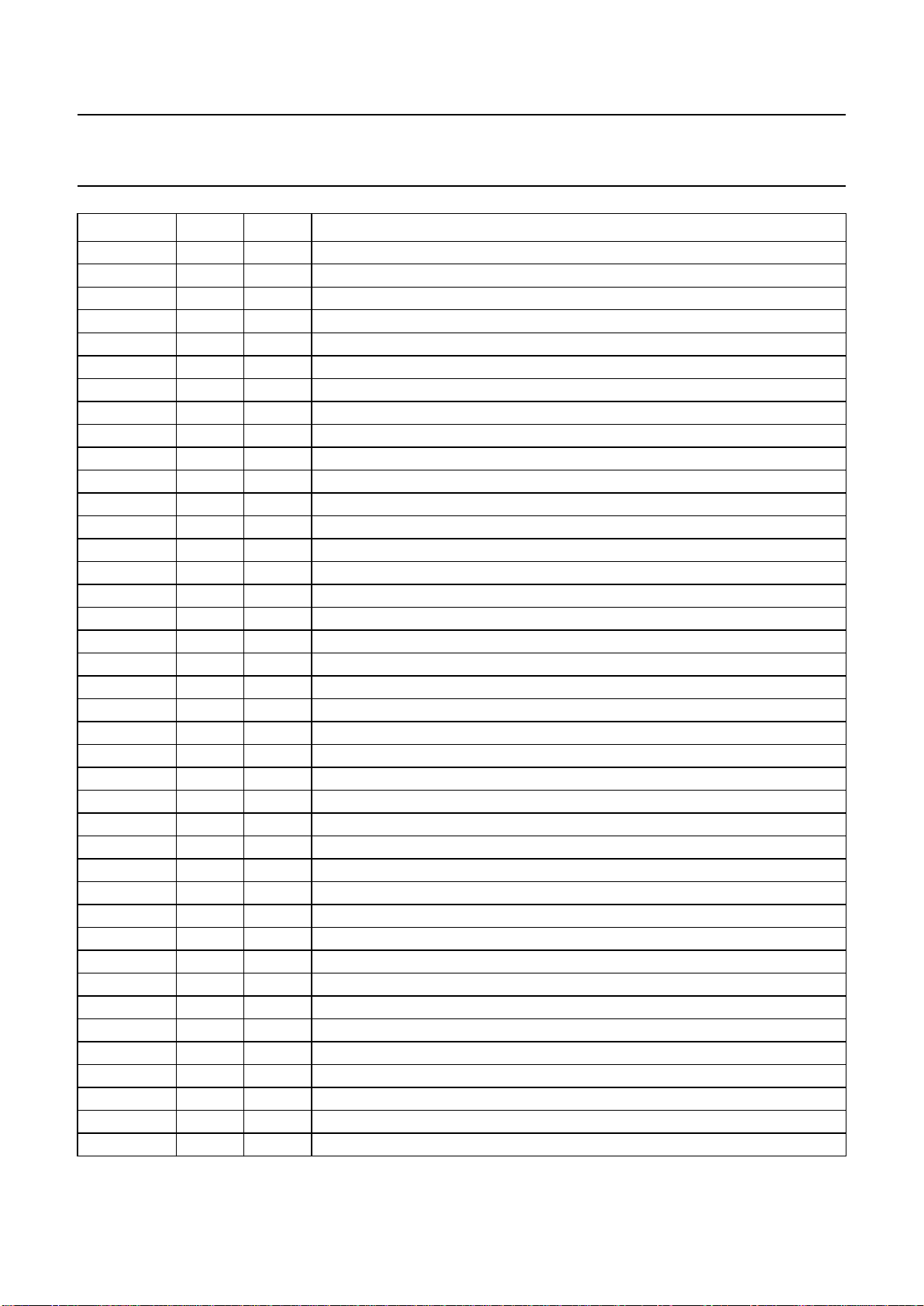

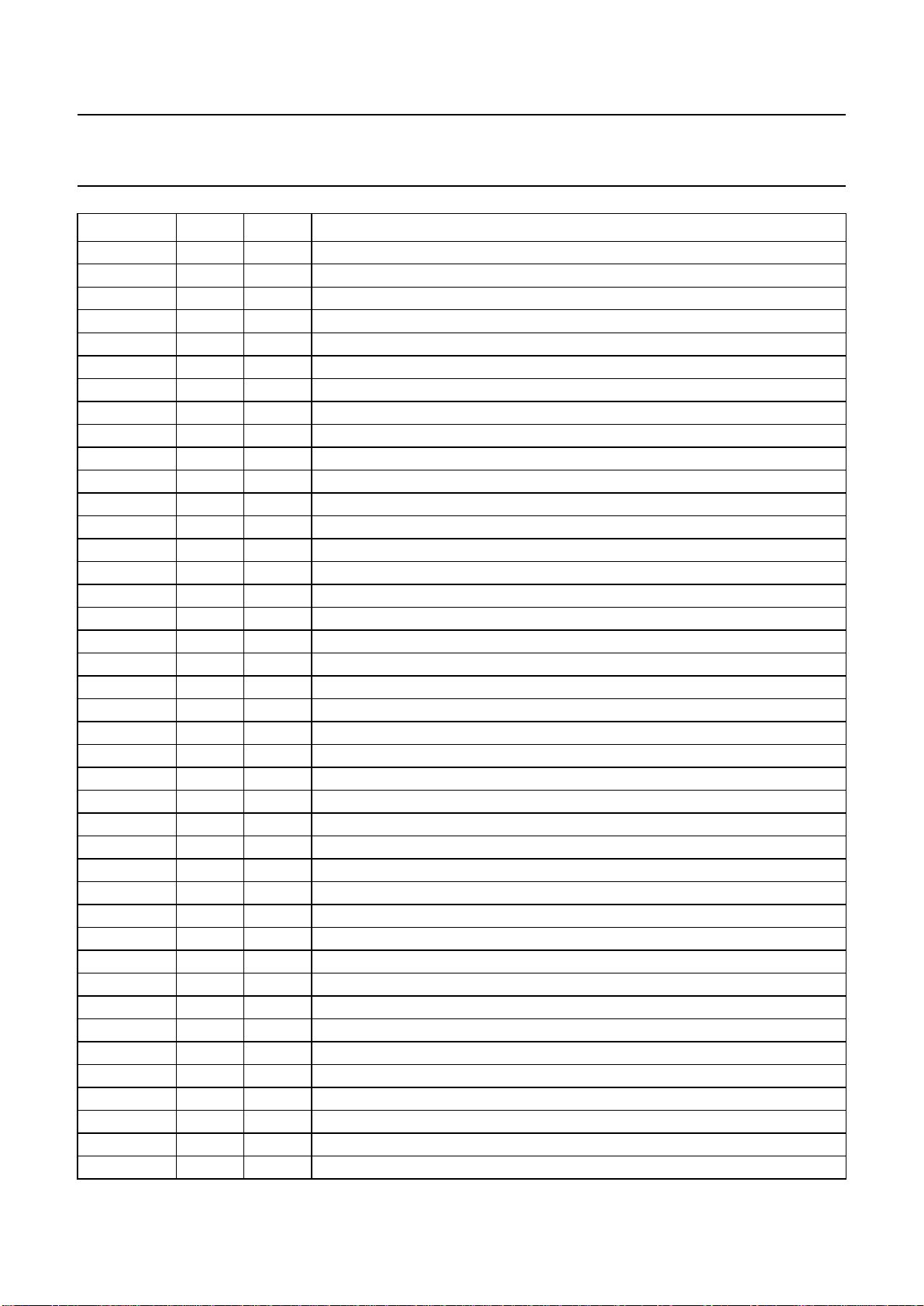

Pin description for SQFP208

SYMBOL PIN STATUS DESCRIPTION

V

SSD0

1 P digital ground 0

D1_A0 2 I/O bidirectional digital CCIR 656 D1 port A bit 0

D1_A1 3 I/O bidirectional digital CCIR 656 D1 port A bit 1

D1_A2 4 I/O bidirectional digital CCIR 656 D1 port A bit 2

D1_A3 5 I/O bidirectional digital CCIR 656 D1 port A bit 3

V

DDD1

6 P digital supply voltage 1 (3.3 V)

n.c. 7 − reserved pin; not connected internally

V

SSD1

8 P digital ground 1

D1_A4 9 I/O bidirectional digital CCIR 656 D1 port A bit 4

D1_A5 10 I/O bidirectional digital CCIR 656 D1 port A bit 5

D1_A6 11 I/O bidirectional digital CCIR 656 D1 port A bit 6

D1_A7 12 I/O bidirectional digital CCIR 656 D1 port A bit 7

V

DDD2

13 P digital supply voltage 2 (3.3 V)

n.c. 14 − reserved pin; not connected internally

V

SSD2

15 P digital ground 2

VS_A 16 I/O bidirectional vertical sync signal port A

HS_A 17 I/O bidirectional horizontal sync signal port A

LLC_A 18 I/O bidirectional line-locked system clock port A

PXQ_A 19 I/O bidirectional pixel qualifier signal to mark valid pixels port A; note 1

n.c. 20 − reserved pin; do not connect

V

DDD3

21 P digital supply voltage 3 (3.3 V)

n.c. 22 − reserved pin; not connected internally

V

SSD3

23 P digital ground 3

TRST 24 I test reset input (JTAG pin must be set LOW for normal operation)

TMS 25 I test mode select input (JTAG pin must be floating or set to HIGH during normal

operation)

TCLK 26 I test clock input (JTAG pin should be set LOW during normal operation)

TDO 27 O test data output (JTAG pin not active during normal operation)

TDI 28 I test data input (JTAG pin must be floating or set to HIGH during normal operation)

V

DDD4

29 P digital supply voltage 4 (3.3 V)

n.c. 30 − reserved pin; not connected internally

V

SSD4

31 P digital ground 4

INTA# 32 O PCI interrupt line output (active LOW)

RST# 33 I PCI global reset input (active LOW)

CLK 34 I PCI clock input

GNT# 35 I bus grant input signal input, PCI arbitration signal (active LOW)

REQ# 36 O bus request output signal output, PCI arbitration signal (active LOW)

V

DDD5

37 P digital supply voltage 5 (3.3 V)

n.c. 38 − reserved pin; not connected internally

1998 Apr 09 12

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

V

SSD5

39 P digital ground 5

AD PCI31 40 I/O bidirectional PCI multiplexed address/data bit 31

AD PCI30 41 I/O bidirectional PCI multiplexed address/data bit 30

AD PCI29 42 I/O bidirectional PCI multiplexed address/data bit 29

AD PCI28 43 I/O bidirectional PCI multiplexed address/data bit 28

V

DDD6

44 P digital supply voltage 6 (3.3 V)

n.c. 45 − reserved pin; not connected internally

V

SSD6

46 P digital ground 6

AD PCI27 47 I/O bidirectional PCI multiplexed address/data bit 27

AD PCI26 48 I/O bidirectional PCI multiplexed address/data bit 26

AD PCI25 49 I/O bidirectional PCI multiplexed address/data bit 25

AD PCI24 50 I/O bidirectional PCI multiplexed address/data bit 24

V

DDD7

51 P digital supply voltage 7 (3.3 V)

n.c. 52 − reserved pin; do not connect

n.c. 53 − reserved pin; not connected internally

V

SSD7

54 P digital ground 7

C/BE# [3] 55 I/O bidirectional PCI multiplexed bus command and byte enable 3 (active LOW)

IDSEL 56 I PCI initialization device select input signal

AD PCI23 57 I/O bidirectional PCI multiplexed address/data bit 23

AD PCI22 58 I/O bidirectional PCI multiplexed address/data bit 22

AD PCI21 59 I/O bidirectional PCI multiplexed address/data bit 21

AD PCI20 60 I/O bidirectional PCI multiplexed address/data bit 20

n.c. 61 − reserved pin; do not connect

n.c. 62 − reserved pin; not connected internally

V

SSD8

63 P digital ground 8

AD PCI19 64 I/O bidirectional PCI multiplexed address/data bit 19

AD PCI18 65 I/O bidirectional PCI multiplexed address/data bit 18

AD PCI17 66 I/O bidirectional PCI multiplexed address/data bit 17

AD PCI16 67 I/O bidirectional PCI multiplexed address/data bit 16

V

DDD8

68 P digital supply voltage 8 (3.3 V)

n.c. 69 − reserved pin; do not connect

V

SSD9

70 P digital ground 9

C/BE# [2] 71 I/O bidirectional PCI multiplexed bus command and byte enable 2 (active LOW)

FRAME# 72 I/O bidirectional PCI cycle frame signal (active LOW)

IRDY# 73 I/O bidirectional PCI initiator ready signal (active LOW)

TRDY# 74 I/O bidirectional PCI target ready signal (active LOW)

V

DDD9

75 P digital supply voltage 9 (3.3 V)

n.c. 76 − reserved pin; do not connect

V

SSD10

77 P digital ground 10

DEVSEL# 78 I/O bidirectional PCI device select signal (active LOW)

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 13

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

STOP# 79 I/O bidirectional PCI stop signal (active LOW)

PERR# 80 O PCI parity error output signal (active LOW)

n.c. 81 − reserved pin; do not connect

PAR 82 I/O bidirectional PCI parity signal

C/BE# [1] 83 I/O bidirectional PCI-bus command and byte enable 1 (active LOW)

V

DDD10

84 P digital supply voltage 10 (3.3 V)

n.c. 85 − reserved pin; not connected internally

V

SSD11

86 P digital ground 11

AD PCI15 87 I/O bidirectional PCI multiplexed address/data bit 15

AD PCI14 88 I/O bidirectional PCI multiplexed address/data bit 14

AD PCI13 89 I/O bidirectional PCI multiplexed address/data bit 13

AD PCI12 90 I/O bidirectional PCI multiplexed address/data bit 12

V

DDD11

91 P digital supply voltage 11 (3.3 V)

n.c. 92 − reserved pin; not connected internally

V

SSD12

93 P digital ground 12

AD PCI11 94 I/O bidirectional PCI multiplexed address/data bit 11

AD PCI10 95 I/O bidirectional PCI multiplexed address/data bit 10

AD PCI9 96 I/O bidirectional PCI multiplexed address/data bit 9

AD PCI8 97 I/O bidirectional PCI multiplexed address/data bit 8

n.c. 98 − reserved pin; do not connect

n.c. 99 − reserved pin; not connected internally

V

SSD13

100 P digital ground 13

C/BE# [0] 101 I/O bidirectional PCI multiplexed bus command and byte enable (active LOW)

AD PCI7 102 I/O bidirectional PCI multiplexed address/data bit 7

AD PCI6 103 I/O bidirectional PCI multiplexed address/data bit 6

V

DDD12

104 P digital supply voltage 12 (3.3 V)

n.c. 105 − reserved pin; do not connect

n.c. 106 − reserved pin; not connected internally

V

SSD14

107 P digital ground 14

AD PCI5 108 I/O bidirectional PCI multiplexed address/data bit 5

AD PCI4 109 I/O bidirectional PCI multiplexed address/data bit 4

AD PCI3 110 I/O bidirectional PCI multiplexed address/data bit 3

AD PCI2 111 I/O bidirectional PCI multiplexed address/data bit 2

V

DDD13

112 P digital supply voltage 13 (3.3 V)

n.c. 113 − reserved pin; not connected internally

V

SSD15

114 P digital ground 15

AD PCI1 115 I/O bidirectional PCI multiplexed address/data bit 1

AD PCI0 116 I/O bidirectional PCI multiplexed address/data bit 0

V

DDD14

117 P digital supply voltage 14 (3.3 V)

n.c. 118 − reserved pin; not connected internally

V

SSD16

119 P digital ground 16

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 14

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

AD15 120 I/O bidirectional DEBI multiplexed address data line bit 15

AD14 121 I/O bidirectional DEBI multiplexed address data line bit 14

AD13 122 I/O bidirectional DEBI multiplexed address data line bit 13

AD12 123 I/O bidirectional DEBI multiplexed address data line bit 12

V

DDD15

124 P digital supply voltage 15 (3.3 V)

n.c. 125 − reserved pin; not connected internally

V

SSD17

126 P digital ground 17

AD11 127 I/O bidirectional DEBI multiplexed address data line bit 11

AD10 128 I/O bidirectional DEBI multiplexed address data line bit 10

AD9 129 I/O bidirectional DEBI multiplexed address data line bit 9

AD8 130 I/O bidirectional DEBI multiplexed address data line bit 8

V

DDD16

131 P digital supply voltage 16 (3.3 V)

n.c. 132 − reserved pin; not connected internally

V

SSD18

133 P digital ground 18

RWN_SBHE 134 O DEBI data transfer control output signal (read write not/system byte high enable)

AS_ALE 135 O DEBI address strobe and address latch enable output

LDS_RDN 136 O lower data strobe/read not output

UDS_WRN 137 O upper data strobe/write not output

DTACK_RDY 138 I DEBI data transfer acknowledge or ready input

V

DDD17

139 P digital supply voltage 17 (3.3 V)

n.c. 140 − reserved pin; not connected internally

V

SSD19

141 P digital ground 19

AD0 142 I/O bidirectional DEBI multiplexed address data line bit 0

AD1 143 I/O bidirectional DEBI multiplexed address data line bit 1

AD2 144 I/O bidirectional DEBI multiplexed address data line bit 2

AD3 145 I/O bidirectional DEBI multiplexed address data line bit 3

V

DDD18

146 P digital supply voltage 18 (3.3 V)

n.c. 147 − reserved pin; not connected internally

V

SSD20

148 P digital ground 20

AD4 149 I/O bidirectional DEBI multiplexed address data line bit 4

AD5 150 I/O bidirectional DEBI multiplexed address data line bit 5

AD6 151 I/O bidirectional DEBI multiplexed address data line bit 6

AD7 152 I/O bidirectional DEBI multiplexed address data line bit 7

n.c. 153 − reserved pin; do not connect

n.c. 154 − reserved pin; do not connect

V

DDD19

155 P digital supply voltage 19 (3.3 V)

n.c. 156 − reserved pin; not connected internally

n.c. 157 − reserved pin; do not connect

V

SSD21

158 P digital ground 21

WS0 159 I/O bidirectional word select signal for audio interface A1

SD0 160 I/O bidirectional serial data for audio interface A1

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 15

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

BCLK1 161 I/O bidirectional bit clock for audio interface A1

WS1 162 O word select output signal for audio interface A1/A2

SD1 163 I/O bidirectional serial data for audio interface A1/A2

WS2 164 O word select output signal for audio interface A1/A2

SD2 165 I/O bidirectional serial data for audio interface A1/A2

V

DDD20

166 P digital supply voltage 20 (3.3 V)

n.c. 167 − reserved pin; not connected internally

V

SSD22

168 P digital ground 22

WS3 169 O word select output signal for audio interface A1/A2

SD3 170 I/O bidirectional serial data for audio interface A1/A2

BCLK2 171 I/O bidirectional bit clock for audio interface A2

WS4 172 I/O bidirectional word select signal for audio interface A2

SD4 173 I/O bidirectional serial data for audio interface A2

ACLK 174 I audio reference clock input signal

SCL 175 I/O bidirectional I

2

C-bus clock line

SDA 176 I/O bidirectional I

2

C-bus data line

V

DDD21

177 P digital supply voltage 21 (3.3 V)

V

DDI2C

178 I I2C-bus voltage sense input; see note 3 of “Characteristics”

V

SSD23

179 P digital ground 23

GPIO3 180 I/O general purpose I/O signal 3

GPIO2 181 I/O general purpose I/O signal 2

GPIO1 182 I/O general purpose I/O signal 1

GPIO0 183 I/O general purpose I/O signal 0

V

DDD22

184 P digital supply voltage 22 (3.3 V)

n.c. 185 − reserved pin; not connected internally

V

SSD24

186 P digital ground 24

D1_B0 187 I/O bidirectional digital CCIR 656 D1 port B bit 0

D1_B1 188 I/O bidirectional digital CCIR 656 D1 port B bit 1

D1_B2 189 I/O bidirectional digital CCIR 656 D1 port B bit 2

D1_B3 190 I/O bidirectional digital CCIR 656 D1 port B bit 3

V

DDD23

191 P digital supply voltage 23 (3.3 V)

n.c. 192 − reserved pin; not connected internally

V

SSD25

193 P digital ground 25

D1_B4 194 I/O bidirectional digital CCIR 656 D1 port B bit 4

D1_B5 195 I/O bidirectional digital CCIR 656 D1 port B bit 5

D1_B6 196 I/O bidirectional digital CCIR 656 D1 port B bit 6

D1_B7 197 I/O bidirectional digital CCIR 656 D1 port B bit 7

V

DDD24

198 P digital supply voltage 24 (3.3 V)

n.c. 199 − reserved pin; not connected internally

V

SSD26

200 P digital ground 26

LLC_B 201 I/O bidirectional line-locked system clock port B

SYMBOL PIN STATUS DESCRIPTION

1998 Apr 09 16

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

Notes

1. For continuous CCIR 656 format at the D1_A port this pin must be set HIGH.

2. For continuous CCIR 656 format at the D1_B port this pin must be set HIGH.

VS_B 202 I/O bidirectional vertical sync signal port B

HS_B 203 I/O bidirectional horizontal sync signal port B

PXQ_B 204 I/O bidirectional pixel qualifier signal to mark valid pixels port B; note 2

n.c. 205 − reserved pin; do not connect

V

DDD25

206 P digital supply voltage 25 (3.3 V)

n.c. 207 − reserved pin; not connected internally

n.c. 208 − reserved pin; do not connect

SYMBOL PIN STATUS DESCRIPTION

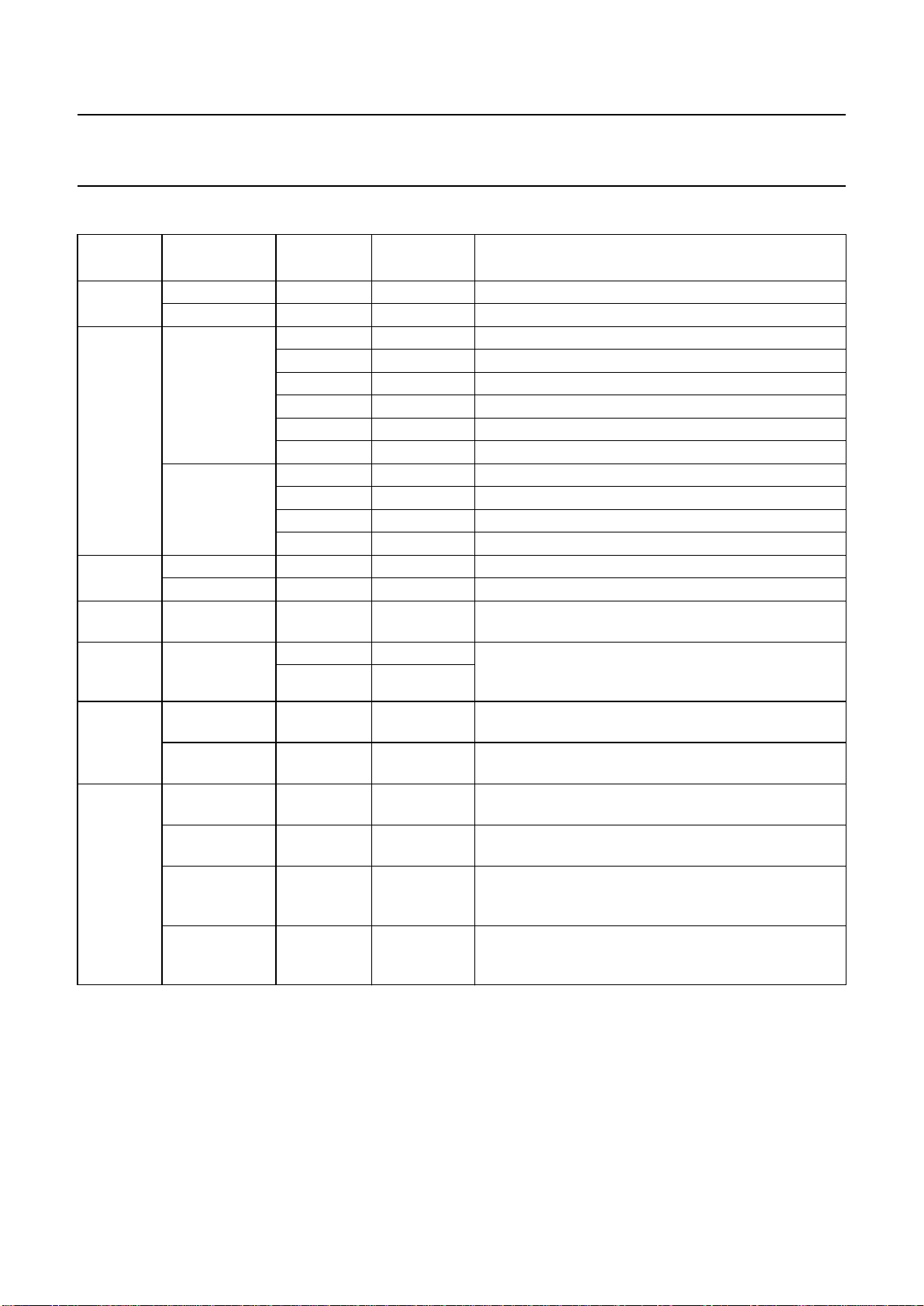

Fig.3 Pin configuration SAA7146AHZ (SQFP208).

handbook, halfpage

SAA7146AHZ

1

208

157

53

104

52

156

105

MHB046

1998 Apr 09 17

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

7 FUNCTIONAL DESCRIPTION

This chapter provides information about the features

realized with this device. First, a general, thus short,

description of the functionality is given. The following

sections deal with the single features in a detailed manner.

7.1 General

The Dual D1 (DD1) interface can be connected to digital

video decoder ICs such as the SAA7110 and SAA7111A,

digital video encoder such as the SAA7185B, video

compression CODECs or to a D1 compatible connector,

e.g. for interconnection to an external digital camera.

The interface supports bidirectional full duplex two channel

full D1 (CCIR 656), optionally with separate sync lines

H/V, pixel qualifier signal and double pixel clock I/O, up to

32 MHz. It also supports a 16-bit parallel ‘YUV bus’ for

interfacing to the SAA7110.

One of the two internal video processors of the SAA7146A

is the two-dimensional High Performance Scaler (HPS).

Phase accurate re-sampling by interpolation supports

independent horizontal up and downscaling. In the

horizontal direction the scaling process is performed in two

functional blocks: integer decimation by window averaging

(up to 65 tap), and phase linear interpolation (10 tap filter

for luminance, 6 tap filter for chrominance). The vertical

processing for downscaling either uses averaging over a

window (up to 65 tap) or linear interpolation (2 tap).

The scaling function can be used for random sized display

windowing, for horizontal upscaling (zoom) or for

conversion between various sample schemes such as

CCIR or SQP. Incorporated with the HPS function is

brightness, contrast and saturation control. Colour key

generation is also established. The output of the HPS can

be formatted in various RGB and YUV formats.

Additionally, this output can be dithered for low bit rate

formats. Packed formats as well as planar formats (YUV)

are supported.

A second video channel (YUV4:2:2 format) bypasses

the HPS and connects the real time video interface with

the PCI interface. This video bypass channel, using the

second video processor Binary Ratio Scaler (BRS), is

bidirectional and has means to convert from full size video

(50 or 60 Hz) to Common Interchange Format (CIF),

Quarter Common Interchange Format (QCIF) or Quarter

Quarter Common Interchange Format (QQCIF) and vice

versa (binary ratio 1, 2, 4, 8,

1

⁄2,1⁄4and1⁄8only). Multiple

programmable VBI data and test signal regions can be

bypassed without processing during each field.

The bidirectional digital audio serial interface is based on

the I

2

S-bus standard, but supports flexible programming

for various data and timing formats.

Two independent interface circuits control audio data

streaming of up to 2 × 128-bit frame width (bidirectional or

simultaneous input/output). Five or more I2S devices such

as the SAA7360 and SAA7366 (ADC) and SAA7350 and

SAA7351 (DAC) can be connected gluelessly.

The peripheral data port [Data Expansion Bus Interface

(DEBI)] enables 8 or 16-bit parallel access for system

set-up and programming of peripheral multimedia devices

(behind SAA7146A), but is also highly capable to interface

compressed MPEG/JPEG data of peripheral ICs with the

PCI system. DEBI supports both Intel compatible (ISA-bus

like) and Motorola (68000 style) compatible handshaking

protocols with up to 23 Mbytes/s peak data rate. Besides

the parallel port, there is also an I2C-bus port to control

peripheral ICs such as single-chip decoders SAA7110 and

SAA7111A or as encoders such as SAA7185B and

SAA7187 or as audio ICs.

The PCI interface has master read and master write

capability. The video signal flows to and from the PCI and

is controlled by three video DMA channels with a total

FIFO capacity of 384 Dwords. The video DMA channel

definition supports the typical video data structure

(hierarchy) of pixels, lines, fields and frames. The audio

signal flow is controlled by four audio DMA channels, each

with 24 Dwords FIFO capacity. The DEBI port is

connected to the PCI by single instruction direct access

(immediate mode) and via a data DMA channel for

streaming data (block mode) with 32 Dwords FIFO

capacity. To improve PCI-bus efficiency, an arbiter

schedules the access to PCI-bus for all local DMA

channels.

The PCI interface of the SAA7146A supports virtual

memory addressing for operating systems running virtual

demand paging. The integrated Memory Management

Unit (MMU) translates linear addressing to physical

addresses using a page table inside the system memory

provided by the software driver. The MMU supports up to

4 Mbytes of virtual address space per DMA channel.

The SAA7146A can change its programming sets using a

Register Programming Sequencer (RPS) that works by

itself on a user defined program controlled by internally

supported real time events. The SAA7146A has two RPS

machines to optimize flow control of e.g. an MPEG

compressed data stream and real time video scaling

control. The RPS programming is defined by an instruction

list in the system main memory that consists of multiple

RPS commands.

1998 Apr 09 18

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

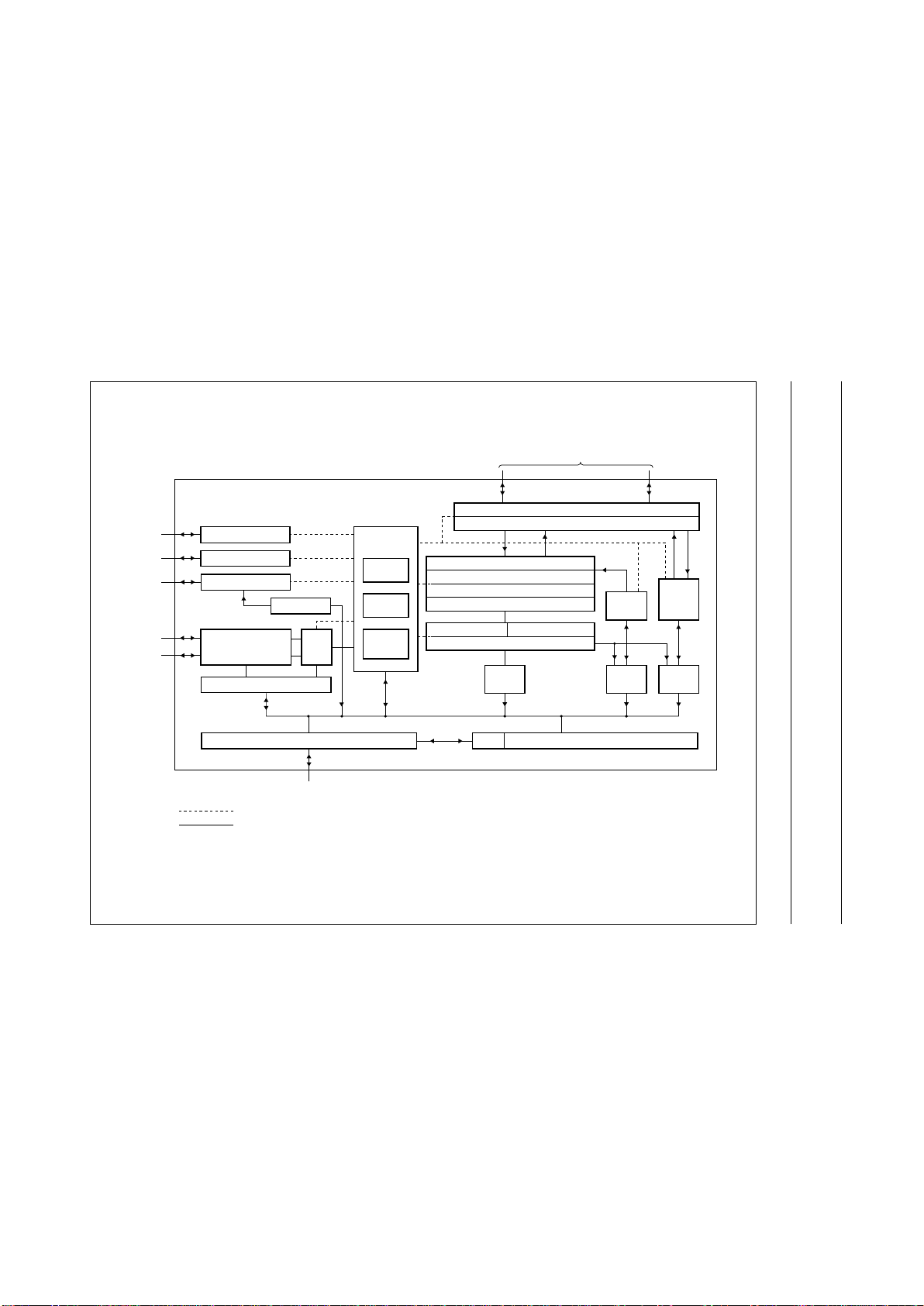

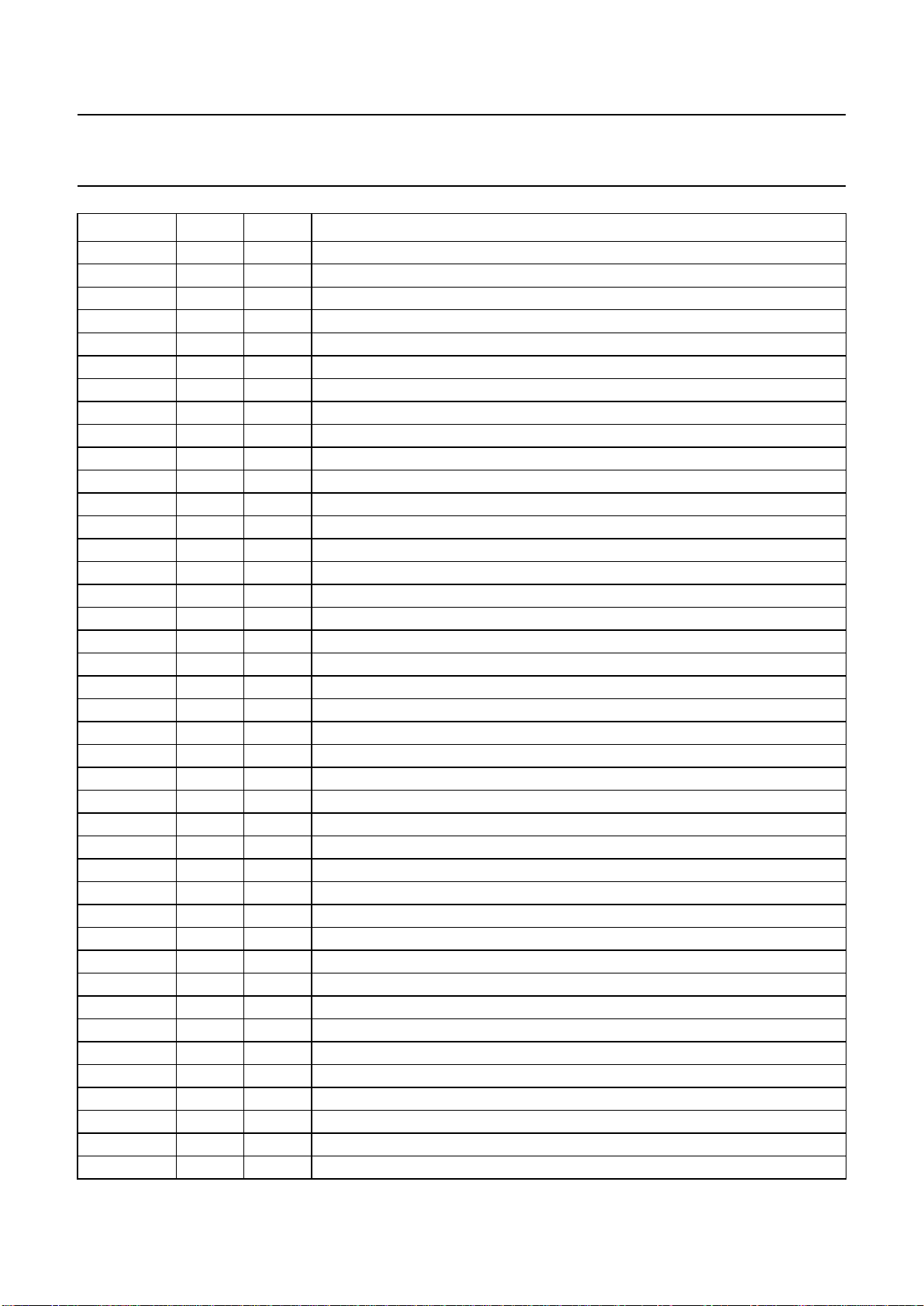

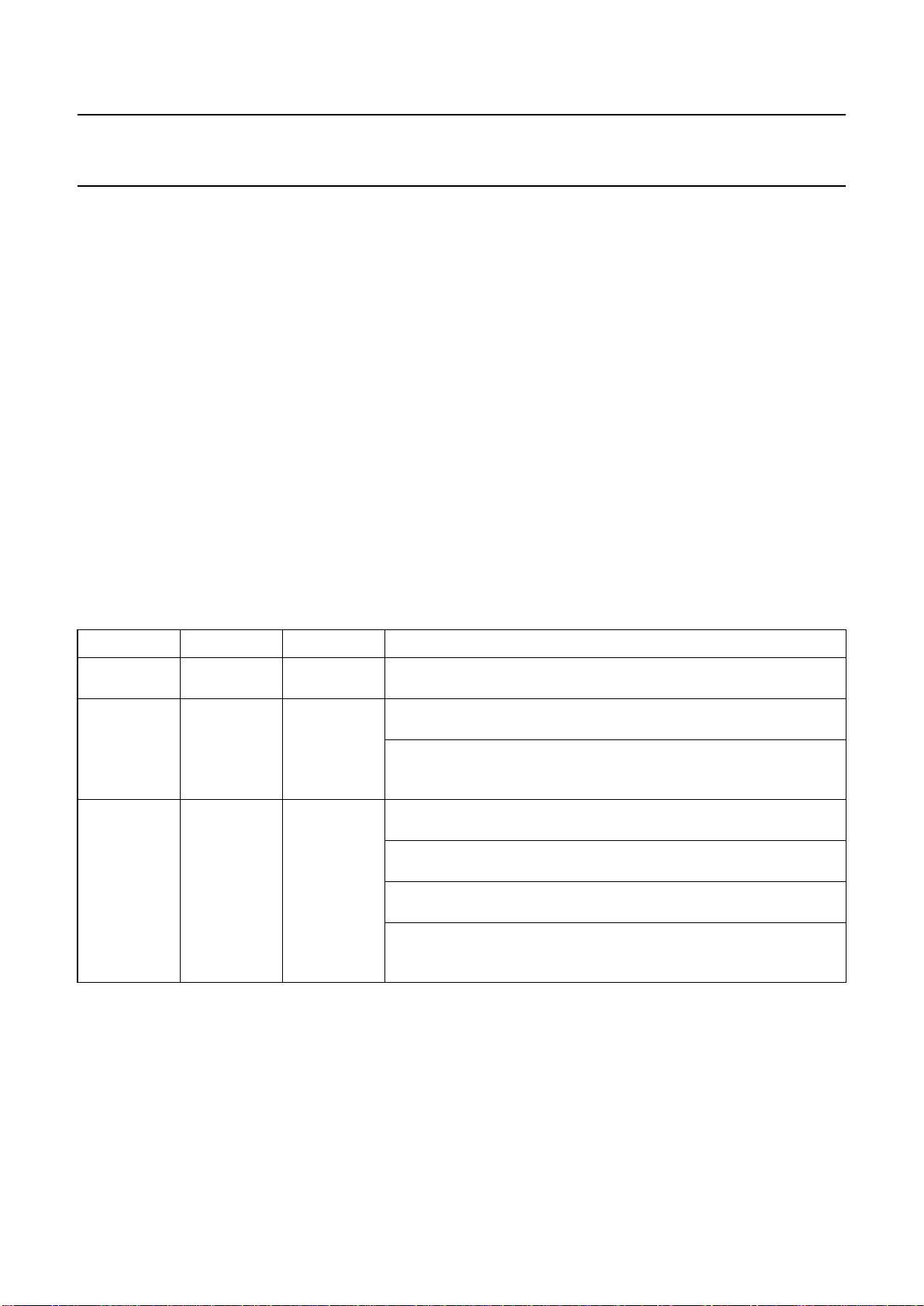

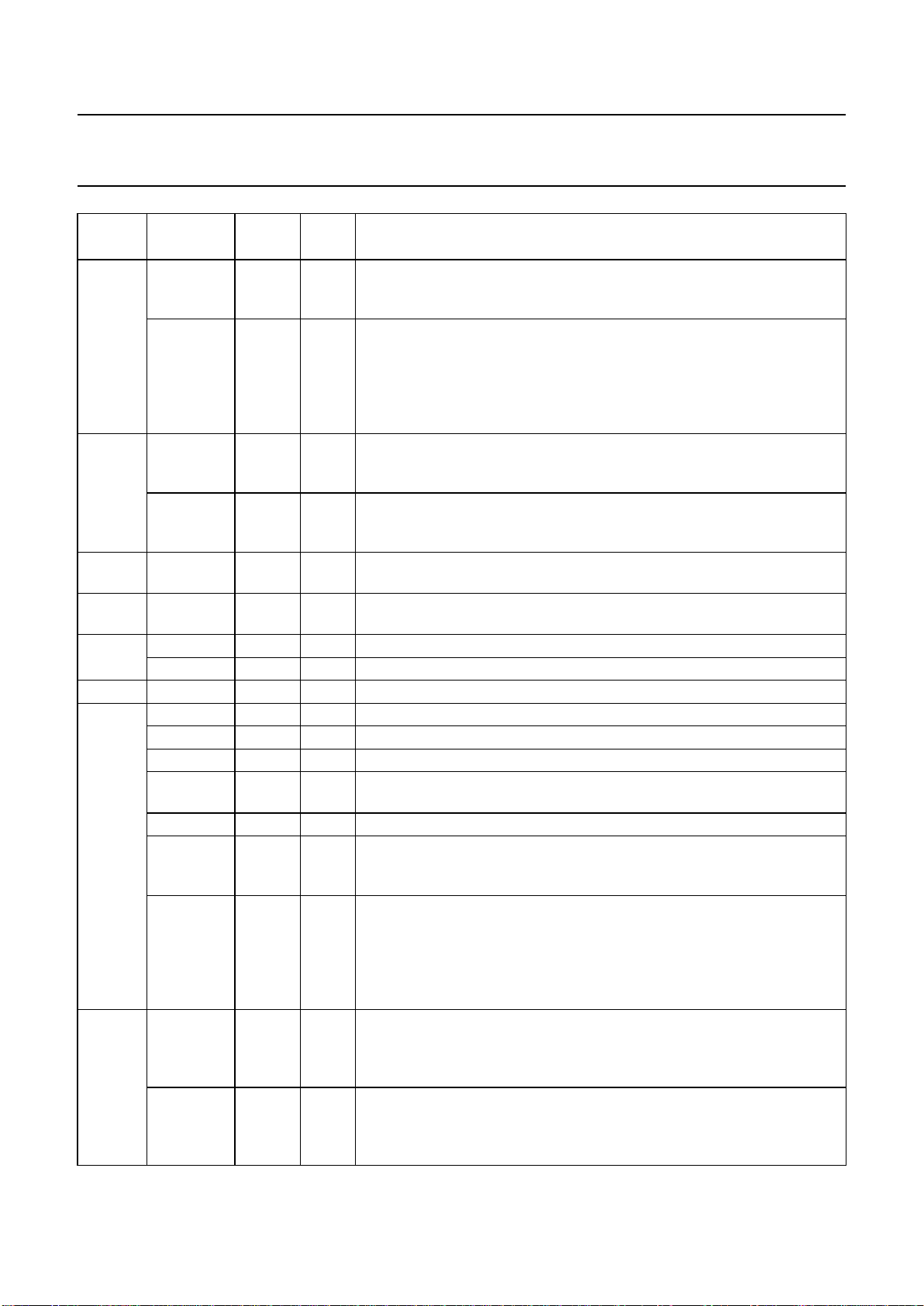

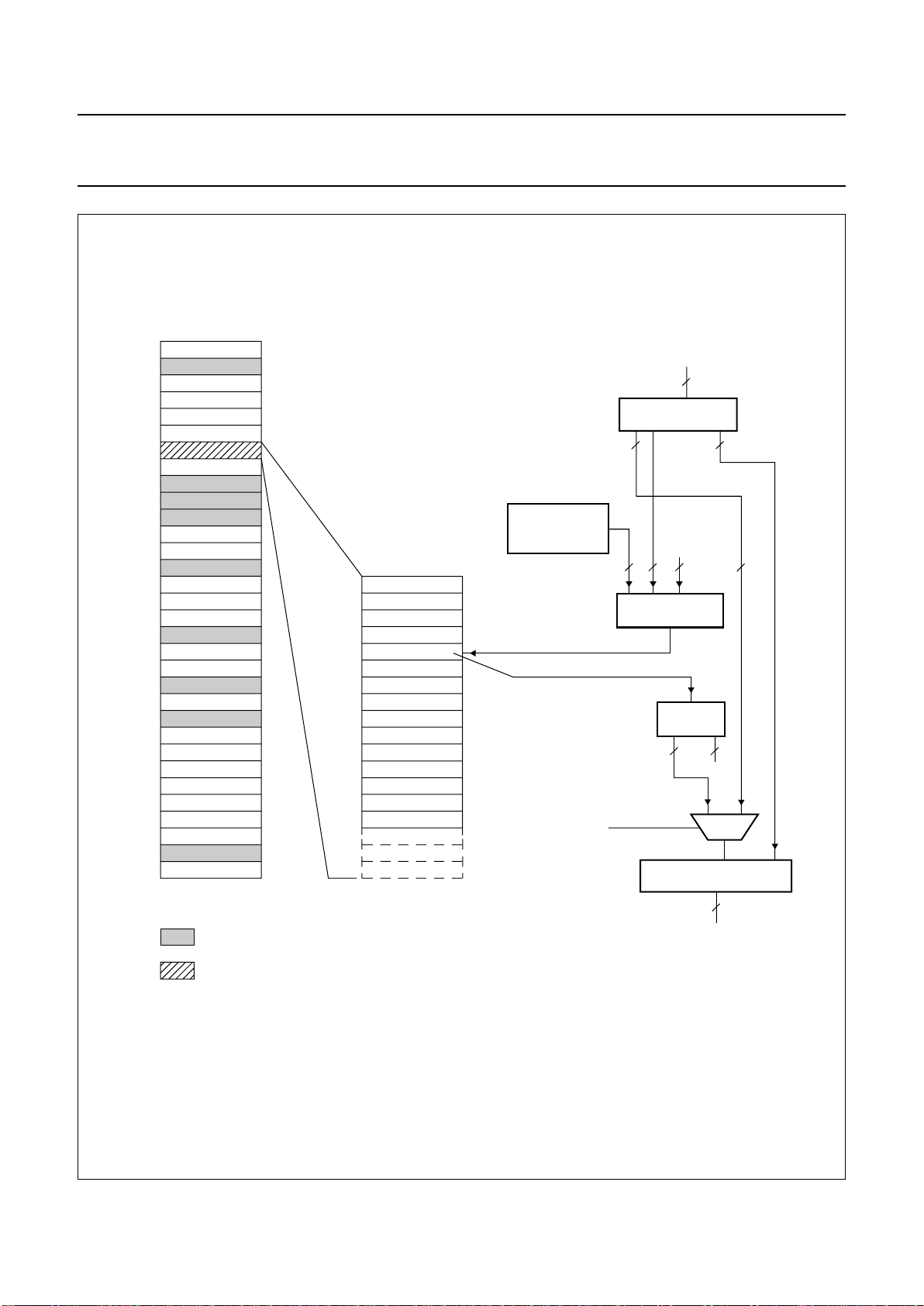

7.2 PCI interface

This section describes the interface of the SAA7146A to

the PCI-bus. This includes the PCI modules, the DMA

controls of the video, audio and data channels, the

Memory Management Unit (MMU) and the Internal

Arbitration Control (INTAC). The handling of the FIFOs

and the corresponding errors are also described and a list

of all DMA control registers is given.

7.2.1 PCI

MODULES AND CONFIGURATION SPACE

The SAA7146A provides a PCI-bus interface having both

slave and master capability. The master and the slave

module fulfil the PCI local bus specification revision 2.1.

They decode the C/BE# lines to provide a byte-wise

access and support 32-bit transfers up to a maximum clock

rate of 33 MHz. To increase bus performance, they are

able to handle fast back-to-back transfers.

During normal operation the SAA7146A checks for parity

errors and reports them via the PERR# pin. If an address

parity error is detected the SAA7146A will not respond.

Using the SAA7146A as a slave, access is obtained only

to the programmable registers and to its configuration

space. Video, audio and other data of the SAA7146A

reads/writes autonomously via the master interface (see

Fig.4). The use of the PCI master module, i.e. which DMA

channel gets access to the PCI-bus, is controlled by the

INTAC (see Section 7.2.5).

The registers described in Table 1 are closely related to

the PCI specification. It should be noted that Header type,

Cache Line Size, BIST, Card bus CIS Pointer and

Expansion ROM Base Address Registers are not

implemented. All registers, which are not implemented are

treated as read only with a value of zero. Some values are

loaded after PCI reset via I

2

C-bus from EEPROM with

device address 1010000 (binary). This loading will take

approximately 1 ms at 33 MHz PCI clock. If any device

tries to read or write data from or to the SAA7146A during

the loading phase after reset, the SAA7146A will

disconnect with retry.

1998 Apr 09 19

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

a

ndbook, full pagewidth

MHB047

MEMORY MANAGEMENT

UNIT

(MMU)

INTERNAL ARBITRATION

CONTROL

(INTAC)

REGISTER PROGRAMMING

SEQUENCER

(RPS)

REGISTER

SETS

interrupts

DEBI data/request

bus requests

channel select

I

2

C-BUS REGISTER

ERROR MANAGER

(EMA)

PCI

MODULE

MASTER

PCI

MODULE

SLAVE

REGISTER

AND

SHADOW RAM

data

physical address

logic

address

byte enable

bus command

new Tr

EOT

CE

data

PCI-bus

address

FIFO

CONTROL

(FICO)

FIFO1

FIFO2

FIFO3

FIFO

INPUT

CONTROL

(FINC)

AUDIO FIFO1 OUT

video/audio

data streams

AUDIO FIFO1 IN

AUDIO FIFO2 OUT

AUDIO FIFO2 IN

Fig.4 Block diagram of the PCI interface.

1998 Apr 09 20

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

Table 1 Configuration space registers

ADDRESS

(HEX)

NAME BIT TYPE DESCRIPTION

00 Device ID 31 to 16 RO 7146H SAA7146A

Vendor ID 15 to 0 RO 1131H Philips

04 Status Register 31 − detected parity error

29 − received master abort

28 − received target abort

26 and 25 RO 01 DEVSEL# timing medium

24 − data parity error detected

23 RO 1 fast back-to-back capable

Command

Register

9 RW fast back-to-back enable

6 RW parity error response

2 RW bus master enable

1 RW memory space

08 Class Code 31 to 8 RO 048000H other multimedia device

Revision ID 7 to 0 RO 01H reading these 8 bits returns 01H

0C Latency 15 to 8 RW this register specifies, in units of PCI-bus clocks, the

value of the latency timer for this PCI-bus master

10 Base Address

Register

31 to 9 RW this value must be added to the register offset to claim

access to the programming registers; the lower 8 bits

are forced to zero

8to0 RO

2C Subsystem ID 31 to 16 RO this value will be loaded after a PCI reset from external

hardware using the I

2

C-bus; the default value is 0000H

Subsystem

vendor ID

15 to 0 RO this value will be loaded after a PCI reset from external

hardware using the I

2

C-bus; the default value is 0000H

3C Max_Lat 31 to 24 RO this value will be loaded after a PCI reset from external

hardware using the I

2

C-bus; the default value is 26H

Min_Gnt 23 to 16 RO this value will be loaded after a PCI reset from external

hardware using the I

2

C-bus; the default value is 0FH

Interrupt Pin 15 to 8 RO 01H The interrupt pin register tells which interrupt pin the

device uses. This device uses interrupt pin INTA#.

When these bits are read they return 01H.

Interrupt Line 7 to 0 RW the interrupt line register tells which input of the system

interrupt controller the device’s interrupt pin is

connected to

1998 Apr 09 21

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

7.2.2 VIDEO DMA CONTROL

The SAA7146A’s DMA control is able to support up to

three independent video targets or sources respectively.

For this purpose it provides three video DMA channels.

Each channel consists of a FIFO, a FIFO Input Control

(FINC) placed on the video side of the FIFO, and a FIFO

Control (FICO) placed on the PCI side of the FIFO.

Channel 1 only supports the unidirectional data stream

into the PCI memory. It is not able to read data from

system memory. However, this access is possible using

Channels 2 or 3. Table 2 surveys the possibilities and

purposes of each video DMA channel.

Each FIFO, i.e. each DMA channel, has its own

programming set including base address (doubled for odd

and even fields), pitch, protection address, page table

base address, several handling mode control bits and a

transfer enable bit (TR_E). In addition, each channel has a

threshold and a burst length definition for internal

arbitration (see Table 6, Section 7.2.5).

To handle the reading modes FIFO 2 and FIFO 3 offer

some additional registers: Number of Bytes per line

(NumBytes), Number of Lines per field (NumLines) and

the vertical scaling ratio (only FIFO 3, see Table 69).

The programming sets could be reloaded after the

previous job is done [Video Transfer Done (VTD)] to

support several DMA targets per FIFO. The programming

set currently used is loaded by the Register Programming

Sequencer (RPS). If the RPS is not used, the registers

could be rewritten each time, using the SAA7146A as a

slave. But then the programmer must take care of the

synchronization of these write accesses.

All registers needed for DMA control are described in

Table 3, except the transfer enable bits, which are

described in Table 10. The registers are accessed through

PCI base address with appropriate offset (see Table 1).

Table 2 Size, direction and purpose of the video FIFOs and the associated DMA controls

FIFO SIZE DIRECTION PURPOSE

FIFO 1 128 Dwords write to PCI FIFO 1 buffers data from the HPS output and writes into PCI memory.

In planar mode FIFO 1 gets the Y data.

FIFO 2 128 Dwords RW Planar mode: FIFO 2 buffers U data provided by the HPS; the

associated DMA control 2 sends it into the PCI memory.

Clip mode: DMA control 2 reads clipping information (clip bit mask or

rectangular overlay data) from the PCI system memory and buffers it

in FIFO 2.

FIFO 3 128 Dwords RW Planar mode: FIFO 3 buffers V data provided by the HPS and writes

it into the PCI memory.

Chroma keying mode: FIFO 3 buffers chroma keying information

and writes it into PCI memory.

BRS mode: FIFO 3 buffers data provided by the BRS. DMA control 3

sends it into the PCI memory.

Read mode: DMA control 3 reads video data from the PCI system

memory (the same data up to four times to offer a simple upscaling

algorithm) and buffers it in FIFO 3.

1998 Apr 09 22

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

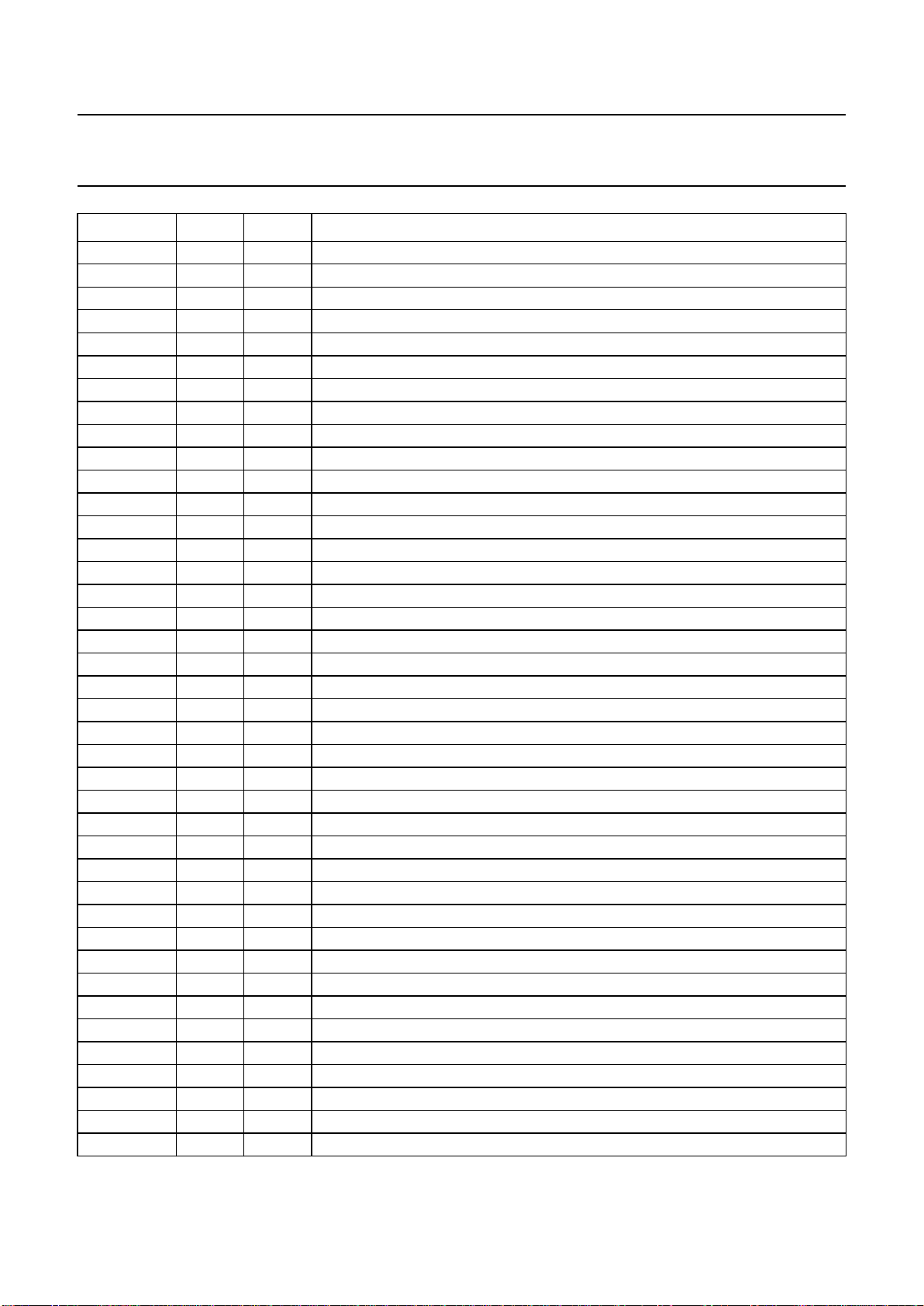

Table 3 Video DMA control registers

OFFSET

(HEX)

NAME BIT TYPE DESCRIPTION

00 BaseOdd1 31 to 0 RW PCI base address for odd fields of the upper (or lower if pitch is

negative) left pixel of the transferred field

04 BaseEven1 31 to 0 RW PCI base address for even fields of the upper (or lower if pitch is

negative) left pixel of the transferred field

08 ProtAddr1 31 to 2 RW protection address

− 1 and 0 − reserved

0C Pitch1 31 to 0 RW distance between the start addresses of two consecutive lines of a single

field

10 Page1 31 to 12 RW base address of the page table (see Section 7.2.4)

ME1 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

Limit1 7 to 4 RW interrupt limit; defines the size of the memory range, that raise an

interrupt, if its boundaries are passed

PV1 3 RW protection violation handling

− 2 − reserved

Swap1 1 and 0 RW endian swapping of all Dwords passing the FIFO 1:

00 = no swap

01 = two bytes swap (3210 to 2301)

10 = four bytes swap (3210 to 0123)

11 = reserved

14 NumLines1 27 to 16 RW Number of lines per field; it defines the number of qualified lines to be

processed by the HPS per field. This will cut off all the following input lines

at the HPS input.

NumBytes1 11 to 0 RW Number of pixels per line; it defines the number of qualified pixels to be

processed by the HPS per line. This will cut off all the following pixels at

the HPS input.

18 BaseOdd2 31 to 0 RW PCI base address for odd fields of the upper (or lower if top-down flip is

selected) left pixel of the transferred field

1C BaseEven2 31 to 0 RW PCI base address for even fields of the upper (or lower if top-down flip is

selected) left pixel of the transferred field

20 ProtAddr2 31 to 2 RW protection address

− 1 and 0 − reserved

24 Pitch2 31 to 0 RW distance between the start addresses of two consecutive lines of a field

28 Page2 31 to 12 RW base address of the page table (see Section 7.2.4)

ME2 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

Limit2 7 to 4 RW interrupt limit; defines the size of the memory range, that raise an

interrupt, if its boundaries are passed

PV2 3 RW protection violation handling

1998 Apr 09 23

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

28 RW2 2 RW Specifies the data stream direction of FIFO 2. A logic 0 enables a write

operation to the PCI memory. A logic 1 enables a read operation from the

PCI memory.

Swap2 1 and 0 RW endian swapping of all Dwords passing the FIFO 2:

00 = no swap

01 = two byte swap (3210 to 2301)

10 = four byte swap (3210 to 0123)

11 = reserved

2C NumLines2 27 to 16 RW Number of lines per field: in read mode NumLines defines the number of

lines to be read from system memory. A logic 0 specifies one line. In write

mode this register is not used.

NumBytes2 11 to 0 RW Number of bytes per line: in read mode this defines the number of bytes

per line to be read from system memory. A logic 0 specifies one byte. In

write mode this register is not used.

30 BaseOdd3 31 to 0 RW PCI base address for odd fields of the upper (or lower if top-down flip is

selected) left pixel of the transferred field

34 BaseEven3 31 to 0 RW PCI base address for even fields of the upper (or lower if top-down flip is

selected) left pixel of the transferred field

38 ProtAddr3 31 to 2 RW protection address

− 1 and 0 − reserved

3C Pitch3 31 to 0 RW distance between the start addresses of two consecutive lines of a field

40 Page3 31 to 12 RW base address of the page table (see Section 7.2.4)

ME3 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

Limit3 7 to 4 RW interrupt limit; defines the size of the memory range, that raise an

interrupt, if its boundaries are passed

PV3 3 RW protection violation handling

RW3 2 RW Specifies the data stream direction of FIFO 3. A logic 0 enables a write

operation to the PCI memory. A logic 1 enables a read operation from the

PCI memory.

Swap3 1 and 0 RW endian swapping of all Dwords passing the FIFO 3:

00 = no swap

01 = two byte swap (3210 to 2301)

10 = four byte swap (3210 to 0123)

11 = reserved

44 NumLines3 27 to 16 RW Number of lines per field: in read mode NumLines defines the number of

lines to be read from system memory. A logic 0 specifies one line. In write

mode it defines the number of qualified lines to be processed by the BRS

per field. This will cut off all the following input-lines at the BRS input.

NumBytes3 11 to 0 RW Number of bytes per line: in read mode this defines the number of bytes

per line to be read from system memory. A logic0 specifies 1 byte. In write

mode it defines the number of qualified bytes to be processed by the BRS

per line. This will cut off all the following bytes at the BRS input.

OFFSET

(HEX)

NAME BIT TYPE DESCRIPTION

1998 Apr 09 24

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

The video channels provide 32 bits of data signals and

4 bits of Byte Enable (BE) signals, End-Of-Line (EOL),

End-Of-Window (EOW), Begin-Of-Field (BOF),

Line-Locked Clock (LLC), Odd/Even signal (OE) and a

Valid Data (VD) signal. To start a video data transfer, e.g.

via video DMA Channel 3, this channel must first be

included in the internal arbitration scheme. This is

achieved by setting the corresponding TR_E bit

(see Table 10). If a TR_E bit is not set, the corresponding

FIFO is reset.

In read mode, which is offered by Channels 2 and 3, the

FICO requests a PCI transfer with the next BOF. Data is

provided by the PCI master module. The FICO calculates

the PCI address autonomously, starting with the base

address of the corresponding field. Only the received data

will be filled into the FIFO. FIFO 3 offers the possibility to

read video information from PCI memory, e.g. from the

frame buffer. This could be achieved by using the

NumBytes and the NumLines register, which defines the

size of the source picture, so that the DMA control is able

to synchronize itself to the source frame. FIFO 2 does the

same if reading clip information from memory.

To support the Binary Ratio Scaler (BRS) included in the

SAA7146A, which only provides the possibility of

horizontal upscaling, the DMA control 3 can be applied to

perform line repetition by reading lines up to four times

from PCI memory. This feature is controlled by the vertical

scaling ratio in outbound mode (see Table 66). This ratio

specifies the number of times each line should be read:

00 = only once, 01 = twice, and so on.

In the event of FIFO underflow, i.e. if the BRS or the

clipping unit respectively tries to read data from the FIFO,

even if the DMA control was not able to fill any data until

that moment, the reading unit tries to synchronize itself to

the outgoing data stream as soon as possible. In this way

the reading of invalid data is minimized. If the clipping unit

receives no data, it will disable the associated pixels.

The behaviour of the BRS depends on the selected read

mode which is described in Section 7.10.

In the event of FIFO overflow, i.e. if the scaler tries to

transfer data although the FIFO is full, the FIFO input

control locks the FIFO for the incoming data. During FIFO

overflow the PCI address of the incoming data will be

increased, over writing itself each time, if the scaler

transfers data, which has been clipped, the same

mechanism is used to improve PCI performance.

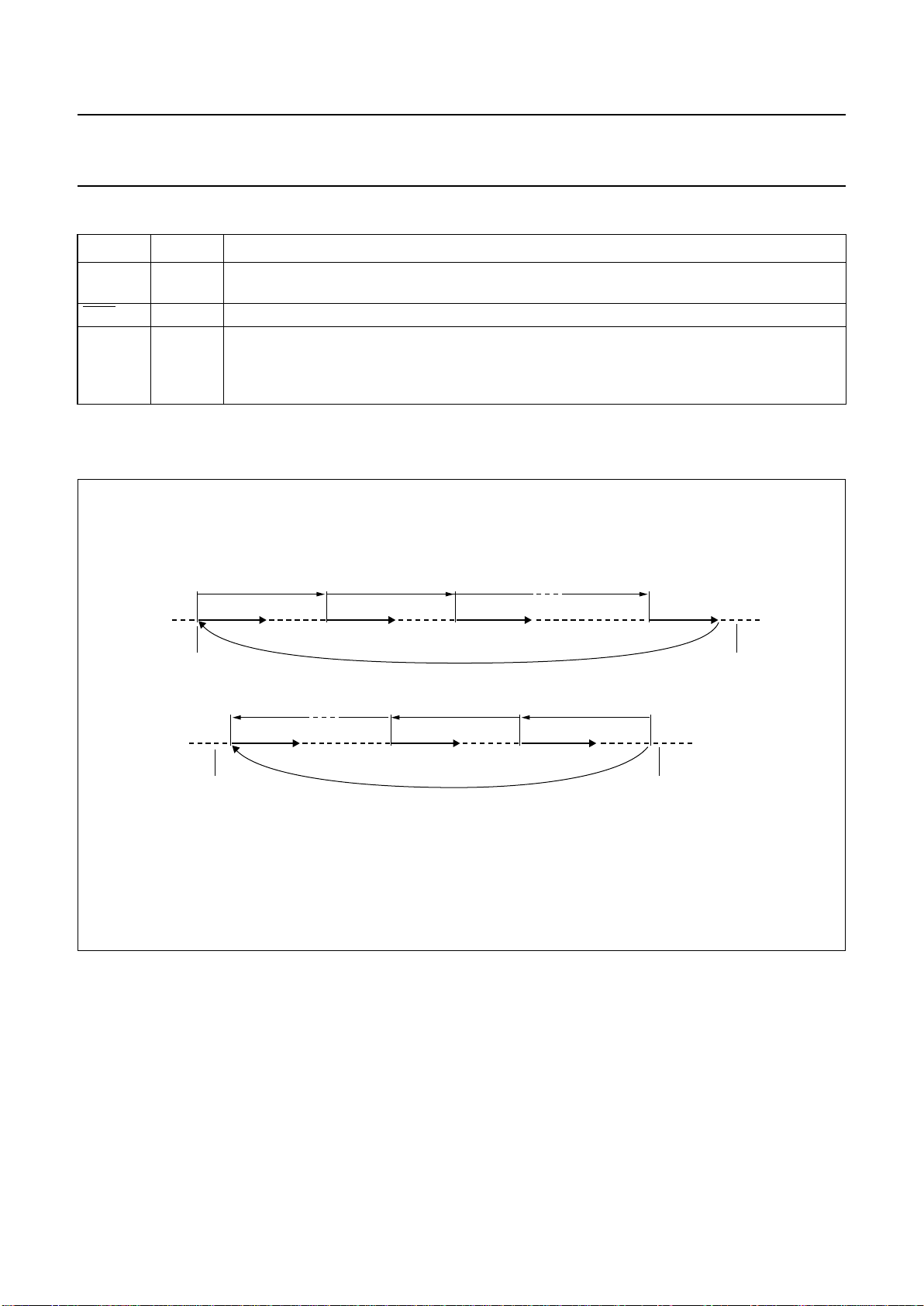

The SAA7146A is able to handle a negative pitch.

With that, top-down-flip of the transmitted fields or frames

is possible. A negative pitch (MSB = 1) leads to a different

definition of the protection and the base address, as

shown in Fig.5. If using negative pitch the first line starts at

base address + pitch.

In ‘none-RPS’ mode the SAA7146A supports the

displaying of interlaced video data by using the two

different base addresses (BaseOdd and BaseEven) and

vertical start phases (YPE6 to YPE0 and YPO6 to YPO0)

for odd and even fields.

Using the protection address, system memory could be

kept of from prohibited write accesses. If the PCI pointer of

the current transfer reaches or exceeds the protection

address, the SAA7146A stops this transfer and an

interrupt is initiated. No interrupt is set if a protection

violation occurs due to the programming that was done

before the channel has been switched on. To prevent one

field from being transferred into memory, set its base

address (BaseOdd or BaseEven) to the same value as the

protection address.

If the Protection Violation (PV) handling bit and the limit

register are reset, the following data will be ignored until

detection of the End-Of-Window (EOW) signal. In read

mode the DMA control also waits for this signal, to start the

next data transfer. If the PV bit is set, the input of the FIFO

will be locked and the FIFO will be emptied. If the FIFO is

empty the TR_E bit is reset. This feature could be used for

a single capture mode, if the protection address is the

same address as the last pixel in this field. With that, the

SAA7146A will write one field into system memory and

then stop.

If the limit register of any DMA channel (video, VBI data or

audio) has a value other than ‘0000’ the continuous write

mode is chosen. If the actual PCI address hits the

protection address and the PV bit is zero, the FINC stops

the current transfer, sets an interrupt and resets the actual

address to the base address. Regarding this, the

protection address could be used to define a memory

space to which data is sent. The SAA7146A offers the

possibility to monitor the filling level of this memory space.

The limit register defines an address limit, which generates

an interrupt if passed by the actual PCI address pointer.

‘0001’ means an interrupt will be generated if the lower

6 bits (64 bytes) of the PCI address are zero. ‘0010’

defines a limit of 128 bytes, ‘0011’ one of 256 bytes, and

so on up to 1 Mbyte defined by ‘1111’. This interrupt range

can be calculated as follows:

Range = 2

(5 + Limit)

bytes.

The protection handling modes such as those selected by

the PV bit and the contents of the limit register are shown

in Table 4.

1998 Apr 09 25

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

Table 4 Protection violation handling modes

Note

1. X = don’t care.

LIMIT PV DESCRIPTION

0000 0 Lock input of FIFO and empty FIFO (only in write mode). Unlock FIFO and start next transfer

using the base address at the detection of BOF.

0000 0 Restart immediately at base address.

XXXX

(1)

1 Lock input of FIFO, empty FIFO (only in write mode) and then reset TR_E bit. The next transfer

starts with BOF using the corresponding base address, if the TR_E bit is set again. This setting

is useful for single-shot, that means transferring only one frame of a video stream. Therefore

the protection address has to be the same as the address of the last pixel of the field.

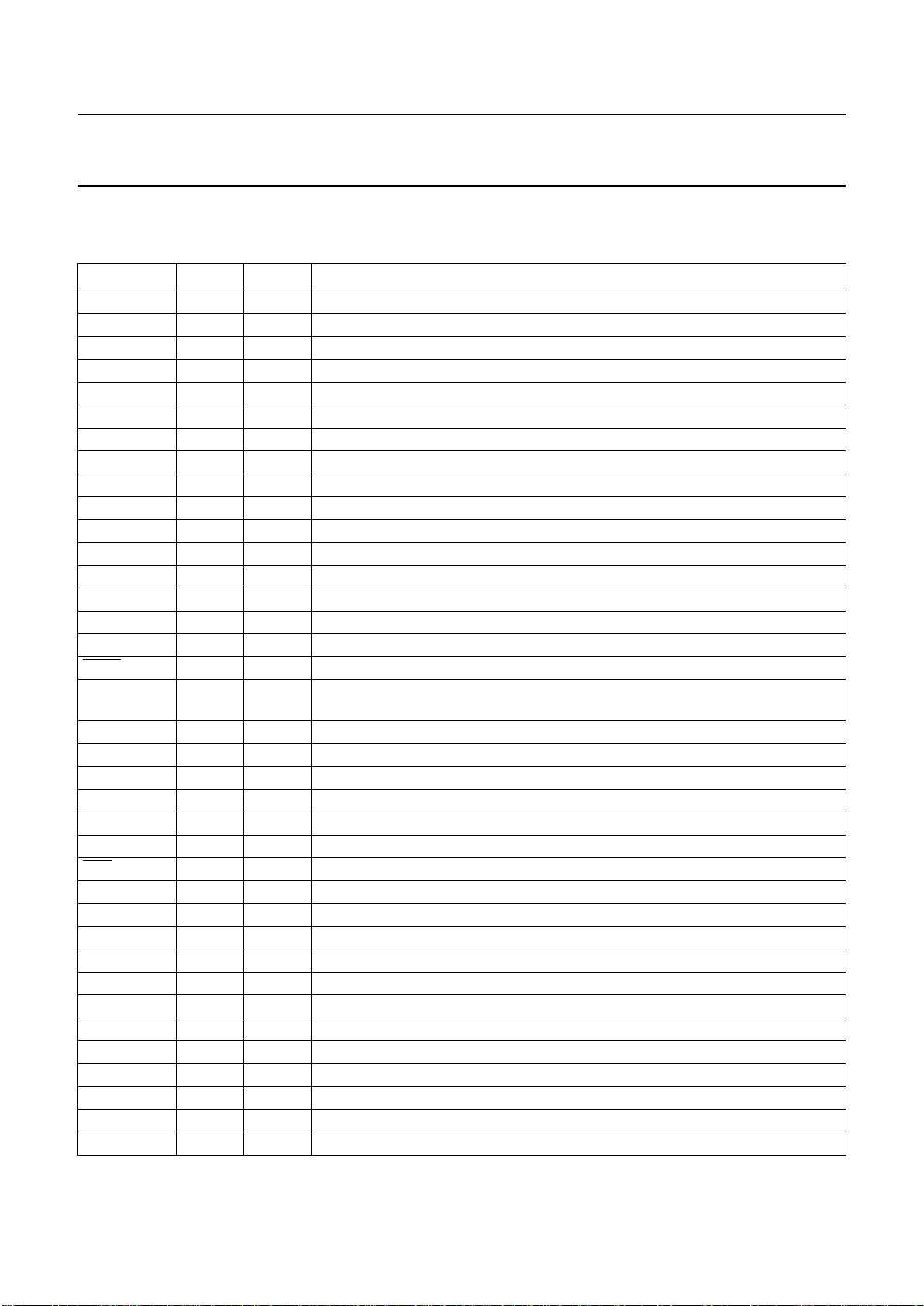

Fig.5 Handling of base and protection address using positive and negative line pitch.

handbook, full pagewidth

MGG260

positive pitch

BaseAddr

ProtAddr

1st line

positive pitch

2nd line

positive pitch

3rd line

Last line

negative pitch

(a) positive line pitch

(b) positive line pitch

BaseAddr

ProtAddr

1st line

negative pitch

2nd line

negative pitch

Last line

1998 Apr 09 26

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

7.2.3 AUDIO DMA CONTROL

The SAA7146A provides up to four audio DMA channels,

each using a FIFO of 24 Dwords. Two channels are read

only (A1_in and A2_in) and two channels are write only

(A1_out and A2_out). Because audio represents a

continuous data stream, which is neither line nor field

dependent, the audio DMA control offers only one base

address (BaseAxx) and no pitch register. For FIFO

overflow and underflow the handling of these channels is

done in the same way as the video DMA channels

(see Section 7.2.2).

The protection violation handling differs only if the limit

register and the PV bit are programmed to zero. The audio

DMA channel does not wait for the EOF signal, like the

video ones. It does not generate interrupts. The interrupt

range specified by the limit register is defined in the same

way as described in Section 7.2.2. The audio DMA

channels try immediately to transfer data after setting the

transfer enable bits. All registers for audio DMA control,

which are the base address, the protection address and

the control bits are listed in the following Table 5, except

the input control bits (Burst, Threshold), which are listed in

Table 6.

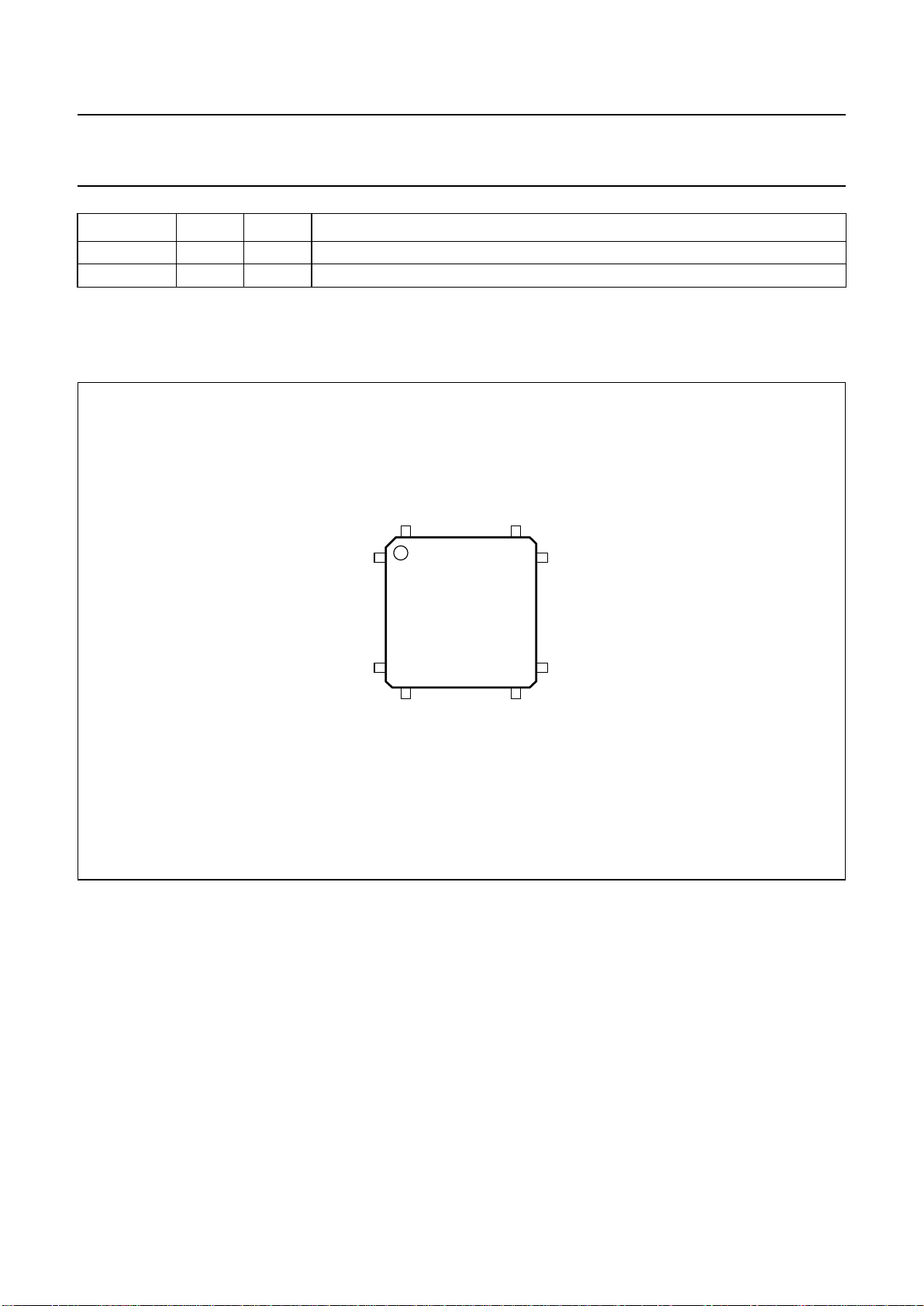

Table 5 Audio DMA control register

OFFSET

(HEX)

NAME BIT TYPE DESCRIPTION

94 BaseA1_in 31 to 0 RW base address for audio input Channel 1; this value specifies a

byte address

98 ProtA1_in 31 to 2 RW protection address for audio input Channel 1; this address

could be used to specify a upper limit for audio access in memory

space

− 1to0 − reserved

9C PageA1_in 31 to 12 RW base address of the page table, see Section 7.2.4.

MEA1_in 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

LimitA1_in 7 to 4 RW interrupt limit; defines the size of the memory range, that

generates interrupt, if its boundaries are passed

PVA1_in 3 RW protection violation handling

− 2to0 − reserved

A0 BaseA1_out 31 to 0 RW Base address for audio output Channel 1; this value specifies a

byte address. The lower two bits are forced to zero.

A4 ProtA1_out 31 to 2 RW protection address for audio output Channel 1; this address

could be used to specify a upper limit for audio access in memory

space

− 1 and 0 − reserved

A8 PageA1_out 31 to 12 RW base address of the page table, see Section 7.2.4.

MEA1_out 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

LimitA1_out 7 to 4 RW interrupt limit; defines the size of the memory range, that

generates an interrupt, if its boundaries are passed

PVA1_out 3 RW protection violation handling

− 2to0 − reserved

1998 Apr 09 27

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

AC BaseA2_in 31 to 0 RW Base address for audio input Channel 2; this value specifies a

byte address. The lower two bits are forced to zero.

B0 ProtA2_in 31 to 2 RW protection address for audio input Channel 2; this address

could be used to specify a upper limit for audio access in memory

space

− 1 and 0 − reserve

B4 PageA2_in 31 to 12 RW base address of the page table, see Section 7.2.4

MEA2_in 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

LimitA2_in 7 to 4 RW interrupt limit; defines the size of the memory range, that raise an

interrupt, if its boundaries are passed

PVA2_in 3 RW protection violation handling

− 2to0 − reserve

B8 BaseA2_out 31 to 0 RW Base address for audio output Channel 2; this value specifies a

byte address. The lower two bits are forced to zero.

BC ProtA2_out 31 to 2 RW protection address for audio output Channel 2; this address

could be used to specify a upper limit for audio access in memory

space

− 1 and 0 − reserved

C0 PageA2_out 31 to 12 RW base address of the page table, see Section 7.2.4

MEA2_out 11 RW mapping enable; this bit enables the MMU

− 10 to 8 − reserved

LimitA2_out 7 to 4 RW interrupt limit; defines the size of the memory range, that raise an

interrupt, if its boundaries are passed

PVA2_out 3 RW protection violation handling

− 2to0 − reserved

OFFSET

(HEX)

NAME BIT TYPE DESCRIPTION

1998 Apr 09 28

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

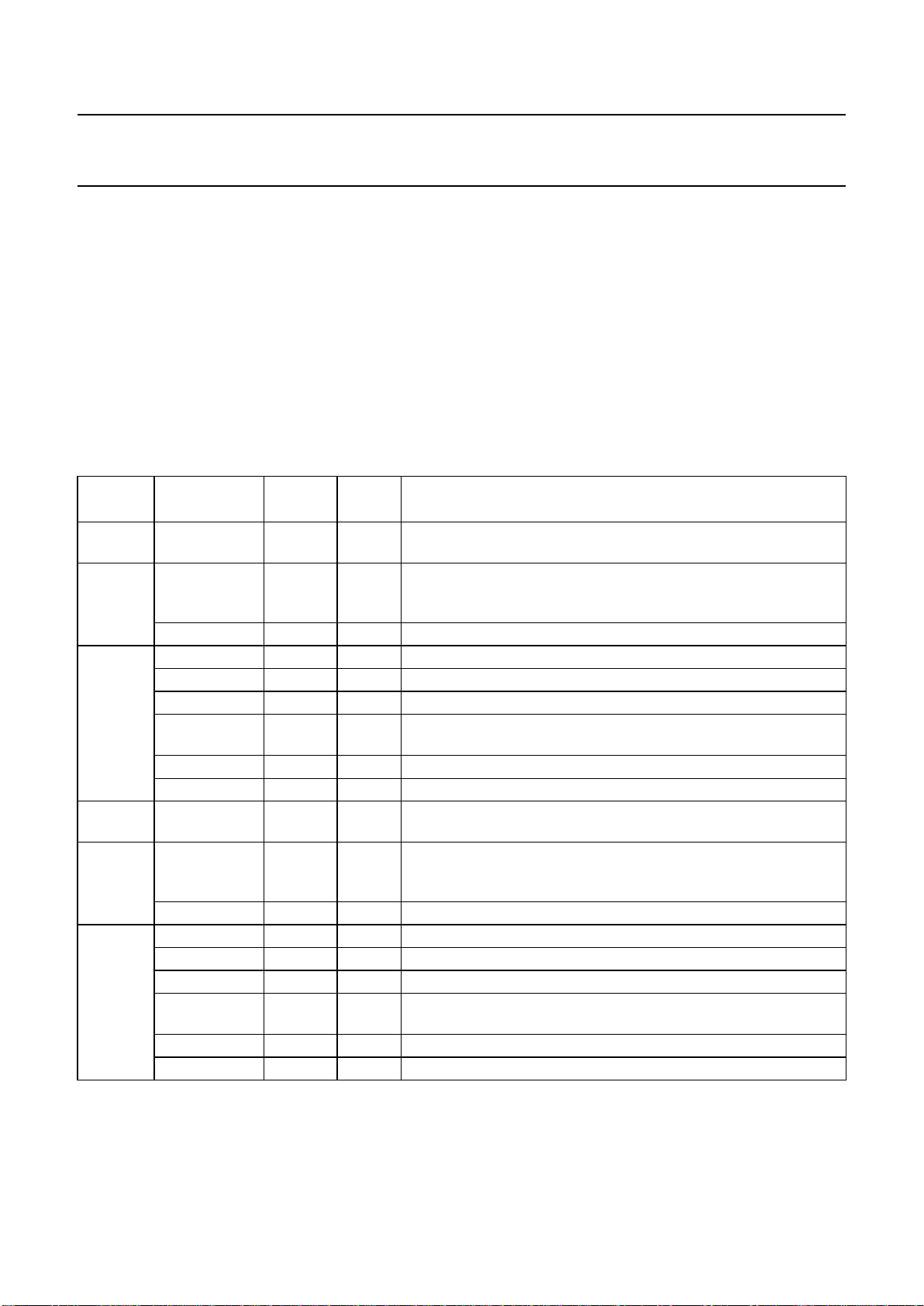

7.2.4 MEMORY MANAGEMENT UNIT (MMU)

7.2.4.1 Introduction

To perform DMA transfers, physically continuous memory

space is needed. However, operating systems such as

Microsoft Windows are working with virtual demand

paging, using a MMU to translate linear to physical

addresses. Memory allocation is performed in the linear

address space, resulting in fragmented memory in the

physical address space. There is no way to allocate large

buffers of physical, continuous memory, except reserving

it during system start-up. Thus decreasing the system

performance dramatically. To overcome this problem the

SAA7146A contains a Memory Management Unit (MMU)

as well. This MMU is able to handle memory fragmented

to 4 kbyte pages, similar to the scheme used by the Intel

8086 processor family. The MMU can be bypassed to

simplify transfers to non-paged memory such as the

graphics adapter’s frame buffer.

7.2.4.2 Memory allocation

The SAA7146A’s MMU requires a special scheme for

memory allocation. The following steps have to be

performed:

• Allocation of n pages, each page being 4 kbytes of size,

aligned to a 4 kbyte boundary

• Allocation of one extra page, to be used as page table

• Initialization of the page table.

Allocation of pages is done in physical address space.

Operating systems implementing virtual memory provide

services to allocate and free these pages.

The page table is stored in a separate page. This limits the

linear address page to a size of 4 Mbytes and results in a

4 kbyte overhead. The page table is organized as an array

of n Dwords, with each entry giving the physical address of

one of the n pages of allocated memory. As pages are

aligned to 4 kbytes, the lower 12 bits of each entry are

fixed to zero.

7.2.4.3 Implementation

The SAA7146A has up to 8 DMA channels (3 video,

4 audio and 1 DEBI channel) for which the memory

mapping is done. Each of them provides the linear address

to (from) which it wants to send (read) data during the next

transfer. Their register sets contain a page table base

address (Pagexx) and a mapping enable bit (MExx).

If MExx is set, mapping is enabled.

The MMU checks for each channel whether its address

has been already translated. If translated, its request can

pass to the Internal Arbitration Control (INTAC) managing

the access to the PCI-bus. If not, the MMU starts a bus

transfer to the page table. The page table entry address

could be calculated from the channels PCI address and

the page table base address, as shown in Fig.6. The upper

20 bits of the PCI address are replaced by the upper

20 bits of the according page address to generate the

mapped PCI address.

If the PCI address crosses a 4 kbyte boundary during a

transfer, the MMU stops this transfer and suppresses its

request to the INTAC until it has renewed the page

address, which means replacing the upper 20 bits of the

current address. To reduce latency the SAA7146A will do

a pre-fetch, i.e. it will always try to load the next page

address in advance.

1998 Apr 09 29

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

Fig.6 Memory Management Unit (MMU).

handbook, full pagewidth

MGG261

00001000H

Page table

Physical memory

(4 kbyte pages)

DMA ADDRESS

PAGE

ADDRESS

ME

(Mapping Enable)

PHYSICAL PCI ADDRESS

PAGE TABLE

ENTRY ADDRESS

PAGE TABLE

BASE ADDRESS

(00006H)

00000H

00007H

0000FH

00017 H

0001FH

015H

000H

007H

00008000H

00009000H

0000A000H

0000D000H

00011000H

00014000H

00016000H

0001E000H

= allocated memory space

= page table

2

32

32

1220

'0'

202010

1210

1998 Apr 09 30

Philips Semiconductors Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

7.2.5 INTERNAL ARBITRATION CONTROL

The SAA7146A has up to three video DMA channels, four

audio DMA channels and three other DMA channels (RPS,

MMU and DEBI) each trying to get access to the PCI-bus.

To handle this, an Internal Arbitration Control (INTAC) is

needed. INTAC controls on the one hand the PCI-bus

requests and on the other hand the order in which each

DMA channel gets access to the bus.

The basic implementation of the internal arbitration control

is a round-robin mechanism on the top, consisting of the

RPS, the MMU and one of the eight data channels. Data

channel arbitration is performed using a ‘first come first

serve’ queue architecture, which may consist of up to eight

entries.

Each data channel reaching a certain filling level of its

FIFO defined by the threshold, is allowed to make an entry

into the arbitration queue. The threshold defines the

number of Dwords needed to start a sensible PCI transfer

and must be small enough to avoid a loss of data due to an

overflow regarding the PCI latency time. After each job

(Video Transfer Done, VTD) the video channels have to be

emptied and are allowed to fill an entry into the queue,

even if they have not yet reached their threshold.

Concurrently to the entry the channel sets a bit which

prohibits further entries to this channel. In the worst case,

each data channel can have only one entry in the queue.

If each channel wants to access the bus, which means the

queue is full, an order like the one shown below will be

given.

• MMU

• RPS.

First entry of the data channel queue:

• MMU

• RPS.

Second entry of the data channel queue:

• MMU

• and so on.

If INTAC detects at least one DMA channel in the queue or

an MMU or an RPS request, it signals the need for the bus

by setting the REQ# signal on the PCI-bus. If the GNT#

signal goes LOW, the SAA7146A is the owner of the bus

and makes the PCI master module working with the first

channel selected. The master module tries to transfer the

number of Dwords defined in the Burst Register. For RPS

the burst length is hardwired to four and for the MMU it is

hardwired to two Dwords. After that the master module

stops this transfer and starts a transfer using the next

channel (due to the round-robin).

If a DMA channel gets its transfer stopped due to a retry,

the arbitration control sets the corresponding retry flag.

INTAC tries to end a retried transfer, even if this transfer

gets stopped via the Transfer Enable bit (TR_E). For this

reason the Transfer Enable bits are internally shadowed

by INTAC. A transfer can only be stopped if it has no retry

pending.

The Arbitration Control Registers (Burst and Threshold of

DEBI, Video 1 to 3, Audio 1 to 4) are listed in Table 6.

Loading...

Loading...