Page 1

Colour Television Chassis

18991_000_100531.eps

100531

Q552.1A

LA

Contents Page Contents Page

1. Revision List 2

2. Technical Specifications, Diversity, and Connections2

3. Precautions, Notes, and Abbreviation List 5

4. Mechanical Instructions 9

5. Service Modes, Error Codes, and Fault Finding 20

6. Alignments 38

7. Circuit Descriptions 44

8. IC Data Sheets 56

9. Block Diagrams

Wiring diagram Matisse 42" 67

Wiring diagram Matisse 46" - 52" 68

Wiring diagram Da Vinci 40" - 46" 69

Block Diagram Video 70

Block Diagram Audio 71

Block Diagram Control & Clock Signals 72

Block Diagram I2C 73

Supply Lines Overview 74

10. Circuit Diagrams and PWB Layouts Drawing PWB

AL1 820400089786 AmbiLight Common

AL1 820400089691 9 LED LiteOn 77 84

AL1 820400089703 15 LED LiteOn 79 84

AL1 820400089712 21 LED LiteOn 81 84

AL1 820400090592 AmbiLight Common 85 91

AL1 820400090601 9 LED Everlight 87 91

AL1 820400090621 15 LED Everlight 89 91

B01 820400089943 Tuner, HDMI & CI 92

B02 820400089505 PNX85500 103

B02 820400089506 PNX85500 112

B03 820400089514 CLASS D 121

B04 820400089524 Analog I/O 129

B05 820400089535 DDR 134

B05 820400089832 DDR 135

B06 820400089572 LVDS Non DVBS 136

B09 820400089812 Non DVBS Con. 140

©

Copyright 2010 Koninklijke Philips Electronics N.V.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic, mechanical,

photocopying, or otherwise without the prior permission of Philips.

75 84

B13 820400090731 TCON AL CPLD 141

B14 820400090713 TCON SHARP 142

310431363643 SSB Layout 148

310431364003 SSB Layout 152

11. Styling Sheets

Matisse 32" - 52" 156

Da Vinci 40" - 46" 157

Published by ER/TY 1065 BU TV Consumer Care, the Netherlands Subject to modification EN 3122 785 18991

2010-Jun-25

Page 2

EN 2 Q552.1A LA1.

Revision List

1. Revision List

Manual xxxx xxx xxxx.0

• First release.

Manual xxxx xxx xxxx.1

• All Chapters: added CTNs to the manual;

refer to Table 2-1

.

2. Technical Specifications, Diversity, and Connections

Index of this chapter:

2.1 Technical Specifications

2.2 Directions for Use

2.3 Connections

2.4 Chassis Overview

Notes:

• Figures can deviate due to the different set executions.

• Specifications are indicative (subject to change).

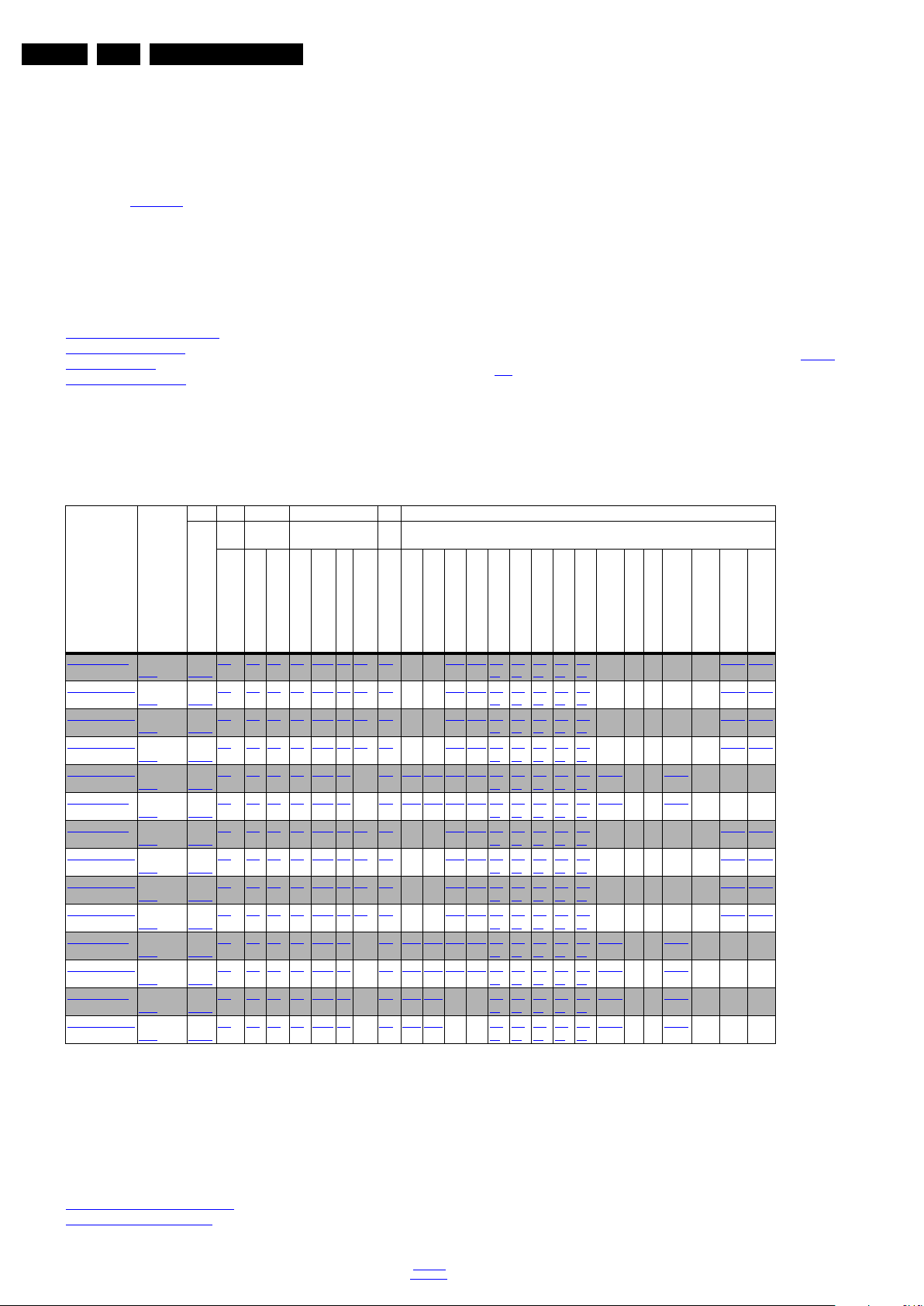

Table 2-1 Described Model Numbers and Diversity

SSB 2 4 7 9 10

Mecha-

Conn

nics Descriptions Wng Schematics

CTN

40PFL6605/98 da Vinci

40PFL6605D/93 da Vinci

40PFL6655D/93 da Vinci

40PFL6665D/93 da Vinci

42PFL8605D/93 Matisse

42PFL8605/98 Matisse

46PFL6605/98 da Vinci

46PFL6605D/93 da Vinci

46PFL6655D/93 da Vinci

46PFL6665D/93 da Vinci

46PFL8605/98 Matisse

46PFL8605D/93 Matisse

52PFL8605/98 Matisse

52PFL8605D/93 Matisse

Styling

styling sh.

11-2

11-2

11-2

11-2

11-1

11-1

11-2

11-2

11-2

11-2

11-1

11-1

11-1

11-1

64003

10-16

64003

10-16

64003

10-16

64003

10-16

63643

10-15

63643

10-15

64003

10-16

64003

10-16

64003

10-16

64003

10-16

63643

10-15

63643

10-15

63643

10-15

63643

10-15

3104 313

Wire

Assembly

Removal

PSU

Tuner

AmbiLight

2.3 4-4 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-7 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-4 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-7 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-4 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-7 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-4 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-7 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-1 4.4 7.2 7.4.1 7.8 - 9-1 10-1 10-2 10-6 10-7 10-1010-1210-1310-1410-1510-17 - - 10-18 - - -

2.3 4-1 4.4 7.2 7.4.1 7.8 - 9-1 10-1 10-2 10-6 10-7 10-1010-1210-1310-1410-1510-17 - - 10-18 - - -

2.3 4-5 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-8 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-5 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-8 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-5 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-8 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-5 4.5 7.2 7.4.1 7.8 7.8 9-3 - - 10-6 10-8 10-1010-1110-1310-1410-16- - - - - 10-19 10-20

2.3 4-2 4.4 7.2 7.4.1 7.8 - 9-2 10-1 10-3 10-6 10-8 10-1010-1210-1310-1410-1510-17 - - 10-18 - - -

2.3 4-2 4.4 7.2 7.4.1 7.8 - 9-2 10-1 10-3 10-6 10-8 10-1010-1210-1310-1410-1510-17 - - 10-18 - - -

2.3 4-3 4.4 7.2 7.4.1 7.8 - 9-2 10-1 10-4 - - 10-1010-1210-1310-1410-1510-17 - - 10-18 - - -

2.3 4-3 4.4 7.2 7.4.1 7.8 - 9-2 10-1 10-4 - - 10-1010-1210-1310-1410-1510-17 - - 10-18 - - -

TCON

2.1 Technical Specifications

For on-line product support please use the CTN links in Table

2-1. Here is product information available, as well as getting

started, user manuals, frequently asked questions and

software & drivers.

Diagram

Common LiteOn

Additional LiteOn

Common Everlight

Additional Everlight

B01 (Tuner)

B02 (PNX85500)

B03 (DC/DC / Class D)

B04 (I/O)

B05 (DDR)

B06 (non-DVBS-LVDS)

B07 (DVBS-FE)

B08 (DVBS-Supp.)

B09 (non-DVBS-conn.)

B11 (TCON-LGD)

B13 (Ambilight)

B14 (TCON-SHP)

Note to the Described Model and Diversity Table:

Not all (circuit-) descriptions and (block-) schematics in this

Service Manual apply to all sets. Use the hyperlinks in this table

to lead you through this manual.

2.2 Directions for Use

You can download this information from the following websites:

http://www.philips.com/support

http://www.p4c.philips.com

2010-Jun-25

back to

div. table

Page 3

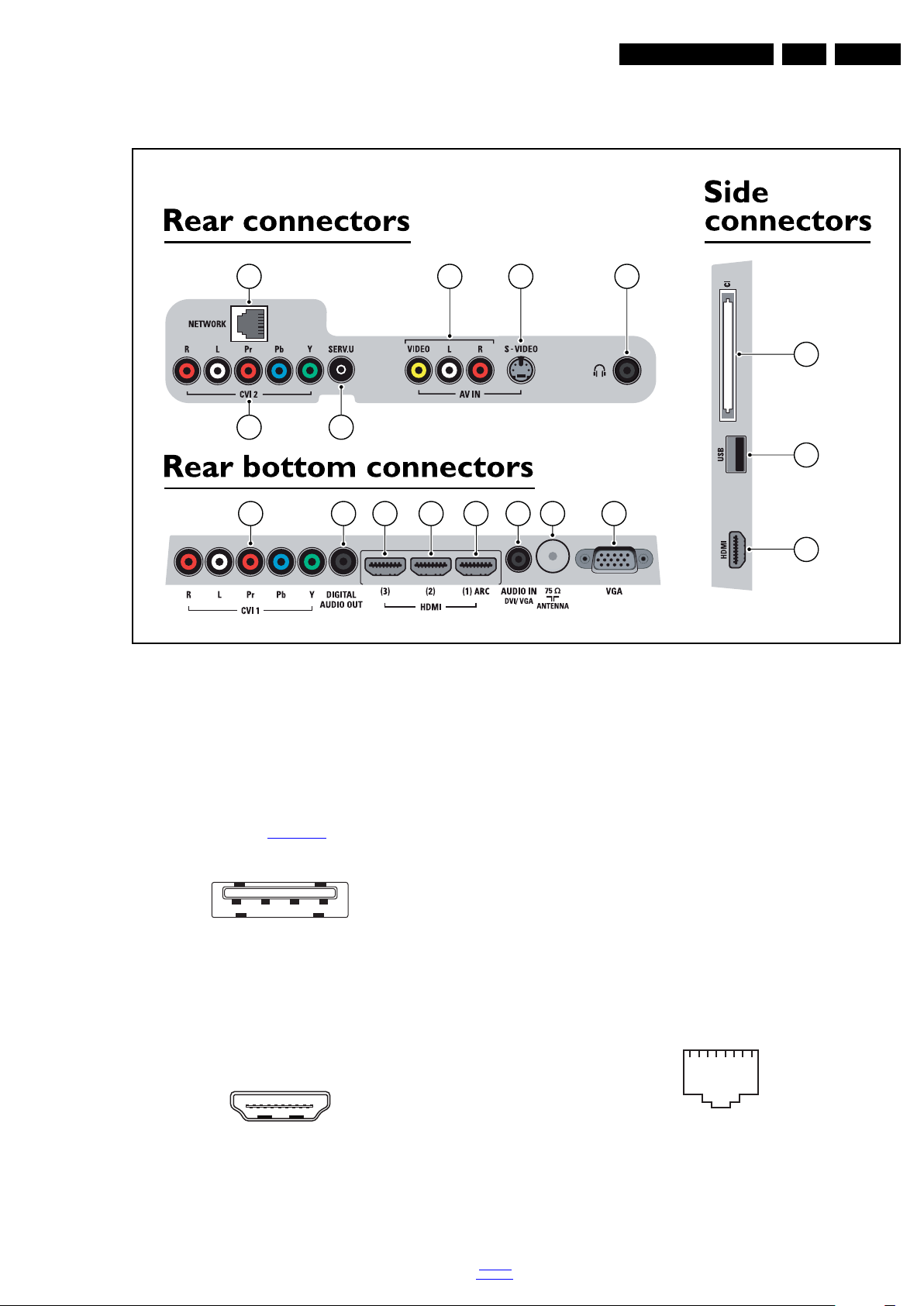

2.3 Connections

18990_001_100401.eps

100401

10 11 1212 13 14 15 16

4 7 8 9

5 6

1

2

3

1 2 3 4

10000_022_090121.eps

090121

10000_017_090121.eps

090428

19

1

18 2

1123 45678

10000_025_090121.eps

090121

Technical Specifications, Diversity, and Connections

EN 3Q552.1A LA 2.

Figure 2-1 Connection overview

Note: The following connector colour abbreviations are used

(acc. to DIN/IEC 757): Bk= Black, Bu= Blue, Gn= Green, Gy=

Grey, Rd= Red, Wh= White, Ye= Yellow.

2.3.1 Side Connections

1 - Common Interface

68p - See diagram B01F HDMI & CI

jk

2 - USB2.0

Figure 2-2 USB (type A)

1-+5V k

2 - Data (-) jk

3 - Data (+) jk

4 - Ground Gnd H

3 - HDMI: Digital Video, Digital Audio - In

4 - D1+ Data channel j

5 - Shield Gnd H

6 - D1- Data channel j

7 - D0+ Data channel j

8 - Shield Gnd H

9 - D0- Data channel j

10 - CLK+ Data channel j

11 - Shield Gnd H

12 - CLK- Data channel j

13 - Easylink/CEC Control channel jk

14 - n.c.

15 - DDC_SCL DDC clock j

16 - DDC_SDA DDC data jk

17 - Ground Gnd H

18 - +5V j

19 - HPD Hot Plug Detect j

20 - Ground Gnd H

2.3.2 Rear Connections

4 - RJ45: Ethernet (optional)

Figure 2-3 HDMI (type A) connector

1 - D2+ Data channel j

2 - Shield Gnd H

3 - D2- Data channel j

back to

div. table

Figure 2-4 Ethernet connector

1 - TD+ Transmit signal k

2 - TD- Transmit signal k

3 - RD+ Receive signal j

4 - CT Centre Tap: DC level fixation

2010-Jun-25

Page 4

EN 4 Q552.1A LA2.

10000_017_090121.eps

090428

19

1

18 2

1

6

10

11

5

15

10000_002_090121.eps

090127

Technical Specifications, Diversity, and Connections

5 - CT Centre Tap: DC level fixation

6 - RD- Receive signal j

7 - GND Gnd H

8 - GND Gnd H

5 - CVI 2: Cinch: Video YPbPr - In, Audio - In

Gn - Video Y 1 V

Bu - Video Pb 0.7 V

Rd - Video Pr 0.7 V

Rd - Audio - R 0.5 V

Wh - Audio - L 0.5 V

/ 75 ohm jq

PP

/ 75 ohm jq

PP

/ 75 ohm jq

PP

/ 10 kohm jq

RMS

/ 10 kohm jq

RMS

6 - Service Connector (UART)

1 - Ground Gnd H

2 - UART_TX Transmit k

3 - UART_RX Receive j

7 - Cinch: Video CVBS - In, Audio - In

Ye - Video CVBS 1 V

Wh - Audio L 0.5 V

Rd - Audio R 0.5 V

/ 75 ohm jq

PP

/ 10 kohm jq

RMS

/ 10 kohm jq

RMS

8 - S-Video (Hosiden): Video Y/C - In

1 - Ground Y Gnd H

2 - Ground C Gnd H

3 - Video Y 1 V

4 - Video C 0.3 V

/ 75 ohm j

PP

P / 75 ohm j

PP

9 - Head phone (Output) (optional)

Bk - Head phone 32 - 600 ohm / 10 mW ot

2.3.3 Rear Connections - Bottom

10 - CVI 1: Video RGB - In, CVBS - In/Out, Audio - In/Out

See 5 - CVI 2: Cinch: Video YPbPr - In, Audio - In

11 - Cinch: S/PDIF - Out

Bk - Coaxial 0.4 - 0.6V

/ 75 ohm kq

PP

12 - HDMI 2 (& 3 optional): Digital Video, Digital Audio - In

See 3 - HDMI: Digital Video, Digital Audio - In

11 - Shield Gnd H

12 - CLK- Data channel j

13 - Easylink/CEC Control channel jk

14 - ARC Audio Return Channel k

15 - DDC_SCL DDC clock j

16 - DDC_SDA DDC data jk

17 - Ground Gnd H

18 - +5V j

19 - HPD Hot Plug Detect j

20 - Ground Gnd H

14 - Cinch: Audio - In (VGA/DVI)

Rd - Audio R 0.5 V

Wh - Audio L 0.5 V

/ 10 kohm jq

RMS

/ 10 kohm jq

RMS

15 - Aerial - In

- - IEC-type (EU) Coax, 75 ohm D

16 - VGA: Video RGB - In

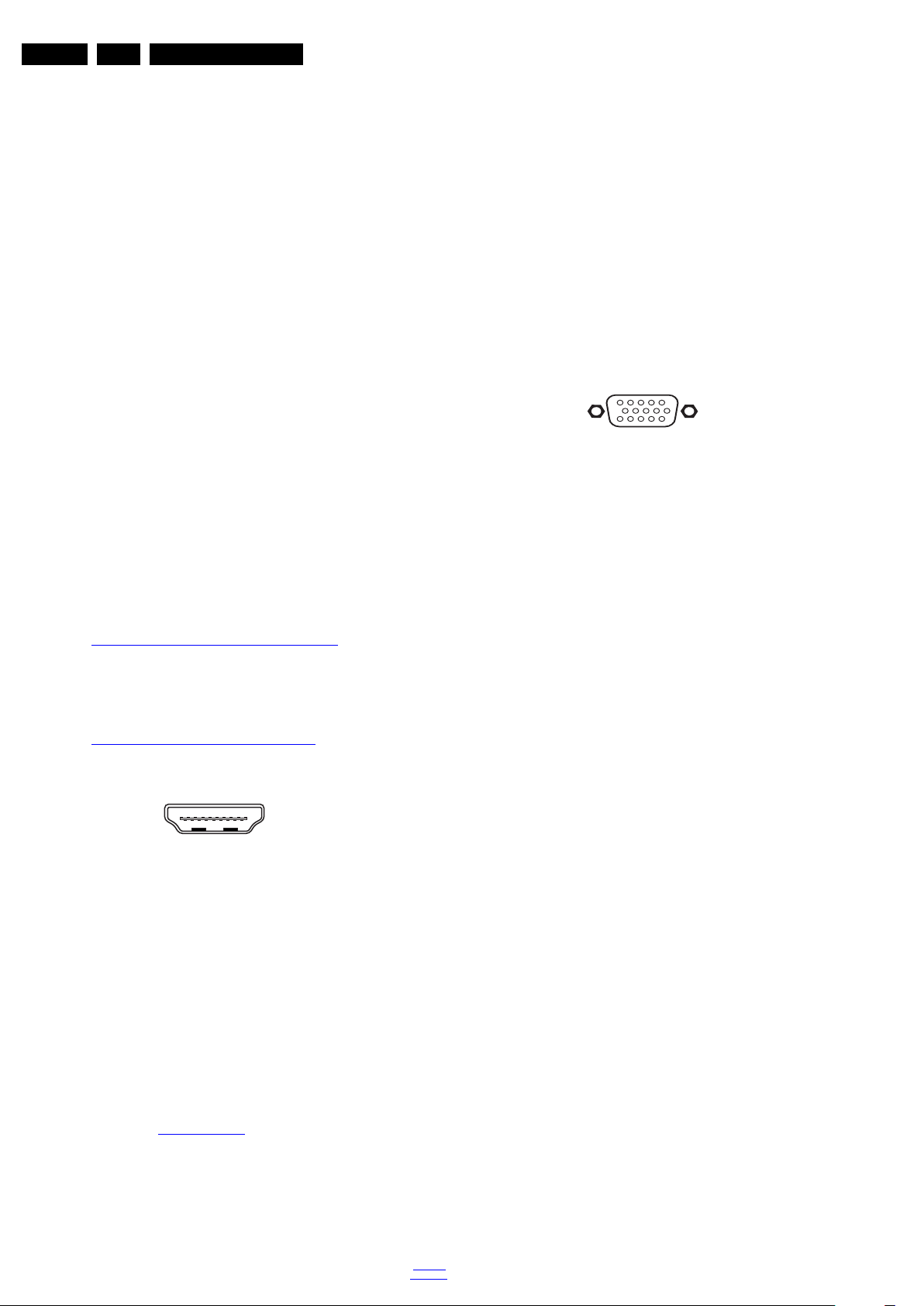

Figure 2-6 VGA Connector

1 - Video Red 0.7 V

2 - Video Green 0.7 V

3 - Video Blue 0.7 V

/ 75 ohm j

PP

/ 75 ohm j

PP

/ 75 ohm j

PP

4-n.c.

5 - Ground Gnd H

6 - Ground Red Gnd H

7 - Ground Green Gnd H

8 - Ground Blue Gnd H

9-+5V

+5 V j

DC

10 - Ground Sync Gnd H

11 - n.c.

12 - DDC_SDA DDC data j

13 - H-sync 0 - 5 V j

14 - V-sync 0 - 5 V j

15 - DDC_SCL DDC clock j

13 - HDMI 1: Digital Video - In, Digital Audio with ARC - In/ Out

Figure 2-5 HDMI (type A) connector

1 - D2+ Data channel j

2 - Shield Gnd H

3 - D2- Data channel j

4 - D1+ Data channel j

5 - Shield Gnd H

6 - D1- Data channel j

7 - D0+ Data channel j

8 - Shield Gnd H

9 - D0- Data channel j

10 - CLK+ Data channel j

2.4 Chassis Overview

Refer to chapter Block Diagrams for PWB/CBA locations.

2010-Jun-25

back to

div. table

Page 5

Precautions, Notes, and Abbreviation List

3. Precautions, Notes, and Abbreviation List

EN 5Q552.1A LA 3.

Index of this chapter:

3.1 Safety Instructions

3.2 Warnings

3.3 Notes

3.4 Abbreviation List

3.1 Safety Instructions

Safety regulations require the following during a repair:

• Connect the set to the Mains/AC Power via an isolation

transformer (> 800 VA).

• Replace safety components, indicated by the symbol h,

only by components identical to the original ones. Any

other component substitution (other than original type) may

increase risk of fire or electrical shock hazard.

Safety regulations require that after a repair, the set must be

returned in its original condition. Pay in particular attention to

the following points:

• Route the wire trees correctly and fix them with the

mounted cable clamps.

• Check the insulation of the Mains/AC Power lead for

external damage.

• Check the strain relief of the Mains/AC Power cord for

proper function.

• Check the electrical DC resistance between the Mains/AC

Power plug and the secondary side (only for sets that have

a Mains/AC Power isolated power supply):

1. Unplug the Mains/AC Power cord and connect a wire

between the two pins of the Mains/AC Power plug.

2. Set the Mains/AC Power switch to the “on” position

(keep the Mains/AC Power cord unplugged!).

3. Measure the resistance value between the pins of the

Mains/AC Power plug and the metal shielding of the

tuner or the aerial connection on the set. The reading

should be between 4.5 MΩ and 12 MΩ.

4. Switch “off” the set, and remove the wire between the

two pins of the Mains/AC Power plug.

• Check the cabinet for defects, to prevent touching of any

inner parts by the customer.

• Where necessary, measure the waveforms and voltages

with (D) and without (E) aerial signal. Measure the

voltages in the power supply section both in normal

operation (G) and in stand-by (F). These values are

indicated by means of the appropriate symbols.

3.3.2 Schematic Notes

• All resistor values are in ohms, and the value multiplier is

often used to indicate the decimal point location (e.g. 2K2

indicates 2.2 kΩ).

• Resistor values with no multiplier may be indicated with

either an “E” or an “R” (e.g. 220E or 220R indicates 220 Ω).

• All capacitor values are given in micro-farads (μ=× 10

nano-farads (n =× 10

• Capacitor values may also use the value multiplier as the

decimal point indication (e.g. 2p2 indicates 2.2 pF).

• An “asterisk” (*) indicates component usage varies. Refer

to the diversity tables for the correct values.

• The correct component values are listed on the Philips

Spare Parts Web Portal.

3.3.3 Spare Parts

For the latest spare part overview, consult your Philips Spare

Part web portal.

3.3.4 BGA (Ball Grid Array) ICs

Introduction

For more information on how to handle BGA devices, visit this

URL: http://www.atyourservice-magazine.com

“Magazine”, then go to “Repair downloads”. Here you will find

Information on how to deal with BGA-ICs.

BGA Temperature Profiles

For BGA-ICs, you must use the correct temperature-profile.

Where applicable and available, this profile is added to the IC

Data Sheet information section in this manual.

-9

), or pico-farads (p =× 10

. Select

-12

-6

),

).

3.2 Warnings

• All ICs and many other semiconductors are susceptible to

electrostatic discharges (ESD w). Careless handling

during repair can reduce life drastically. Make sure that,

during repair, you are connected with the same potential as

the mass of the set by a wristband with resistance. Keep

components and tools also at this same potential.

• Be careful during measurements in the high voltage

section.

• Never replace modules or other components while the unit

is switched “on”.

• When you align the set, use plastic rather than metal tools.

This will prevent any short circuits and the danger of a

circuit becoming unstable.

3.3 Notes

3.3.1 General

• Measure the voltages and waveforms with regard to the

chassis (= tuner) ground (H), or hot ground (I), depending

on the tested area of circuitry. The voltages and waveforms

shown in the diagrams are indicative. Measure them in the

Service Default Mode with a colour bar signal and stereo

sound (L: 3 kHz, R: 1 kHz unless stated otherwise) and

picture carrier at 475.25 MHz for PAL, or 61.25 MHz for

NTSC (channel 3).

3.3.5 Lead-free Soldering

Due to lead-free technology some rules have to be respected

by the workshop during a repair:

• Use only lead-free soldering tin. If lead-free solder paste is

required, please contact the manufacturer of your soldering

equipment. In general, use of solder paste within

workshops should be avoided because paste is not easy to

store and to handle.

• Use only adequate solder tools applicable for lead-free

soldering tin. The solder tool must be able:

– To reach a solder-tip temperature of at least 400°C.

– To stabilize the adjusted temperature at the solder-tip.

– To exchange solder-tips for different applications.

• Adjust your solder tool so that a temperature of around

360°C - 380°C is reached and stabilized at the solder joint.

Heating time of the solder-joint should not exceed ~ 4 sec.

Avoid temperatures above 400°C, otherwise wear-out of

tips will increase drastically and flux-fluid will be destroyed.

To avoid wear-out of tips, switch “off” unused equipment or

reduce heat.

• Mix of lead-free soldering tin/parts with leaded soldering

tin/parts is possible but PHILIPS recommends strongly to

avoid mixed regimes. If this cannot be avoided, carefully

clear the solder-joint from old tin and re-solder with new tin.

3.3.6 Alternative BOM identification

It should be noted that on the European Service website,

“Alternative BOM” is referred to as “Design variant”.

back to

div. table

2010-Jun-25

Page 6

EN 6 Q552.1A LA3.

Precautions, Notes, and Abbreviation List

The third digit in the serial number (example:

AG2B0335000001) indicates the number of the alternative

B.O.M. (Bill Of Materials) that has been used for producing the

specific TV set. In general, it is possible that the same TV

model on the market is produced with e.g. two different types

of displays, coming from two different suppliers. This will then

result in sets which have the same CTN (Commercial Type

Number; e.g. 28PW9515/12) but which have a different B.O.M.

number.

By looking at the third digit of the serial number, one can

identify which B.O.M. is used for the TV set he is working with.

If the third digit of the serial number contains the number “1”

(example: AG1B033500001), then the TV set has been

manufactured according to B.O.M. number 1. If the third digit is

a “2” (example: AG2B0335000001), then the set has been

produced according to B.O.M. no. 2. This is important for

ordering the correct spare parts!

For the third digit, the numbers 1...9 and the characters A...Z

can be used, so in total: 9 plus 26= 35 different B.O.M.s can be

indicated by the third digit of the serial number.

Identification: The bottom line of a type plate gives a 14-digit

serial number. Digits 1 and 2 refer to the production centre (e.g.

AG is Bruges), digit 3 refers to the B.O.M. code, digit 4 refers

to the Service version change code, digits 5 and 6 refer to the

production year, and digits 7 and 8 refer to production week (in

example below it is 2006 week 17). The 6 last digits contain the

serial number.

MODEL :

PROD.NO:

32PF9968/10

AG 1A0617 000001

MADE IN BELGIUM

220-240V 50/60Hz

VHF+S+H+UHF

S

10000_024_090121.eps

~

BJ3.0E LA

Figure 3-1 Serial number (example)

3.3.7 Board Level Repair (BLR) or Component Level Repair (CLR)

If a board is defective, consult your repair procedure to decide

if the board has to be exchanged or if it should be repaired on

component level.

If your repair procedure says the board should be exchanged

completely, do not solder on the defective board. Otherwise, it

cannot be returned to the O.E.M. supplier for back charging!

3.3.8 Practical Service Precautions

• It makes sense to avoid exposure to electrical shock.

While some sources are expected to have a possible

dangerous impact, others of quite high potential are of

limited current and are sometimes held in less regard.

• Always respect voltages. While some may not be

dangerous in themselves, they can cause unexpected

reactions that are best avoided. Before reaching into a

powered TV set, it is best to test the high voltage insulation.

It is easy to do, and is a good service precaution.

128W

100105

3.4 Abbreviation List

0/6/12 SCART switch control signal on A/V

board. 0 = loop through (AUX to TV),

6 = play 16 : 9 format, 12 = play 4 : 3

format

AARA Automatic Aspect Ratio Adaptation:

algorithm that adapts aspect ratio to

remove horizontal black bars; keeps

the original aspect ratio

ACI Automatic Channel Installation:

algorithm that installs TV channels

directly from a cable network by

means of a predefined TXT page

ADC Analogue to Digital Converter

AFC Automatic Frequency Control: control

signal used to tune to the correct

frequency

AGC Automatic Gain Control: algorithm that

controls the video input of the feature

box

AM Amplitude Modulation

AP Asia Pacific

AR Aspect Ratio: 4 by 3 or 16 by 9

ASF Auto Screen Fit: algorithm that adapts

aspect ratio to remove horizontal black

bars without discarding video

information

ATSC Advanced Television Systems

Committee, the digital TV standard in

the USA

ATV See Auto TV

Auto TV A hardware and software control

system that measures picture content,

and adapts image parameters in a

dynamic way

AV External Audio Video

AVC Audio Video Controller

AVIP Audio Video Input Processor

B/G Monochrome TV system. Sound

carrier distance is 5.5 MHz

BDS Business Display Solutions (iTV)

BLR Board-Level Repair

BTSC Broadcast Television Standard

Committee. Multiplex FM stereo sound

system, originating from the USA and

used e.g. in LATAM and AP-NTSC

countries

B-TXT Blue TeleteXT

C Centre channel (audio)

CEC Consumer Electronics Control bus:

remote control bus on HDMI

connections

CL Constant Level: audio output to

connect with an external amplifier

CLR Component Level Repair

ComPair Computer aided rePair

CP Connected Planet / Copy Protection

CSM Customer Service Mode

CTI Color Transient Improvement:

manipulates steepness of chroma

transients

CVBS Composite Video Blanking and

Synchronization

DAC Digital to Analogue Converter

DBE Dynamic Bass Enhancement: extra

low frequency amplification

DCM Data Communication Module. Also

referred to as System Card or

Smartcard (for iTV).

DDC See “E-DDC”

D/K Monochrome TV system. Sound

carrier distance is 6.5 MHz

DFI Dynamic Frame Insertion

2010-Jun-25

back to

div. table

Page 7

Precautions, Notes, and Abbreviation List

EN 7Q552.1A LA 3.

DFU Directions For Use: owner's manual

DMR Digital Media Reader: card reader

DMSD Digital Multi Standard Decoding

DNM Digital Natural Motion

DNR Digital Noise Reduction: noise

reduction feature of the set

DRAM Dynamic RAM

DRM Digital Rights Management

DSP Digital Signal Processing

DST Dealer Service Tool: special remote

control designed for service

technicians

DTCP Digital Transmission Content

Protection; A protocol for protecting

digital audio/video content that is

traversing a high speed serial bus,

such as IEEE-1394

DVB-C Digital Video Broadcast - Cable

DVB-T Digital Video Broadcast - Terrestrial

DVD Digital Versatile Disc

DVI(-d) Digital Visual Interface (d= digital only)

E-DDC Enhanced Display Data Channel

(VESA standard for communication

channel and display). Using E-DDC,

the video source can read the EDID

information form the display.

EDID Extended Display Identification Data

(VESA standard)

EEPROM Electrically Erasable and

Programmable Read Only Memory

EMI Electro Magnetic Interference

EPG Electronic Program Guide

EPLD Erasable Programmable Logic Device

EU Europe

EXT EXTernal (source), entering the set by

SCART or by cinches (jacks)

FDS Full Dual Screen (same as FDW)

FDW Full Dual Window (same as FDS)

FLASH FLASH memory

FM Field Memory or Frequency

Modulation

FPGA Field-Programmable Gate Array

FTV Flat TeleVision

Gb/s Giga bits per second

G-TXT Green TeleteXT

H H_sync to the module

HD High Definition

HDD Hard Disk Drive

HDCP High-bandwidth Digital Content

Protection: A “key” encoded into the

HDMI/DVI signal that prevents video

data piracy. If a source is HDCP coded

and connected via HDMI/DVI without

the proper HDCP decoding, the

picture is put into a “snow vision” mode

or changed to a low resolution. For

normal content distribution the source

and the display device must be

enabled for HDCP “software key”

decoding.

HDMI High Definition Multimedia Interface

HP HeadPhone

I Monochrome TV system. Sound

2

I

C Inter IC bus

2

I

D Inter IC Data bus

2

I

S Inter IC Sound bus

carrier distance is 6.0 MHz

IF Intermediate Frequency

IR Infra Red

IRQ Interrupt Request

ITU-656 The ITU Radio communication Sector

(ITU-R) is a standards body

subcommittee of the International

Telecommunication Union relating to

radio communication. ITU-656 (a.k.a.

back to

div. table

SDI), is a digitized video format used

for broadcast grade video.

Uncompressed digital component or

digital composite signals can be used.

The SDI signal is self-synchronizing,

uses 8 bit or 10 bit data words, and has

a maximum data rate of 270 Mbit/s,

with a minimum bandwidth of 135

MHz.

ITV Institutional TeleVision; TV sets for

hotels, hospitals etc.

LS Last Status; The settings last chosen

by the customer and read and stored

in RAM or in the NVM. They are called

at start-up of the set to configure it

according to the customer's

preferences

LATAM Latin America

LCD Liquid Crystal Display

LED Light Emitting Diode

L/L' Monochrome TV system. Sound

carrier distance is 6.5 MHz. L' is Band

I, L is all bands except for Band I

LPL LG.Philips LCD (supplier)

LS Loudspeaker

LVDS Low Voltage Differential Signalling

Mbps Mega bits per second

M/N Monochrome TV system. Sound

carrier distance is 4.5 MHz

MHEG Part of a set of international standards

related to the presentation of

multimedia information, standardised

by the Multimedia and Hypermedia

Experts Group. It is commonly used as

a language to describe interactive

television services

MIPS Microprocessor without Interlocked

Pipeline-Stages; A RISC-based

microprocessor

MOP Matrix Output Processor

MOSFET Metal Oxide Silicon Field Effect

Transistor, switching device

MPEG Motion Pictures Experts Group

MPIF Multi Platform InterFace

MUTE MUTE Line

MTV Mainstream TV: TV-mode with

Consumer TV features enabled (iTV)

NC Not Connected

NICAM Near Instantaneous Compounded

Audio Multiplexing. This is a digital

sound system, mainly used in Europe.

NTC Negative Temperature Coefficient,

non-linear resistor

NTSC National Television Standard

Committee. Color system mainly used

in North America and Japan. Color

carrier NTSC M/N= 3.579545 MHz,

NTSC 4.43= 4.433619 MHz (this is a

VCR norm, it is not transmitted off-air)

NVM Non-Volatile Memory: IC containing

TV related data such as alignments

O/C Open Circuit

OSD On Screen Display

OAD Over the Air Download. Method of

software upgrade via RF transmission.

Upgrade software is broadcasted in

TS with TV channels.

OTC On screen display Teletext and

Control; also called Artistic (SAA5800)

P50 Project 50: communication protocol

between TV and peripherals

PAL Phase Alternating Line. Color system

mainly used in West Europe (color

carrier= 4.433619 MHz) and South

America (color carrier PAL M=

2010-Jun-25

Page 8

EN 8 Q552.1A LA3.

Precautions, Notes, and Abbreviation List

3.575612 MHz and PAL N= 3.582056

MHz)

PCB Printed Circuit Board (same as “PWB”)

PCM Pulse Code Modulation

PDP Plasma Display Panel

PFC Power Factor Corrector (or Pre-

conditioner)

PIP Picture In Picture

PLL Phase Locked Loop. Used for e.g.

FST tuning systems. The customer

can give directly the desired frequency

POD Point Of Deployment: a removable

CAM module, implementing the CA

system for a host (e.g. a TV-set)

POR Power On Reset, signal to reset the uP

PSDL Power Supply for Direct view LED

backlight with 2D-dimming

PSL Power Supply with integrated LED

drivers

PSLS Power Supply with integrated LED

drivers with added Scanning

functionality

PTC Positive Temperature Coefficient,

non-linear resistor

PWB Printed Wiring Board (same as “PCB”)

PWM Pulse Width Modulation

QRC Quasi Resonant Converter

QTNR Quality Temporal Noise Reduction

QVCP Quality Video Composition Processor

RAM Random Access Memory

RGB Red, Green, and Blue. The primary

color signals for TV. By mixing levels

of R, G, and B, all colors (Y/C) are

reproduced.

RC Remote Control

RC5 / RC6 Signal protocol from the remote

control receiver

RESET RESET signal

ROM Read Only Memory

RSDS Reduced Swing Differential Signalling

data interface

R-TXT Red TeleteXT

SAM Service Alignment Mode

S/C Short Circuit

SCART Syndicat des Constructeurs

d'Appareils Radiorécepteurs et

Téléviseurs

SCL Serial Clock I

2

C

SCL-F CLock Signal on Fast I

SD Standard Definition

SDA Serial Data I

2

C

SDA-F DAta Signal on Fast I

SDI Serial Digital Interface, see “ITU-656”

SDRAM Synchronous DRAM

SECAM SEequence Couleur Avec Mémoire.

Color system mainly used in France

and East Europe. Color carriers=

4.406250 MHz and 4.250000 MHz

SIF Sound Intermediate Frequency

SMPS Switched Mode Power Supply

SoC System on Chip

SOG Sync On Green

SOPS Self Oscillating Power Supply

SPI Serial Peripheral Interface bus; a 4-

wire synchronous serial data link

standard

S/PDIF Sony Philips Digital InterFace

SRAM Static RAM

SRP Service Reference Protocol

SSB Small Signal Board

SSC Spread Spectrum Clocking, used to

reduce the effects of EMI

STB Set Top Box

STBY STand-BY

SVGA 800 × 600 (4:3)

2010-Jun-25

2

C bus

2

C bus

back to

div. table

SVHS Super Video Home System

SW Software

SWAN Spatial temporal Weighted Averaging

Noise reduction

SXGA 1280 × 1024

TFT Thin Film Transistor

THD Total Harmonic Distortion

TMDS Transmission Minimized Differential

Signalling

TS Transport Stream

TXT TeleteXT

TXT-DW Dual Window with TeleteXT

UI User Interface

uP Microprocessor

UXGA 1 600 × 1 200 (4:3)

V V-sync to the module

VESA Video Electronics Standards

Association

VGA 640 × 480 (4:3)

VL Variable Level out: processed audio

output toward external amplifier

VSB Vestigial Side Band; modulation

method

WYSIWYR What You See Is What You Record:

record selection that follows main

picture and sound

WXGA 1280 × 768 (15:9)

XTAL Quartz crystal

XGA 1 024 × 768 (4:3)

Y Luminance signal

Y/C Luminance (Y) and Chrominance (C)

signal

YPbPr Component video. Luminance and

scaled color difference signals (B-Y

and R-Y)

YUV Component video

Page 9

4. Mechanical Instructions

18990_100_100401.eps

100401

Index of this chapter:

4.1 Cable Dressing Matisse styling (8000 series)

4.2 Cable Dressing da Vinci styling (6000 series)

4.3 Service Positions

4.4 Assy/Panel Removal Matisse Styling (8000 series)

4.5 Assy/Panel Removal da Vinci Styling (6000 series)

4.6 Set Re-assembly

Mechanical Instructions

4.1 Cable Dressing Matisse styling (8000 series)

EN 9Q552.1A LA 4.

Notes:

• Figures below can deviate slightly from the actual situation,

due to the different set executions.

Note: pictures are taken from the European equivalent (with

SCART connector).

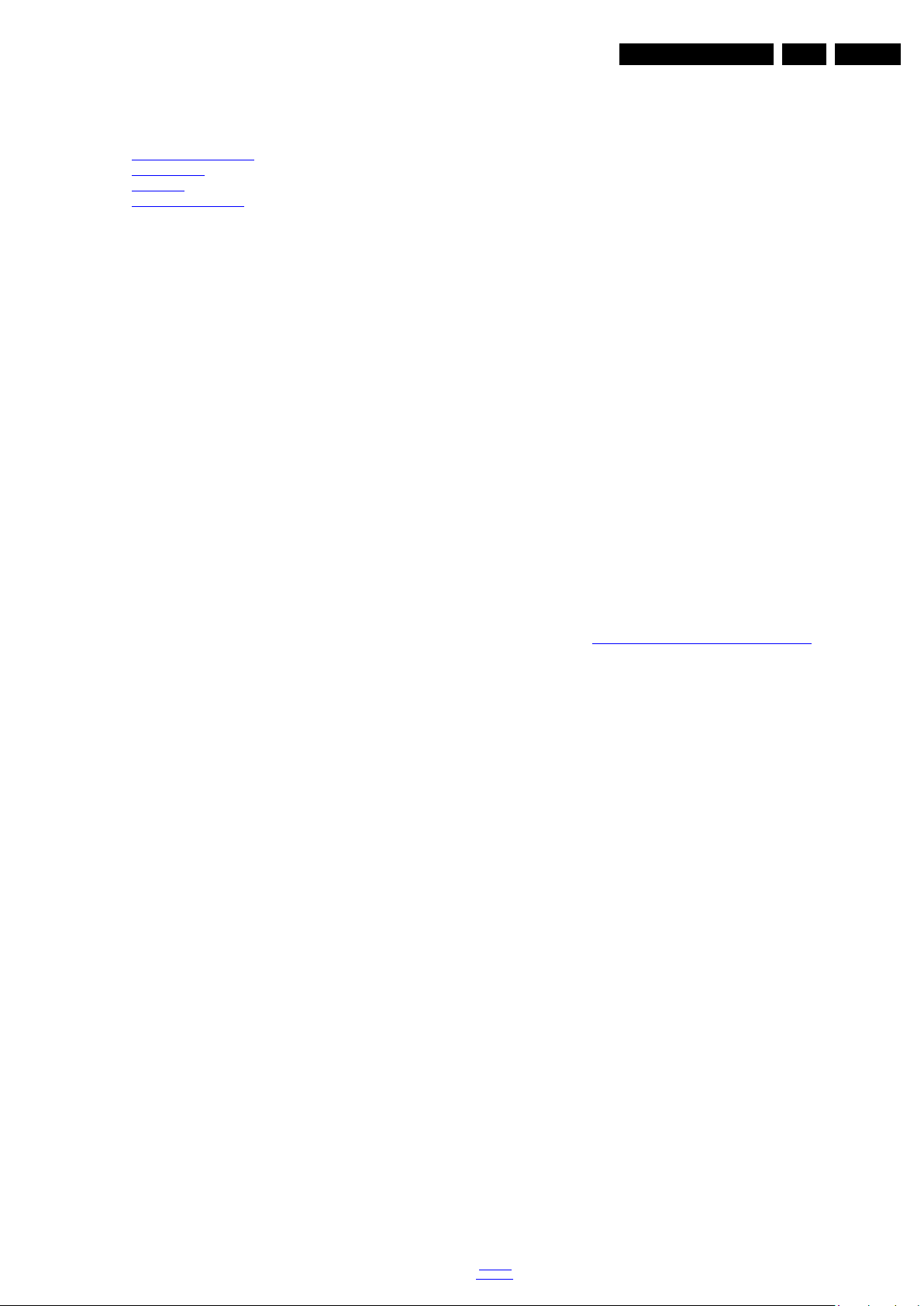

Figure 4-1 Cable dressing 42" 8000-series

back to

div. table

2010-Jun-25

Page 10

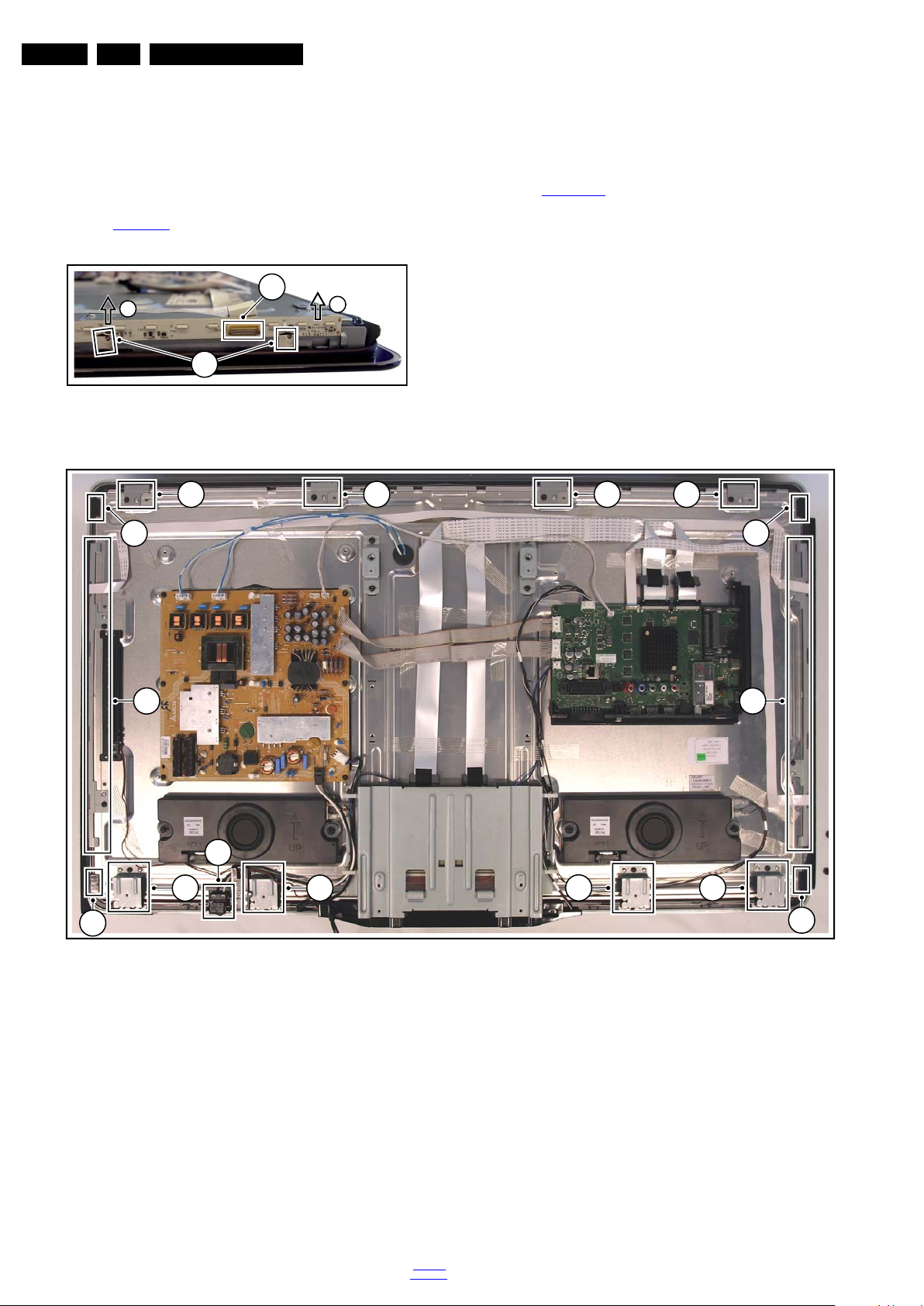

EN 10 Q552.1A LA4.

18990_101_100401.eps

100401

Mechanical Instructions

Figure 4-2 Cable dressing 46" 8000-series

2010-Jun-25

back to

div. table

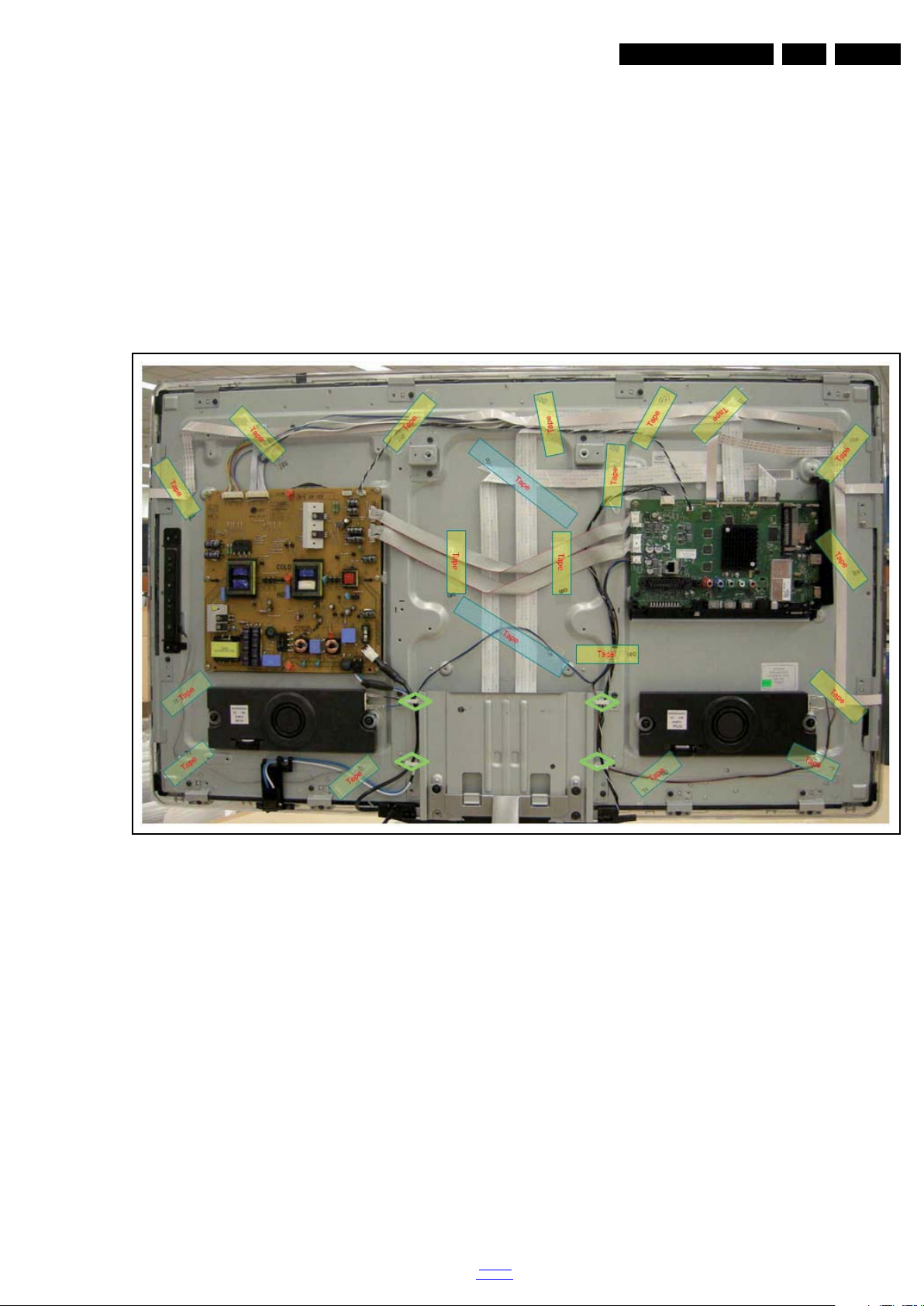

Page 11

Mechanical Instructions

18991_100_100601.eps

100601

EN 11Q552.1A LA 4.

Figure 4-3 Cable dressing 52" 8000-series

back to

div. table

2010-Jun-25

Page 12

EN 12 Q552.1A LA4.

18991_101_100601.eps

100601

Mechanical Instructions

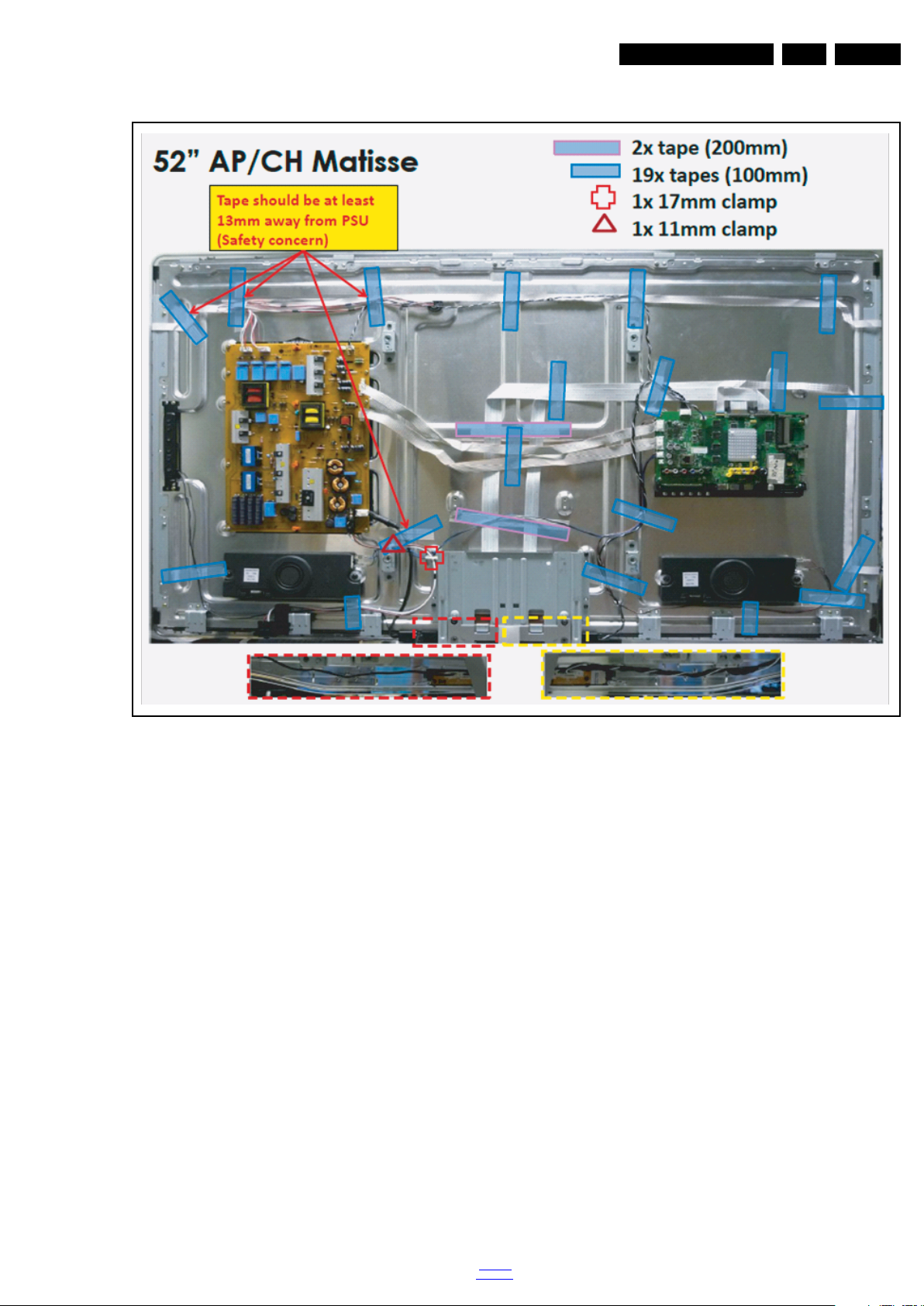

4.2 Cable Dressing da Vinci styling (6000 series)

Figure 4-4 Cable dressing 40" 6000-series

2010-Jun-25

back to

div. table

Page 13

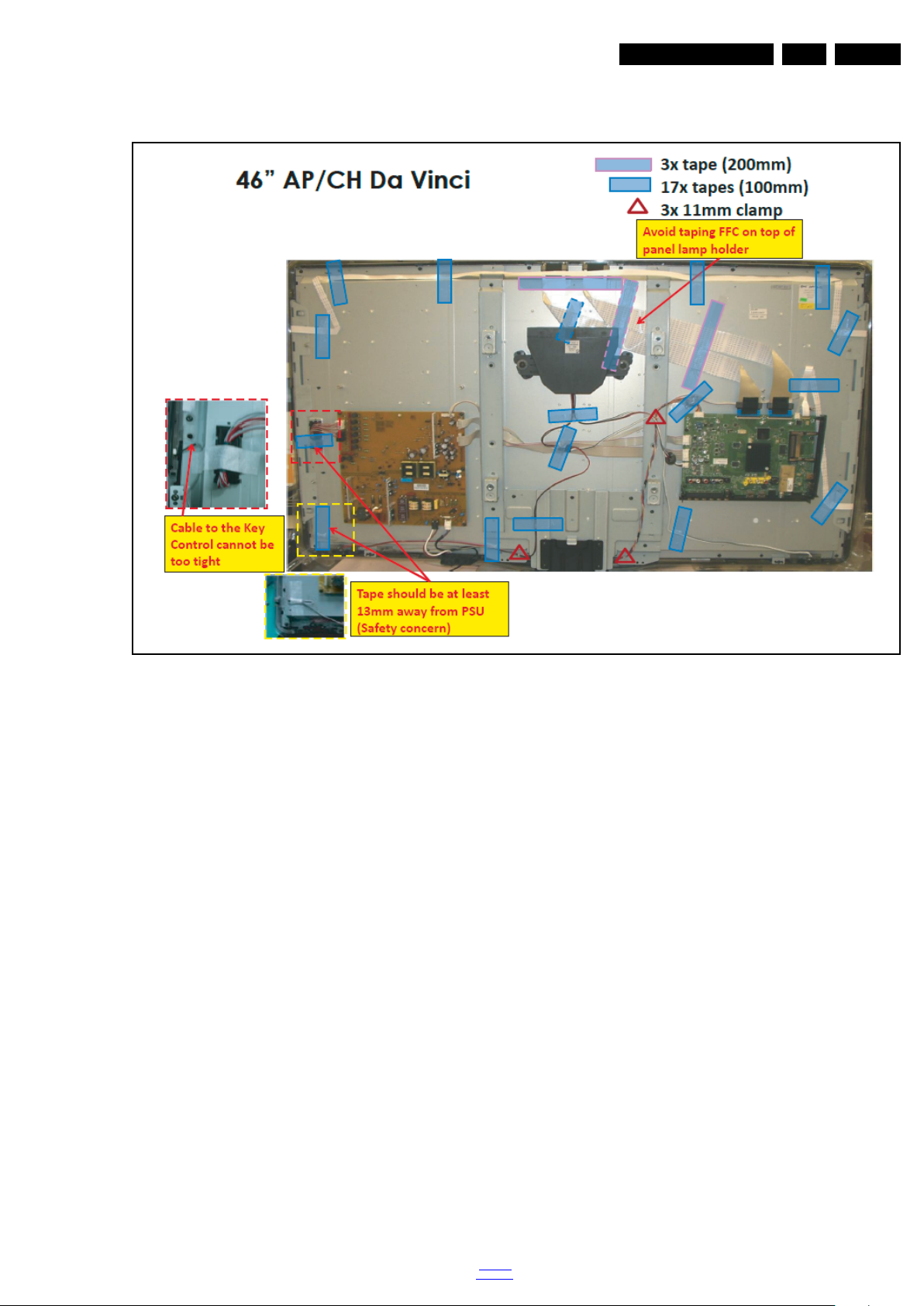

Mechanical Instructions

18991_102_100601.eps

100601

EN 13Q552.1A LA 4.

Figure 4-5 Cable dressing 46" 6000-series

back to

div. table

2010-Jun-25

Page 14

EN 14 Q552.1A LA4.

Mechanical Instructions

4.3 Service Positions

For easy servicing of a TV set, the set should be put face down

on a soft flat surface, foam buffers or other specific workshop

tools. Ensure that a stable situation is created to perform

measurements and alignments. When using foam bars take

care that these always support the cabinet and never only the

display. Caution: Failure to follow these guidelines can

seriously damage the display!

Ensure that ESD safe measures are taken.

4.4 Assy/Panel Removal Matisse Styling (8000 series)

The instructions apply to the Q552.1E LA chassis

(40PFL7605H/12), but are similar for other models.

4.4.1 Rear Cover

Warning: Disconnect the mains power cord before you remove

the rear cover.

Note: it is not necessary to remove the stand while removing

the rear cover.

1. Remove all screws of the rear cover.

2. Lift the rear cover from the TV. Make sure that wires and

flat coils are not damaged while lifting the rear cover from

the set.

4.4.2 Speakers

Each speakerbox unit is mounted with two screws.

When defective, replace the whole unit.

2010-Jun-25

back to

div. table

Page 15

Mechanical Instructions

18771_108_100504.eps

100504

1

1

1

2

22

22

2

2

2

18771_109_100504.eps

100505

1

4

2

5

1

3

3

3

3

3

18771_110_100504.eps

100504

31 31

EN 15Q552.1A LA 4.

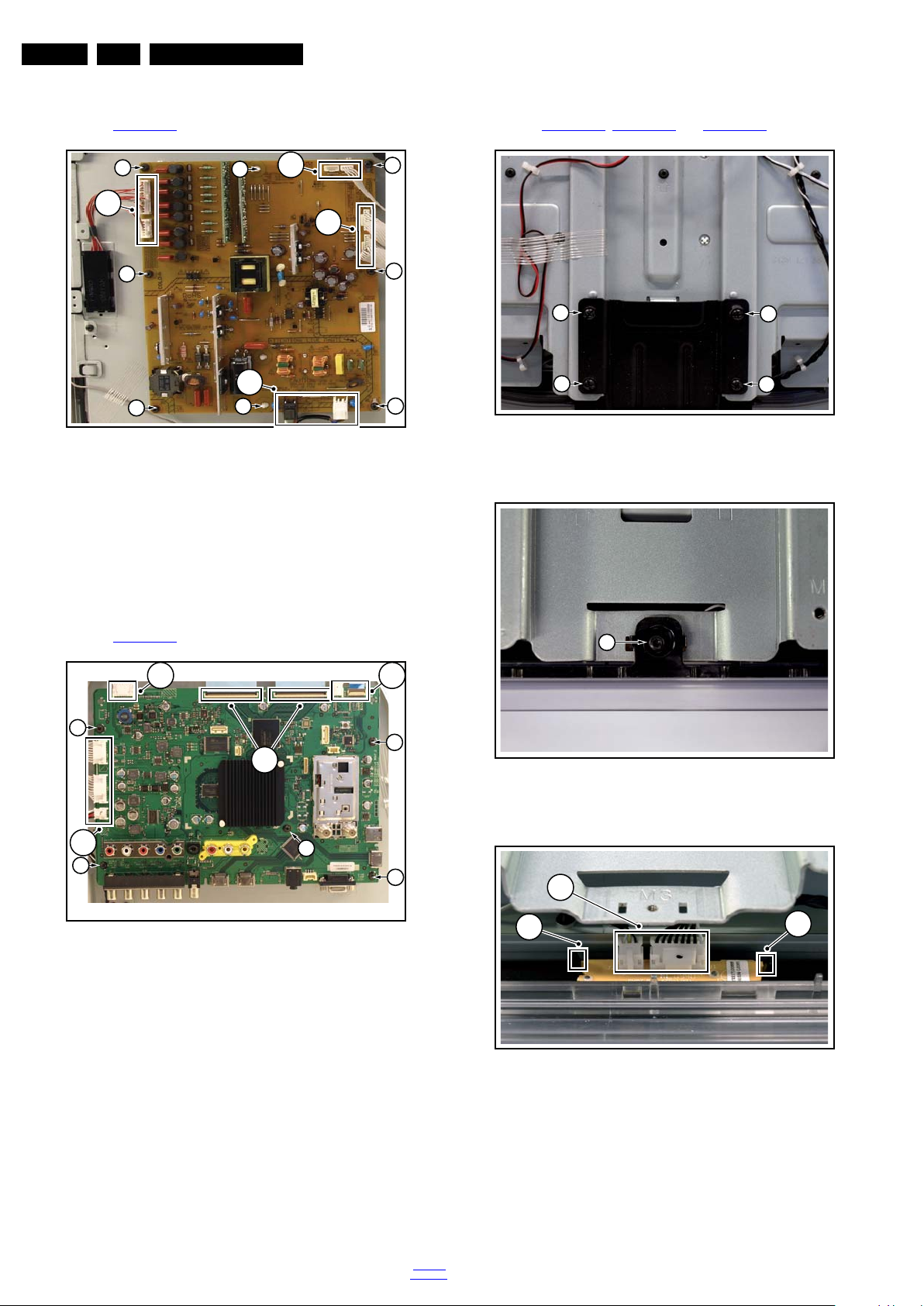

4.4.3 Main Power Supply

Refer to Figure 4-6

for details.

Figure 4-6 Main Power Supply

1. Unplug all connectors [1].

2. Remove the fixation screws [2].

3. Take the board out.

When defective, replace the whole unit.

4.4.4 Small Signal Board (SSB)

4.4.5 IR & LED Board

Refer to Figure 4-8

for details.

Figure 4-8 IR & LED Board

1. Remove the stand.

2. Remove the IR & LED board cover [1].

Now the IR & LED board can be accessed.

When defective, replace the whole unit.

Refer to Figure 4-7

for details.

Figure 4-7 SSB

1. Unplug all connectors [1].

2. Slide the side cover sidewards [2].

3. Remove the fixation screws [3].

4. Lift the clip [4].

5. Remove the bottom cover downwards [5].

6. Take the board out.

back to

div. table

2010-Jun-25

Page 16

EN 16 Q552.1A LA4.

18771_112_100504.eps

100504

4

3

3

3

3

4 4 4

22

5

2

5

2

1

Mechanical Instructions

4.4.6 Keyboard Control Board

The keyboard control panel is mounted on the LCD panel with

two screws.

When defective, replace the whole unit.

4.4.7 Ambilight Units

Refer to Figure 4-9

for details.

Note: the Ambilight units are to be swapped on PWB level.

1

3

2

18771_111_100504.eps

Figure 4-9 Ambilight units

1. Unplug the flat foil(s) [1].

2. Release the clips [2] that secure the PWB.

3. Slide the PWB out of the set [3].

4.4.8 LCD Panel

Refer to Figure 4-10

for details.

1. Remove the stand.

2. Remove all boards as described earlier.

3. Remove all cables from the set.

4. Remove the speaker boxes as earlier described.

5. Remove the IR & LED board cover as described earlier.

6. Remove the mains switch [1].

3

7. Remove the keyboard control panel as described earlier.

8. Remove the clamps [2]. Pay attention to the positioning

of the different screws!

9. Remove the plastic clamps [3].

10. Tilt the clamps [4] after having removed the screw.

11. Remove the Ambilight PWBs as earlier described.

100504

12. Tilt the Ambilight subframes [5] after having removed the

screw.

Now the LCD Panel can be lifted from the front cabinet.

Pay special attention to use the correct screws at the

proper location when mounting a new LCD panel!

Using the wrong screws will damage the LCD panel!

4.5 Assy/Panel Removal da Vinci Styling (6000 series)

Instructions below apply to the LC9.3L LA chassis

(32PFL6605D/xx), but are similar for other models.

2010-Jun-25

Figure 4-10 LCD Panel

back to

div. table

Page 17

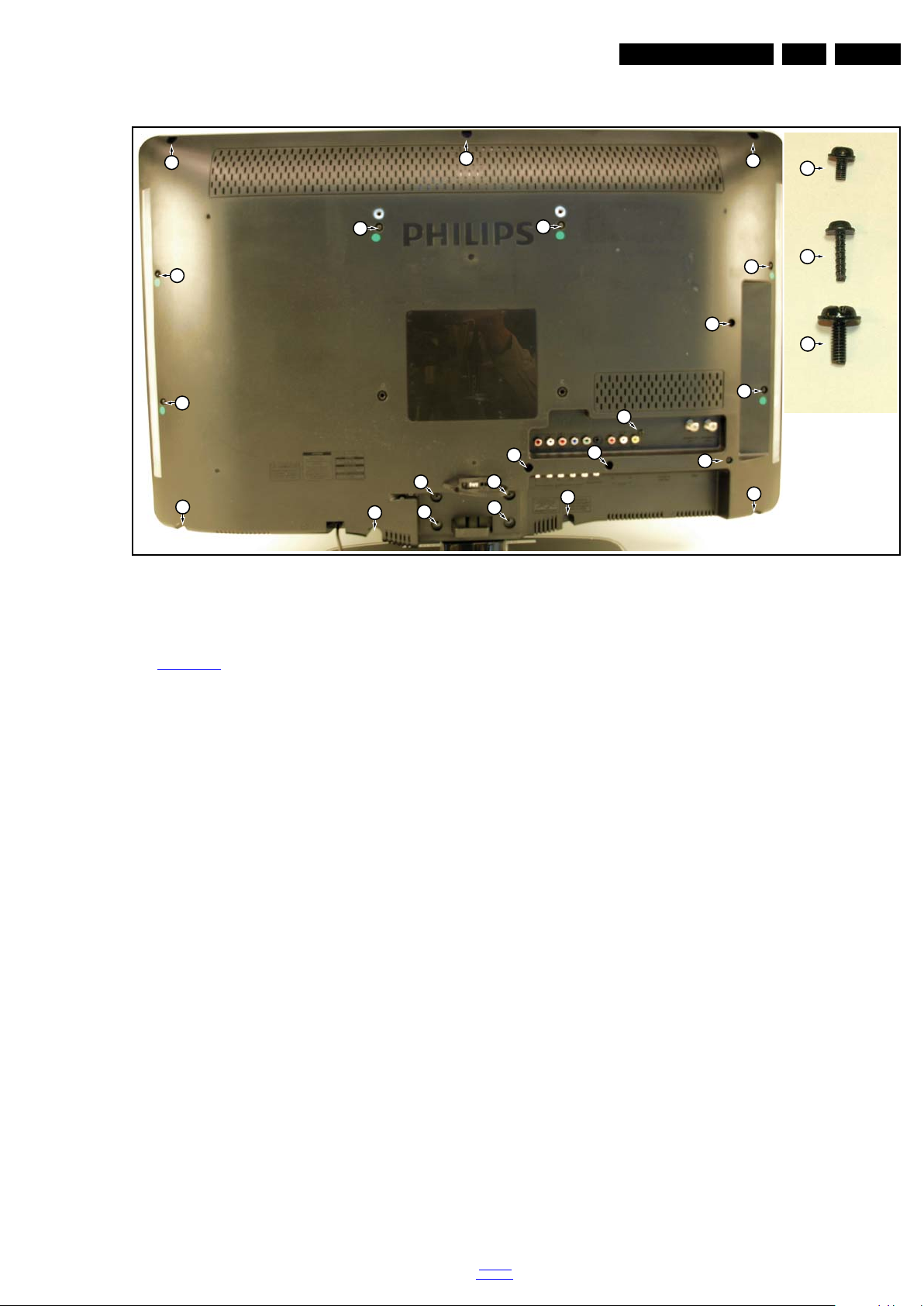

4.5.1 Rear Cover

18970_113_100326.eps

100326

3

3

2

2

2

2

2

2

2

2

2

1

1

1

1

2

2

2

3

3

3

3

2

3

1

Mechanical Instructions

EN 17Q552.1A LA 4.

Figure 4-11 Rear cover removal (32")

Warning: Disconnect the mains power cord before removing

the rear cover.

See Figure 4-11

1. Remove fixation screws [2] and [3] that secure the rear

cover. It is not necessary to remove the stand first [1].

2. Lift the rear cover from the TV. Make sure that wires and

flat foils are not damaged while lifting the rear cover from

the set.

4.5.2 Speakers

Tweeters (when applicable)

Each tweeter unit is mounted with one screw.

When defective, replace the whole unit.

Loudspeaker/subwoofer

The loudspeaker/subwoofer is located in the centre of the set,

and is fixed with two screws.

When defective, replace the whole unit.

.

back to

div. table

2010-Jun-25

Page 18

EN 18 Q552.1A LA4.

18970_103_100323.eps

100323

1

2

2

2

2

2

2

1

3

3

1

1

18770_142_100215.eps

100215

1

1

1

1

18770_143_100215.eps

100215

2

18770_144_100215.eps

100215

4

3

3

Mechanical Instructions

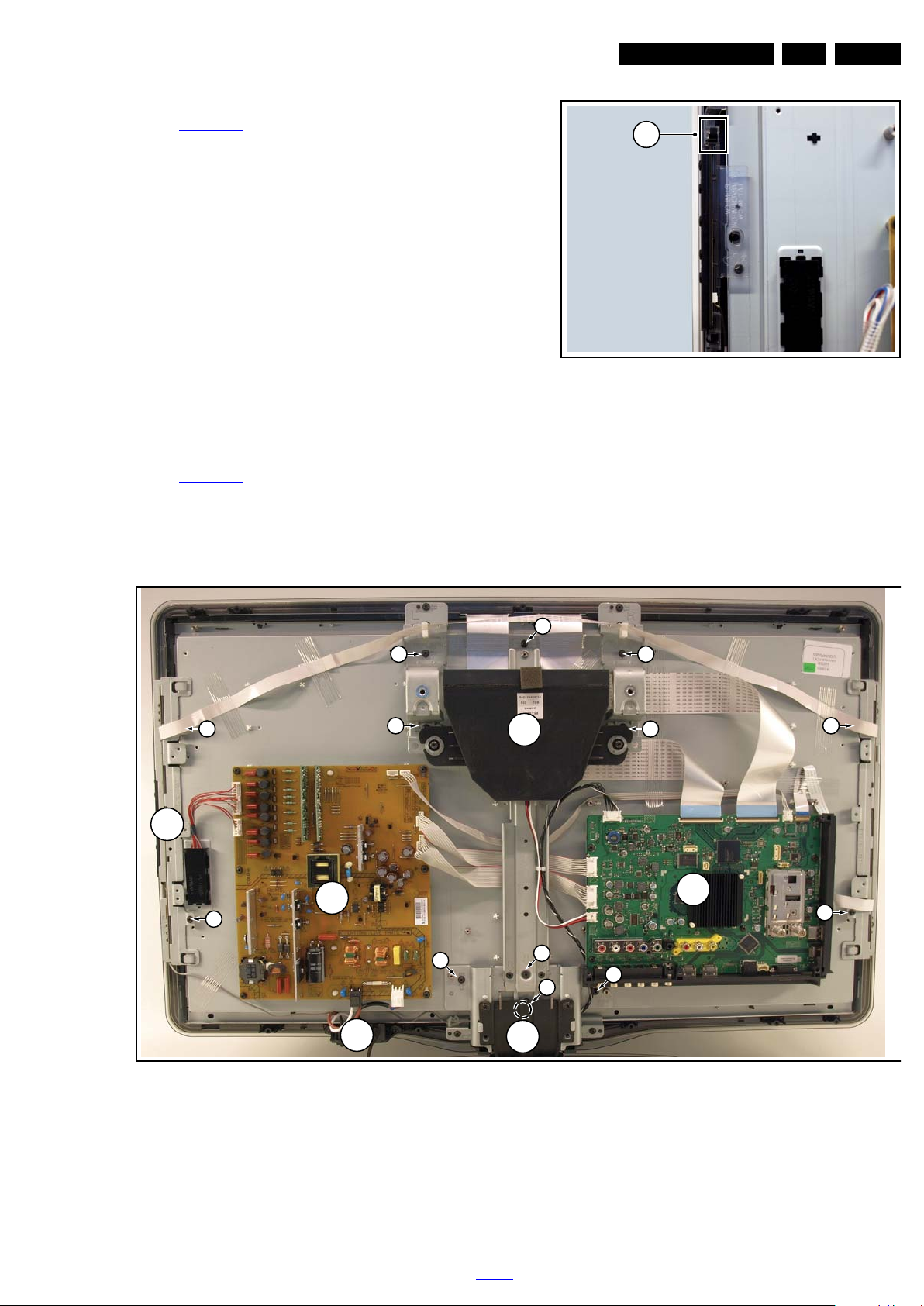

4.5.3 Main Power Supply

Refer to Figure 4-12

for details.

Figure 4-12 Main Power Supply

1. Unplug all connectors [1].

2. Remove the fixation screws [2].

3. Take the board out.

When defective, replace the whole unit.

Be aware to (re)place the spacers [3].

4.5.6 IR & LED Board

Refer to Figure 4-14

Figure 4-14 IR & LED Board -1-

, Figure 4-15 and Figure 4-16 for details.

4.5.4 Small Signal Board (SSB)

Refer to Figure 4-13

for details.

2

3

1

2

3

3

18970_104_100323.eps

Figure 4-13 SSB

1. Unplug all connectors [1] and [2].

2. Remove the fixation screws [3].

3. Take the board out.

When defective, replace the whole unit.

4.5.5 Mains Switch

The mains switch assy is mounted below the PSU on the front

bezel with two screws.

When replacing the switch, remove it from its bracket.

2

3

Figure 4-15 IR & LED Board -2-

3

100323

Figure 4-16 IR & LED Board -3-

1. Remove the stand [1].

2. Remove the IR & LED board cover [2].

3. Release the clips [3] that secure the IR & LED board.

4. Remove the connectors [4] on the IR/LED board.

2010-Jun-25

back to

div. table

Page 19

4.5.7 Local Control Board

18770_145_100216.eps

100217

1

18970_112_100326.eps

100326

1

1

1

1

2

2

1

2

2

1

1

1

C

D

A

B

E

1

F

Mechanical Instructions

EN 19Q552.1A LA 4.

Refer to Figure 4-17

1. Unplug the connector on the IR & LED board that leads to

the Local Control board as described earlier.

2. Release the cable from its clamps/tape.

3. Release the clip on top of the unit [1] and take the unit out.

When defective, replace the whole unit.

4.5.8 LCD Panel

Refer to Figure 4-18

1. Remove the Stand and IR/LED board [A] as earlier

described.

2. Remove the Speakers/Subwoofer [B] as earlier described.

3. Remove the PSU [C] and SSB [D] as earlier described.

4. Remove the Mains Switch [E] as earlier described.

for details.

for details.

Figure 4-17 Local Control board

5. Remove the Local Control board [F] as earlier described.

6. Remove the brackets [1].

7. Remove the clamps [2].

8. Remove the flare.

Now the LCD Panel can be lifted from the front cabinet.

4.6 Set Re-assembly

To re-assemble the whole set, execute all processes in reverse

order.

Notes:

back to

div. table

• While re-assembling, make sure that all cables are placed

and connected in their original position.

• Pay special attention not to damage the EMC foams in the

set. Ensure that EMC foams are mounted correctly.

Figure 4-18 LCD Panel removal (based on 32" AL model)

2010-Jun-25

Page 20

EN 20 Q552.1A LA5.

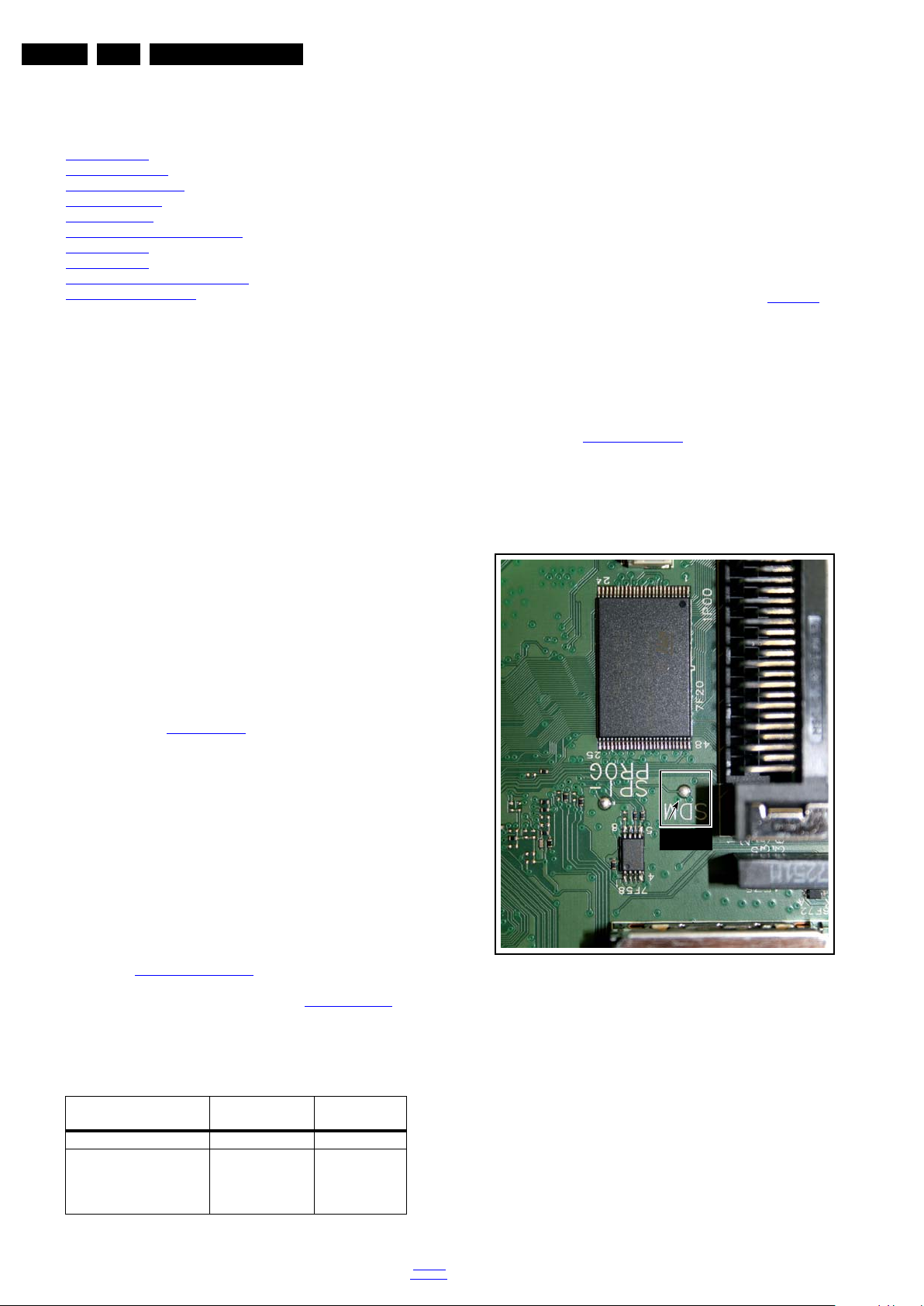

18770_249_100215.eps

100407

SDM

Service Modes, Error Codes, and Fault Finding

5. Service Modes, Error Codes, and Fault Finding

Index of this chapter:

5.1 Test Points

5.2 Service Modes

5.3 Stepwise Start-up

5.4 Service Tools

5.5 Error Codes

5.6 The Blinking LED Procedure

5.7 Protections

5.7 Protections

5.8 Fault Finding and Repair Tips

5.9 Software Upgrading

5.1 Test Points

As most signals are digital, it will be difficult to measure

waveforms with a standard oscilloscope. However, several key

ICs are capable of generating test patterns, which can be

controlled via ComPair. In this way it is possible to determine

which part is defective.

Perform measurements under the following conditions:

• Service Default Mode.

• Video: Colour bar signal.

• Audio: 3 kHz left, 1 kHz right.

5.2 Service Modes

Service Default mode (SDM) and Service Alignment Mode

(SAM) offers several features for the service technician, while

the Customer Service Mode (CSM) is used for communication

between the call centre and the customer.

• Sound volume at 25%.

• All service-unfriendly modes (if present) are disabled, like:

– (Sleep) timer.

– Child/parental lock.

– Picture mute (blue mute or black mute).

– Automatic volume levelling (AVL).

– Skip/blank of non-favourite pre-sets.

How to Activate SDM

For this chassis there are two kinds of SDM: an analogue SDM

and a digital SDM. Tuning will happen according Table 5-1

• Analogue SDM: use the standard RC-transmitter and key

in the code “062596”, directly followed by the “MENU” (or

“HOME”) button.

Note: It is possible that, together with the SDM, the main

menu will appear. To switch it “off”, push the “MENU” (or

"HOME") button again.

Analogue SDM can also be activated by grounding for a

moment the solder path on the SSB, with the indication

“SDM” (see Service mode pad

• Digital SDM: use the standard RC-transmitter and key in

the code “062593”, directly followed by the “MENU” (or

"HOME") button.

Note: It is possible that, together with the SDM, the main

menu will appear. To switch it “off”, push the “MENU” (or

"HOME") button again.

).

.

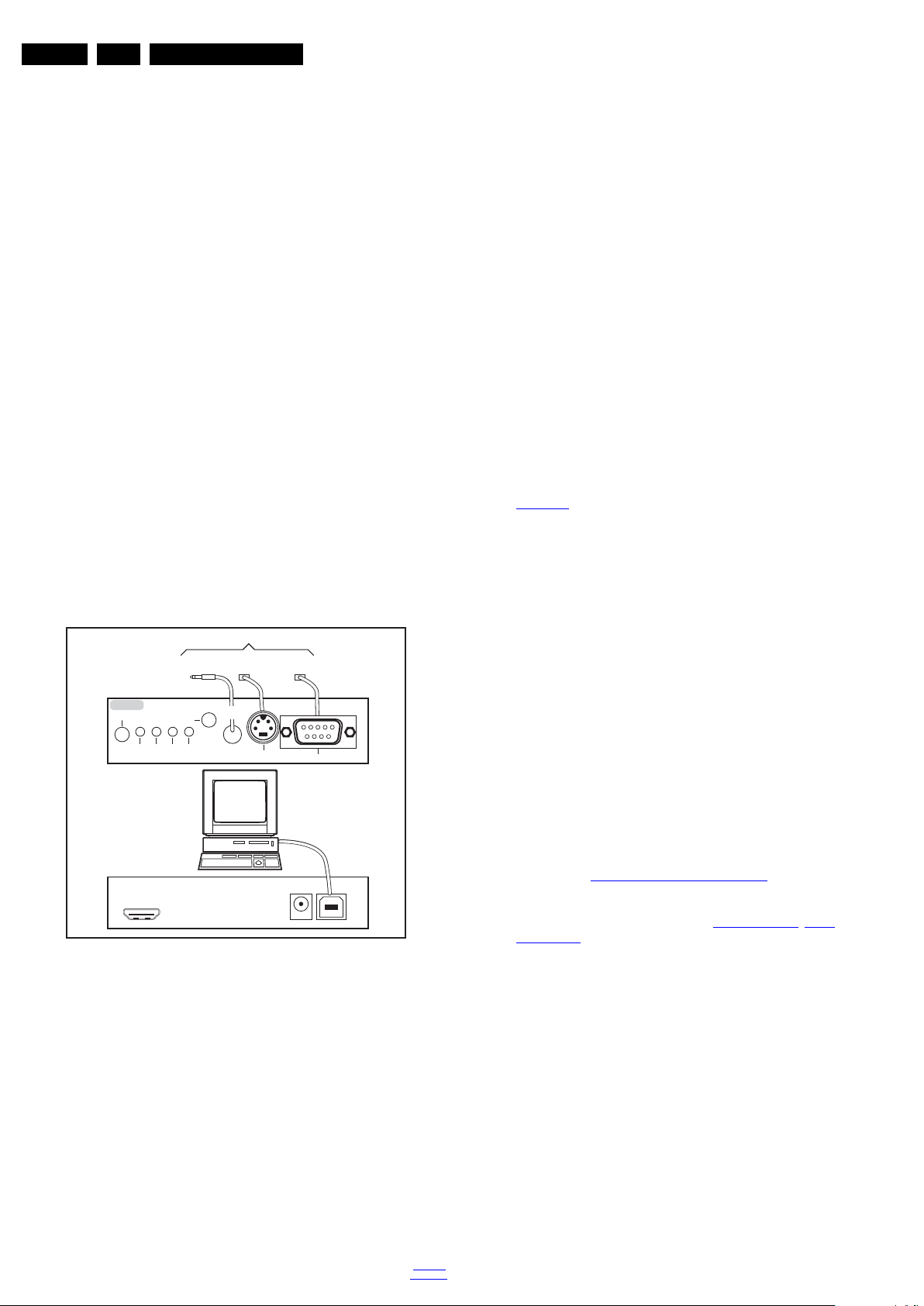

This chassis also offers the option of using ComPair, a

hardware interface between a computer and the TV chassis. It

offers the abilities of structured troubleshooting, error code

reading, and software version read-out for all chassis.

(see also section “5.4.1 ComPair

Note: For the new model range, a new remote control (RC) is

used with some renamed buttons. This has an impact on the

activation of the Service modes. For instance the old “MENU”

button is now called “HOME” (or is indicated by a “house” icon).

5.2.1 Service Default Mode (SDM)

Purpose

• To create a pre-defined setting, to get the same

measurement results as given in this manual.

• To override SW protections detected by stand-by

processor and make the TV start up to the step just before

protection (a sort of automatic stepwise start-up). See

section “5.3 Stepwise Start-up

• To start the blinking LED procedure where only LAYER 2

errors are displayed. (see also section “5.5 Error Codes

Specifications

Table 5-1 SDM default settings

Region Freq. (MHz)

Europe, AP(PAL/Multi) 475.25 PAL B/G

Europe, AP DVB-T 546.00 PID

• All picture settings at 50% (brightness, colour, contrast).

2010-Jun-25

”).

”.

Video: 0B 06 PID

PCR: 0B 06 PID

Audio: 0B 07

Default

system

DVB-T

”).

back to

div. table

Figure 5-1 Service mode pad

After activating this mode, “SDM” will appear in the upper right

corner of the screen (when a picture is available).

How to Navigate

When the “MENU” (or “HOME”) button is pressed on the RC

transmitter, the TV set will toggle between the SDM and the

normal user menu.

How to Exit SDM

Use one of the following methods:

• Switch the set to STAND-BY via the RC-transmitter.

• Via a standard customer RC-transmitter: key in “00”sequence.

Page 21

Service Modes, Error Codes, and Fault Finding

PHILIPS

MODEL:

32PF9968/10

PROD.SERIAL NO:

AG 1A0620 000001

040

39mm

27mm

(CTN Sticker)

Display Option

Code

E_06532_038.eps

240108

EN 21Q552.1A LA 5.

5.2.2 Service Alignment Mode (SAM)

Purpose

• To perform (software) alignments.

• To change option settings.

• To easily identify the used software version.

• To view operation hours.

• To display (or clear) the error code buffer.

How to Activate SAM

Via a standard RC transmitter: Key in the code “062596”

directly followed by the “INFO” (or “OK”) button. After activating

SAM with this method a service warning will appear on the

screen, continue by pressing the “OK” button on the RC.

Contents of SAM (see also Table 6-11

• Hardware Info.

– A. SW Version. Displays the software version of the

main software (example: Q555X-1.2.3.4 =

AAAAB_X.Y.W.Z).

• AAAA= the chassis name.

• B= the SW branch version. This is a sequential

number (this is no longer the region indication, as

the software is now multi-region).

• X.Y.W.Z= the software version, where X is the

main version number (different numbers are not

compatible with one another) and Y.W.Z is the sub

version number (a higher number is always

compatible with a lower number).

– B. STBY PROC Version. Displays the software

version of the stand-by processor.

– C. Production Code. Displays the production code of

the TV, this is the serial number as printed on the back

of the TV set. Note that if an NVM is replaced or is

initialized after corruption, this production code has to

be re-written to NVM. ComPair will foresee in a

possibility to do this.

• Operation Hours. Displays the accumulated total of

operation hours (not the stand-by hours). Every time the

TV is switched “on/off”, 0.5 hours is added to this number.

• Errors (followed by maximum 10 errors). The most recent

error is displayed at the upper left (for an error explanation

see section “5.5 Error Codes

• Reset Error Buffer. When “cursor right” (or the “OK”

button) is pressed and then the “OK” button is pressed, the

error buffer is reset.

• Alignments. This will activate the “ALIGNMENTS” submenu. See Chapter 6. Alignments

• Dealer Options. Extra features for the dealers.

• Options. Extra features for Service. For more info

regarding option codes, 6. Alignments

Note that if the option code numbers are changed, these

have to be confirmed with pressing the “OK” button before

the options are stored, otherwise changes will be lost.

• Initialize NVM. The moment the processor recognizes a

corrupted NVM, the “initialize NVM” line will be highlighted.

Now, two things can be done (dependent of the service

instructions at that moment):

– Save the content of the NVM via ComPair for

development analysis, before initializing. This will give

the Service department an extra possibility for

diagnosis (e.g. when Development asks for this).

– Initialize the NVM.

Note: When the NVM is corrupted, or replaced, there is a high

possibility that no picture appears because the display code is

not correct. So, before initializing the NVM via the SAM, a

picture is necessary and therefore the correct display option

has to be entered. Refer to Chapter 6. Alignments

To adapt this option, it’s advised to use ComPair (the correct

values for the options can be found in Chapter 6. Alignments

or a method via a standard RC (described below).

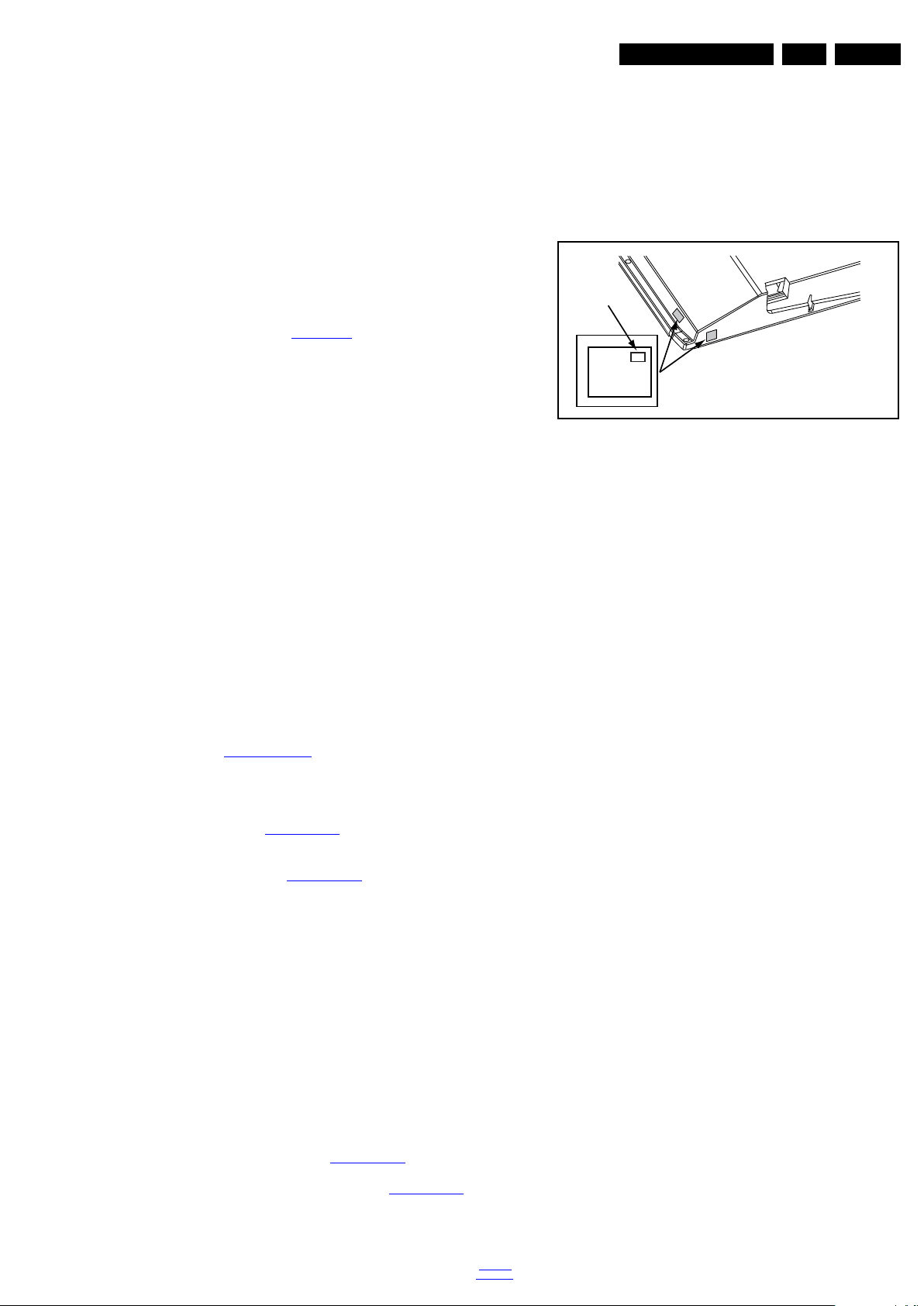

Changing the display option via a standard RC: Key in the

code “062598” directly followed by the “MENU” (or "HOME")

”).

button and “XXX” (where XXX is the 3 digit decimal display

code as mentioned on the sticker in the set). Make sure to key

in all three digits, also the leading zero’s. If the above action is

successful, the front LED will go out as an indication that the

RC sequence was correct. After the display option is changed

in the NVM, the TV will go to the Stand-by mode. If the NVM

was corrupted or empty before this action, it will be initialized

first (loaded with default values). This initializing can take up to

20 seconds.

)

Figure 5-2 Location of Display Option Code sticker

• Store - go right. All options and alignments are stored

when pressing “cursor right” (or the “OK” button) and then

the “OK”-button.

• Operation hours display. Displays the accumulated total

of operation hours of the screen itself. In case of a display

replacement, reset to “0” or to the consumed operation

hours of the spare display.

• SW Maintenance.

– SW Events. In case of specific software problems, the

development department can ask for this info.

– HW Events. In case of specific software problems, the

development department can ask for this info :

- Event 26 : refers to a power dip, this is logged after

the TV set reboots due to a power dip.

- Event 17 : refers to the power OK status, sensed

even before the 3 x retry to generate the error code.

• Test settings. For development purposes only.

• Development file versions. Not useful for Service

purposes, this information is only used by the development

department.

• Upload to USB. To upload several settings from the TV to

.

an USB stick, which is connected to the SSB. The items are

“Channel list”, “Personal settings”, “Option codes”,

“Alignments”, “Identification data” (includes the set type

.

and prod code + all 12NC like SSB, display, boards),

“History list”. The “All” item supports to upload all several

items at once.

First a directory “repair\” has to be created in the root

of the USB stick.

To upload the settings, select each item separately, press

“cursor right” (or the “OK” button), confirm with “OK” and

wait until “Done” appears. In case the download to the USB

stick was not successful “Failure” will appear. In this case,

check if the USB stick is connected properly and if the

directory “repair” is present in the root of the USB stick.

Now the settings are stored onto the USB stick and can be

used to download into another TV or other SSB. Uploading

is of course only possible if the software is running and

preferably a picture is available. This method is created to

be able to save the customer’s TV settings and to store

them into another SSB.

• Download from USB. To download several settings from

for details.

)

the USB stick to the TV, same way of working needs to be

followed as with uploading. To make sure that the

download of the channel list from USB to the TV is

executed properly, it is necessary to restart the TV and

tune to a valid preset if necessary. The “All” item supports

to download all several itels at once.

back to

div. table

2010-Jun-25

Page 22

EN 22 Q552.1A LA5.

Service Modes, Error Codes, and Fault Finding

• NVM editor. For NET TV the set “type number” must be

entered correctly.

Also the production code (AG code) can be entered here

via the RC-transmitter.

Correct data can be found on the side/rear sticker.

How to Navigate

• In SAM, the menu items can be selected with the

“CURSOR UP/DOWN” key on the RC-transmitter. The

selected item will be highlighted. When not all menu items

fit on the screen, move the “CURSOR UP/DOWN” key to

display the next/previous menu items.

• With the “CURSOR LEFT/RIGHT” keys, it is possible to:

– (De) activate the selected menu item.

– (De) activate the selected sub menu.

• With the “OK” key, it is possible to activate the selected

action.

How to Exit SAM

Use one of the following methods:

• Switch the TV set to STAND-BY via the RC-transmitter.

• Via a standard RC-transmitter, key in “00” sequence, or

select the “BACK” key.

5.2.3 Customer Service Mode (CSM)

Purpose

When a customer is having problems with his TV-set, he can

call his dealer or the Customer Helpdesk. The service

technician can then ask the customer to activate the CSM, in

order to identify the status of the set. Now, the service

technician can judge the severity of the complaint. In many

cases, he can advise the customer how to solve the problem,

or he can decide if it is necessary to visit the customer.

The CSM is a read only mode; therefore, modifications in this

mode are not possible.

When in this chassis CSM is activated, a test pattern will be

displayed during 5 seconds (1 second Blue, 1 second Green

and 1 second Red, then again 1 second Blue and 1 second

Green). This test pattern is generated by the PNX51X0

(located on the 200Hz board as part of the display). So if this

test pattern is shown, it could be determined that the back end

video chain (PNX51X0 and display) is working.For TV sets

without the PNX51X0 inside, every menu from CSM will be

used as check for the back end chain video.

When CSM is activated and there is a USB stick connected to

the TV set, the software will dump the CSM content to the USB

stick. The file (CSM_model number_serial number.txt) will be

saved in the root of the USB stick. This info can be handy if no

information is displayed.

When in CSM mode (and a USB stick connected), pressing

“OK” will create an extended CSM dump file on the USB stick.

This file (Extended_CSM_model number_serial number.txt)

contains:

• The normal CSM dump information,

• All items (from SAM “load to USB”, but in readable format),

• Operating hours,

• Error codes,

• SW/HW event logs.

To have fast feedback from the field, a flashdump can be

requested by development. When in CSM, push the “red”

button and key in serial digits ‘2679’ (same keys to form the

word ‘COPY’ with a cellphone). A file “Dump_model

number_serial number.bin” will be written on the connected

USB device. This can take 1/2 minute, depending on the

quantity of data that needs to be dumped.

Also when CSM is activated, the LAYER 1 error is displayed via

blinking LED. Only the latest error is displayed (see also

section 5.5 Error Codes

).

How to Activate CSM

Key in the code “123654” via the standard RC transmitter.

Note: Activation of the CSM is only possible if there is no (user)

menu on the screen!

How to Navigate

By means of the “CURSOR-DOWN/UP” knob on the RCtransmitter, can be navigated through the menus.

Contents of CSM

The contents are reduced to 3 pages: General, Software

versions and Quality items. The group names itself are not

shown anywhere in the CSM menu.

General

• Set Type. This information is very helpful for a helpdesk/

workshop as reference for further diagnosis. In this way, it

is not necessary for the customer to look at the rear of the

TV-set. Note that if an NVM is replaced or is initialized after

corruption, this set type has to be re-written to NVM.

ComPair will foresee in a possibility to do this. The update

can also be done via the NVM editor available in SAM.

• Production Code. Displays the production code (the serial

number) of the TV. Note that if an NVM is replaced or is

initialized after corruption, this production code has to be

re-written to NVM. ComPair will foresee in a possibility to

do this. The update can also be done via the NVM editor

available in SAM.

• Installed date. Indicates the date of the first installation of

the TV. This date is acquired via time extraction.

• Options 1. Gives the option codes of option group 1 as set

in SAM (Service Alignment Mode).

• Options 2. Gives the option codes of option group 2 as set

in SAM (Service Alignment Mode).

• 12NC SSB. Gives an identification of the SSB as stored in

NVM. Note that if an NVM is replaced or is initialized after

corruption, this identification number has to be re-written to

NVM. ComPair will foresee in a possibility to do this. This

identification number is the 12nc number of the SSB.

• 12NC display. Shows the 12NC of the display.

• 12NC supply. Shows the 12NC of the power supply.

• 12NC 200Hz board. Shows the 12NC of the 200Hz Panel

(when present).

Software versions

• Current main SW. Displays the build-in main software

version. In case of field problems related to software,

software can be upgraded. As this software is consumer

upgradeable, it will also be published on the Internet.

Example: Q55xx1.2.3.4

• Stand-by SW. Displays the build-in stand-by processor

software version. Upgrading this software will be possible

via ComPair or via USB (see section 5.9 Software

Upgrading).

Example: STDBY_88.68.1.2.

• e-UM version. Displays the electronic user manual SWversion (12NC version number). Most significant number

here is the last digit.

Quality items

• Signal quality. Bad / average /good (not for DVB-S).

• Ethernet MAC address. Displays the MAC address

present in the SSB.

• Wireless MAC address. Displays the wireless MAC

address to support the Wi-Fi functionality.

• BDS key. Indicates if the set is in the BDS status.

• CI module. Displays status if the common interface

module is detected.

• CI + protected service. Yes/No.

• Event counter :

S : 000X 0000(number of software recoveries : SW

EVENT-LOG #(reboots)

2010-Jun-25

back to

div. table

Page 23

Service Modes, Error Codes, and Fault Finding

18770_250_100216.eps

100402

Active

Semi

St by

St by

Mains

on

Mains

off

GoToProtection

-WakeUp requested

-Acquisition needed

-Tact switch pushed

- stby requested and

no data Acquisition

required

- St by requested

-tact SW pushed

WakeUp

requested

Protection

WakeUp

requested

(SDM)

GoToProtection

Hibernate

-Tact switch pushed

-last status is hibernate

after mains ON

Tact switch

pushed

EN 23Q552.1A LA 5.

S : 0000 000X (number of software events : SW EVENTLOG #(events)

H : 000X 0000(number of hardware errors)

H : 0000 000X (number of hardware events : SW EVENTLOG #(events).

How to Exit CSM

Press “MENU” (or "HOME") / “Back” key on the RC-transmitter.

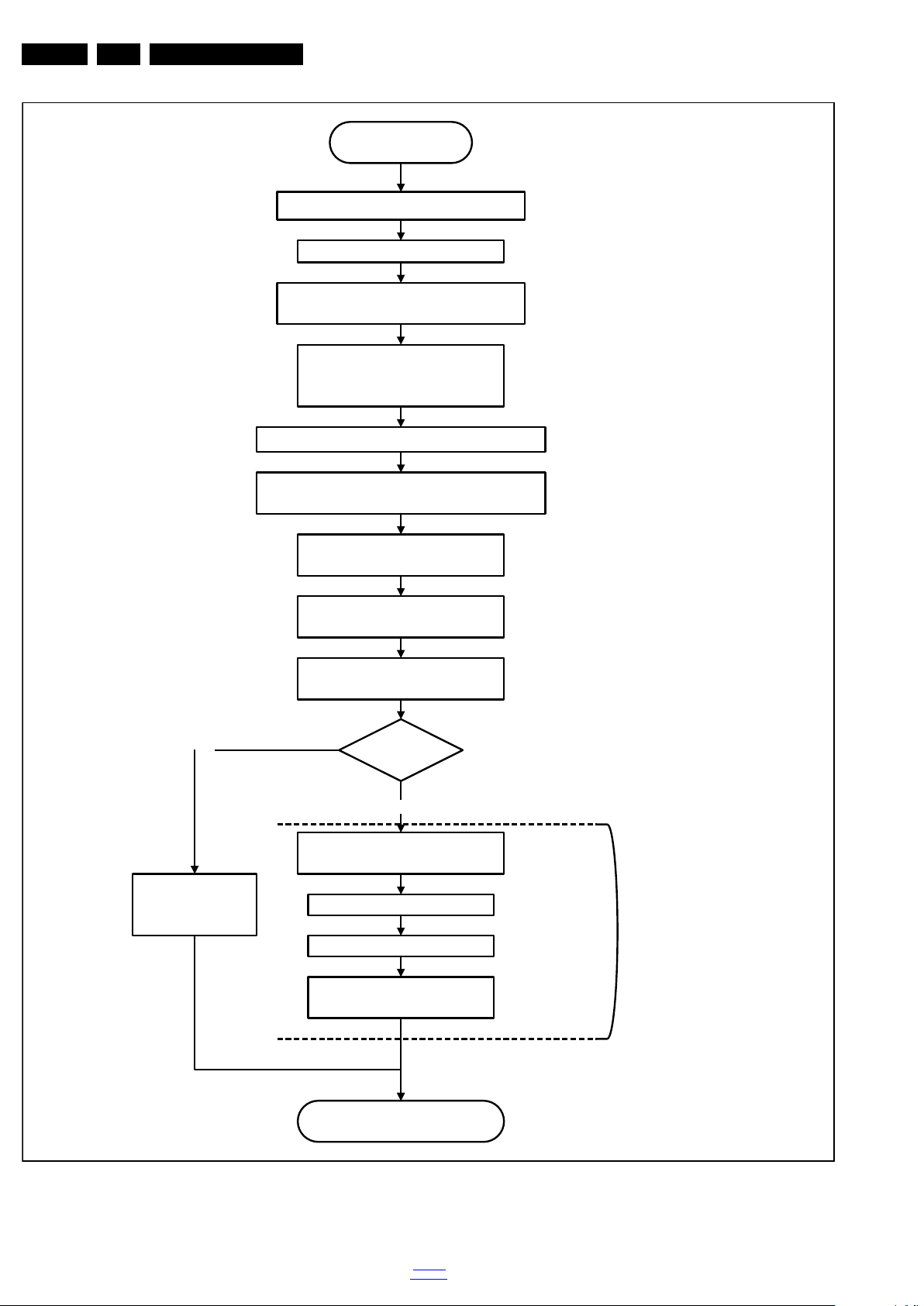

5.3 Stepwise Start-up

When the TV is in a protection state due to an error detected by

stand-by software (error blinking is displayed) and SDM is

activated via shortcutting the SDM solder path on the SSB, the

TV starts up until it reaches the situation just before protection.

So, this is a kind of automatic stepwise start-up. In combination

with the start-up diagrams below, you can see which supplies

are present at a certain moment. Caution: in case the start-up

in this mode with a faulty FET 7U0X is done, you can destroy

all IC’s supplied by the +1V8 and +1v1, due to overvoltage (12V

on XVX-line). It is recommended to measure first the FET

7U0X or others FET’s on shortcircuit before activating SDM via

the service pads.

The abbreviations “SP” and “MP” in the figures stand for:

• SP: protection or error detected by the Stand-by

Processor.

• MP: protection or error detected by the MIPS Main

Processor.

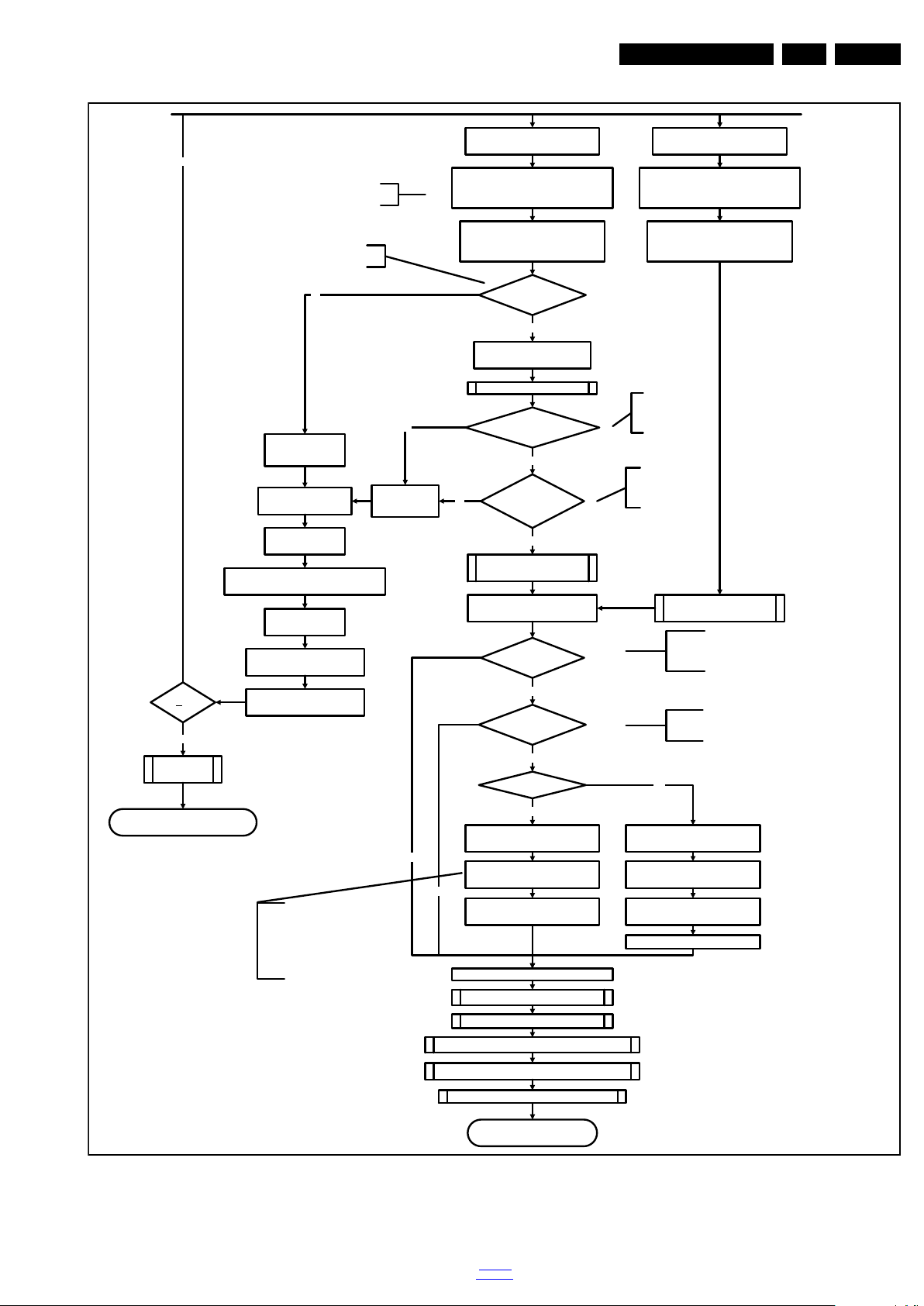

Figure 5-3 Transition diagram

back to

div. table

2010-Jun-25

Page 24

EN 24 Q552.1A LA5.

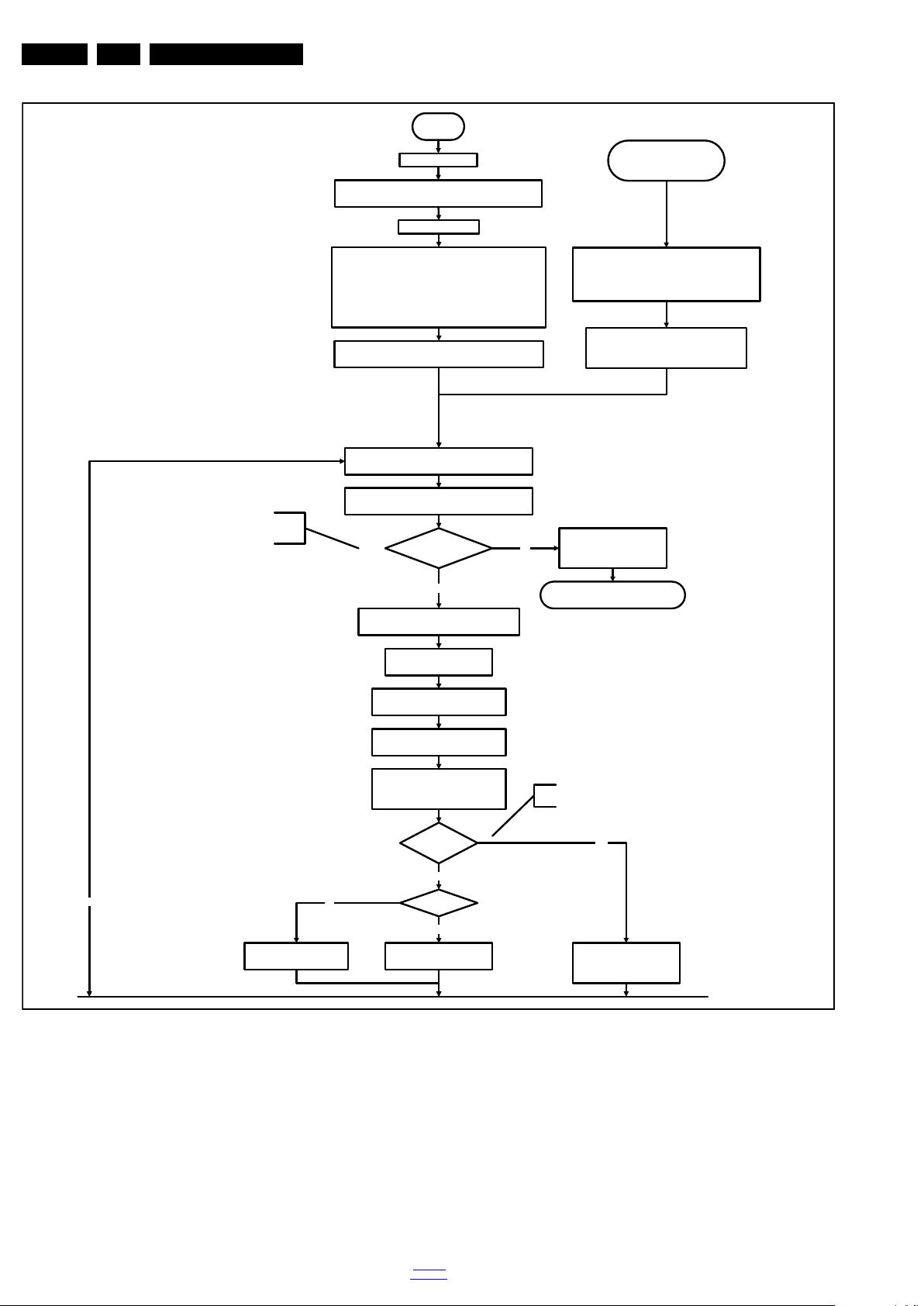

18770_251_100216.eps

100216

No

EJTAG probe

connected ?

No

Yes

Release AVC system reset

Feed warm boot script

Cold boot?

Yes

No

Set I²C slave address

of Standby µP to (A0h)

An EJTAG probe (e.g . WindPower ICE prob e) can be

connected for Linux Kernel debugging purposes.

Detect EJTAG debug probe

(pulling pin of the probe interface to

ground by inserting EJTAG probe)

Release AVC system reset

Feed cold boot script

Release AVC system reset

Feed initializing boot script

disable alive mechanism

Off

Standby Supply starts running.

All standby supply voltages become available.

st-by µP resets

Stand by or

Protection

Mains is applied

- Switch Audio-Reset high.

It is low in the standby mode if the standby

mode lasted longer than 10s.

start keyboard scanning, RC detection. Wake up reasons are

off.

If the protection state was left by short c ircuiting the

SDM pins, detection of a protection condition during

startup will stall the startup. Protection conditions in a

playing set will be ignored. The protection mode will

not be entered.

Detect2 is moved to an interrupt. To be checked if

the detection on interrupt base is feasible or not or if

we should stick to the standard 40ms interval.

+12V, +24Vs, AL and Bolt-on power

isswitched on, followed by the +1V2 DCDC convert er

Enable the supply detection algorithm

Switch ON Platform and display supply by switching

LOW the Standby line.

Initialise I/O pins of the st-by µP:

- Switch reset-AVC LOW (reset state)

- Switch reset-system LOW (reset state)

- Switch reset-Ethernet LOW (reset state)

- Switch reset-USB LOW (reset state)

- Switch reset-DVBs LOW (reset state)

-keep Audio-reset and Audio-Mute-Up HIGH

Enable the DCDC converters

(ENABLE-3V3n LOW)

No

Detect2 high received

within 2 seconds?

12V error :

Layer1: 3

Layer2: 16

Enter protection

Yes

Wait 50ms

Service Modes, Error Codes, and Fault Finding

2010-Jun-25

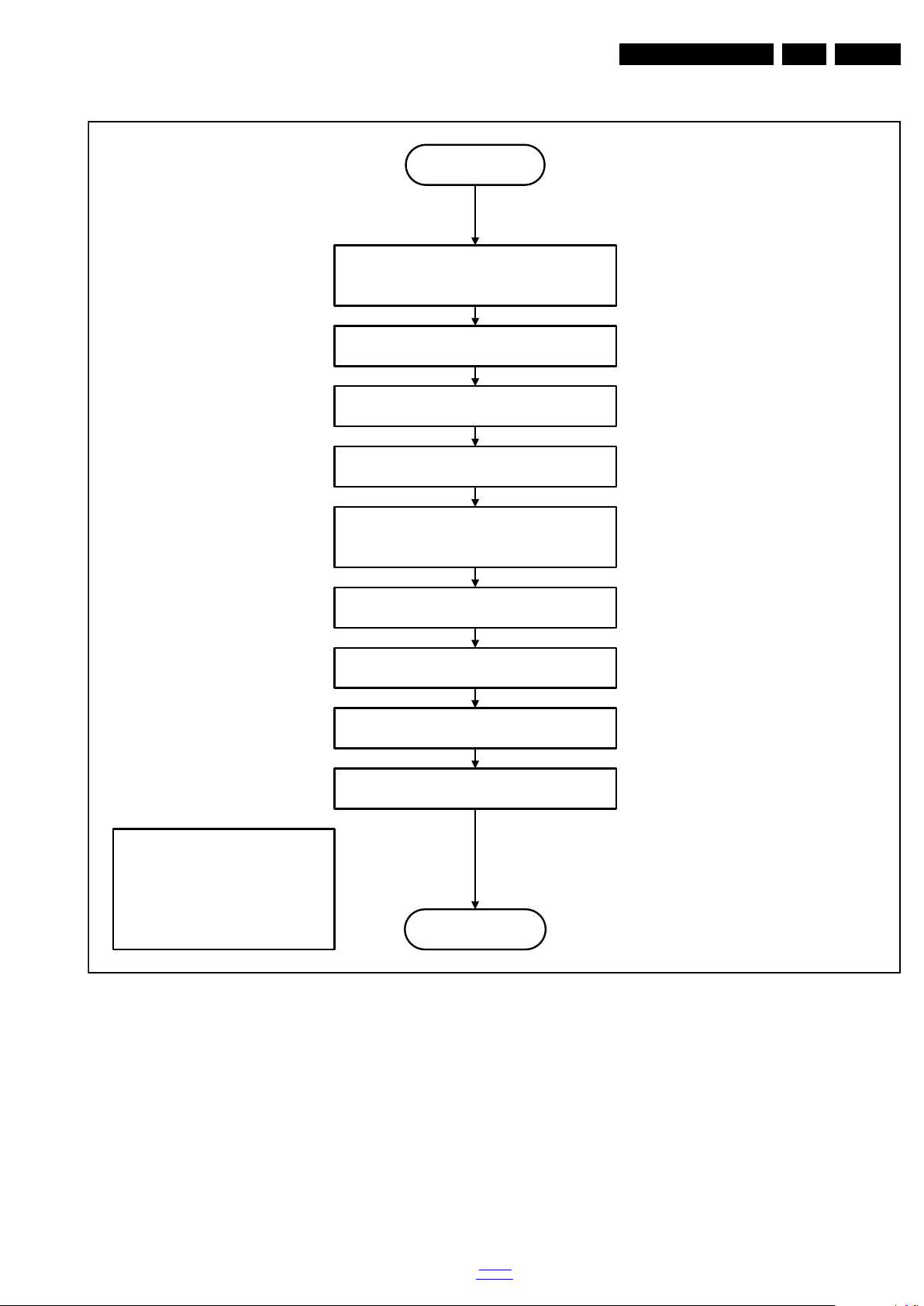

Figure 5-4 “Off” to “Semi Stand-by” flowchart (part 1)

back to

div. table

Page 25

Service Modes, Error Codes, and Fault Finding

18770_252_100216.eps

100216

Yes

MIPS reads the wake up reason

from standby µP.

Semi-Standby

initialize tuner and channel decoders

Initialize video processing IC’s

Initialize source selection

initialize AutoTV by triggering CHS AutoTV Init interface

3-th try?

No

Blink Code as

error code

Bootscript ready

in 1250 ms?

Yes

No

Enable Alive check mechanism

Wait until AVC starts to

communicate

SW initialization

succeeded

within 20s?

No

Switch StandbyI/O line high

and wait 4 seconds

RPC start (comm. protocol)

Set I²C slave address

of Standby µP to (60h)

Yes

Disable all supply related protections and

switch off the +3V3 +5V DC/DC converter.

switch off the remaining DC/DC

converters

Wait 5ms

Switch AVC PNX85500 in

reset (active low)

Wait 10ms

Flash to Ram

image transfer succeeded

within 30s?

No

Yes

Code =

Layer1: 2

Layer2: 53

Code =

Layer1: 2

Layer2: 15

Initialize Ambilight with Lights off.

Timing need to be updated if

more mature info is available.

Timing needs to

be updated if more

mature info is

available.

Timing needs to be

updated if more

mature info is

available.

Initialize audio

Enter protection

Reset-system is switched HIGH by the

AVC at the end of t he bootscript

AVC releases Reset-Ether net, Reset-USB and

Reset-DVBs when the end of the AVC boot-

script is detected

This cannot be done through the bootscript,

the I/O is on the standby µP

Reset-Audio and Audio-Mute-Up are

switched by MIPS code later on in the

startup process

Reset-system is switched HIGH by the

AVC at the end of the bootscript

Reset-Audio and Audio-Mute-Up a re

switched by MIPS code later on in the

startup process

Wake up reason

coldboot & not semi-

standby?

85500 sends out startup screen

Startup screen cfg file

present?

85500 starts up the display.

Startup screen visible

yes

yes

To keep this flowchart readable, the exact

display turn on description is not copied

here. Please see the Semi-standby to On

description for the detailed display startup

sequence.

During the complete display time of the

Startup screen, the preheat condition of

100% PWM is valid.

No

No

Startup screen shall only be visible when there is a coldboot to

an active state end situation. The startup screen shall not be

visible when waking up for reboot reasons or waking up to semi-

standby conditions or waking up to enter Hibernate mode..

The first time after the option turn on of the startup screen or

when the set is virgin, the cfg file is not present and hence

the startup screen will not be shown.

AVC releases Reset-Ethernet, Reset-USB and

Reset-DVBs when the end of the AVC boot-

script is detected

200Hz set?

No

yes

85500 sends out startup screen

200Hz Tcon has started up the

display.

Startup screen visible

85500 requests Lamp on

EN 25Q552.1A LA 5.

Figure 5-5 “Off” to “Semi Stand-by” flowchart (part 2)

back to

div. table

2010-Jun-25

Page 26

EN 26 Q552.1A LA5.

18770_253_100216.eps

100216

Active

Semi Standby

Initialize audio and video

processing IC's and functions

according needed use case.

Assert RGB video blanking

and audio mute

Wait until previous on-state is left more than2

secondsago. (to prevent LCD display problems)

The assumption here is that a fast toggle (<2s) can

only happen during ON->SEMI ->ON. In these states,

the AVC is still active and can provide the 2s delay. A

transition ON->SEMI->STBY->SEMI->ON cannot be

made in less than 2s, because the standby state will

be maintained for at least 4s.

Switch Audio-Reset low and wait 5ms

Constraints taken into account:

-Display may only be started when valid LVDS output clock can be delivered by the AVC.

-To have a reliable operation of the EEFL backlight, the backlight should be driven with a maximum PWM duty

cycle during the first seconds. Only after this first one or two seconds, the PWM may be set to the required output

level (Note that the PWM output should be present b

efore the backlight is switched on). To minimize the artefacts,

the picture should only be unblanked after these first seconds.

Restore dimming backlight feature, PWM and BOOST output

and unblank the video.

Wait until valid and stable audio and video, corresponding to the

requested output is delivered by the AVC

AND

the backlight has been switched on for at least the time which is

indicated in the display file as preheat time.

The higher level requirement is that audio and video

should be demuted without transient effects and that

the audio should be demuted maximum 1s before or

at the same time as the unblanking of the video.

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

CPipe already generates a valid output

clock in the semi-standby state: display

startup can start immediately when leaving

the semi-standby state.

Switch on LCD backlight (Lamp-ON)

Switch off the dimming backlight feature, set

the BOOST control to nominal and make sure

PWM output is set to maximum allowed PWM

Switch on the Ambilight functionality according the last status

settings.

Delay Lamp-on with the sum of the LVDS delay and

the Lamp delay indicated in the display file

Switch on the displaypowerby

switching LCD-PWR-ON low

Wait x ms

Switch on LVDS output in the 85500

No

The exact timings to

switch on the

display(LVDS

delay, lamp delay)

are defined in the

display file.

Start POK line

detection algorithm

return

Display already on?

(splash screen)

Yes

Display cfg file present

and up to date, according

correct display option?

Startup screen Option

and Installation setting

Photoscreen ON?

Yes

No

Prepare Start screen Display config

file and copy to Flash

No

Yes

A LED set does not normally need a

preheat time. The preheat remains present

but is set to zero in the display file.

Service Modes, Error Codes, and Fault Finding

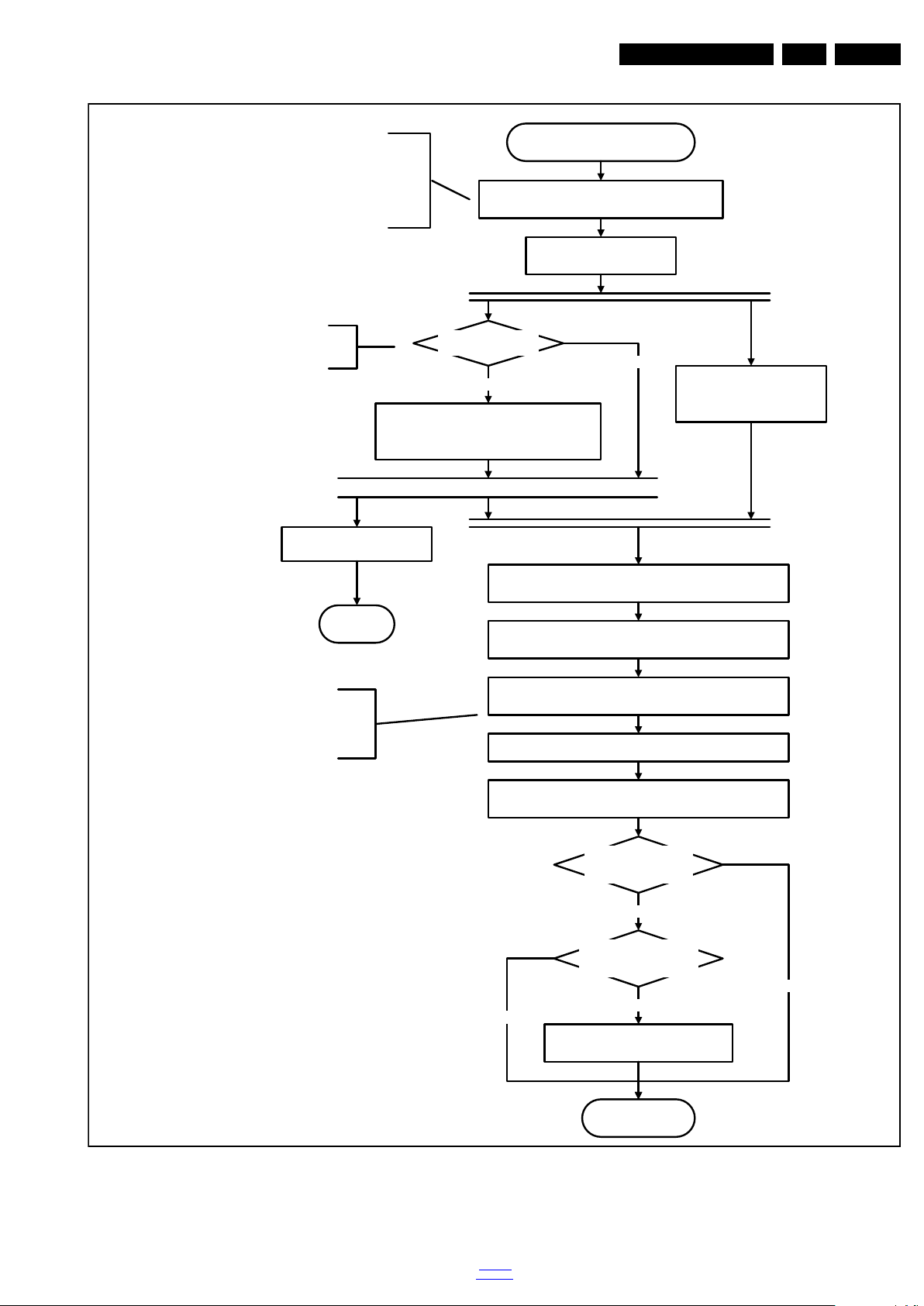

Figure 5-6 “Semi Stand-by” to “Active” flowchart (EEFL or LED backlight 50/100 Hz only)

2010-Jun-25

back to

div. table

Page 27

Service Modes, Error Codes, and Fault Finding

18770_254_100216.eps

100216

Active

Semi Standby

Initialize audio and video

processing IC's and functions

according needed use case.

Assert RGB video blanking

and audio mute

Wait until previous on-state is left more than2

secondsago. (to prevent LCD display problems)

The assumption here is that a fast toggle (<2s)

can only happen during ON->SEMI ->ON. In

these states, the AVC is still active and can

provide the 2s delay. If the transition ON->SEMI-

>STBY->SEMI->ON can be made in less than 2s,

we have to delay the semi -> stby transition until

the requirement is met.

Switch Audio-Reset low and wait 5ms

unblank the video.

Wait until valid and stable audio and video, corresponding to

the requested output is delivered by the AVC.

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

unblanking of the video.

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

Request Tcon to Switch on the backlight in a

direct LED or

set Lamp-on I/O line in case of a side LED

Switch on the Ambilight functionality according the last status

settings.

There is no need to define the

display timings since the timing

implementation is part of the Tcon.

Start POK line

detection algorithm

return

Display cfg file present

and up to date, according

correct display option?

Startup screen Option

and Installation setting

Photoscreen ON?

Yes

No

Prepare Start screen Display config

file and copy to Flash

No

Yes

Backlight already on?

(splash screen)

No

Yes

EN 27Q552.1A LA 5.

Figure 5-7 “Semi Stand-by” to “Active” flowchart (LED backlight 200 Hz)

back to

div. table

2010-Jun-25

Page 28

EN 28 Q552.1A LA5.

18770_255_100216.eps

100216

Semi Standby

Active

Wait x ms (display file)

Mute all sound outputs via softmute

Mute all video outputs

switch off LCD backlight

(I/O or I²C)

Force ext audio outputs to ground

(I/O: audio reset)

And wait 5ms

switch off Ambilight

Set main amplifier mute (I/O: audio-mute)

Wait 100ms

Wait until Ambilight has faded out: Output power

Observer should be zero

Switch off the displaypowerby

switching LCD-PWR-ON high

Wait x ms

Switch off LVDS output in 85500

The exact timings to

switch off the

display(LVDS

delay, lamp delay)

are defined in the

display file.

Switch off POK line

detection algorithm

200Hz set?

No

Yes

Instruct 200Hz

Tcon to turn off

the display

Service Modes, Error Codes, and Fault Finding

2010-Jun-25

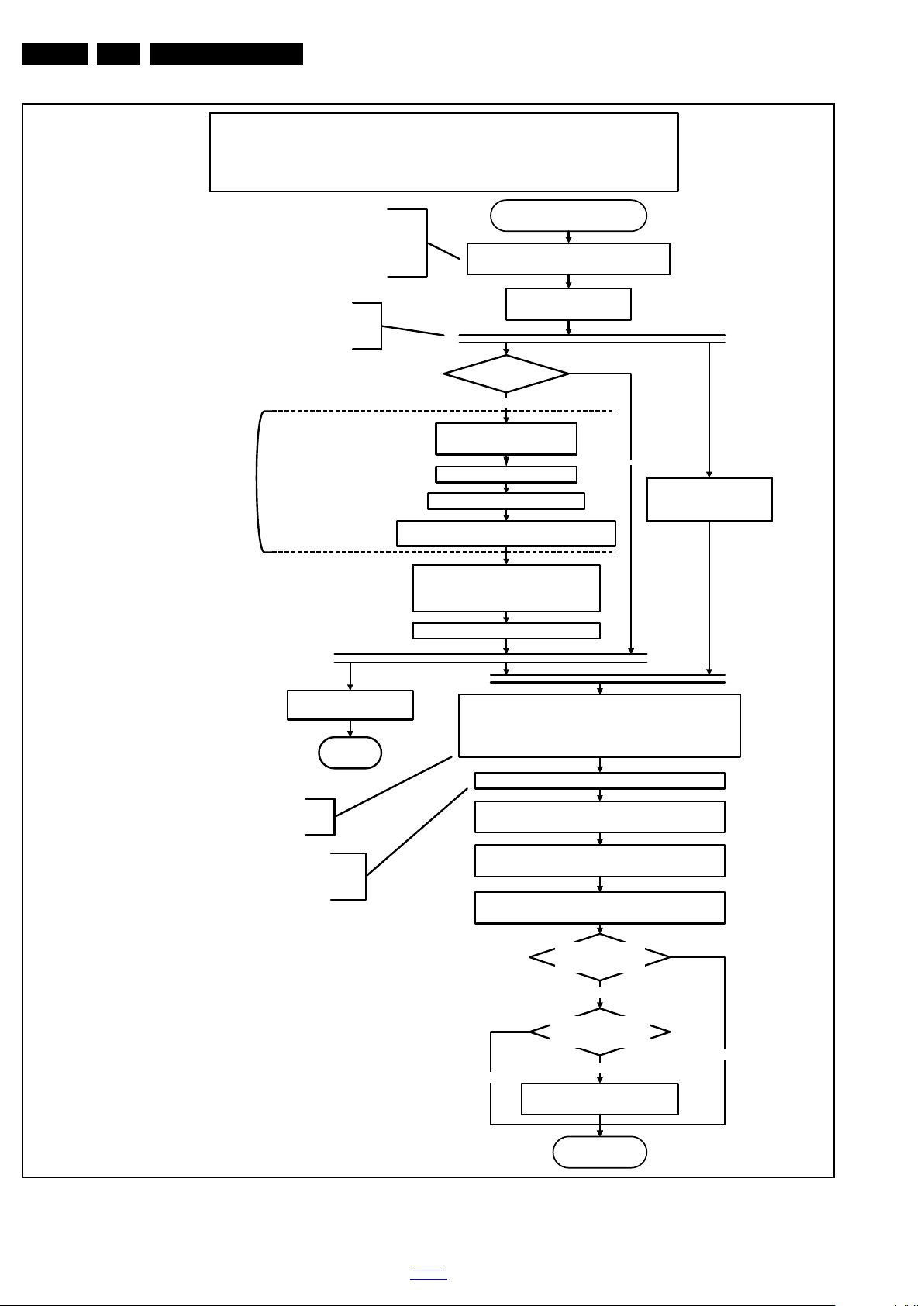

Figure 5-8 “Active” to “Semi Stand-by” flowchart

back to

div. table

Page 29

Service Modes, Error Codes, and Fault Finding

18770_256_100216.eps

100216

transfer Wake up reasons to the Stand by µP.

Stand by

Semi Stand by

Disable all supply related protections and switch off

the DC/DC converters (ENABLE-3V3n)

Switch OFF all supplies by switching HIGH the

Standby I/O line

Switch AVC system in reset state (reset-system and

reset-AVC lines)

Switch reset-USB, Reset-Ethernet and Reset-DVBs

LOW

Important remarks:

release reset audio 10 sec after entering

standby to save power

Also here, the standby state has to be

maintained for at least 4s before starting

another state transition.

Wait 5ms

Wait 10ms

Delay transition until ramping down of ambient light is

finished. *)

If ambientlight functionality was used in semi-standby

(lampadaire mode), switch off ambient light (see CHS

ambilight)

*) If this is not performed and the set is