Philips PSMN057-200B Datasheet

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN057-200B

FEATURES SYMBOL QUICK REFERENCE DATA

• ’Trench’ technology

• Very low on-state resistance V

d

= 200 V

DSS

• Fast switching

• Low thermal resistance

g

s

ID = 39 A

R

DS(ON)

≤ 57 mΩ

GENERAL DESCRIPTION

SiliconMAX products use the latest Philips Trench technology to achieve the lowest possible on-state resistance in

each package at each voltage rating.

Applications:-

• d.c. to d.c. converters

• switched mode power supplies

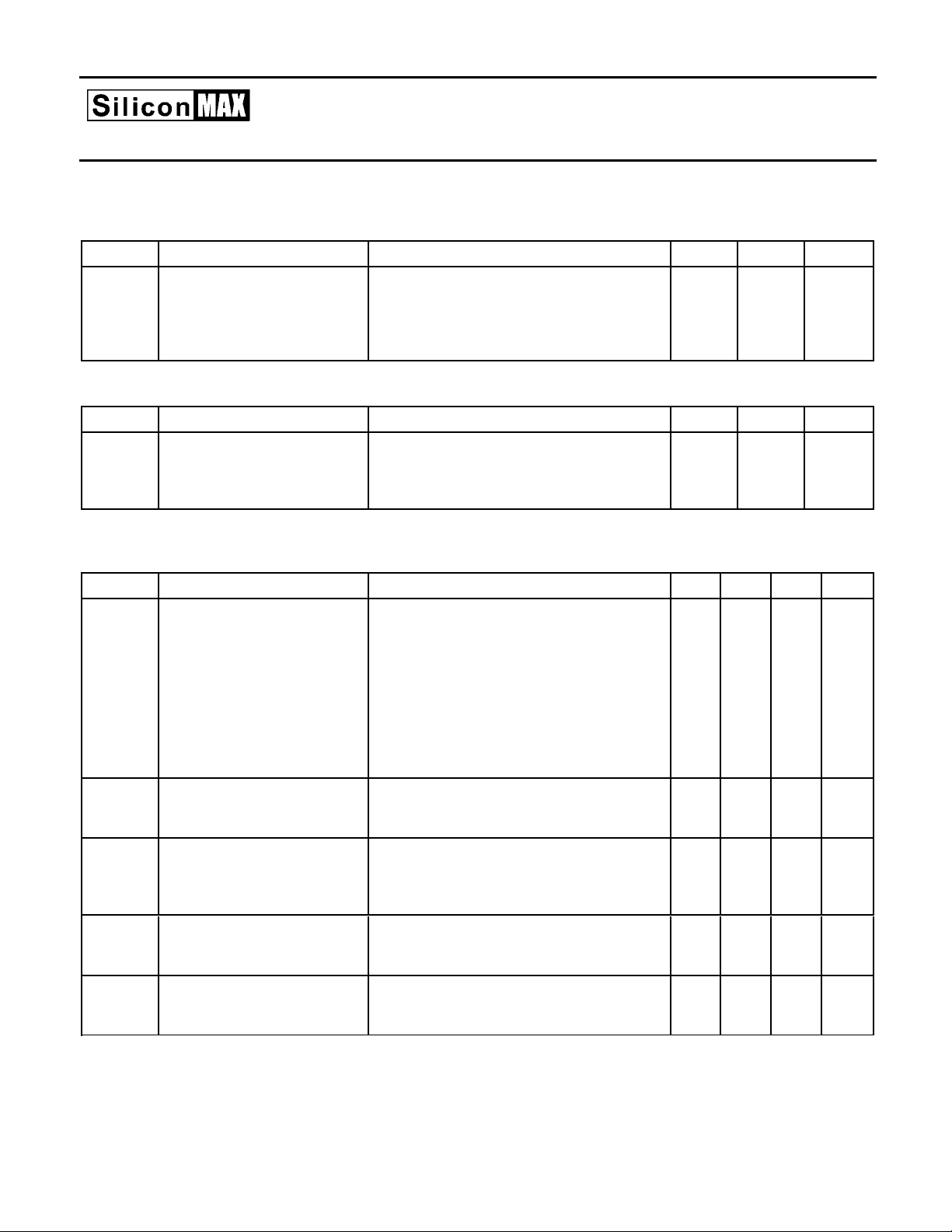

The PSMN057-200B is supplied in the SOT404 (D2PAK) surface mounted package.

PINNING - SOT404 PIN CONFIGURATION SYMBOL

PIN DESCRIPTION

1 gate

2 drain

(no connection possible)

3 source

mb drain

mb

g

2

13

d

s

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DSS

V

DGR

V

GS

I

D

I

DM

P

D

Tj, T

December 2000 1 Rev 1.000

Drain-source voltage Tj = 25 ˚C to 175˚C - 200 V

Drain-gate voltage Tj = 25 ˚C to 175˚C; RGS = 20 kΩ - 200 V

Gate-source voltage - ± 20 V

Continuous drain current Tmb = 25 ˚C - 39 A

Tmb = 100 ˚C - 27.5 A

Pulsed drain current Tmb = 25 ˚C - 156 A

Total power dissipation Tmb = 25 ˚C - 250 W

Operating junction and - 55 175 ˚C

stg

storage temperature

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN057-200B

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

E

AS

I

AS

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS TYP. MAX. UNIT

R

th j-mb

R

th j-a

Non-repetitive avalanche Unclamped inductive load, IAS = 35 A; - 300 mJ

energy tp = 100 µs; Tj prior to avalanche = 25˚C;

VDD ≤ 50 V; RGS = 50 Ω; VGS = 10 V;

Non-repetitive avalanche - 35 A

current

Thermal resistance junction - 0.6 K/W

to mounting base

Thermal resistance junction Minimum footprint, FR4 board 50 - K/W

to ambient

ELECTRICAL CHARACTERISTICS

Tj= 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(BR)DSS

V

GS(TO)

R

DS(ON)

I

GSS

I

DSS

Q

g(tot)

Q

gs

Q

gd

t

d on

t

r

t

d off

t

f

L

d

L

s

C

iss

C

oss

C

rss

Drain-source breakdown VGS = 0 V; ID = 0.25 mA; 200 - - V

voltage Tj = -55˚C 178 - - V

Gate threshold voltage VDS = VGS; ID = 1 mA 2.0 3.0 4.0 V

Tj = 175˚C 1.0 - - V

Tj = -55˚C - - 6 V

Drain-source on-state VGS = 10 V; ID = 17 A - 41 57 mΩ

resistance Tj = 175˚C - - 165 mΩ

Gate source leakage current VGS = ±10 V; VDS = 0 V - 2 100 nA

Zero gate voltage drain VDS = 200 V; VGS = 0 V; - 0.03 10 µA

current Tj = 175˚C - - 500 µA

Total gate charge ID = 39 A; V

= 160 V; VGS = 10 V - 96 - nC

DD

Gate-source charge - 13 - nC

Gate-drain (Miller) charge - 37 50 nC

Turn-on delay time VDD = 100 V; RD = 2.7 Ω; - 18 - ns

Turn-on rise time VGS = 10 V; RG = 5.6 Ω -58-ns

Turn-off delay time Resistive load - 105 - ns

Turn-off fall time - 78 - ns

Internal drain inductance Measured from tab to centre of die - 3.5 - nH

Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 3750 - pF

Output capacitance - 385 - pF

Feedback capacitance - 180 - pF

December 2000 2 Rev 1.000

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN057-200B

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

I

S

I

SM

V

SD

t

rr

Q

rr

Continuous source current - - 39 A

(body diode)

Pulsed source current (body - - 156 A

diode)

Diode forward voltage IF = 25 A; VGS = 0 V - 0.85 1.2 V

Reverse recovery time IF = 20 A; -dIF/dt = 100 A/µs; - 133 - ns

Reverse recovery charge VGS = 0 V; VR = 30 V - 895 - nC

December 2000 3 Rev 1.000

Loading...

Loading...