Page 1

PNX2000

Audio video input processor

Rev. 01 – 04 May 2004 Preliminary data

1. General description

2. Features

The PNX2000 is a companion IC for use with the Nexperia™

entertainment engines such as PNX8526 and PNX8550.

The PNX2000 is always used in combination with the PNX3000.

PNX2000 is intended for mid to high-end analog and h ybrid TV sets , performing input

decoding of single stream analog audio and single stream analog video signals. In

addition, the PNX2000 is used for decoding and presentation of all audio output

streams in the system.

■ Detection of PAL, NTSC or SECAM, and various 1fH and 2fH component video

input sources.

■ Full support for 1fH and 2fH video sources; progressive and interlaced.

■ Decoding for global VBI Standards (WST, WSS, VPS, CC, VITC).

■ ITU-656 output interface.

■ Global multi-standard audio demodulation and decoding.

■ Dolby Pro Logic II™ 2 multi-channel audio decoding and post-processing.

■ Advanced fully programmable audio post-processing functions, including

psychoacoustic spatial algorithms for optimal loudspeaker matching.

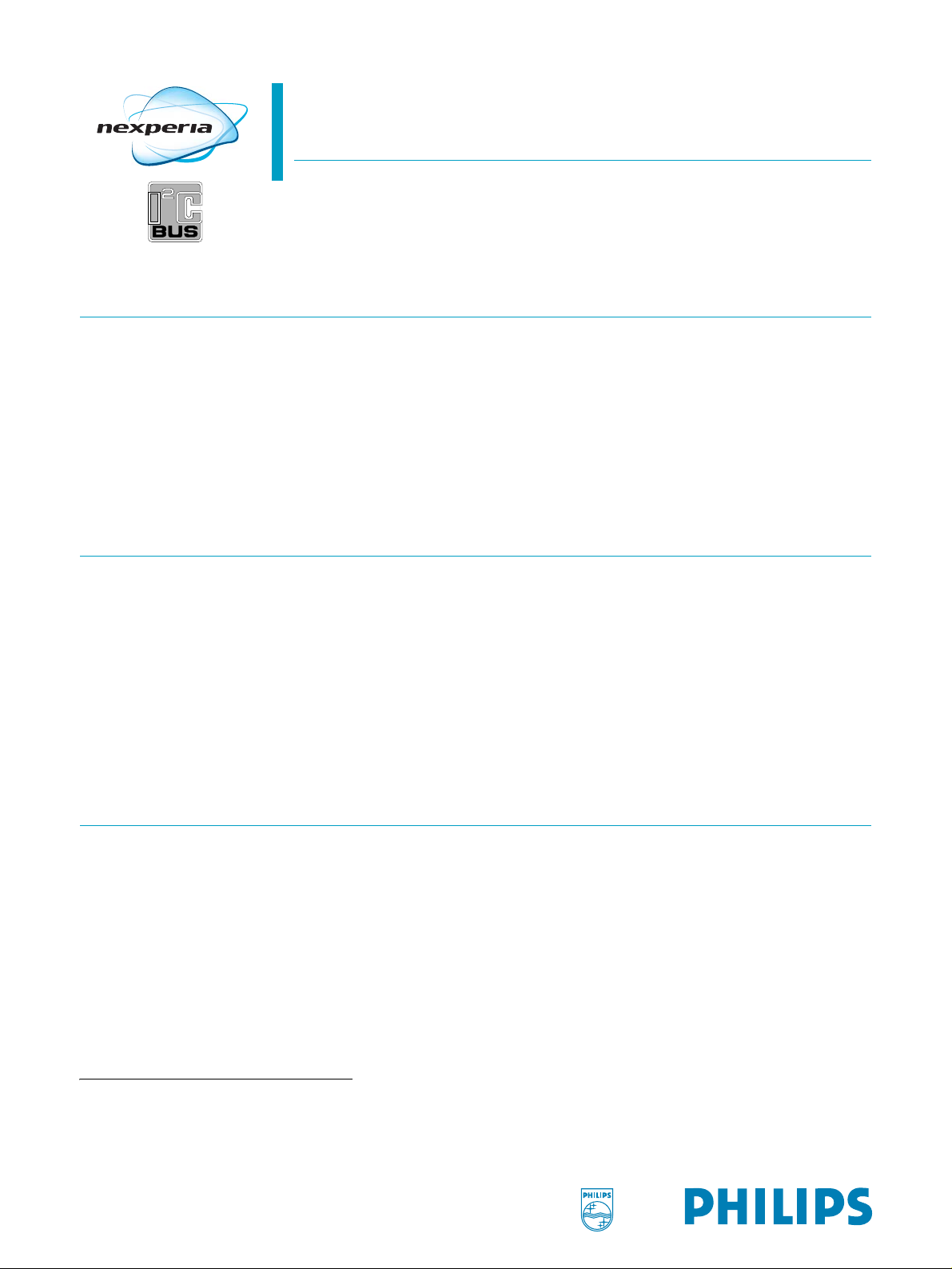

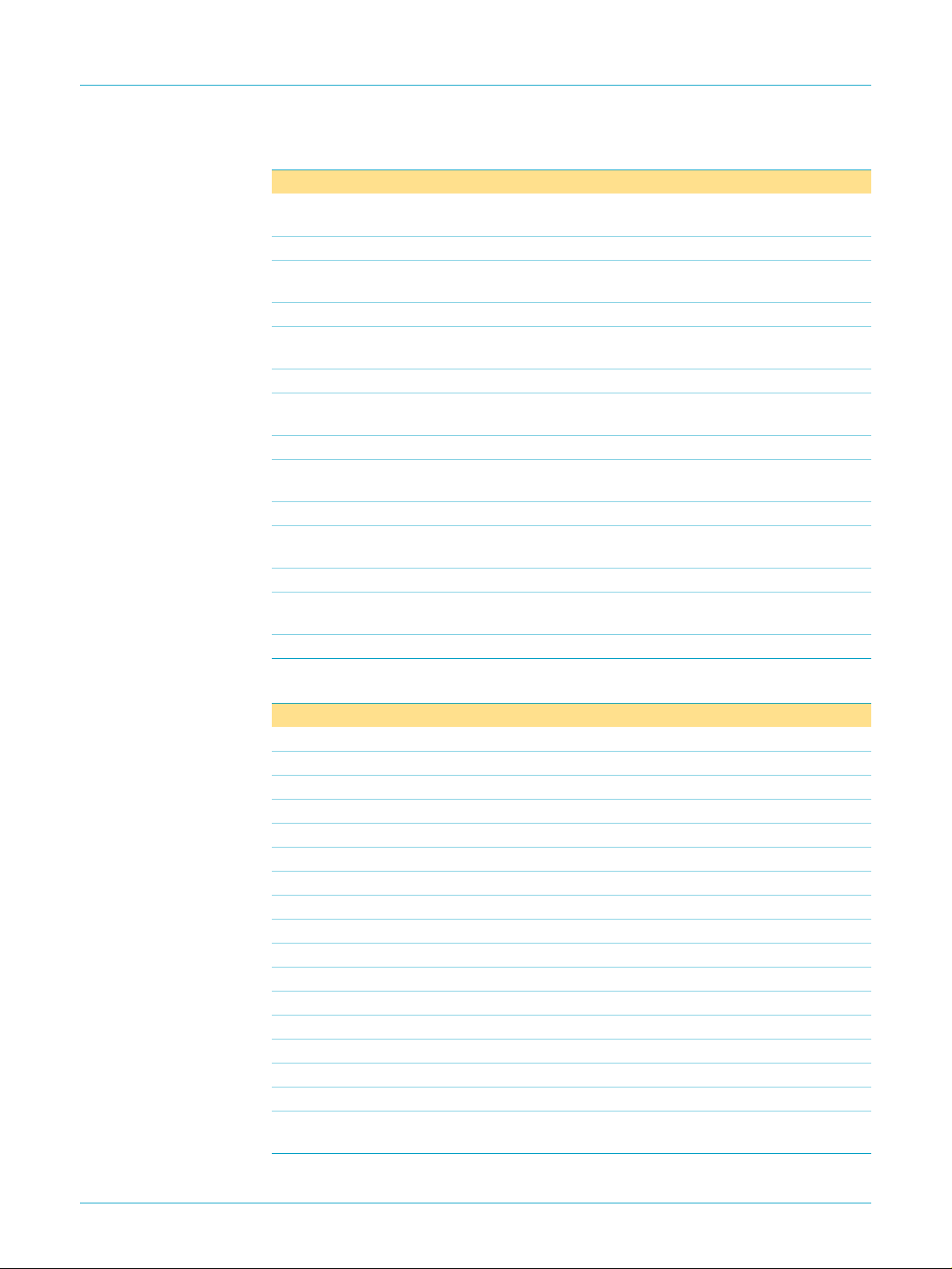

Figure 1 shows a block diagram of the device.

1

digital video home

3. Applications

■ Analog TV receivers.

■ Hybrid TV receivers.

■ DVD recorders.

■ VCRs.

1. Nexperia is a trademark of Koninklijke Philips Electronics N.V.

2. Dolby is a trademark of Dolby Laboratories

Page 2

Philips Semiconductors

PNX2000

Audio video input processor

4. Ordering information

Table 1: Ordering information

Type numb er Package

Description Version

name

PNX2000HL LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

5. Block diagram

DLINK2

DLINK1 DLINK3

2

I

C-bus

INT

13.5 MHz or

27 MHz

Xtal

2

6× I

S-bus

outputs

2

6× I

S-bus

inputs

PNX2000

audio data SIF or L/R

I2C-BUS

GTU

CLOCKS

DEMDEC DSP

AUDIO DSP

×4

PNX3000

interface

(2 stereo

or 4 mono)

video data CVBS, Y/C, YUV

54 MHz clock

I2D

×2×6

BCU

27 Msps or 54 Msps

PI-bus

VIDDEC

DCU

ITU-656

ITU-656

1f

or 2f

H

10-bit data

HSYNC

HSYNC/

VSYNC

mce559

H

Fig 1. Block diagram

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 2 of 26

Page 3

Philips Semiconductors

7

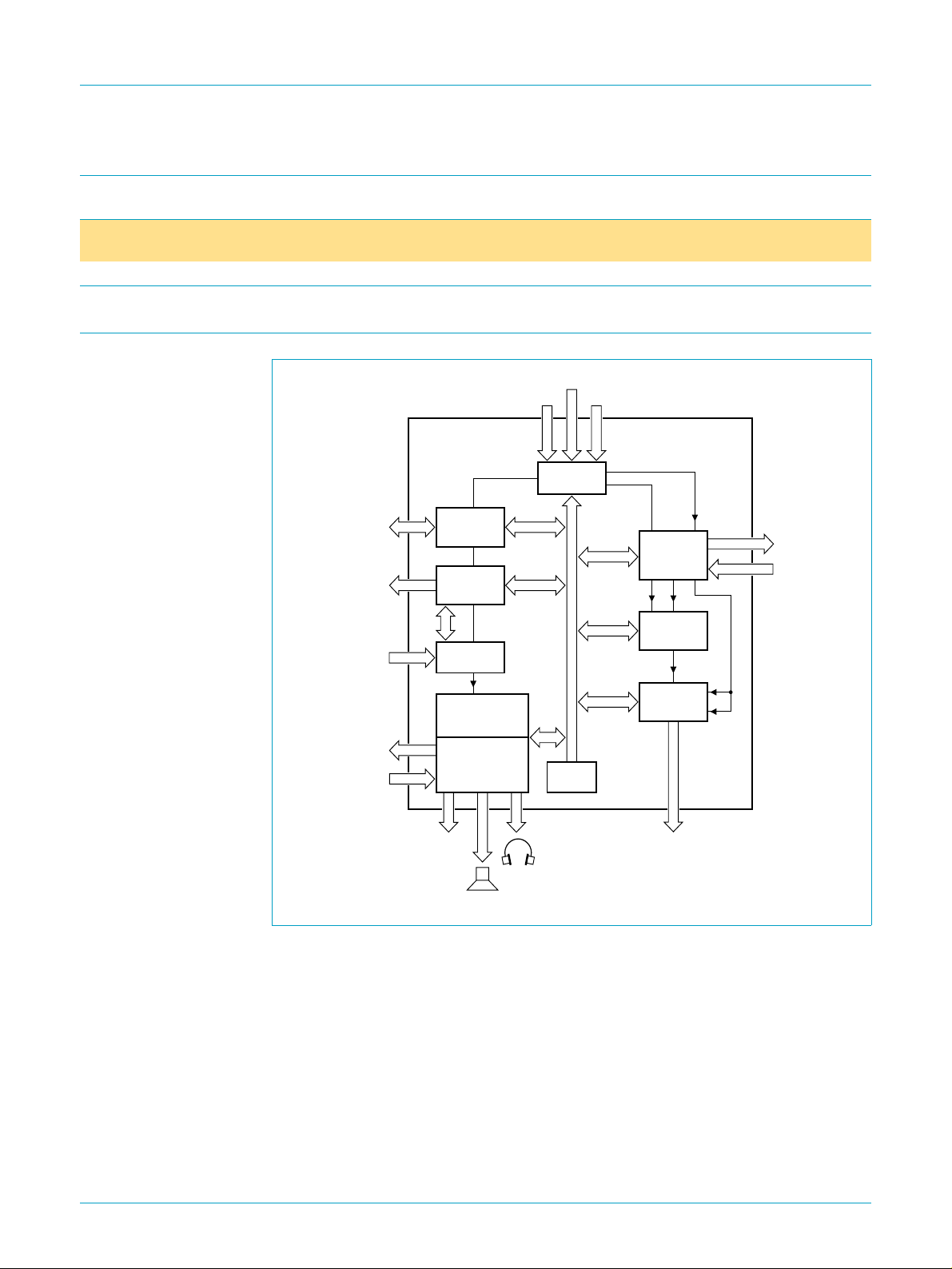

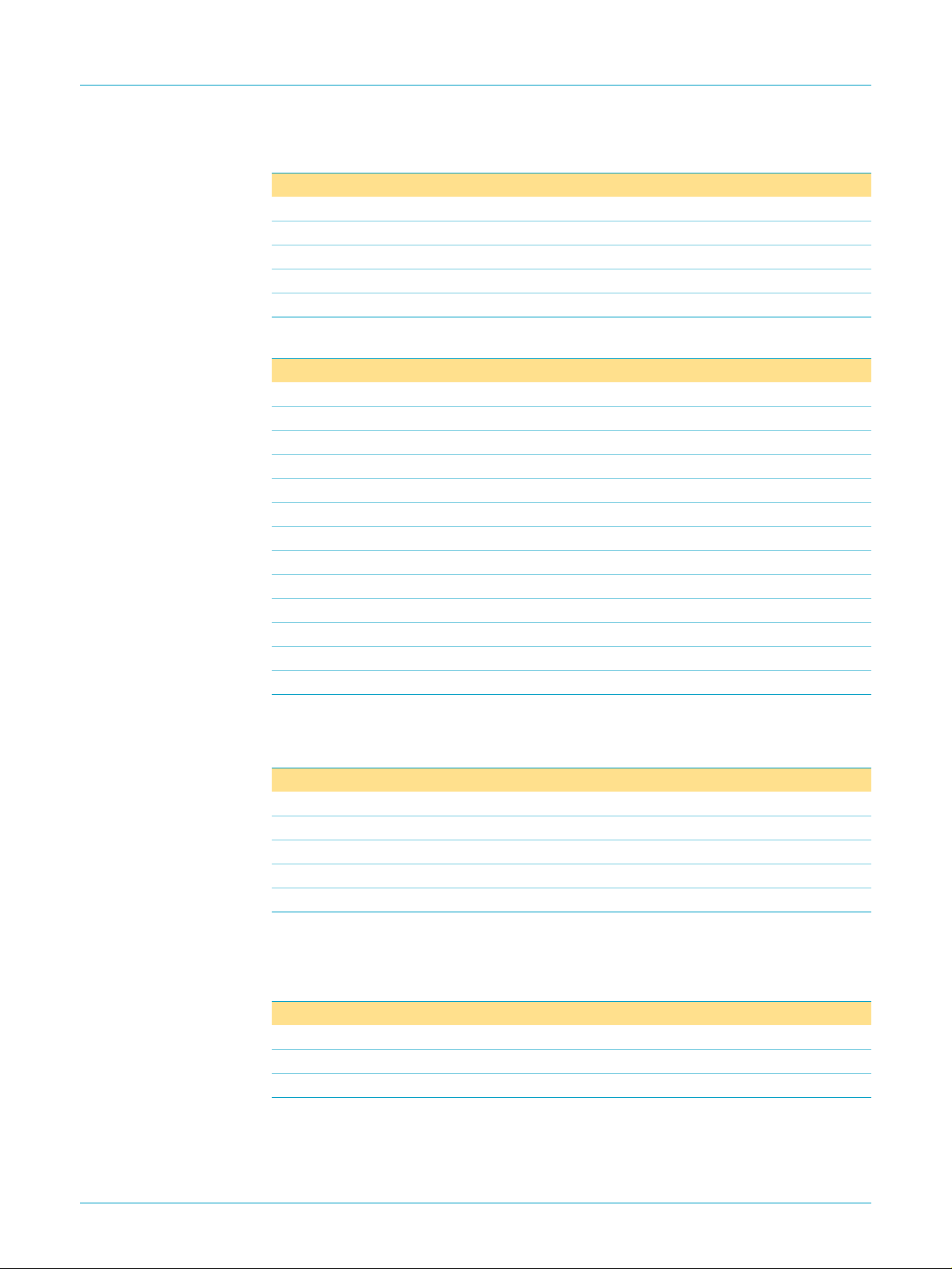

6. Pinning information

6.1 Pinning

PNX2000

Audio video input processor

Fig 2. Pin configuration

6.1.1 Pin description

Table 2 describes acronyms used in the pin tables:

Table 2: Acronym description

Acronym Description

3V 3.3 V LVCMOS

5VT 5 V tolerant inputs

Z 3-state

TTL TTL logic

TTL-H TTL with hysteresis

CMOS CMOS logic

IA Input Analog

ID Input Digital

OD Output Digital

OA Output Analog

IOA I/O Analog

IOD I/O Digital

GA Ground Analog

SA Supply Analog

SD Supply Digital

OSCIN Crystal Oscillator Input

OSCOUT Cr ystal Oscillator Output

OSCGND Crystal Oscillator Ground

144

1

PNX2000HL

36

37

109

72

108

73

001aaa28

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 3 of 26

Page 4

Philips Semiconductors

Table 3: I2D pins

Symbol Pin Type Description

DLINK1DP 2 IA analog differential data link 1 positive termination

DLINK1DN 3 IA analog differential data link 1 negative termination

DLINK1SP 4 IA analog differential strobe link 1 positive termination

DLINK1SN 5 IA analog differential strobe link 1 negative termination

DLINK2DP 7 IA analog differential data link 2 positive termination

DLINK2DN 8 IA analog differential data link 2 negative termination

DLINK2SP 9 IA analog differential strobe link 2 positive termination

DLINK2SN 10 IA analog differential strobe link 2 negative termination

DLINK3DP 12 IA analog differential data link 3 positive termination

DLINK3DN 13 IA analog differential data link 3 negative termination

DLINK3SP 14 IA analog differential strobe link 3 positive termination

DLINK3SN 15 IA analog differential strobe link 3 negative termination

Table 4: Audio pins

Symbol Pin Type Description

ADAC1 104 OA digital audio output 1

ADAC2 107 OA digital audio output 2

ADAC3 110 OA digital audio output 3

ADAC4 113 OA digital audio output 4

ADAC5 116 OA digital audio output 5

ADAC6 119 OA digital audio output 6

ADAC7 122 OA digital audio output 7

ADAC8 125 OA digital audio output 8

ADAC9 128 OA digital audio output 9

ADAC10 131 OA digital audio output 10

ADAC11 134 OA digital audio output 11

ADAC12 137 OA digital audio output 12

ADAC1_P 103 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC1_N 105 GA Negative analog reference star connected at PNX3000.

ADAC2_P 108 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC2_N 106 GA Negative analog reference star connected at PNX3000.

ADAC3_P 109 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC3_N 111 GA Negative analog reference star connected at PNX3000.

ADAC4_P 114 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC4_N 112 GA Negative analog reference star connected at PNX3000.

ADAC5_P 115 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC5_N 117 GA Negative analog reference star connected at PNX3000.

PNX2000

Audio video input processor

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 4 of 26

Page 5

Philips Semiconductors

Table 4: Audio pins…continued

Symbol Pin Type Description

ADAC6_P 120 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC6_N 118 GA Negative analog reference star connected at PNX3000.

ADAC7_P 121 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC7_N 123 GA Negative analog reference star connected at PNX3000.

ADAC8_P 126 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC8_N 124 GA Negative analog reference star connected at PNX3000.

ADAC9_P 127 SA Positiv e analog ref e rence derived via emitter f ollower from

ADAC9_N 129 GA Negative analog reference star connected at PNX3000.

ADAC10_P 132 SA Positiv e analog reference derived via emitter follower from

ADAC10_N 130 GA Negative analog reference star connected at PNX3000.

ADAC11_P 133 SA Positiv e analog reference derived via emitter follower from

ADAC11_N 135 GA Negative analog reference star connected at PNX3000.

ADAC12_P 138 SA Positiv e analog reference derived via emitter follower from

ADAC12_N 136 GA Negative analog reference star connected at PNX3000.

PNX2000

Audio video input processor

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

PNX3000 V_SND pin.

Table 5: I2S-bus pins

Symbol Pin Type Description

I2S_IN_SD1 88 ID I2S-bus data in channel 1; TTL; 5VT

I2S_IN_SD2 87 ID I2S-bus data in channel 2; TTL; 5VT

I2S_IN_SD3 86 ID I2S-bus data in channel 3; TTL; 5VT

I2S_IN_SD4 85 ID I2S-bus data in channel 4; TTL; 5VT

I2S_IN_SD5 84 ID I2S-bus data in channel 5; TTL; 5VT

I2S_IN_SD6 83 ID I2S-bus data in channel 6; TTL; 5VT

I2S_OUT_SD1 77 OD I2S-bus data out channel 1; CMOS

I2S_OUT_SD2 76 OD I2S-bus data out channel 2; CMOS

I2S_OUT_SD4 75 OD I2S-bus data out channel 4; CMOS

I2S_OUT_SD5 74 OD I2S-bus data out channel 5; CMOS

I2S_OUT_SD6 73 OD I2S-bus data out channel 6; CMOS

I2S_OUT_SD3_SCK 71 OD I2S-bus bit clock channel 3; CMOS

I2S_OUT_SD3_WS 70 OD I2S-bus word select channel 3; CMOS

I2S_OUT_SD3 69 OD I2S-bus data-out channel 3; CMOS

I2S_SCK_SYS 79 IOD I2S-bus system bit clock; TTL-H; CMOS

I2S_WS_SYS 78 IOD I2S-bus system word select; TTL-H; CMOS

ADAC_CLK 89 OD Used for 128 fs or 256 fs clock output to external audio

DAC; CMOS.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 5 of 26

Page 6

Philips Semiconductors

Table 6: VIDDEC pins

Symbol Pin Type Description

HVINFO 20 OD horizontal and vertical sync information to PNX3000; CMOS

HSYNCFBL1 18 IA horizontal sync (external); fastblanking signal from SCART

HSYNCFBL2 19 IA horizontal sync (external); fastblanking signal from SCART

VSYNC1 21 ID vertical sync (external); TTL; 5VT

VSYNC2 22 ID vertical sync (external); TTL; 5VT

Table 7: ITU-656 pins

Symbol Pin Type Description

DVO_DATA_0 55 OD digital video output state 0; CMOS; Z; 5VT

DVO_DATA_1 56 OD digital video output state 1; CMOS; Z; 5VT

DVO_DATA_2 57 OD digital video output state 2; CMOS; Z; 5VT

DVO_DATA_3 58 OD digital video output state 3; CMOS; Z; 5VT

DVO_DATA_4 60 OD digital video output state 4; CMOS; Z; 5VT

DVO_DATA_5 61 OD digital video output state 5; CMOS; Z; 5VT

DVO_DATA_6 62 OD digital video output state 6; CMOS; Z; 5VT

DVO_DATA_7 63 OD digital video output state 7; CMOS; Z; 5VT

DVO_DATA_8 64 OD digital video output state 8; CMOS; Z; 5VT

DVO_DATA_9 65 OD digital video output state 9; CMOS; Z; 5VT

DVO_VALID 52 OD digital video data valid; CMOS; Z; 5VT

DVO_CLK 51 OD digital video output clock; CMOS; Z; 5VT

LL_CLK 50 ID reserved; TTL; 5VT

PNX2000

Audio video input processor

[1]

[1] It is recommended to bias this pad with a 10 kΩ resistor

Table 8: JTAG pins

Symbol Pin Type Description

TDO 93 OD JT AG test data out; CMOS

TDI 92 ID JTAG test data in; TTL-H; 5VT

TCK 94 ID JTAG test clock; TTL-H; 5VT

TRST_N

TMS 95 ID JTAG test mode select; TTL-H; 5VT

[1] It is recommended to pull-down TRST_N with a 10 kΩ resistor. This ensures correct reset state of

Table 9: I2C-bus pins

Symbol Pin Type Description

I2C_SDA 27 IOD I2C-bus data; TTL; Z; 5VT

I2C_SCL 26 IOD I2C-bus clock; TTL; Z; 5VT

I2C_ADR 17 ID I2C-bus address select (internal pull-down); TTL; 5VT

[1]

96 ID JTAG reset (active low); TTL-H; 5VT

internal TAP circuitry and correct POR of the device within defined state machine.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 6 of 26

Page 7

Philips Semiconductors

Table 10: Clock pins

Symbol Pin Type Description

MPIFCLK 31 OD 13.5 MHz or 27 MHz to PNX3000; CMOS

DCLK 47 OD reserved; CMOS

XIN 38 OSCIN crystal oscillator input

XOUT 39 OSCOUT crystal oscillator output

XGND 40 OSCGND crystal oscillator ground

Table 11: GTU pins

Symbol Pin Type Description

INTOUT 48 OD interrupt line output; Z; 5VT

Table 12: Reset pins

Symbol Pin Type Description

RESET_N 45 IA external reset input

RESET_SEL 46 ID selects between using an external reset input or using

PNX2000

Audio video input processor

internal POR; TTL; 5VT

HIGH = internal reset

LOW = external reset

Table 13: Digital supply pins

Symbol Pin Type Description

V

DDE

32,49,66, 82,91,

- 3.3 V supply voltage

141,143

V

SSE

28,41,59, 72,99,

- 3.3 V ground

144

[1]

V

DDI

30,35,42, 53,67,

- 1.8 V supply voltage

80,97

V

SS

29,36,43, 54,68,81,

- 1.8 V ground

98,139

[1]

V

DDM

V

SSD(I2D)

V

DDD(I2D)

V

SS(ADAC)

V

DDD(ADAC)

V

DD3(DTC)

V

DDD(DTC)

[1] V

44,140 - 1.8 V supply voltage for KSFRAMs and KROMs

1 GA I2D digital ground

16 SA I2D digital 1.8 V supply voltage

100 GD audio DAC 1.8 V digital ground

101 SD audio DAC 1.8 V digital supply voltage

23 SA DTC 3.3 V supply voltage

24 SA DTC 1.8 V supply voltage

DDI

and V

can be connected to same 1.8 V supply voltage.

DDM

Table 14: Analog supply pins

Symbol Pin Type Description

V

SSA(I2D)

V

DDA(I2D)

V

DDA(PLL)

6 GA I2D analog ground

11 SA I2D analog 1.8 V supply voltage

33 - phase locked loop 1.8 V supply voltage

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 7 of 26

Page 8

Philips Semiconductors

Table 14: Analog supply pins…continued

Symbol Pin Type Description

V

DDA(ADAC)

V

SS(DTC)

V

DDA(XTAL)

7. Functional description

7.1 Overview

Table 15 describes the functions of the hardware blocks (see also PNX2000 Block

Diagram Figure 1).

For more detailed functional description refer to the PNX2000 User Manual.

Table 15: Block function

Function Block Description

High speed data link I2D Receives data in three streams from PNX3000.

Video decoder

processor

Serial interface I2C-bus To access all the internal registers.

Global Task Unit GTU Generates all the internal clocks, reset and power

TV sound decoder DEMDEC

Audio processor AUDIO DSP Processing analog and digital audio sources.

Data Capture Unit DCU Acquires VBI data (Telete xt; CC; VPS) and f ormats in a

Formatter unit ITU-656 Formats YUV, VBI data and CVBS data in ITU-656.

Bus Control Unit BCU Bus arbitration among all the internal blocks.

Audio video input processor

102 SA audio DAC 3.3 V supply voltage

25 GA DTC analog ground

37 OSCVDD 1.8 V crystal oscillator supply voltage

VIDDEC Decodes and processes CVBS, YUV or Y/C in YUV

stream.

management.

Demodulation, decoding of terrestrial TV aud io

DSP

standards .

stream.

PNX2000

7.2 Interfaces

Table 16: Interfaces

Interface Description

I2C-bus The PNX2000 IC is controlled using an I2C-bus. It performs like an I2C-bus to

PI-bus bridge, i.e. translates I

commands.

I2D Receives data in three streams from PNX3000.

I2S-bus Seria l digital audio interface (6 stereo inputs, 6 stereo outputs) for connection to

other devices that support the I2S-bus standard. Can be used to receive decoded

sound from a multi-channel digital audio decoder, provide additional ADCs and

DACs, or loop audio signals through an external processor or delay line.

ITU-656 Mainly intended to transfer output data stream externally to the PNX8550, but the

output data stream could also be readable by other ITU-656 input devices that

implement data val id signalling.

DACS Digital-analog converters used to generate analog outputs from Sound Core.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 8 of 26

2

C-bus slave received commands to PI-bus master

Page 9

Philips Semiconductors

7.3 Features in detail

7.3.1 Video

• Automatic Gain Control (AGC) to correct amplitude errors at input source.

• Synchronization identification (used for channel search).

• Sync processing for 1f

• Standard detection of PAL, NTSC or SECAM and various 1f

1fH video

• Color decoding (ITU-601) for PAL, NTSC or SECAM input sources.

• 2D comb filtering.

• Support for component video sources with sync on CVBS or green.

• Fastbl ank insertion of RGB signals onto CVBS input.

2fH video

video input sources.

and 2fH video input source.

H

PNX2000

Audio video input processor

and 2fH component

H

• Support for various progressive and interlaced component video sources.

• Synchronization of video sources with sync on Y or external H/V inputs.

VBI data capture

• Decoding of 525 line standards; WST, WSS, VPS, CC, VITC.

• Decoding of 625 line standards; WST, WSS, CC, VITC.

ITU-656 output interface

• Video and VBI formatting into ITU-style output data stream, compliant to

ITU-656/1364 (exception being the use of a data valid signal).

• Interfacing to PNX8550 IC.

• Support for CVBS/C mode to interface to external picture improvement devices.

7.3.2 Audio

Demodulator and decoder

• Demodulator and Decoder Easy Programming (DDEP).

• Auto Standard Detection (ASD).

• Static Standard Selection (SSS).

• DQPSK demodulation for different standards, simultaneously with 1-channel FM

demodulation.

• NICAM decoding (B/G, I, D/K and L standard).

• Two-carrier multi-standard FM demodulation (B/G, D/K and M standard).

• Decoding for three analog multi-channel systems (A2, A2+ and A2*) and satellite

sound.

• Adaptive de-emphasis for satellite FM.

• Optional AM demodulation for system L, simultaneously with NICAM.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 9 of 26

Page 10

Philips Semiconductors

• Identification A2 systems (B/G, D/K and M standard) with different identification

• FM pilot carrier present detector.

• Monitor selection for FM/AM DC values and signals, with peak and quasi peak

• BTSC MPX decoding.

• SAP decoding.

• dbx

• Japan (EIAJ) decoding.

• FM radio decoding.

• Soft muting for DEMDEC outputs DEC, MONO and SAP.

• FM over modulation adaptation option to avoid clipping and distortion.

• Sample Rate Conversion (SRC) for up to three demodulated terrestrial audio

Audio multi-channel decoder

PNX2000

Audio video input processor

time constants.

detection option.

® 1

TV noise reduction.

signals. Allows processing of SCART and demodulated terrestrial signals.

• Dolby Pro Logic II™

• 6-channel processing for Main Left and Main Right, Subwoofer, Center, Surround

Left and Surround Right.

Volume and tone control

• Automatic Volume Level (AVL) control.

• Smooth volume control.

• Master volume control and balance.

• Soft mute.

• Loudness.

• Bass, treble.

• Dynamic Bass Enhancement (DBE).

• Dynamic ULTRABASS (DUB).

• Non-processed subwoofer.

• 5-band equalizer.

• Acoustical compensation.

• Programmable beeper.

• Noise generation for loudspeaker level trimming.

Reflection and delay

• Dolby Pro Logic II™ delay.

• Pseudo hall/matrix function.

Psychoacoustic spatial algorithms, downmix and split

1. dbx is a registered trademark of Carillon Electronics Corp.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 10 of 26

Page 11

Philips Semiconductors

• Incredible Mono.

• Incredible Stereo.

• Virtual Dolby Surround™.

• Virtual Dolby Digital™.

• Bass Redirection according to Dolby™ specifications.

• BBE

Interfaces and switching

®

Sound Processing

PNX2000

Audio video input processor

1

• Digital audio input interface (stereo I

• Digital audio output interface (stereo I

• Digital crossbar switch for all digital signal sources and destinations.

• Output crossbar for exchange of channel processing functionality.

• Voice recognition output interface (stereo I

• Audio monitoring for level detection.

• Eight audio DACs for 6-channel loudspeaker outputs and stereo headphones

output.

• Four audio DACs for stereo SCART output and stereo LINE output.

• Serial data link interfacing for analog multi-purpose interface PNX3000.

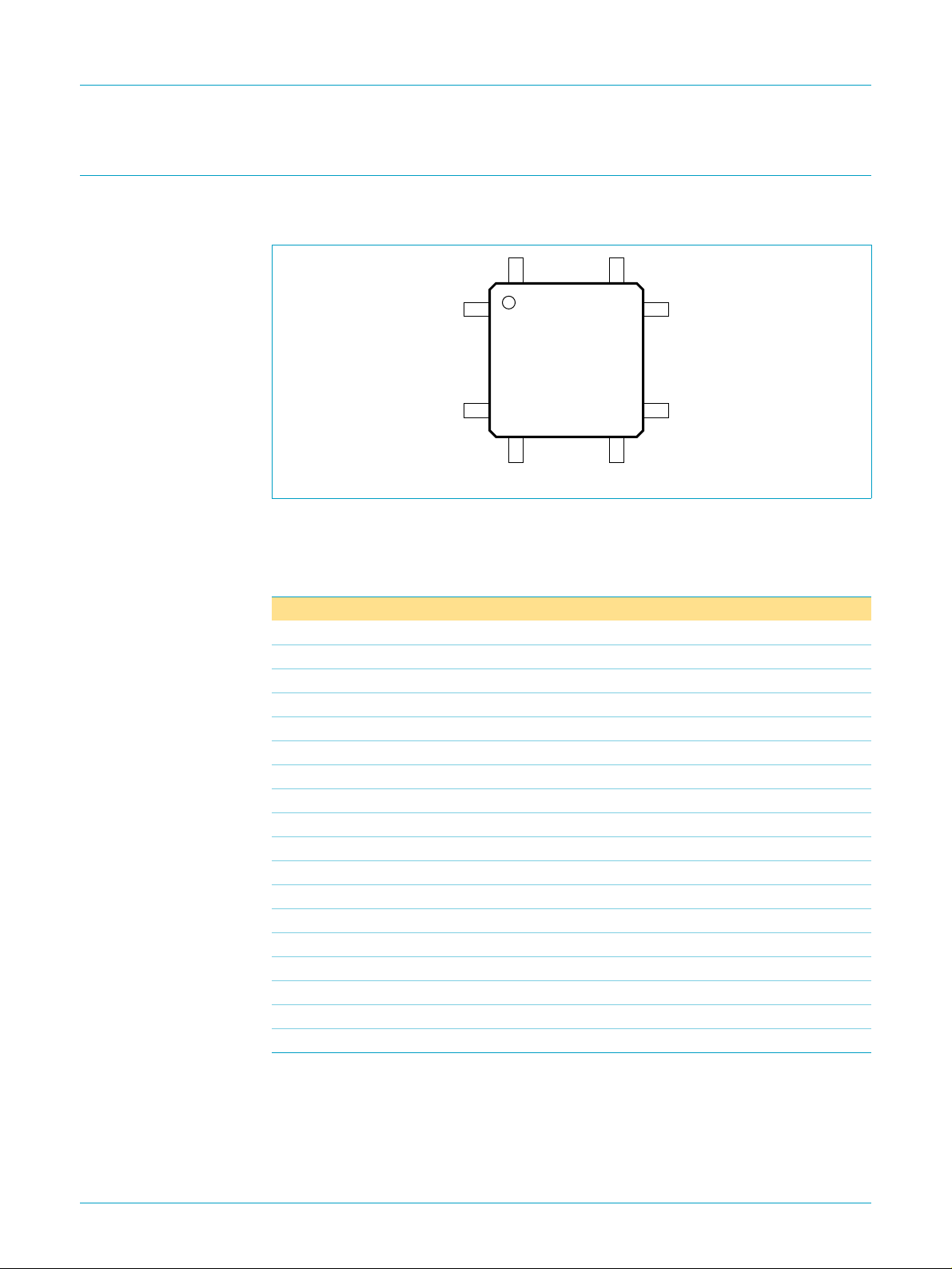

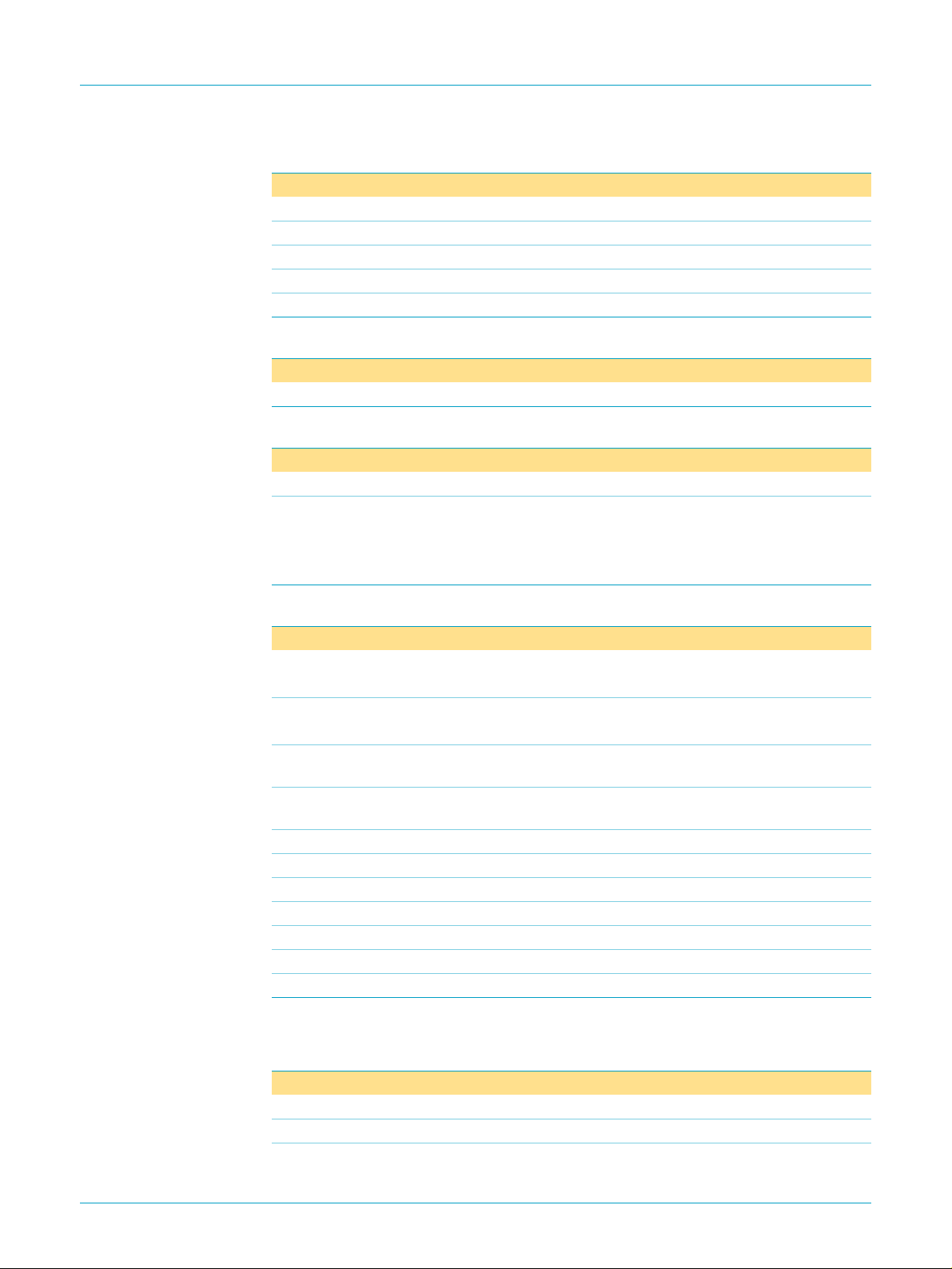

8. Television application

Figure 3 shows an overview of the top level hardware architecture of a TV application,

using the PNX3000 and PNX2000 as an analog front-end and the PNX8550 as the

main processor. This system is aimed at the hybrid (analog or digital) TV market.

The main SOC in the system, PNX8550, performs key features for high quality

television like video quality enhancement, motion compensation and

picture-in-picture processing.

2

S-bus input interface).

2

S-bus output interface).

2

S-bus output interface).

PNX2000 together with PNX3000 are used to perform the input decoding of a single

stream of analog audio and a single stream of analog video (1f

signals.

PNX2000 performs the following main functions:

• Color decoding into ITU-601 compatible format (1f

or 2fH).

H

or 2fH) broadcast

H

• A digital interface to external 3D comb filter.

• VBI data capture (Teletext, WSS, CC).

• ITU-656 formatting for communication to PNX8550.

• Audio demodulation and decoding.

• Audio processing and D-A conversion.

The audio data is transferred between PNX2000 and PNX8550 using I2S-bus.

PNX2000 and PNX3000 are controlled from PNX8550 via the I

1. BBE is a registered trademark of BBE Sound Inc. See Section 18.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 11 of 26

2

C-bus.

Page 12

Philips Semiconductors

PNX2000

Audio video input processor

CVBS Y/C

RGB 2

L/R audio 2

CVBS 1

L/R audio 1

SIF

VIF

PNX3000

SCART

21

20

19

18

17

16

15

14

13

12

11

10

8

6

4

2

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

TUNERS

UV1316

UV13361

status

LEVEL ADJUSTMENT

REMOTE CONTROL

LOCAL KEYPAD

Fig 3. TV application

9. Limiting values

I2D

L/R

audio

STANDBY

MICRO-

CONTROLLER

PNX2000

CVBS

YUV (656)

2

S-bus

audio I

2

audio I

S-bus

(2×)

audio I2S-bus

(3×)

PNX8550

8-bit or 16-bit

32-bit

RGB

10 bits (3×)

DISPLAY

PROCESSOR

DDR

16 Mb

FLASH

ROM

18 Mb

RGB

AMPLIFIER

DEFL.

CONT.

AUDIO

AMPLIFIER

mce558

Permanent damage ma y occur if absolute maxim um ratings are e xceeded. Prolo nged

operation at maximum rating may significantly reduce the reliability of the product.

Table 17: Absolute maximum ratings

Ratings are valid only within operating temperature range unless otherwise specified. All voltages are with respect to VSS

unless otherwise stated.

Symbol Parameter Min Max Unit

V

DD(core)

V

DD(I/O)

V

I

V

I

I

latchup

V

esd

V

esd

T

stg

[1] Not to exceed 4.6 V.

[2] Including voltage on outputs in 3-state mode.

[3] Only valid when the V

[4] Valid for : −(0.5 × VDD) < V < +(1.5 × VDD); Tj < 125 °C.

[5] Human Body Model, I

[6] Machine Model 0.5 mH, I

[7] This product includes circuits specifically designed for the protection of its internal devices from the damaging effects of excessive static

charge. However, it is suggested that conventional precautions be taken to avoid applying voltages greater than the rated maximum.

supply voltage −0.5 +2.5 V

supply voltage −0.5 +4.6 V

DC input voltage (

[1] [2]

DC input voltage 5V tolerant I/O pins (

latch-up current (

[4]

) 100 - mA

electrostatic discharge voltage HBM (

electrostatic discharge voltage MM (

[3]

and

) −0.5 V

[2]

[3]

and

) −0.5 +6 V

[5] [7]

) - ±2 kV

[6] [7]

) - ±200 V

+ 0.5 V

DD(I/O)

storage temperature −40 +125 °C

supply voltage is present.

DD(I/O)

< 1 mA.

leak

< 1 mA.

leak

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 12 of 26

Page 13

Philips Semiconductors

PNX2000

Audio video input processor

10. Characteristics

10.1 Static characteristics

Table 18: Static characteristics: power supply pins

T

= 0 °C to +70 °C to commercial unless otherwise specified.

amb

Symbol Parameter Conditions Min Typ Max Unit

1.8V Power Supply Pins: V

V

DD(core)

I

DD(core)

supply voltage, 1.8 V supplies - 1.65 1.8 1.95 V

supply current, 1.8 V supplies V

3.3V Power Supply Pins: V

V

DD(3V3)

I

DD(3V3)

supply voltage, 3.3 V supplies - 3.0 3.3 3.6 V

supply current, 3.3 V supplies V

DDI

DDE

, V

, V

, V

DDM

DD3(DTC)

DDD(I2D)

, V

DDA(ADAC)

, V

DDA(I2D)

, V

DDA(PLL)

, V

DDA(XTAL)

= 1.8 V - 250 - mA

DD(core)

= 3.3 V - 50 - mA

DD(core)

, V

DDD(ADAC)

, V

DDD(DTC)

Table 19: Static characteristics: digital pins

T

= 0 °C to +70 °C to commercial unless otherwise specified.

amb

Symbol Parameter Conditions Min Typ Max Unit

I2S inputs: I2S_IN_SD1-6, I2C Address: I2C_ADR

I

IL

V

I

V

IH

V

IL

I

PD

LOW-level input current Vi = 0 - - 1 µA

input voltage - 0 - 5.5 V

HIGH-level input voltage - 2.0 - - V

LOW-level input voltage - - - 0.8 V

pull-down current Vi = V

DD(I/O)

20 50 75 µA

External Sync: VSYNC1, VSYNC2, Reset: RESET_SEL, ITU-656: LL_CLK

I

IL

I

IH

V

I

V

IH

V

IL

LOW-level input current Vi = 0 - - 1 µA

HIGH-level input current Vi = V

DD(I/O)

- - 1 µA

input voltage - 0 - 5.5 V

HIGH-level input voltage - 2.0 - - V

LOW-level input voltage - - - 0.8 V

Jtag inputs: TDI, TCK, TRST_N, TMS

I

IH

V

I

V

IH

V

IL

V

hys

I

PU

HIGH-level input current Vi = V

DD(I/O)

- - 1 µA

input voltage - 0 - 5.5 V

HIGH-level input voltage - 2.0 - - V

LOW-level input voltage - - - 0.8 V

hysteresis voltage - - 0.3 - V

pull-up current Vi = 0 −25 −50 −65 µA

V

DD(I/O)

< V

< 5 V 0 0 0 µA

i

I2C Pins: I2C_SDA, I2C_SCL

C

I

I

LI

input capacitance - - 5 - pF

input leakage current [1] V

DD(3V3)

= 3.3 V; T

= 25 °C 1.37 1.85 2.45 µA

amb

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 13 of 26

Page 14

Philips Semiconductors

PNX2000

Audio video input processor

Table 19: Static characteristics: digital pins…continued

T

= 0 °C to +70 °C to commercial unless otherwise specified.

amb

Symbol Parameter Conditions Min Typ Max Unit

I

IN(MAX)

V

I

V

IL

V

IH

V

OL

I

OL

max. input current [2] at 5 V 8.20 10.7 12.45 µA

input voltage - 0 - 5 V

LOW-level input voltage - - - 0.8 V

HIGH-level input voltage - 2.0 - - V

LOW-level output voltage - - - 0.4 V

LOW-level output current VOL=0.4V - 8.45 - mA

ITU-656 Outputs: DVO_DATA_0-9, DVO_VALID, DVO_CLK

I

oz

V

I

V

OH

V

OL

I

OH

I

OL

I

OH

I

OL

3-state output leakage VO = 0

VO = V

DD(I/O)

- - 1 µA

input voltage - 0 - 5.5 V

HIGH-level output voltage I

LOW-level output voltage I

HIGH-level output current V

LOW-level output current V

HIGH-level short circuit current V

LOW-level short circuit current V

= −4 mA 2.4 - - V

OH

= 4 mA - - 0.4 V

OL

= 2.4 −4 - - mA

OH

= 0.4 V 4 - - mA

OL

= 0 - - −45 mA

OH

OL

= V

DD(I/O)

- - 50 mA

I2S I/O: I2S_SCK_SYS, I2S_WS_SYS

I

IL

I

IH

V

I

V

IH

V

IL

V

hys

I

oz

V

OH

V

OL

I

OH

I

OL

I

OH

I

OL

LOW-level input current Vi = 0 - - 1 µA

HIGH-level input current Vi = V

DD(I/O)

- - 1 µA

input voltage - 0 - V

HIGH-level input voltage - 2.0 - - V

LOW-level input voltage - - - 0.8 V

hysteresis voltage - - 0.4 - V

3-state output leakage VO = 0

VO = V

HIGH-level output voltage I

LOW-level output voltage I

HIGH-level output current V

LOW-level output current V

HIGH-level short circuit current V

LOW-level short circuit current V

= −8 mA 2.4 - - V

OH

= 8 mA - - 0.4 V

OL

= 2.4 −8 - - mA

OH

= 0.4 V 8 - - mA

OL

= 0 - - −95 mA

OH

= V

OL

DD(I/O)

DD(I/O)

- - 1 µA

- - 95 mA

I2S Outputs: I2S_OUT_SD1-6, JTAG Output: TDO, PNX3000 Clock: MPIFCLK, Sync Output: HVINFO

V

OH

V

OL

I

OH

I

OL

I

OH

I

OL

HIGH-level output voltage I

LOW-level output voltage I

HIGH-level output current V

LOW-level output current V

HIGH-level short circuit current V

LOW-level short circuit current V

= −4 mA 2.4 - - V

OH

= 4 mA - - 0.4 V

OL

= 2.4 −4 - - mA

OH

= 0.4V 4 - - mA

OL

= 0 - - −45 mA

OH

OL

= V

DD(I/O)

- - 50 mA

I2S Output: I2S_OUT_SD3_SCK, I2S_OUT_SD3_WS, ADAC_CLK, Clock Output: DCLK

V

OH

HIGH-level output voltage I

= −8 mA 2.4 - - V

OH

DD(I/O)

V

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 14 of 26

Page 15

Philips Semiconductors

PNX2000

Audio video input processor

Table 19: Static characteristics: digital pins…continued

T

= 0 °C to +70 °C to commercial unless otherwise specified.

amb

Symbol Parameter Conditions Min Typ Max Unit

V

OL

I

OH

I

OL

I

OH

I

OL

LOW-level output voltage I

HIGH-level output current V

LOW-level output current V

HIGH-level short circuit current V

LOW-level short circuit current V

= 8 mA - - 0.4 V

OL

= 2.4 −8 - - mA

OH

= 0.4 V 8 - - mA

OL

= 0 - - −95 mA

OH

OL

= V

DD(I/O)

- - 95 mA

Interrupt: INTOUT

I

oz

V

I

V

OL

I

OL

I

OL

3-state output leakage VO = 0

VO = V

DD(I/O)

- - 1 µA

input voltage - 0 - 5.5 V

LOW-level output voltage I

LOW-level output current V

LOW-level short circuit current V

= 8 mA - - 0.4 V

OL

= 0.4 V 8 - - mA

OL

OL

= V

DD(I/O)

- - 140 mA

Table 20: Static characteristics: analog pins

T

= 0 °C to +70 °C to commercial unless otherwise specified.

amb

Symbol Parameter Conditions Min Typ Max Unit

External Sync: HSYNCFBL1, HSYNCFBL2

V

IT

V

IT

input threshold dtc_lowth = 0 - 1.65 - V

input threshold dtc_lowth = 1 - 0.65 - V

Reset: RESET_N

V

trip_high

V

trip_low

high trip level RESET_SEL = 0 1.0 1.2 1.4 V

low trip level RESET_SEL = 0 0.95 1.1 1.3 V

I2D Inputs: DLINK1-3DP, DLINK1-3DN,DLINK1-3SP, DLINK1-3SN

V

sens

Z

diff

V

DATA(pos)

V

DATA(neg)

V

STROBE(pos)

V

STROBE(neg)

input sensitivity - - 6 - mV

differential line load impedance across input diff pair - 100 - Ω

data pos. range - 0 - 300 mV

data neg. range - 0 - 300 mV

strobe pos. range - 0 - 300 mV

strobe neg. range - 0 - 300 mV

Audio DACs: ADAC 1-12P, ADAC1-12N

V

REFP

V

REFN

I

REFP

positive reference voltage - 3.0 3.3 3.6 V

negative reference voltage - - 0 - V

positive reference current - - 820 - µA

Audio DACs: ADAC 1-12

V

OUT(rms)

output voltage (rms); single-ended, digital

- - 1.17 - V

i/p level = 0 dBFS

R

OUT

R

L

output resistance - 0.7 1.0 1.3 kΩ

load resistance - 10 - - kΩ

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 15 of 26

Page 16

Philips Semiconductors

PNX2000

Audio video input processor

10.2 Dynamic characteristics

Table 21: Dynamic characteristics

Symbol Parameter Conditions Min Typ Max Unit

I2C

f

clk

t

r

t

f

clock frequency - - 400 - kHz

rise time 1.5 kΩ ext. pull-up; 160 pF load - 550 - ns

fall time 1.5 kΩ ext. pull-up; 160 pF load 130 162 245 ns

Viddec: HVINFO (slew rate limited)

t

thl

t

tlh

output transition time (H to L) 30 pF load - 10 13.8 ns

output transition time (L to H) 30 pF load - 10 13.8 ns

ITU-656

t

su(DATA)

t

h(DATA)

data setup at Rx 40 pF load - - 7.3 ns

data hold at Rx 40 pF load - - 4.9 ns

I2S

f

s

f

SCK

f

SCK

DF

SCK

audio sample frequency - 32 48 48 kHz

SCK frequency I2S-bus master mode - 64f

SCK frequency I2S-bus slave mode 32f

SCK duty factor I2S-bus master mode 40 50 60 %

- -

s

64f

s

256fs-

s

DF

t

RSCK

t

RSCK

SCK

SCK duty factor I2S-bus slave mode 35 - 65 %

SCK rise / fall time I2S-bus master mode; C

SCK rise / fall time I2S-bus slave mode; f

= 30 pF - - 5 ns

load

SCK

= 3.072

- - 50 ns

MHz

t

d

t

h

t

s

delay time: SCK to WS and SD

[2]

outputs

hold time: SCK to WS and SD inputs - 0 - - ns

setup time: WS and SD inputs to

T

= 1/f

SCK

T

SCK

= 1/f

SCK

SCK

0.3 0.5 0.7 T

0.2 - - T

SCK

SCK

SCK

I2D

f

clock(WORD)

word clock frequency - - 13.5 - MHz

WL word length - - 44 - bit

DR data rate - - 594 - Mbit/s

f

clock(BIT)

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 16 of 26

bit clock freq. - - 297 - MHz

Page 17

Philips Semiconductors

PNX2000

Audio video input processor

Table 21: Dynamic characteristics…continued

Symbol Parameter Conditions Min Typ Max Unit

JTAG Clock Reset

t

low

t

high

t

pulse

[1] Allowed SCK/WS ratios are 32, 48, 64, 128 and 256 SCK periods per WS period.

[2] All timings relative to the rising edge of SCK.

[3] See Section 10.4 for waveforms.

Time RESET_N should be below

V

before internal reset = 1.

trip_high

Time RESET_N should be above

V

(after t

before internal reset = 0

trip_high

pulse

).

Time before PNX2000 internal reset

[3]

.

= 0

RESET_SEL = 0 - - 11 µs

RESET_SEL = 0 - - 2 µs

RESET_SEL = 0 200 - - ns

10.3 Audio DAC characteristics

Table 22: Dynamic characteristics: Audio DAC

Tamb = 0 °C to +70 °C for commercial unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Unit

Audio DAC Outputs: ADAC1-12

f

s

audio sample frequency - 32 48

S/N Signal to Noise Ratio, CCIR-2 k

weighted

(THD+N)/S Total Harmonic Distortion + Noise to

Signal ratio

f

res

frequency response +/-1 dB <10 - 22.5 kHz

outputs muted; reference f = 2 kHz,

0 dBFS

f =1 kHz; 0 dBFS; 22 kHz

measurement bandwidth

- 94 - dB

- -77 - dB

[1]

48 kHz

α

ct

[1] Allowed audio sample frequencies are 32 kHz, 44.1 kHz and 48 kHz. Default fS in I2S-bus master mode is 48 kHz.

crosstalk between adjacent DACs f = 1 kHz; 0 dBFS - -90 - dB

The audio DACs are based on a switched-resistor architecture which acts as a

controlled voltage divider between the positive and negative references ADACn_P

and ADACn_N. Therefore all noise on the reference pins will spread directly to the

associated output pin ADACn. Consequently it is important to provide adequate

filtering of the reference voltage to allow optimum signal-to-noise performance. Also,

the voltage difference between ADACn_P and SDAC_3V3 should be kept to a

minimum as any difference will degrade distortion performance.

The DA Cs hav e an internal resolution of 4 bits , running at a clock frequency of 128 fS,

using a noise shaper circuit to shift the quantization noise to out-of-band frequenci es.

To prevent HF overloading of the circuit that is driven by the DAC outputs, a 3.3 nF

capacitor should be used to filter off the HF signal content. Together with the DAC’s

nominal output impedance of 1 kΩ, a first order roll-off at approximately 50 kHz will

result. One capacitor is required for each DAC output, connected between ADACn

and the corresponding ADACn_N.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 17 of 26

Page 18

Philips Semiconductors

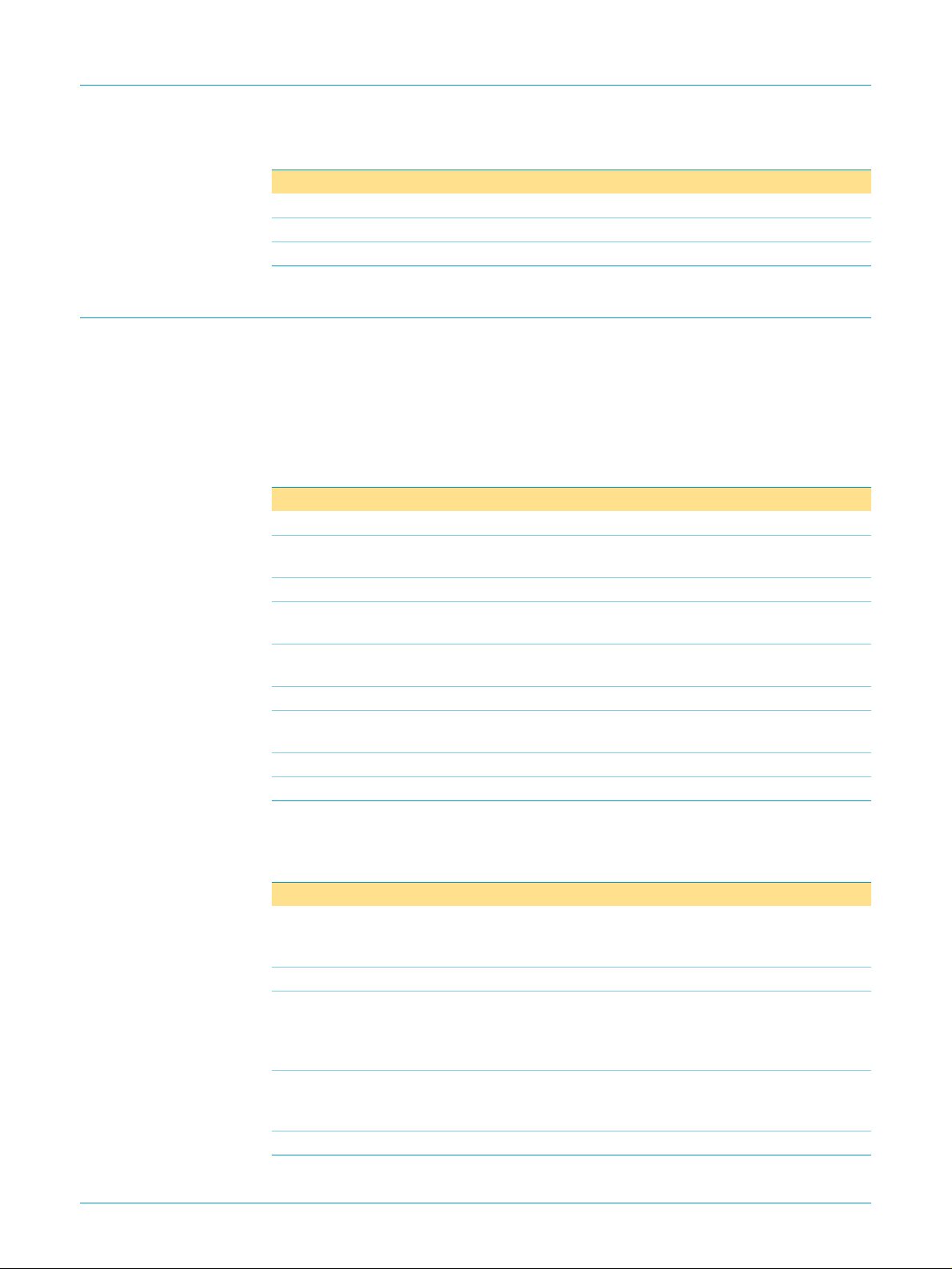

10.4 Timing

10.4.1 Clock

Crystal specification

The crystal oscillator can be used with an external crystal, or in bypass mode with

external clock signal, see

PNX2000

Audio video input processor

Figure 4.

V

V

SSA

DDA

xtm

pd

V

V

SSA

DDA

xtmpd

on-chip

off-chip

XO

osc_in

n.c.

(a) (b)

clock

clkout

osc_out

XO

clkout

osc_outosc_in

Cx2Cx1

mce560

Fig 4. Application diagram: (a) slave/test mode, (b) oscillation mode

The supported crystal/external clock frequencies are 27 MHz and 13.5 MHz. The

crystal oscillator is followed by a selectable divide-by-two frequency divider giving

three available clock frequencies, as shown in

Table 23: Primary clock settings

Clock/Crystal Input Divider setting Clock frequency

27 MHz x/1 27 MHz

27 MHz x/2 13.5 MHz

13.5 MHz x/1 13.5 MHz

13.5 MHz x/2 6.75 MHz

Table 23.

The crystal specification is:

• Package: surface mount.

• Accuracy: (±50 ppm).

• Temperature: (±50 ppm).

• Operating temperature range: −20 to +70

o

C.

• Load capacitance: 30 pF.

Table 24: Crystal parameters

Oscillator

frequency (fc)

13.5 MHz

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 18 of 26

Crystal load

capacitance (CL)

Max.crystal series

resistance (RS)

External load

capacitors (Cx1; Cx2)

10 pF < 600 Ω 2 x 18 pF

20 pF < 255 Ω 2 x 38 pF

30 pF < 140 Ω 2 x 58 pF

Page 19

Philips Semiconductors

Table 24: Crystal parameters…continued

Oscillator

frequency (f

27 MHz

10.4.2 Reset

Audio video input processor

Crystal load

capacitance (C

)

c

10 pF < 130 Ω 2 x 18 pF

20 pF < 50 Ω 38 pF; 18 pF

30 pF n.a. n.a.

Max.crystal series

resistance (R

)

L

External load

capacitors (Cx1; Cx2)

)

S

PNX2000

RESET_N pin and internal reset timing

Fig 5. PNX2000 reset

10.4.3 ITU-656

DVO_CLK

DVO_DATA[9:0]

RESET_N

internal

reset

long external reset

produces internal reset

t

low

t

high

short spike

ignored

t

pulse

mce561

DVO_VALID

t

su(DATA)

t

h(DATA)

mce562

Fig 6. Timing ITU interface

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 19 of 26

Page 20

Philips Semiconductors

11. Glossary

PNX2000

Audio video input processor

AGC .................Automatic Gain Control

ASD .................Auto Standard Detection

AVL ..................Auto Volume Level

BCU .................Bus Control Unit

BTSC ...............Broadcast TV System Committee

DBE .................Dynamic Base Enhancement

DCU .................Data Capture Unit

DDEP.............. Demodulator and Decoder Easy

Programming

DEMDEC..........Demodulator Decoder

DQPSK ............Differential Quadrature Phase Shift Keying

DSP..................Digital Signal Processor

DUB .................Dynamic UltraBass

DVD..................Digital Video Disc

EIAJ.................Electronic Industries Association of Japan

GTU .................Global Task Unit

HBM.................Human Body Model

I2C-bus.............Inter Integrated Circuit bus

LQFP ...............Low profile Quad Flat Package

MM...................Machine Model

MPX.................Multiplexer

NICAM.............Near Instantaneous Compounded Audio

Multiplex

NTSC...............National TV Systems Committee

PAL ..................Phase Alternate Line

SAP .................Secondary Audio Program

SCART ............Syndicate for Constructors of Apparatus for

Radio and Television

SECAM............Sequential Color and Memory

SMD.................Surface Mount Device

SRC.................Sample Rate Conversion

SSS .................Static Standard Selection

SSOP...............Shrink Small Outline Package

SOC.................System On Chip

VBI...................Vertical Blanking Interval

VIDDEC...........Video front-end Decoder

VITC ................Vertical Interval Time Code

VPS .................Video Program System

WSS ................Wide Screen Signaling

WST.................World System Teletext

9397 750 12066 © Philips Electronics N.V. 2004 All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 20 of 26

Page 21

Philips Semiconductors

12. Package outline

PNX2000

Audio video input processor

LQFP144: plastic low profile quad flat package; 144 leads; body 20 x 20 x 1.4 mm

c

108

109

144

1

y

pin 1 index

e

b

wM

p

D

H

D

Z

X

D

73

36

72

37

Z

E

B

e

wM

b

p

vM

vM

B

A

E

A

H

E

A

A

2

A

1

detail X

L

L

p

SOT486-1

(A )

3

θ

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

A

UNIT A1A2A3bpc E

max.

0.15

mm

1.6

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

OUTLINE

VERSION

SOT486-1 136E23 MS-026

0.05

1.45

1.35

0.27

0.17

0.20

0.09

0.25

IEC JEDEC JEITA

(1)

(1) (1)(1)

D

20.1

20.1

19.9

19.9

REFERENCES

H

e HEL L

D

22.15

21.85

22.15

21.85

0.5

p

0.75

0.45

0.080.2 0.081

EUROPEAN

PROJECTION

Z

D

1.4

1.1

Zywv θ

E

1.4

7

1.1

0

ISSUE DATE

00-03-14

03-02-20

o

o

Fig 7. LQFP package outline

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 21 of 26

Page 22

Philips Semiconductors

13. Soldering

13.1 Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account

of soldering ICs can be found in our Data Handbook IC26; Integrated Circuit

Packages (document order number 9398

There is no soldering method that is ideal for all IC packages. W a v e soldering can still

be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In

these situations reflow soldering is recommended. In these situations reflo w soldering

is recommended.

13.2 Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and

binding agent) to be applied to the printed-circuit board by screen printing, stencilling

or pressure-syringe dispensing before package placement. Driven by legislation and

environmental forces the worldwide use of lead-free solder pastes is increasing.

PNX2000

Audio video input processor

652 90011).

Several methods exist for reflowing; for example, convection or convection/infrared

heating in a conveyor type oven. Throughput times (preheating, soldering and

cooling) vary between 100

Typical reflow peak temperatures range from 215 to 270 °C depending on solder

paste material. The top-surface temperature of the packages should preferably be

kept:

• below 220 °C (SnPb process) or below 245 °C (Pb-free process)

— for all BGA and SSOP-T packages

— for packages with a thickness ≥Š 2.5 mm

— for packages with a thickness < 2.5 mm and a volume ≥ 350 mm3 so called

thick/large packages.

• below 235 °C (SnPb process) or below 260 °C (Pb-free process) f or packages with

a thickness <

Moisture sensitivity precautions, as indicated on packing, must be respected at all

times.

2.5 mm and a volume < 350 mm3 so called small/thin packages.

13.3 Wave soldering

Conventional single wave soldering is not recommended for surface mount devices

(SMDs) or printed-circuit boards with a high component density, as solder bridging

and non-wetting can present major problems.

and 200 seconds depending on heating method.

To overcome these problems the double-wave soldering method was specifically

developed.

If wave soldering is used the following conditions must be observed for optimal

results:

• Use a double-wave soldering method comprising a turbulent wave with high

upward pressure followed by a smooth laminar wave.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 22 of 26

Page 23

Philips Semiconductors

• For packages with leads on two sides and a pitch (e):

• For packages with leads on four sides, the footprint must be placed at a 45° angle

During placement and before soldering, the package must be fixed with a droplet of

adhesive. The adhesive can be applied by screen printing, pin transfer or syringe

dispensing. The package can be soldered after th e adhesive is cured.

Typical dwell time of the leads in the wave ranges from 3 to 4 seconds at 250 °C or

265

A mildly-activated flux will eliminate the need for removal of corrosive residues in

most applications.

PNX2000

Audio video input processor

— larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be

parallel to the transport direction of the printed-circuit board;

— smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the

transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

to the transport direction of the printed-circuit board. The footprint must incorporate

solder thieves downstream and at the side corners.

°C, depending on solder material applied, SnPb or Pb-free respectively.

13.4 Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low

voltage (24

must be limited to 10

V or less) soldering iron applied to the flat part of the lead. Contact time

seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within

2

to 5 seconds between 270 and 320 °C.

13.5 Package related soldering information

Table 25: Suitability of surface mount IC packages for wave and reflow soldering

methods

Package

BGA, LBGA, LFBGA, SQFP, SSOP-T

TFBGA, VFBGA

DHVQFN, HBCC, HBGA, HLQFP, HSQFP,

HSOP, HTQFP, HTSSOP, HVQFN, HVSON,

SMS

PLCC

LQFP, QFP, TQFP not recommended

SSOP, TSSOP, VSO, VSSOP not recommended

PMFP

[1]

[3]

,

[5]

, SO, SOJ suitable suitable

[8]

Soldering method

Wave Reflow

not suitable suitable

not suitable

not suitable not suitable

[2]

[4]

[5][6]

[7]

suitable

suitable

suitable

[1] For more detailed information on the BGA packages refer to the (LF)BGA Application Note

(AN01026); order a copy from your Philips Semiconductors sales office.

[2] All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the

maximum temperature (with respect to time) and body size of the package, there is a risk that internal

or external package cracks may occur due to vaporization of the moisture in them (the so called

popcorn effect). For details, refer to the Drypack information in the Data

Circuit Packages; Section: Packing Methods.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 23 of 26

Handbook IC26; Integrated

Page 24

Philips Semiconductors

[3] These transparent plastic packages are extremely sensitive to reflow soldering conditions and must

on no account be processed through more than one soldering cycle or subjected to infrared reflow

soldering with peak temperature exceeding 217

oven. The package body peak temperature must be kept as low as possible.

[4] These packages are not suitable for wa v e soldering. On versions with the heatsink on the bottom side,

the solder cannot penetrate between the printed-circuit board and the heatsink. On versions with the

heatsink on the top side, the solder might be deposited on the heatsink surface.

[5] If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave

direction. The

[6] Wave soldering is suitable for LQFP, QFP and TQFP packages with a pitch (e) larger than 0.8 mm; it

is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65

[7] Wave soldering is suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than

0.65

mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

[8] Hot bar or manual soldering is suitable for PMFP packages.

package footprint must incorporate solder thieves downstream and at the side corners.

14. Revision history

Table 26: Revision history

Rev Date CPCN Description

01 20040504 - preliminary data (9397 750 12066)

PNX2000

Audio video input processor

°C ± 10 °C measured in the atmosphere of the reflow

mm.

9397 750 12066 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 24 of 26

Page 25

Philips Semiconductors

15. Data sheet status

PNX2000

Audio video input processor

Level Data sheet

I Objective data Development This data sheet contains data from the objective specification for product development. Philips

II Preliminary data Qualification This data sheet contains data from the preliminary specification. Supplementary data will be published at a

III Product data Production This data sheet contains data from the product specification. Philips Semiconductors reserves the right to

[1] Please consul t the most recently issued data sheet before initiating or completing a

design.

[2] The product status of the device(s) described in this data sheet may have changed

since this data sheet was published. The latest information is available on the

Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status

determines the data sheet status.

status

[1]

16. Definitions

Short-form specification – The data in a short-form specification is

extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition – Limiting values given are in accordance with

the Absolute Maximum Rating System (IEC

more of the limiting values may cause permanent damage to the device.

These are stress ratings only and operation of the device at these or at any

other conditions above those giv en in the Characteristics sections of the

specification is not implied. Exposure to limiting values for extended periods

may affect device reliability.

Application information – Applications that are described herein for any of

these products are for illustrative purposes only. Philips Semiconductors

make no representation or warranty that such applications will be suitable for

the specified use without further testing or modification.

17. Disclaimers

Life support – These products are not designed for use in life support

appliances, devices, or systems where malfunction of these products can

reasonably be expected to result in personal injury. Philips Semiconductors

customers using or selling these products for use in such applications do so

at their own risk and agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Right to make changes – Philips Semiconductors reserves the right to

make changes in the products - including circuits, standard cells, and/or

software - described or contained herein in order to improve design and/or

performance. When the product is in full production (status ‘Production’),

relevant changes will be communicated via a Customer Product/Process

Change Notification (CPCN). Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no

licence or title under any patent, copyright, or mask work right to these

Product

status

[2][3]

Definition

Semiconductors reserves the right to change the specification in any manner without notice .

later date. Philips Semiconductors reserves the right to change the specification without notice, in order to

improve the design and supply the best possible product.

make changes at any time in order to imp ro v e th e design, man ufacturing and supply. Relevant changes will be

communicated via a Customer Product/Process Change Notification (CPCN).

60134). Stress above one or

products, and makes no representations or warranties that these products

are free from patent, copyright, or mask work right infringement, unless

otherwise specified.

18. Licenses

Purchase of Philips I2C components

Purchase of Philips I2C components conveys a license

under the Philips’ I

2

I

C system provided the system conforms to the I2C

specification defined by Philips. This specification can be

ordered using the code 9398

Dolby Laboratories

‘Dolby’ and ‘Pro Logic’ are trademarks of Dolby Laboratories, San

Francisco, USA. Products are available to licensees of Dolby Laborat ories

Licensing Corp., 100 P otrero Avenue, San Francisco, CA, 94103, USA. Tel:

1-415-558-0200, Fax: 1-415-863-1373.

Supply of this implementation of Dolby Technology does not convey a

license, nor imply a right under any pat ent to use this impleme ntation in an y

final product. A license for such use is required from Dolby Labor atories.

BBE Sound

BBE is a registered trademark of BBE Sound Inc., 5381 Production Drive,

Huntington Beach, CA, 92649, USA. The use of BBE needs licensing from

BBE Sound Inc. Tel: 1-714-897-6766, Fax: 1-714-895-6728.

dbx - TV noise reduction

A Set-Maker License is required for use of this product unde r one (or more)

of the following patents: US4,539, 526; 5,796,842; 6,118,879 and U.S.

Patent Application 09/638245 . For further information contact THAT

Corporation, 45 Sumner Street, Milford, Massachusetts 01757-1656, USA.

Tel: 1-508-478-9200, FAX: 1-508-478-0990

2

C patent to use the components in the

393 40011.

19. Trademarks

Nexperia – is a trademark of Koninklijke Philips Electronics N.V.

Dolby Pro Logic,Virtual Dolby Digital and Virtual Dolby Surround – are

trademarks of Dolby Laboratories |nc.

BBE – is a registered trademark of BBE Sound Inc.

dbx – is a registered trademark of Carillon Electronics Corp.

20. Contact information

For additional information, please visit http://www.semiconductors.philips.com.

For sales office addresses, send an email to: sales.addresses@www.semiconductors.philips.com.

9397 750 12066 © Philips Electronics N.V. 2004 All rights reserved.

Preliminary data Rev. 01 – 04 May 2004 25 of 26

Page 26

Philips Semiconductors

Contents

1 General description. . . . . . . . . . . . . . . . . . . . . . 1

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

4 Ordering information. . . . . . . . . . . . . . . . . . . . . 2

5 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 2

6 Pinning information. . . . . . . . . . . . . . . . . . . . . . 3

6.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

6.1.1 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

7 Functional description . . . . . . . . . . . . . . . . . . . 8

7.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

7.2 Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

7.3 Features in detail . . . . . . . . . . . . . . . . . . . . . . . 9

7.3.1 Video . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

7.3.2 Audio. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

8 Television application . . . . . . . . . . . . . . . . . . . 11

9 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . 12

10 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . 13

10.1 Static characteristics . . . . . . . . . . . . . . . . . . . . 13

10.2 Dynamic characteristics . . . . . . . . . . . . . . . . . 16

10.3 Audio DAC characteristics . . . . . . . . . . . . . . . 17

10.4 Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

10.4.1 Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

10.4.2 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

10.4.3 ITU-656. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

11 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

12 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 21

13 Soldering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

13.1 Introduction to soldering surface mount

packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

13.2 Reflow soldering. . . . . . . . . . . . . . . . . . . . . . . 22

13.3 Wave soldering. . . . . . . . . . . . . . . . . . . . . . . . 22

13.4 Manual soldering . . . . . . . . . . . . . . . . . . . . . . 23

13.5 Package related soldering information . . . . . . 23

14 Revision history. . . . . . . . . . . . . . . . . . . . . . . . 24

15 Data sheet status. . . . . . . . . . . . . . . . . . . . . . . 25

16 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

17 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

18 Licenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

19 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

20 Contact information . . . . . . . . . . . . . . . . . . . . 25

PNX2000

Audio video input processor

© Koninklijke Philips Electronics N.V. 2004.

Printed in Netherlands

All rights are reserved. Reprod uction in whole or in part is prohibited without the p rior

written consent of the copyright owner.

The information presented in this document does not form part of any quotation or

contract, is believed to be accurate and reliable and may be changed without notice. No

liability will be accepted by the publisher for any consequence of its use. Publication

thereof does not convey nor imply any license under patent- or other industrial or

intellectual property rights.

Date of release: 04 May 2004 Document order number: 9397 750 12066

Loading...

Loading...