Philips PDI1394L11BA Datasheet

INTEGRATED CIRCUITS

PDI1394L11

1394 AV link layer controller

Product specification 1997 Oct 21

Philips Semiconductors Product specification

PDI1394L1 11394 AV link layer controller

1.0 FEA TURES

•IEEE 1394–1995 Standard Link Layer Controller

•Hardware Support for the IEC61883 International Standard of

Digital Interface for Consumer Electronics

•Interface to any IEEE 1394–1995 Physical Layer Interface

•5V Tolerant I/Os

•Single 3.3V supply voltage

2.0 DESCRIPTION

The PDI1394L1 1, Philips Semiconductors 1394 Audio/V ideo (AV)

Link Layer Controller, is an IEEE 1394–1995 compliant link layer

controller featuring an embedded AV layer interface. The AV layer is

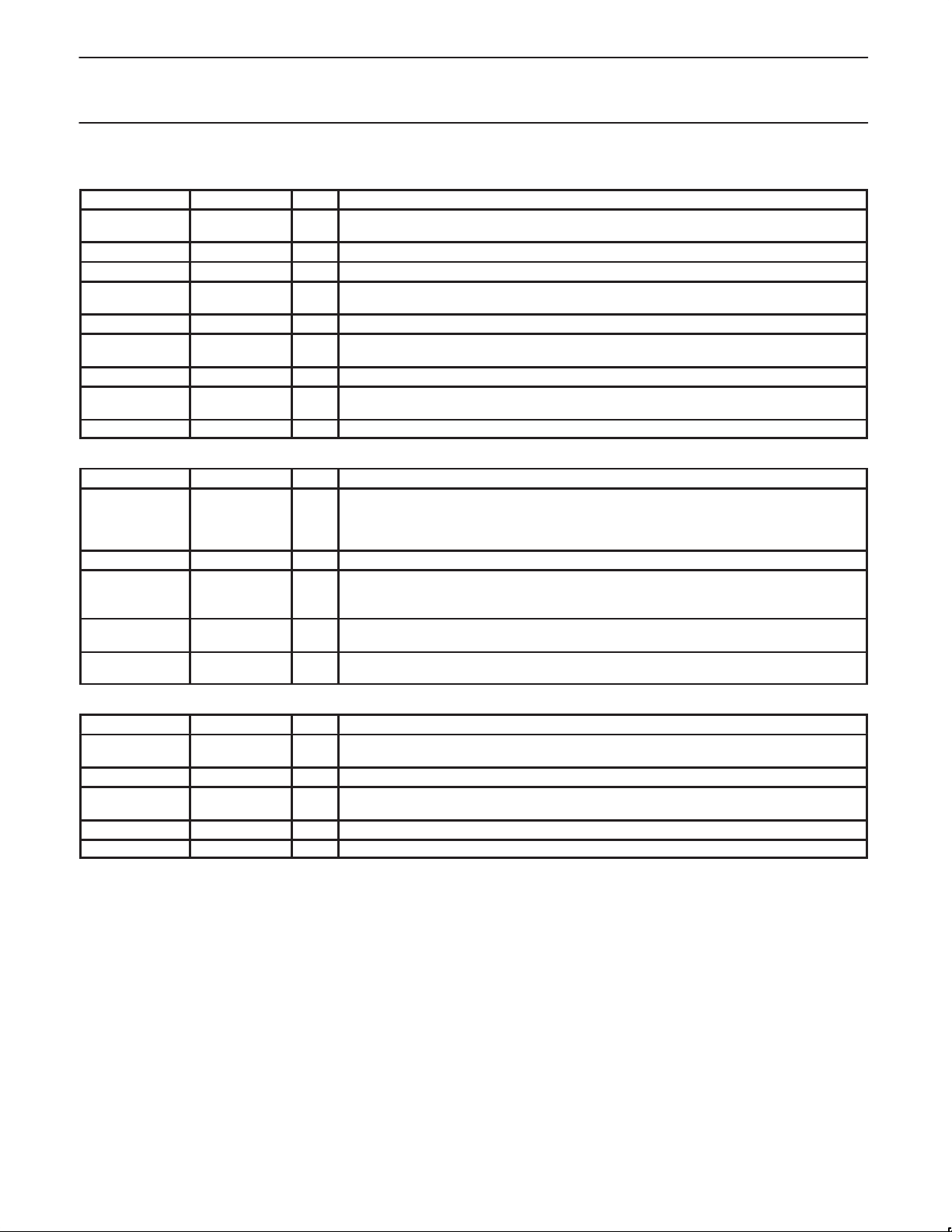

3.0 QUICK REFERENCE DAT A

GND = 0V; T

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNIT

V

DD

I

DD

SCLK Device clock 49.147 49.152 49.157 MHz

= 25°C

amb

Functional supply voltage range 3.0 3.3 3.6 V

Supply current @ VDD=3.3V 20 mA

designed to pack and un-pack application data packets for

transmission over an IEEE 1394 bus using isochronous data

transfers.

The application data is packetized according to the IEC 61883

International Standard of Digital Interface for Consumer Electronic

Audio/Video Equipment. The AV layer interface is a byte-wide port

capable of accommodating various MPEG–2 and DVC codecs. An

80C51 compatible byte-wide host interface is provided for internal

register configuration as well as performing asynchronous data

transfers.

The PDI1394L11 is powered by a single 3.3V power supply and the

inputs and outputs are 5V tolerant. It is available in the PQFP80

package.

4.0 ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA PKG. DWG. #

80-pin plastic PQFP80 0°C to +70°C PDI1394L11 BA PDI1394L11 BA SOT318-2

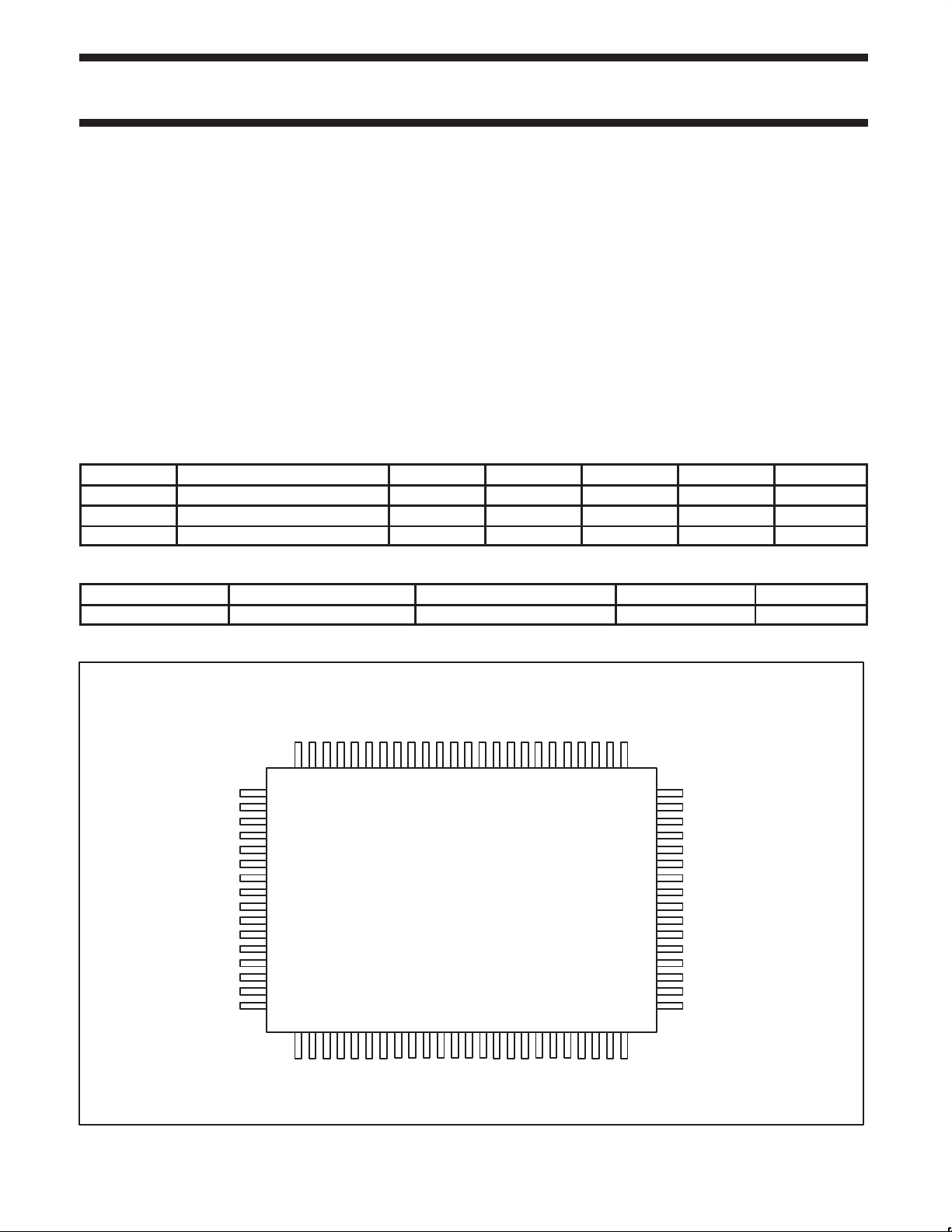

5.0 PIN CONFIGURATION

N/C

N/C

GND

VDD

63

62

RESERVED PHY D3

RESERVED

RESERVED

AV D0

AV D1

AV D2

AV D3

VDD

GND

AV D4

AV D5

AV D6

AV D7

VDD_

GND

N/C

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

2

3

1

AVFSYNCIN

AVVALID

AVFSYNCOUT

61

59

60

4

6

5

AVCLK

58

7

LREQ

SCLK

AVENDPCK

AVSYNC

55

54

56

57

PDI1394L11

AV LINK LAYER CONTROLLER

9

8

11

10

AVERR0

AVERR1

53

12

GND

VDD

515052

49

141513

16

PHY CTL0

ISO_N

47

48

18

17

PHY CTL1

46

VDD

45

202119

GND

44

PHY D0

43

222423

PHY D1

42

PHY D2

41

40

VDD

39

38

GND

37

PHY D4

PHY D5

36

PHY D6

35

PHY D7

34

CYCLEOUT

33

32

VDD

31

GND

30

CYCLEIN

29

RESET_N

28

HIF INT _N

HIF RD_N

27

26

HIF WR_N

HIF CS_N

25

HIF D6

HIF D7

HIF D5

HIF D4

HIF D2

HIF D3

HIF D1

VDD

GND

1997 Oct 21 853-2038 18592

HIF D0

CLK 25

GND

VDD

2

HIF A8

HIF A7

HIF A6

HIF A5

HIF A4

HIF A3

HIF A2

HIF A1

HIF A0

GND

VDD

SV00270

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

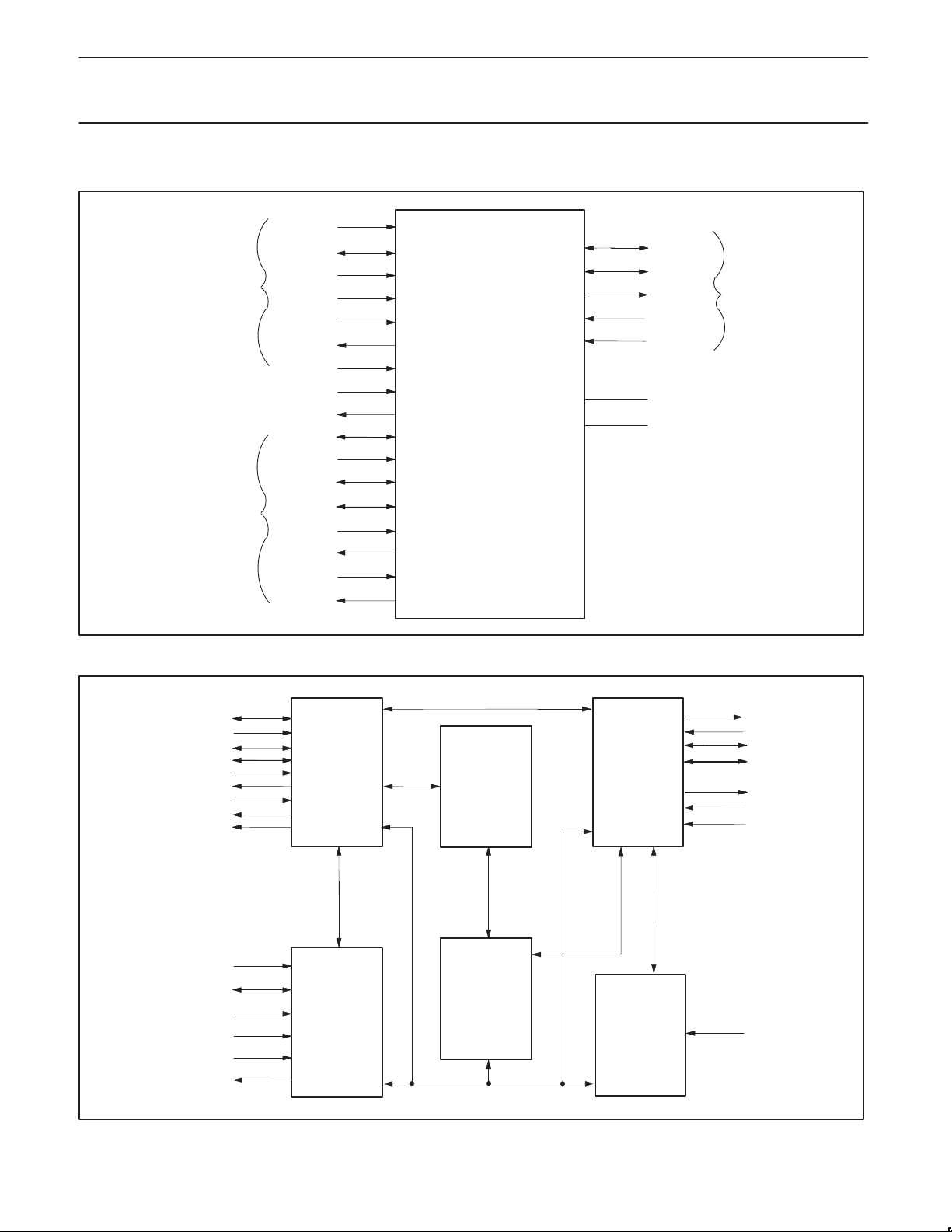

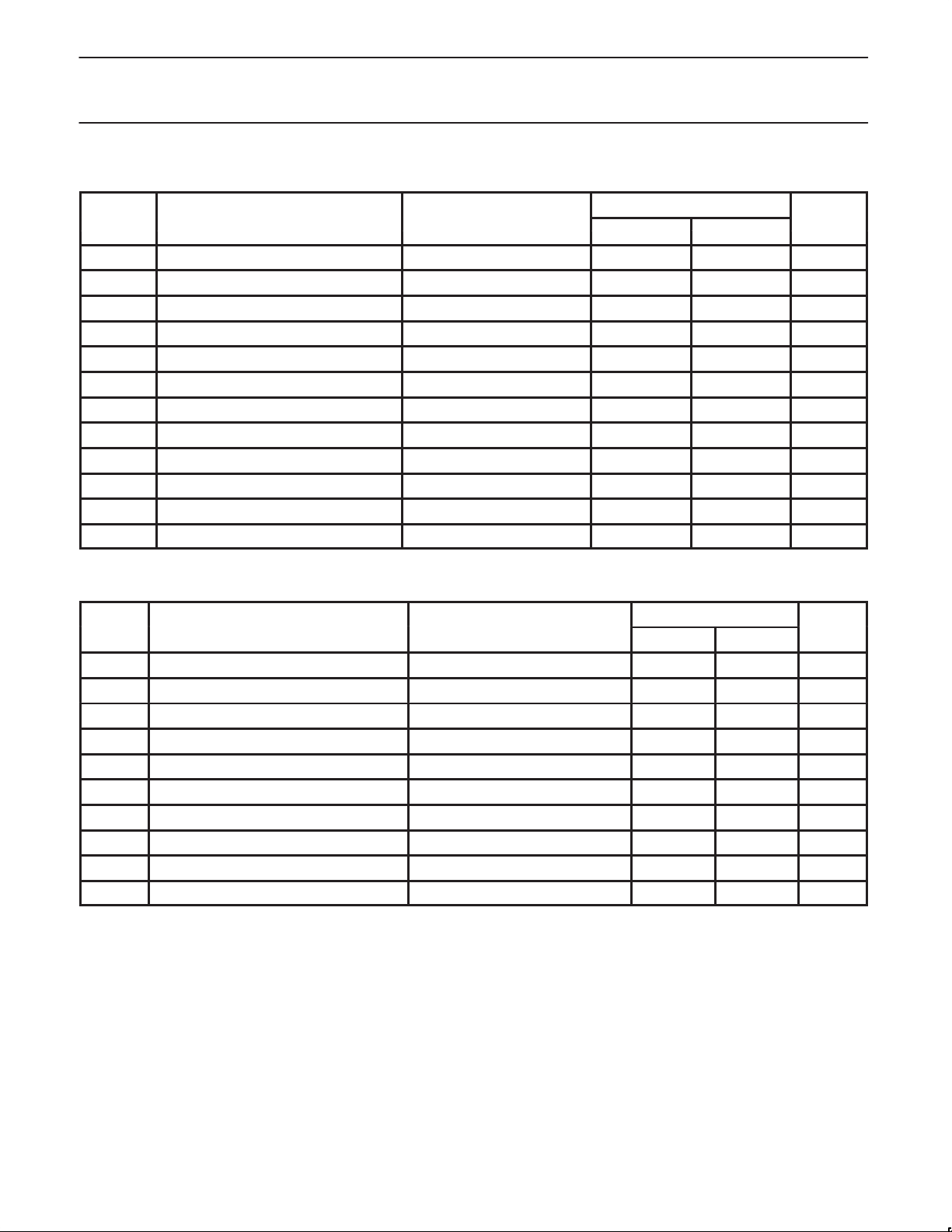

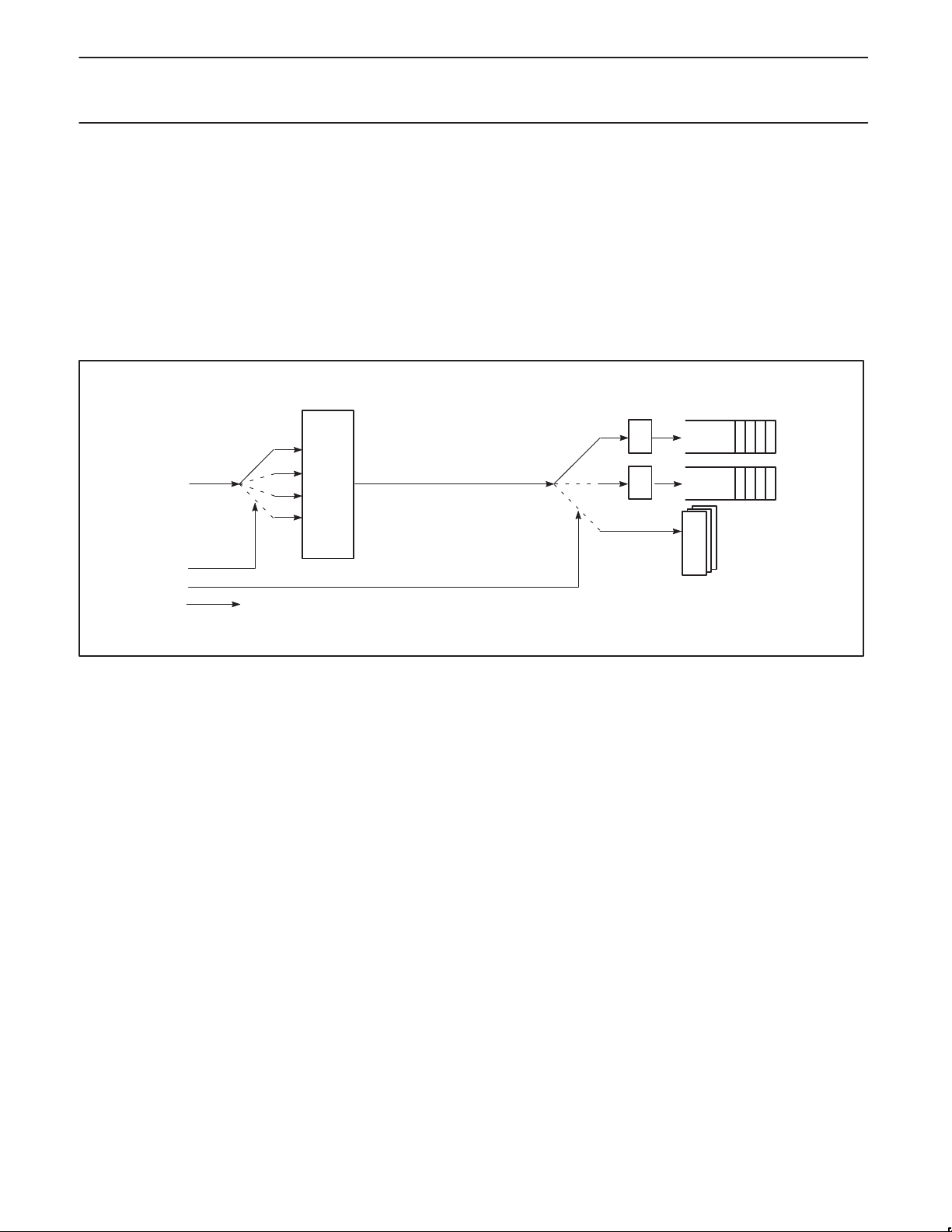

6.0 FUNCTIONAL DIAGRAM

HIF A[8:0]

PHY D[0:7]

PHY CTL[0:1]

LREQ

ISO_N

SCLK

VDD

GND

PHY

HOST

AV LAYER

AVFSYNCOUT

HIF D[7:0]

HIF WR_N

HIF RD_N

HIF CS_N

HIF INT_N

RESET_N

CYCLEIN

CYCLEOUT

AV D[7:0]

AVCLK

AVVALID

AVSYNC

AVFSYNCIN

AVENDPCK

AVERR[1:0]

PDI1394L11

IEEE 1394

AV LINK LAYER CONTROLLER

7.0 INTERNAL BLOCK DIAGRAM

AV D[7:0]

AVCLK

AVSYNC

AVVALID

AFSYNCIN

AVFSYNCOUT

AVENDPCK

AVERR1

AVERR0

HIF A[8:0]

HIF D[7:0]

HIF WR_N

HIF RD_N

HIF CS_N

HIF INT_N

AV LAYER

TRANSMITTER

RECEIVER

INTERFACE

AND

8-BIT

5KB BUFFER

MEMORY

(ISOCH & ASYNC

PACKETS)

ASYNC

TRANSMITTER

AND

RECEIVER

LINK CORE

CONTROL

AND

STATUS

REGISTERS

SV00267

CYCLEOUT

CYCLEIN

PHY D[0:7]

PHY CTL[0:1]

LREQ

ISO_N

SCLK

RESET_N

1997 Oct 21

SV00269

3

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

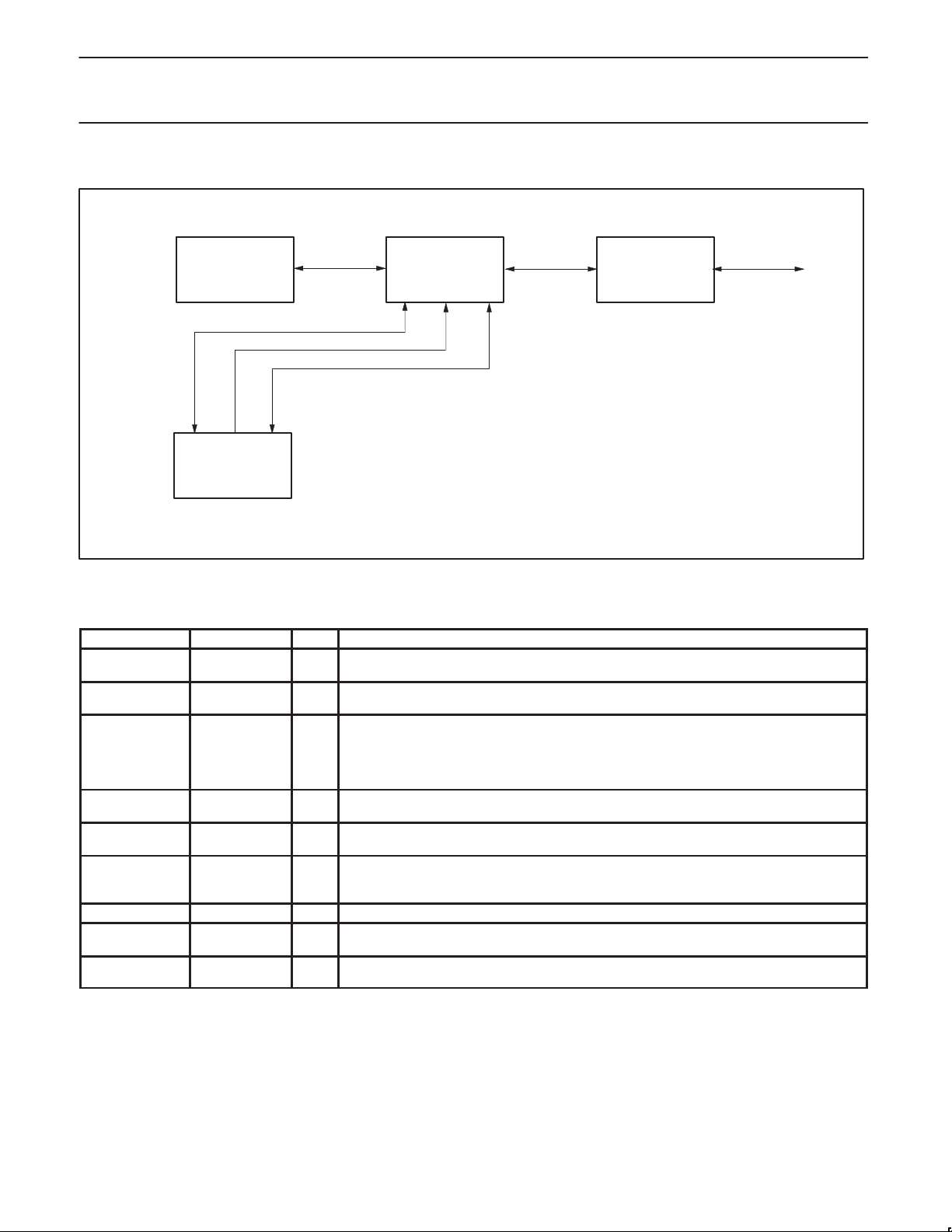

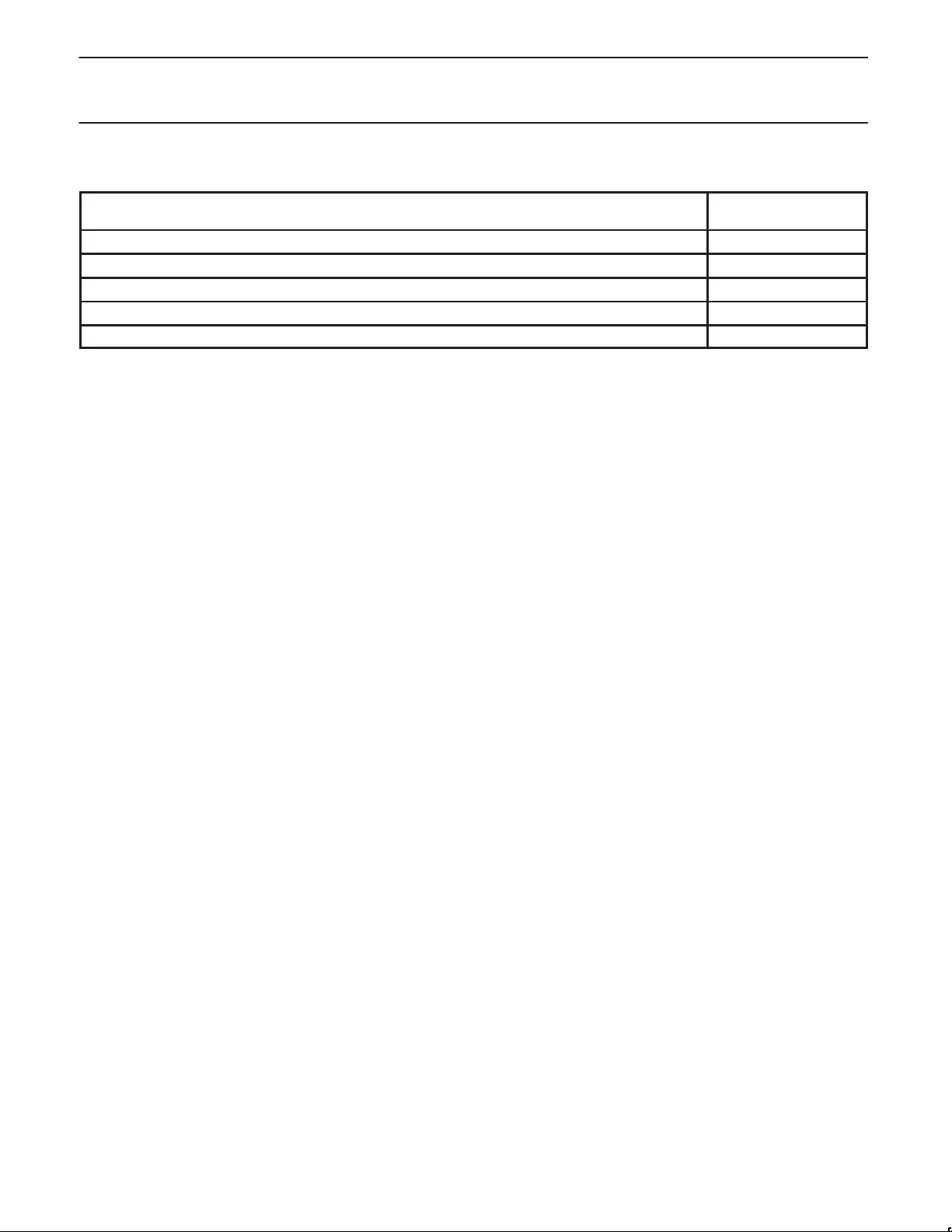

8.0 APPLICATION DIAGRAM

MPEG OR DVC

DECODER

HOST CONTROLLER

AV

INTERFACE

DATA 8/

ADDRESS 9/

INTERRUPT & CONTROL

PDI1394L11

AV LINK

PHY–LINK

INTERFACE

9.0 PIN DESCRIPTION

9.1 Host Interface

PIN No. PIN SYMBOL I/O NAME AND FUNCTION

14, 15, 16, 17,

18, 19, 20, 21, 22

1, 2, 3, 4, 7, 8, 9,

10

HIF A[8:0] I

HIF D[7:0] I/O Host Interface Data 7 (MSB) through 0. Byte wide data path to internal registers.

26 HIF WR_N I

27 HIF RD_N I

25 HIF CS_N I

28 HIF INT_N O

29 RESET_N I Reset (active LOW). The asynchronous master reset to the PDI1394L11.

6, 13, 24, 32, 39,

45, 49, 64, 72, 78

5, 12, 23, 31, 38,

44, 50, 63, 73, 79

V

DD

GND Ground reference

Host Interface Address 0 through 8. Provides the host with a byte wide interface to internal

registers. See description of Host Interface for addressing rules.

Write enable. When asserted (LOW) in conjunction with HIF CS_N, a write to the PDI1394L1 1

internal registers is requested. (NOTE: HIF WR_N and HIF RD_N : if these are both LOW in

conjunction with HIF CS_N, then a write cycle takes place. This can be used to connect

CPUs that use R/W_N line rather than separate RD_N and WR_N lines. In that case, connect

the R/W_N line to the HIF WR_N and tie HIF RD_N LOW.)

Read enable. When asserted (LOW) in conjunction with HIF CS_N, a read of the PDI1394L11

internal registers is requested.

Chip Select (active LOW). Host bus control signal to enable access to the FIFO and control

and status registers.

Interrupt (active LOW). Indicates a interrupt internal to the PDI1394L11. Read the General

Interrupt Register for more information. This pin is open drained and requires a 1K pullup

resistor.

3.3V ± 0.3V power supply

PDI1394P11

PHY

1394 CABLE

INTERFACE

SV00268

1997 Oct 21

4

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

9.2 AV Interface

PIN No. PIN SYMBOL I/O NAME AND FUNCTION

77, 76, 75, 74,

71, 70, 69, 68

58 AVCLK I External application clock. Rising edge active.

57 AVSYNC I/O Start of packet indicator; should only be used when AVVALID is active.

59 AVFSYNCIN I

60 AVFSYNCOUT O Frame sync output. Signal is derived from SYT field of IRXHQ2.

56 AVENDPCK I

61 AVVALID I/O Indicates data on AV D [7:0] is valid

53 AVERR0 O

52 AVERR1 O Sequence Error. Indicates at least one source packet was lost before the current AV D [7:0]

9.3 Phy Interface

PIN No. PIN SYMBOL I/O NAME AND FUNCTION

34, 35, 36, 37,

40, 41, 42, 43

46, 47 PHY CTL[0:1] I/O Control Lines between Link and Phy . See 1394 Specification for more information.

48 ISO_N I

54 LREQ O

55 SCLK I

AV D[7:0] I/O Audio/Video Data 7 (MSB) through 0. Byte-wide interface to the AV layer.

Frame sync input. Used for Digital Video (DV). The signal is time stamped and transmitted in

the SYT field of ITXHQ2.

End of application packet indication from data source. Required only if input packet is not

multiple of 4 bytes. It can be tied LOW for data packets that are 4*N in size.

CRC error, indicates bus packet containing AV D [7:0] had a CRC error, the current AV packet

is unreliable.

Data 0 (MSB) through 7 (NOTE: To preserve compatibility to the specified Link-Phy interface

PHY D[0:7] I/O

of the IEEE 1394–1995 standard, Annex J, bit 0 is the most significant bit). Data is expected

on AV D[0:1] for 100Mb/s, AV D[0:3] for 200Mb/s, and AV D[0:7] for 400Mb/s. See IEEE

1394–1995 standard, Annex J for more information.

Isolation barrier. This terminal is asserted (LOW) when an isolation barrier is present. See

IEEE 1394–1995 standard, Annex J for more information (used to request arbitration or

read/write PHY registers).

Link Request. Bus request to access the PHY. See IEEE 1394–1995 standard, Annex J for

more information.

System clock. 49.152MHz input from the PHY (the PHY -LINK interface operates at this

frequency).

9.4 Other Pins

PIN No. PIN SYMBOL I/O NAME AND FUNCTION

65, 66, 67 RESER VED NA

51, 62, 80 N/C NA These are test mode pins and should not be connected or terminated.

30 CYCLEIN I

33 CYCLEOUT O Reproduces the 8kHz cycle clock of the cycle master.

11 CLK 25 O Auxiliary clock, value is SCLK/2 (usually 24.576 MHz)

These pins are reserved for factory testing. For normal operation they should be connected to

ground.

Provides the capability to supply an external cycle timer signal for the beginning of 1394 bus

cycles.

1997 Oct 21

5

Philips Semiconductors Product specification

SYMBOL

PARAMETER

CONDITIONS

UNIT

MIN.MAX

SYMBOL

PARAMETER

CONDITIONS

UNIT

PDI1394L111394 AV link layer controller

10.0 RECOMMENDED OPERATING CONDITIONS

LIMITS

.

V

CC

V

V

V

I

OH

I

OL

dT/dV Input transition rise or fall time 0 20 ns/V

T

amb

SCLK System clock 49.147 49.157 MHz

AVCLK AV interface clock 0 24 MHz

t

t

DC supply voltage 3.0 3.6 V

Input voltage 0 5 V

I

High-level input voltage 2.0 V

IH

Low-level input voltage 0.8 V

IL

High-level output current 8 mA

Low-level output current –8 mA

Operating ambient temperature range 0 +70 °C

Input rise time 10 ns

r

input fall time 10 ns

f

11.0 ABSOLUTE MAXIMUM RATINGS

1, 2

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to GND (ground = 0V)

LIMITS

MIN MAX

I

GND

V

T

I

I

V

I

T

amb

P

DC supply voltage –0.5 +4.6 V

DD

DC input diode current – –50 mA

IK

V

DC input voltage –0.5 +5.5 V

I

DC output diode current – ±50 mA

OK

DC output voltage –0.5 VDD +0.5 V

O

DC output source or sink current – ±50 mA

O

, ICCDC VCC or GND current – ±150 mA

Storage temperature range –60 150 °C

stg

Operating ambient temperature 0 70 °C

Power dissipation per package 0.6 W

tot

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

1997 Oct 21

6

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

11.1 Buffer Memory Sizes

BUFFER MEMORY

Asynchronous Receive Transaction Response FIFO 64

Asynchronous Receive Transaction Request FIFO 64

Asynchronous Transmit Transaction Response FIFO 64

Asynchronous Transmit Transaction Request FIFO 64

AV Transmit/Receive Buffer 1024

12.0 FUNCTIONAL DESCRIPTION

12.1 Overview

The PDI1394L1 1 is an IEEE 1394–1995 compliant link layer

controller. It provides a direct interface between a 1394 bus and

various MPEG–2 and DVC codecs. Via this interface, the AV Link

maps and unmaps these AV datastreams from these codecs onto

1394 isochronous bus packets. The AV Link also provides an 8051

compatible microcontroller interface for an attached host controller.

Through the host interface port, the host controller can configure the

AV layer for transmission or reception of AV datastreams. The host

interface port also allows the host controller to transmit and receive

1394 asynchronous data packets.

12.2 AV interface and AV layer

The AV interface and AV layer allow AV packets to be transmitted

from one node to another. The AV transmitter and receiver within the

AV layer perform all the functions required to pack and unpack AV

packet data for transfer over a 1394 network. Once the AV layer is

properly configured for operation, no further host controller service

should be required. The operation of the AV layer is half-duplex, i.e.,

the AV layer can either receive or transmit AV packets at a particular

time.

12.2.1 The AV Interface

The AV Link provides an 8 bit data path to the AV layer. The 8 bit

data path is designed with associated clock and control signals to be

compatible with various MPEG–2 and DVC codecs.

The AV interface port buf fer, if so programmed, can time stamp

incoming AV packets. The AV packet data is stored in the embedded

memory buffer , along with its time stamp information. After the AV

packet has been written into the AV layer, the AV layer creates an

isochronous bus packet with the appropriate CIP header. The bus

packet along with the CIP header is transferred over the appropriate

isochronous channel/packet. The size and configuration of

isochronous data packet payload transmitted is determined by the

AV layer’s configuration registers accessible through the host

interface.

The AV interface port waits for the assertion for AVVALID and

AVSYNC. Note: Do not assert AVSYNC without AVVALID.

AVSYNC is aligned with the rising edge of AVCLK and the first byte

of data on AVDATA[7:0]. The duration of AVSYNC is one AVCLK

cycle. AVSYNC signals the AV layer that the transfer of an AV

packet has begun. At the time the AVSYNC is asserted, the AV layer

creates a new time stamp in the buffer memory. (This only happens

if so configured. The DVC format does not require these time

stamps). The time stamp is then transmitted as part of the standard

packet header. This allows the AV receiver to provide the AV packet

for output at the appropriate time.

When the DV video is enabled (via the format code of the CIP

header), the frame synchronization signal AVFSYNCIN is time

stamped and placed in the SYT field. The timestamp value is 3 cycle

times (duration of 125ms) in the future and is transmitted in the SYT

field of the current CIP header. On the receiver side, when the SYT

stamp matches the cycle timer register, a pulse is generated on the

AVFSYNCOUT output. The timing for AVFSYNCIN and

AVFSYNCOUT are independent of AV clock.

12.2.2 IEC 61883 International Standard

The PDI1394L1 1 is specifically designed to support the proposed

IEC61883 International Standard of Digital Interface for Consumer

Electronic Audio/Video Equipment. The IEC specification defines a

scheme for mapping various types of AV datastreams onto 1394

isochronous data packets. The standard also defines a software

protocol for managing isochronous connections in a 1394 bus called

Connection Management Protocol (CMP). It also provides a

framework for transfer of functional commands, called Function

Control Protocol (FCP).

12.2.3 CIP Headers

A feature of the IEC61883 International Standard is the definition of

Common Isochronous Packet (CIP) headers. These CIP headers

contain information about the source and type of datastream

mapped onto the isochronous packets.

The AV Layer supports the use of CIP headers. CIP headers are

added to transmitted isochronous data packets at the AV data

source. When receiving isochronous data packets, the AV layer

automatically analyzes their CIP headers. The analysis of the CIP

headers determines the method the AV layer uses to unpack the AV

data from the isochronous data packets.

The information contained in the CIP headers is accessible via

registers in the host interface.

(See IEC61883 International Standard of Digital Interface for

Consumer Electronic Audio/Video Equipment for more details on

CIP headers).

12.3 The host interface

The host interface allows an 8 bit CPU to access all registers and

the asynchronous packet queues. It is specifically designed for an

8051 microcontroller but can also be used with other CPUs. There

are 64 register addresses (for quadlet wide registers). To access

SIZE

(Quadlets)

1997 Oct 21

7

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

bytes rather than quadlets the address spaces is 256 bytes,

requiring 8 address lines.

The use of an 8 bit interface introduces an inherent problem that

must be solved: register fields can be more than 8 bits wide and be

used (control) or changed (status) at every internal clock tick. If such

a field is accessed through an 8 bit interface it requires more than

one read or write cycle, and the value should not change in between

to maintain consistency . To overcome this problem accesses to the

chip’s internal register space are always 32 bits, and the host

interface must act as a converter between the internal 32 bit

accesses and external 8 bit accesses. This is where the shadow

registers come in.

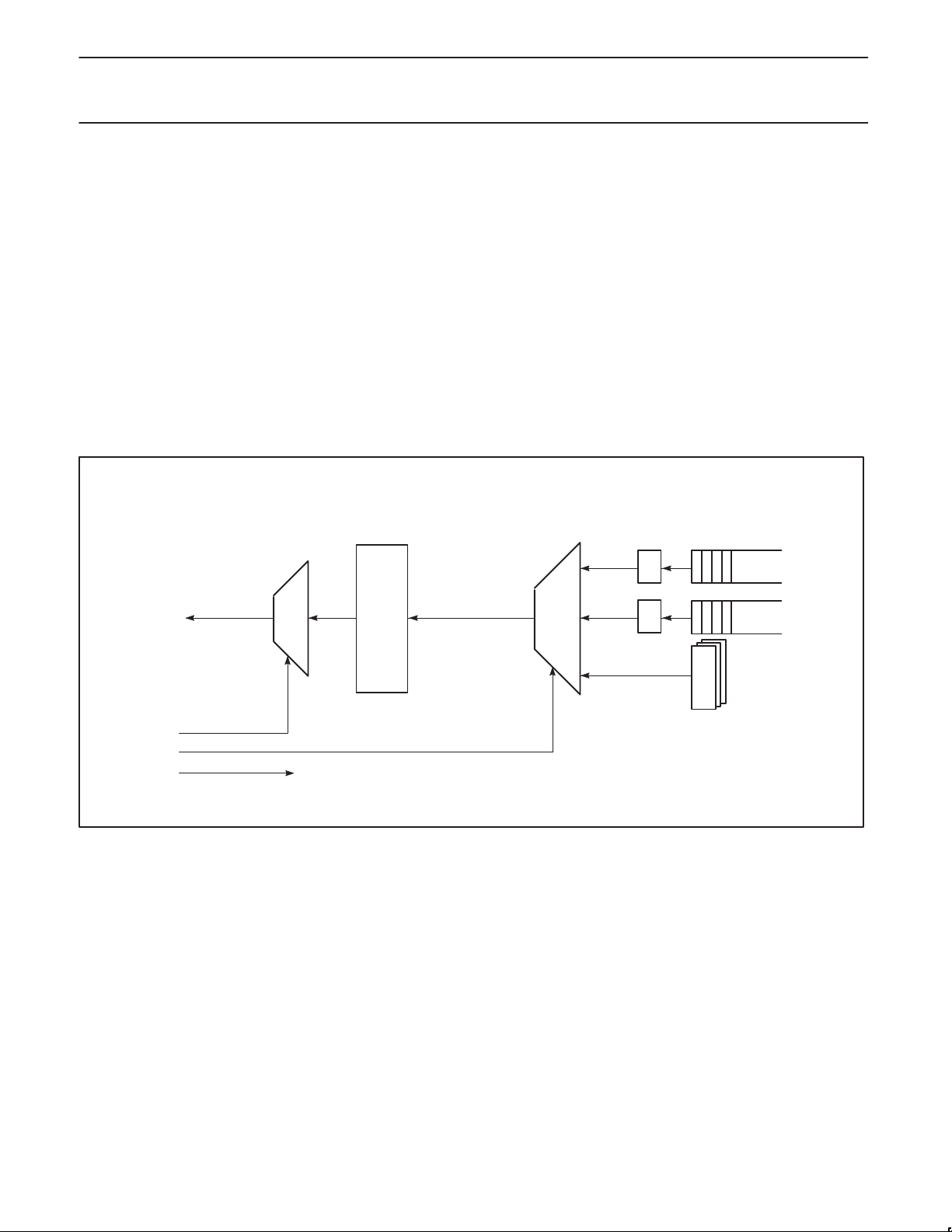

12.3.1 Read accesses

To read an internal register the host interface can make a snapshot

(copy) of that specific register which is then made available to the

CPU 8 bits at a time. The register that holds the snapshot copy of

the real register value inside the host interface is called the read

MUX MUX

CPU

832 32

shadow register. During a read cycle address lines HIF A0 and

HIF A1 are used to select which of the 4 bytes currently stored in the

read shadow register is output onto the CPU data bus. This

selection is done by combinatorial logic only, enabling external

hardware to toggle these lines through values 0 to 3 while keeping

the chip in a read access mode to get all 4 bytes out very fast (in a

single extended read cycle), for example into an external quadlet

register.

This solution requires a control line to direct the host interface to

make a snapshot of an internal register when needed, as well as the

internal address of the target register. The register address is

connected to input address lines HIF A2..HIF A7, and the update

control line to input address line HIF A8. To let the host interface

take a new snapshot the target address must be presented on

HIF A2..HIF A7 and HIF A8 must be raised while executing a read

access. The new value will be stored in the read shadow register

and the selected byte (HIF A0, HIF A1) appears on the output.

TR

Q

Q

REGISTERS

SV00803

HIF A0..1

HIF A2..7

HIF A8

READ SHADOW REGISTER

UPDATE/COPY CONTROL

32

NOTES:

1. It is not required to read all 4 bytes of a register before reading another register. For example, if only byte 2 of register 0x54 is required a

read of byte address 0x100 + (0×54) + 2 = 0x156 is sufficient.

2. The update control line does not necessarily have to be connected to the CPU address line HIF A8. This input could also be controlled by

other means, for example a combinatorial circuit that activates the update control line whenever a read access is done for byte 0. This

makes the internal updating automatic for quadlet reading.

3. Reading the bytes of the read shadow register can be done in any order and as often as needed.

1997 Oct 21

8

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

12.3.2 Write accesses

To write to an internal register the host interface must collect the 4

byte values into a 32 bit value and then write the result to the target

register in a single clock tick. This requires a register to hold the 32

bit value being compiled until it is ready to be written to the actual

target register. This temporary register inside the host interface is

called the write shadow register. During all write cycles address

lines HIF A0 and HIF A1 are used to select which of the 4 bytes of

the write shadow register is to be written with the value on the

CPU data bus. Only one byte can be written in a single write access

cycle.

MUX

CPU

HIF A0..1

HIF A2..7

HIF A8

832

WRITE SHADOW REGISTER

UPDATE/COPY CONTROL

This solution requires a control line to direct the host interface to

copy the write shadow register to the actual destination register

when ready, as well as the internal address of that register. The

destination register address is connected to input address lines

HIF A2..HIF A7, and the update control line to input address line

HIF A8. To let the host interface make the internal transfer the target

address must be presented on HIF A2..HIF A7 and HIF A8 must be

raised while executing a write access. The current value on the CPU

data bus will be stored in the write shadow register at the selected

byte (HIF A0, HIF A1) and the result will be copied into the specified

destination register.

TR

MUX

Q

Q

REGISTERS

32

SV00804

NOTES:

1. It is not required to write all 4 bytes of a register: those bytes that are either reserved (undefined) or don’t care do not have to be written in

which case they will be assigned the value that was left in the corresponding byte of the write shadow register from a previous write

access. For example, to acknowledge an interrupt for the isochronous receiver (external address 0x04C), a single byte write to location

0x100+(0x4C)+3 = 0x14F is sufficient. The value 256 represents setting HIF A8=1. The host interface cannot directly access the FIFOs, but

instead reads from/writes into a transfer register (shown as TR in the Figures above). Data is moved between FIFO and TR by internal logic

as soon as possible without CPU intervention.

2. The update control line does not necessarily have to be connected to the CPU address line HIF A8. This input could also be controlled by

other means, for example a combinatorial circuit that activates the update control line whenever a write access is done for byte 3. This

makes the internal updating automatic for quadlet writing.

3. Writing the bytes of the read shadow register can be done in any order and as often as needed (new writes simply overwrite the old value).

1997 Oct 21

9

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

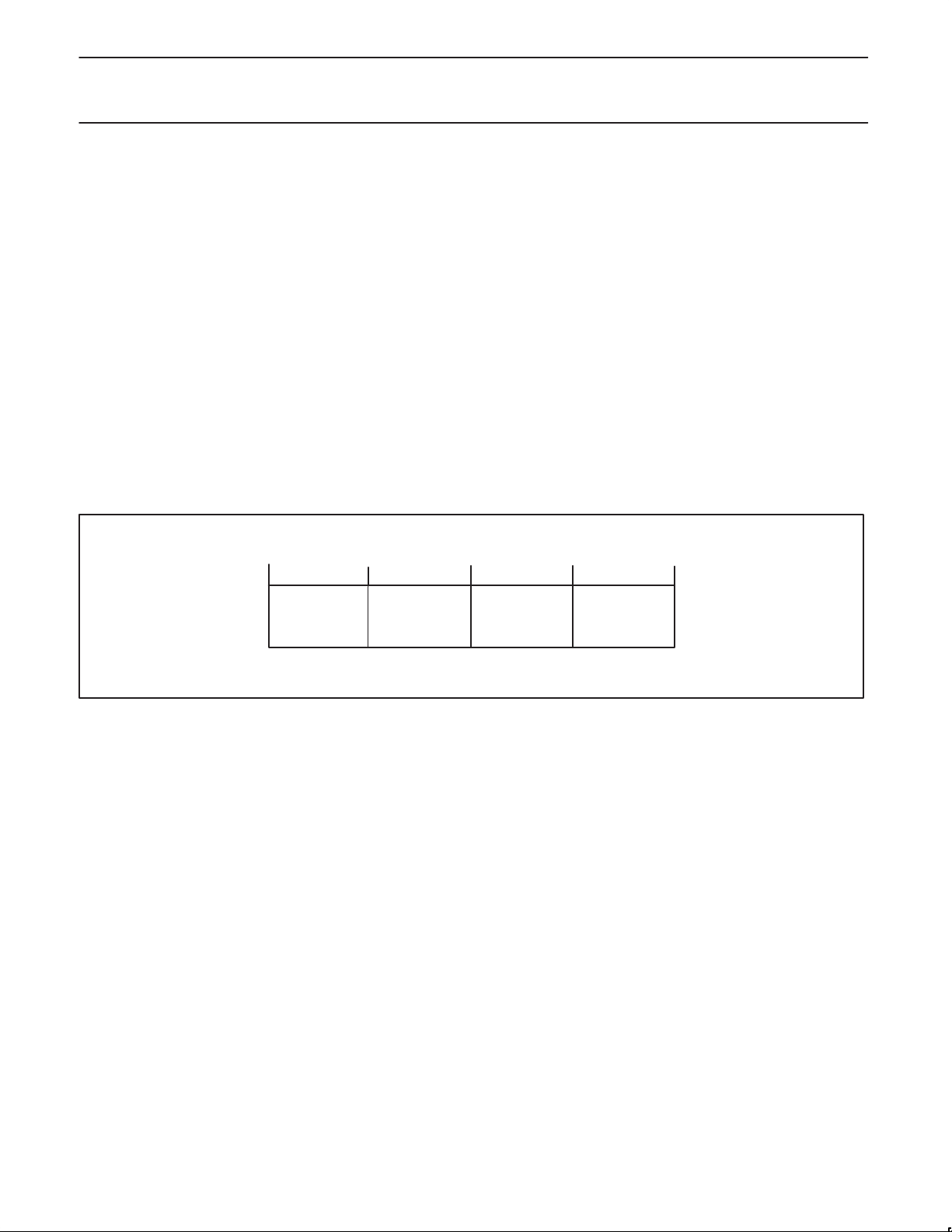

12.3.3 Byte order

The bytes in each quadlet are numbered 0..3 from left (most

significant) to right (least significant) as shown in Figure 1.

To access a register at internal address N the CPU should use

addresses E:

E = 4 N ; to access the upper 8 bits of the register.

E = 4 N + 1 ; to access the upper middle 8 bits of the register.

E = 4 N + 2 ; to access the lower middle 8 bits of the register.

E = 4 N + 3 ; to access the lower 8 bits of the register.

12.3.4 Accessing the packet queues

Although entire incoming packets are stored in the receiver buffer

memory they are not randomly accessible. These buffers act like

fifos and only the frontmost (oldest) data quadlet entry is accessible

for reading. Therefore only one location (register address) is

allocated to each of the two receiver queues. Reading this location

returns the head entry of the queue, and at the same time removes

it from the queue, making the next stored data quadlet accessible.

With the current host interface such a read is in fact a move

operation of the data quadlet from the queue to the read shadow

3130

29 28 27 2625 24 23 22 2120 19 18 1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

BYTE 0 BYTE 1

register. Once the data is copied into the read shadow register it is

no longer available in the queue itself so the CPU should always

read all 4 bytes before attempting any other read access (be careful

with interrupt handlers for AVLink!).

A similar argument applies to the transmitter queues. Data cannot

be written arbitrarily , but only to the next available free location.

Since the transmitter needs to know when the packet is complete

(all data stored in memory, so that it may start the arbitration

process on the 1394 bus) two separate register locations are

reserved per transmitter queue: one to write all but the last packet

quadlet to, and one to write the last quadlet of every packet to.

Writing to any of these register locations stores the data in the

queue and makes the next memory location accessible for writing.

NOTE:

1. Because of the way it is implemented memory access is not

always immediate; consequently it may take some time before

the next data quadlet in the queue is accessible after reading or

writing the current one. Status flags are provided to the CPU to

indicate availability.

BYTE 2

BYTE 3

Figure 1. Byte order in quadlets as implemented in the host interface

12.3.5 The CPU bus interface signals

The CPU interface is directly compatible with an 8051

microcontroller. It uses a separate HIF RD_N and HIF WR_N inputs

and a HIF CS_N chip select line, all of which are active LOW. There

are 9 address inputs (HIF A0..HIF A8) and 8 data in/out lines

HIF D0..HIF D7. An open drain HIF INT_N output is used to signal

interrupts to the CPU.

The CPU is not required to run at a clock that is synchronous to the

1394 base clock. The control signals will be resampled by the host

interface before being used internally.

An access through the host interface starts when HIF CS_N = 0 and

either HIF WR_N = 0 or HIF RD_N = 0. Typically the chip select

signal is derived from the upper address lines of the CPU (address

decode stage), but it could also be connected to a port pin of the

CPU to avoid the need for an external address decoder in very

simple CPU systems. When both HIF CS_N = 0 and HIF RD_N = 0

the host interface will start a read access cycle, so the cycle is

triggered at the falling edge of either HIF CS_N or HIF RD_N,

whichever is later.

SV00656

Very shortly after the start of the cycle, the selected byte in the read

shadow register will be output (indicated in Figure 2 as RSR

). If

O

HIF A8 is asserted then the target register value will be copied into

the read shadow register, leading to a new value RSR

later in the read cycle. If HIF A8 is LOW, then the read shadow

some time

n

register will not change.

A write access starts when the later of HIF CS_N and HIF WR_N

becomes LOW (see Figure 3). Data is written to the shadow

register, following which, if HIF A8 is asserted, the shadow register

value is copied to the addressed register.

NOTES:

1. The time between the end of any access and the start of the next

access must be at least t

which needs to be greater than

CH

(2 x SCLK).

2. When HIF A8 = 0 for either write or read access the address bits

HIF A2..HIF A7 are ignored.

3. If both HIF WR_N = 0 and HIF RD_N = 0 while HIF CS_N = 0,

then a write cycle takes place.

1997 Oct 21

10

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

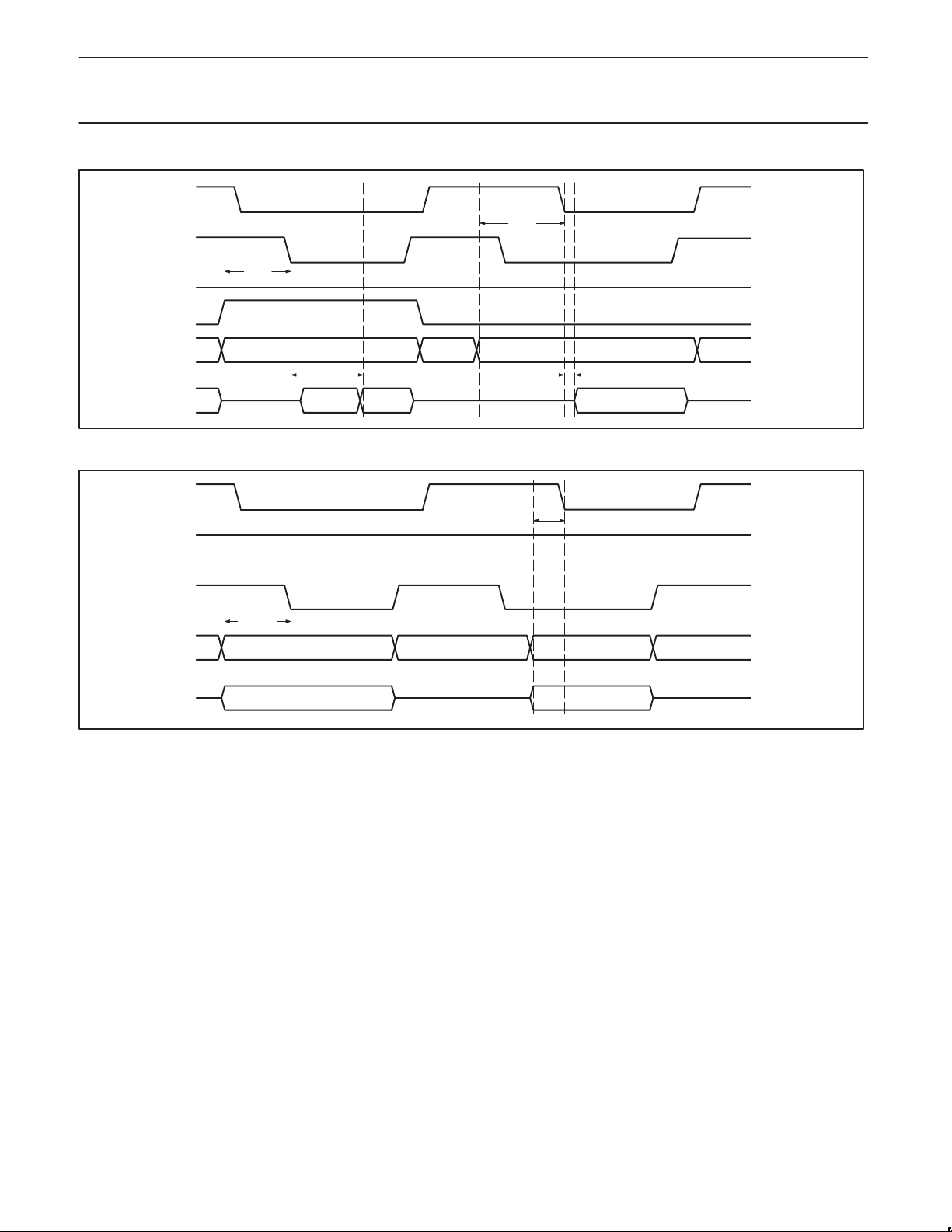

HIF CS_N

T

AS

HIF RD_N

T

HIF WR_N

HIF A8

HIF A0..HIF A7

HIF D0..HIF D7

AS

T

ACC

RSR

RSR

O

n

T

ACC

Figure 2. Read cycle signal timing (2 independent read cycles)

RSR

n

SV00686

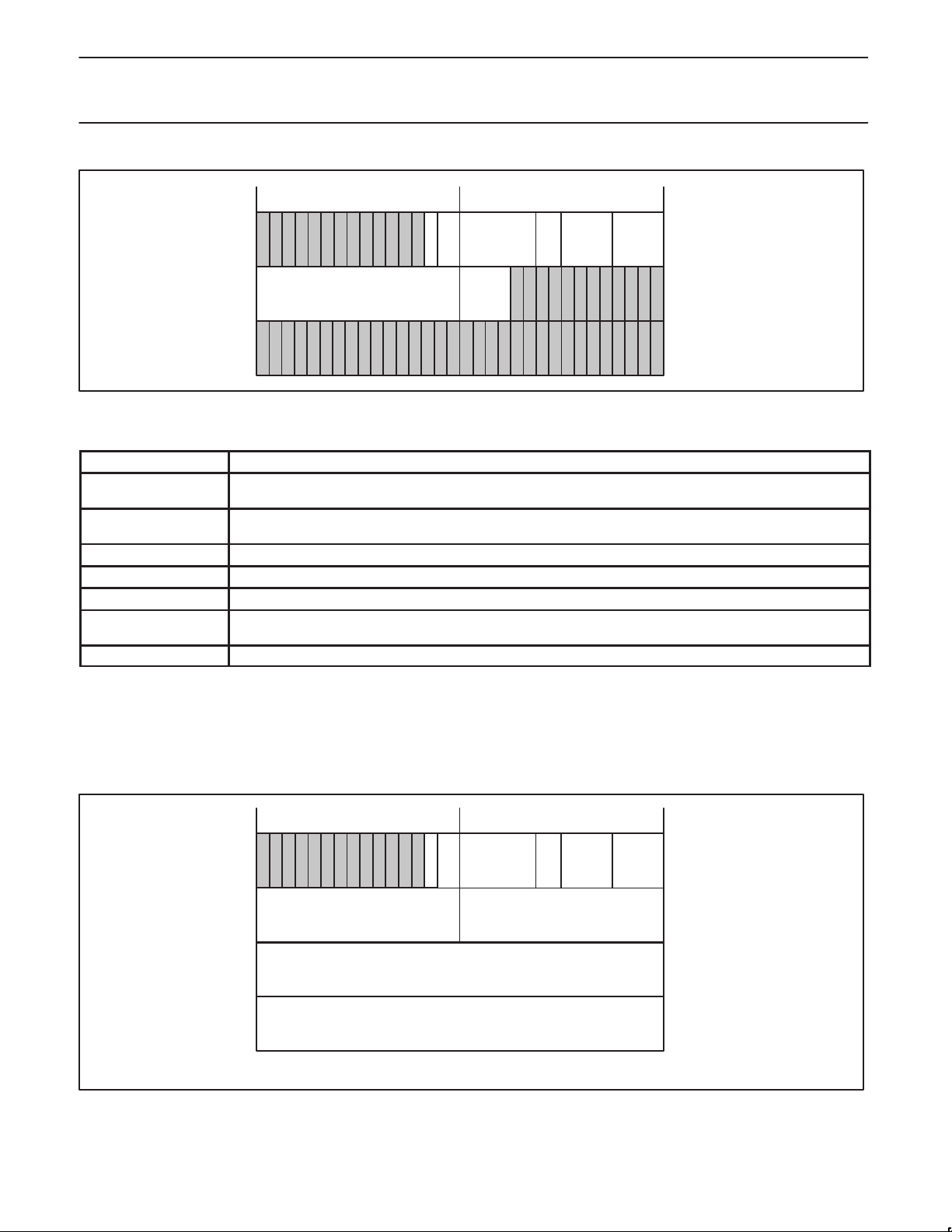

HIF CS_N

HIF RD_N

HIF WR_N

T

AS

HIF A0..HIF A8

HIF D0..HIF D7

<VALID ADDRESS> <VALID ADDRESS>

<WRITE DATA> <WRITE DATA>

Figure 3. Write cycle signal timing (2 independent write cycles)

12.4 The Asynchronous Packet Interface

The PDI1394L1 1 provides an interface to asynchronous data

packets through the registers in the host interface. The format of the

asynchronous packets is specified in the following sections.

12.4.1 Reading an Asynchronous Packet

Upon reception of a packet, the packet data is stored in the

appropriate receive FIFO, either the Request or Response FIFO.

The location of the packet is indicated by either the RREQQQAV or

RRSPQAV status bit being set in the Asynchronous Interrupt

Acknowledge (ASYINT ACK) register. The packet is transferred out

of the FIFO by successive reads of the Asynchronous Receive

Request (RREQ) or Asynchronous Receive Response (RRSP)

register. The end of the packet (the last quadlet) is indicated by

either the RREQQLASTQ or RRSPQLASTQ bit set in ASYINTACK.

Attempting to read the FIFO when either RREQQQAV bit or

RRSPQQAV bit is set to 0 (in the Asynchronous RX/TX interrupt

acknowledge (ASYINT ACK) register) will result in a queue read

error.

T

AS

SV00687

12.4.2 Writing an Asynchronous Packet

An asynchronous packet intended for transmission is first stored in

the appropriate Transmitter FIFO. Once writing to the FIFO is

complete, the link layer controller arbitrates for the bus to transmit

the packet.

To generate an asynchronous packet, the first and next to last

quadlets of the packet must be written to the Asynchronous

Transmit Request Next (TX_RQ_NEXT) register, for request type

packets, or the Asynchronous Transmit Response Next

(TX_RP_NEXT) register, for response type packets. The last

quadlet of the packet is written to the Asynchronous Transmit

Request Last (TX_RQ_LAST) register, for request type packets, or

the Asynchronous Transmit Response Last (TX_RP_LAST)

register, for response type packets. After writing the last quadlet,

the packet is automatically queued by the AVlink layer controller for

transmission over the bus.

1997 Oct 21

11

Philips Semiconductors Product specification

1

No-packet data

Block write requests

1

PDI1394L111394 AV link layer controller

12.5 Link Packet Data Formats

The data formats for transmission and reception of data are shown below. The transmit format describes the expected organization for data

presented to the link at the asynchronous transmit, physical response, or isochronous transmit FIFO interfaces.

12.5.1 Asynchronous Transmit Packet Formats

These sections describe the formats in which packets need to be delivered to the queues (FIFOs) for transmission. There are four basic formats

as follows:

TRANSACTION

ITEM

FORMAT USAGE

p

2 Quadlet packet

Quadlet read

requests

Quadlet/block write

responses

Qaudlet write

requests

Quadlet read

responses

Block read requests 5

CODE

(tCode)

4

2

0

6

3 Block Packet

Block read

responses

7

Lock requests 9

4

Unformatted

transmit

Lock responses B

Concatenated self-ID

/ PHY packets

hex

E

hex

Each packet format uses several fields (see names and descriptions below). More information about these fields (not the format) can be found

in the 1394 specification. Grey fields are reserved and should be set to zero values.

12.5.1.1 No-data Transmit

The no-data transmit formats are shown in Figures 4 and 5. The first quadlet contains packet control information. The second and third quadlets

contain 16-bit destination ID and either the 48-bit, quadlet aligned destination offset (for requests) or the response code (for responses).

31 30

29 28 27 2625 24 23 22 2120 19 18 1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0

spd tLabel rt tCode 0000

destinationID

destinationOffsetLow

destinationOffsetHigh

SV00250

Figure 4. Quadlet Read Request Transmit Format

1997 Oct 21

12

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

29 28 27 2625 24 23 22 2120 19 18 1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

3130

spd tLabel rt tCode 0000

0

destinationID

rCode

SV00249

Figure 5. Quadlet/Block Write Response Packet Transmit Format

Table 1. No-Data Transmit Format

Field Name Description

spd This field indicates the speed at which this packet is to be sent. 00=100 Mbs, 01=200 Mbs, and 10=400 Mbs.

tLabel This field is the transaction label, which is used to pair up a response packet with its corresponding request

rt The retry code for this packet. Supported values are: 00=retry1, and 01=retryX.

tCode The transaction code for this packet.

DestinationID Contains a node ID value.

DestinationOffsetHigh

DestinationOffsetLow

rCode Response code for write response packet.

12.5.1.2 Quadlet Transmit

Three quadlet transmit formats are shown below. In these figures: The first quadlet contains packet control information. The second and third

quadlets contain 16-bit destination ID and either the 48-bit quadlet-aligned destination offset (for requests) or the response code (for

responses).

The fourth quadlet contains the quadlet data for read response and write quadlet request formats, or the upper 16 bits contain the data length

for the block read request format.

11 = undefined

packet.

The concatenation of these two field addresses a quadlet in the destination node’s address space.

1997 Oct 21

29 28 27 2625 24 23 22 2120 19 18 1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

3130

spd tLabel rt tCode 0000

0

destinationID

destinationOffsetLow

quadlet data

destinationOffsetHigh

Figure 6. Quadlet Write Request T ransmit Format

13

SV00251

Philips Semiconductors Product specification

PDI1394L111394 AV link layer controller

29 28 27 2625 24 23 22 2120 19 18 1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

31 30

spd tLabel rt tCode 0000

0

destinationID

rCode

quadlet data

Figure 7. Quadlet Read Response Transmit Format

29 28 27 2625 24 23 22 2120 19 18 1716 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

31 30

spd tLabel rt tCode 0000

0

destinationID

destinationOffsetLow

data length

destinationOffsetHigh

SV00252

SV00253

Figure 8. Block Read Request Transmit Format

Table 2. Quadlet Transmit Fields

Field Name Description

spd, tLabel, rt, tCode, destinationID,

destinationOffsetHigh, destinationOffsetLow, rCode

Quadlet data For quadlet write requests and quadlet read responses, this field holds the data to

Data length The number of bytes requested in a block read request

1997 Oct 21

See Table 1.

be transferred

14

Loading...

Loading...