Philips pcx8582x DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

PCX8582X-2 Family

256 x 8-bit CMOS EEPROMS

with I

Product specification

Supersedes data of February 1992

File under Integrated Circuits, IC12

Philips Semiconductors

2

C-bus interface

December 1994

Philips Semiconductors Product specification

256 x 8-bit CMOS EEPROMS

with I

FEATURES

• Low power CMOS

– maximum active current 2.0 mA

– maximum standby current 10 µA (at 6.0 V),

• Non-volatile storage of 2-Kbits organized as 256 × 8-bits

• Single supply with full operation down to 2.5 V

• On-chip voltage multiplier

• Serial input/output I2C-bus

• Write operations

– byte write mode

– 8-byte page write mode

• Read operations

– sequential read

– random read

• Internal timer for writing (no external components)

• Power-on reset

• High reliability by using a redundant storage code

• Endurance

– >500 k E/W-cycles at T

• 40 years non-volatile data retention time (typ.)

• Pin and address compatible to

– PCX8570, PCF8571, PCF8572 and PCF8581

– PCX8494X-2, PCX8598X-2 -Family.

2

C-bus interface

typical 4 µA

(minimizes total write time per byte)

=22°C

amb

PCX8582X-2 Family

DESCRIPTION

The PCX8582X-2 is a 2-Kbit (256 × 8-bit) floating gate

electrically erasable programmable read only memory

(EEPROM). By using an internal redundant storage code

it is fault tolerant to single bit errors. This feature

dramatically increases reliability compared to conventional

EEPROM memories.

Power consumption is low due to the full CMOS

technology used. The programming voltage is generated

on-chip, using a voltage multiplier.

As data bytes are received and transmitted via the serial

I2C-bus, a package using eight pins is sufficient. Up to

eight PCX8582X-2 devices may be connected to the

I2C-bus. Chip select is accomplished by three address

inputs (A0, A1, A2).

Timing of the ERASE/WRITE cycle is carried out

internally, thus no external components are required. Pin 7

(PTC) must be connected to either VDD or left open-circuit.

There is an option of using an external clock for timing the

length of an ERASE/WRITE cycle.

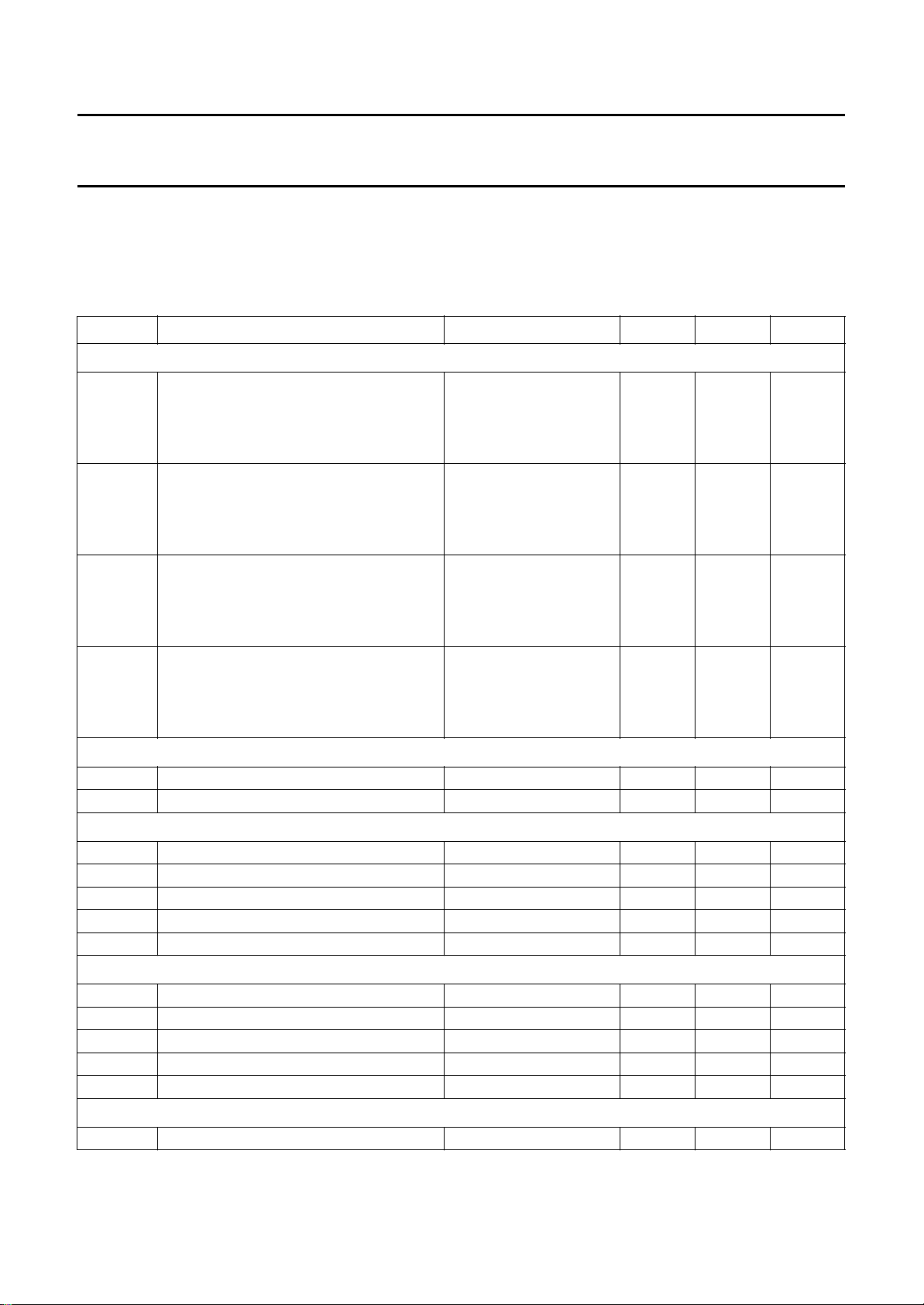

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

I

DDR

I

DDW

I

DDSB

supply voltage 2.5 6.0 V

supply current READ f

supply current ERASE/WRITE f

= 100 kHz

SCL

=3V − 60 µA

V

DD

=6V − 200 µA

V

DD

= 100 kHz

SCL

=3V − 0.6 mA

V

DD

=6V − 2.0 mA

V

DD

supply current STANDBY VDD=3V − 3.5 µA

VDD=6V − 10 µA

December 1994 2

Philips Semiconductors Product specification

256 x 8-bit CMOS EEPROMS

with I

ORDERING INFORMATION

PCF8582C-2P DIP8 plastic dual in-line package;

PCD8582D-2P −25 +70 3.0 6.0

PCF8582E-2P −40 +85 4.5 5.5

PCA8582F-2P −40 +125 4.5 5.5

PCF8582C-2T SO8 plastic small outline

PCD8582D-2T −25 +70 3.0 6.0

PCF8582E-2T −40 +85 4.5 5.5

PCA8582F-2T −40 +125 4.5 5.5

DEVICE SELECTION

Table 1 Device selection code

SELECTION DEVICE CODE CHIP ENABLE R/

Bit b71 b6 b5 b4 b3 b2 b1 b0

Device 1 0 1 0 A2 A1 A0 R/W

2

C-bus interface

TYPE

NUMBER

P ACKAGE TEMPERA TURE (°C) SUPPLY (V)

NAME DESCRIPTION VERSION MIN. MAX. MIN. MAX.

SOT97-1 −40 +85 2.5 6.0

8 leads (300 mil)

SOT96-1 −40 +85 2.5 6.0

package;

8 leads; body width 3.9 mm

PCX8582X-2 Family

W

Note

1. The MSB b7 is sent first.

Table 2 Endurance and data retention guarantees

DEVICE ENDURANCE E/W CYCLES DATA RETENTION YEARS

PCF8582C-2; PCA8582F-2 500000

Note

1. At the time of publication of this data sheet the statistical history was not yet sufficient to guarantee 1000000000 E/W

cycle performance for these types.

(1)

40

December 1994 3

Philips Semiconductors Product specification

256 x 8-bit CMOS EEPROMS

with I

BLOCK DIAGRAM

2

C-bus interface

DIVIDER

( 128)

SEQUENCER

EE

CONTROL

4

PTC

7

( 16)

TIMER

PCX8582X-2 Family

MBC794

OSCILLATOR

HIGH

ADDRESS

2

I C - BUS CONTROL LOGIC

REGISTER

EEPROM

8

POINTER

ADDRESS

PCX8582X-2

handbook, full pagewidth

Fig.1 Block diagram.

BYTE

INPUT

FILTER

8

DD

V

6

n

5

3

COUNTER

BYTE

LATCH

(8 bytes)

SHIFT

REGISTER

SWITCH

ADDRESS

TEST MODE DECODER

321

POWER - ON RESET

SS

V

4

December 1994 4

SCL

SDA

A2

A1

A0

Philips Semiconductors Product specification

256 x 8-bit CMOS EEPROMS

with I

2

C-bus interface

PINNING

SYMBOL PIN DESCRIPTION

A0 1 address input 0

A1 2 address input 1

A2 3 address input 2

V

SS

SDA 5 serial data input/output (I

SCL 6 serial clock input (I

4 negative supply voltage

2

C-bus)

2

C-bus)

PTC 7 programming time control output

V

DD

8 positive supply voltage

handbook, halfpage

A0

A1

A2

V

SS

Fig.2 Pin configuration.

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

V

I

I

I

I

O

T

stg

T

amb

supply voltage −0.3 +7.0 V

voltage on any input pin |ZI| > 500 Ω VSS− 0.8 VDD+ 0.8 V

current on any input pin − 1mA

output current − 10 mA

storage temperature −65 +150 °C

operating ambient temperature

PCF8582C-2; PCF8582E-2 −40 +85 °C

PCD8582D-2 −25 +70 °C

PCA8582F-2 −40 +125 °C

PCX8582X-2 Family

1

2

PCX8582X-2

3

4

MBC792

V

8

DD

PTC

7

SCL

6

5

SDA

December 1994 5

Philips Semiconductors Product specification

256 x 8-bit CMOS EEPROMS

with I

2

C-bus interface

CHARACTERISTICS

PCF8582C-2: V

PCD8582D-2: V

PCF8582E-2: V

PCA8582F-2: V

= 2.5 to 6.0 V; VSS=0V; T

DD

= 3.0 to 6.0 V; VSS=0V; T

DD

= 4.5 to 5.5 V; VSS=0V; T

DD

= 4.5 to 5.5 V; VSS=0V; T

DD

= −40 to +85 °C; unless otherwise specified.

amb

= −25 to +70 °C; unless otherwise specified.

amb

= −40 to +85 °C; unless otherwise specified.

amb

= −40 to +125 °C; unless otherwise specified.

amb

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

Supplies

V

DD

supply voltage

PCF8582C-2 2.5 6.0 V

PCD8582D-2 3.0 6.0 V

PCF8582E-2; PCA8582F-2 4.5 5.5 V

I

DDR

I

DDW

I

DDSB

supply current READ f

PCF8582C-2; PCD8582D-2 V

PCF8582E-2; PCA8582F-2 V

supply current ERASE/WRITE f

PCF8582C-2; PCD8582D-2 V

PCF8582E-2; PCA8582F-2 V

supply current STANDBY f

PCF8582C-2; PCD8582D-2 V

PCF8582E-2; PCA8582F-2 V

= 100 kHz

SCL

= 3.0 V − 60 µA

DD

V

= 6.0 V − 200 µA

DD

= 5.5 V − 200 µA

DD

= 100 kHz

SCL

= 3.0 V − 0.6 mA

DD

= 6.0 V − 2.0 mA

V

DD

= 5.5 V − 2.0 mA

DD

= 100 kHz

SCL

= 3.0 V − 3.5 µA

DD

= 6.0 V − 10 µA

V

DD

= 5.5 V − 10 µA

DD

PTC input (pin 7)

V

IL

V

IH

LOW level input voltage −0.8 0.1V

HIGH level input voltage 0.9V

SCL input (pin 6)

V

IL

V

IH

I

LI

f

SCL

C

I

LOW level input voltage −0.8 0.3V

HIGH level input voltage 0.7V

input leakage current VI=VDDor V

SS

clock input frequency 0 100 kHz

input capacitance VI=V

SS

SDA input/output (pin 5)

V

IL

V

IH

V

OL

I

LO

C

I

LOW level input voltage −0.8 0.3V

HIGH level input voltage 0.7V

LOW level output voltage IOL= 3 mA; V

output leakage current VOH=V

input capacitance VI=V

SS

DD(min)

DD

Data retention time

t

S

data retention time T

=55°C10−years

amb

PCX8582X-2 Family

V

DD

VDD+ 0.8 V

DD

V

DD

VDD+ 0.8 V

DD

−±1µA

− 7pF

V

DD

VDD+ 0.8 V

DD

− 0.4 V

− 1 µA

− 7pF

December 1994 6

Loading...

Loading...