INTEGRATED CIRCUITS

DATA SH EET

PCF8833

STN RGB - 132 × 132 × 3 driver

Objective specification 2003 Feb 14

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

4 BLOCK DIAGRAM

5 PINNING

6 INSTRUCTIONS

6.1 Exit commands

6.2 Function set

7 FUNCTIONAL DESCRIPTION

7.1 MPU interfaces

7.2 Display data RAM and access arbiter

7.3 Command decoder

7.4 Grey scale controller

7.5 Timing generator

7.6 Oscillator

7.7 Reset

7.8 LCD voltagegenerator and bias level generator

7.9 Column drivers, data processing and data

latches

7.10 Row drivers

8 PARALLEL INTERFACE

8.1 8080-series 8-bit parallel interface

9 SERIAL INTERFACE

9.1 Write mode

9.2 Read mode

10 LIMITING VALUES

11 HANDLING

12 DC CHARACTERISTICS

13 AC CHARACTERISTICS

14 APPLICATION INFORMATION

14.1 Supply and capacitor connection configuration

15 MODULE MAKER PROGRAMMING

15.1 V

calibration

LCD

15.2 Factory defaults

15.3 Seal bit

15.4 OTP architecture

15.5 Interface commands

15.6 Suggestion on how to calibrate V

LCD2

using

MMVOP

15.7 Example of filling the shift register

15.8 Programming flow

15.9 Programming specification

16 INTERNAL PROTECTION CIRCUITS

17 BONDING PAD INFORMATION

18 TRAY INFORMATION

19 DATA SHEET STATUS

20 DEFINITIONS

21 DISCLAIMERS

2003 Feb 14 2

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

1 FEATURES

• Single chip LCD controller and driver

• 132 rows and 396 column outputs (132 × RGB)

• Low cross talk by Frame Rate Control (FRC)

• 4 kbyte colours (RGB) = 4 : 4 : 4 mode

• 256 colours (RGB) = 3:3:2 mode using the 209 kbit

RAM and a Look-Up Table (LUT)

• 65 kbyte colours (RGB) = 5 : 6 : 5 mode using the

209 kbit RAM with dithering

• 8 colours Power-save mode

• Display data RAM 132 × 132 (RGB) (4 kbyte colour)

• Interfaces:

– 3-line serial interface

– 8-bit 8080 Intel CPU interface.

• Display features:

– Area scrolling

– 32-line partial Display mode

– Software programmable colour depth mode

– N-line inversion for low cross talk.

• On-chip:

– Oscillator for display system, requires no external

components (external clock also possible)

– Generation of V

– Segmented temperature compensation of V

LCD

LCD

and

frame frequency.

• Logic supply voltage range V

DD1

to V

SS1

:

– 1.5 to 3.3 V.

• Analog supply voltage range for V

to V

SS2

:

generation V

LCD

DD2

– 2.4 to 4.5 V.

• Analog supply voltage range for reference voltage

generation V

DD3

to V

SS1

:

– 2.4 to 3.5 V.

• Display supply voltage range V

LCD

to V

SS1

:

– 3.8 to 20 V.

• Low power consumption; suitable for battery operated

systems

• CMOS compatible inputs

• Manufactured in silicon gate CMOS process

• Optimized layout for COF, Chip On Glass (COG) and

Transformer Coupled Plasma (TCP) assembly.

2 GENERAL DESCRIPTION

The PCF8833 is a single chip low power CMOS LCD

controller driver, designed to drive colour Super-Twisted

Nematic (STN) displays of 132 rows and 132 RGB

columns. All necessary functions for the display are

provided in a single chip, includingdisplay RAMwhich has

a capacity of 209 kbit (132 × 12-bit × 132). The PCF8833

uses the Multiple Row Addressing (MRA) driving

technique in order toachieve thebest opticalperformance

at the lowest power consumption. The PCF8833 offers

2 types of microcontroller interfaces namely the

8080 system interface and the 3-line serial interface.

3 ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

PCF8833U/2DA/1 − chip with bumps in tray −

2003 Feb 14 3

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

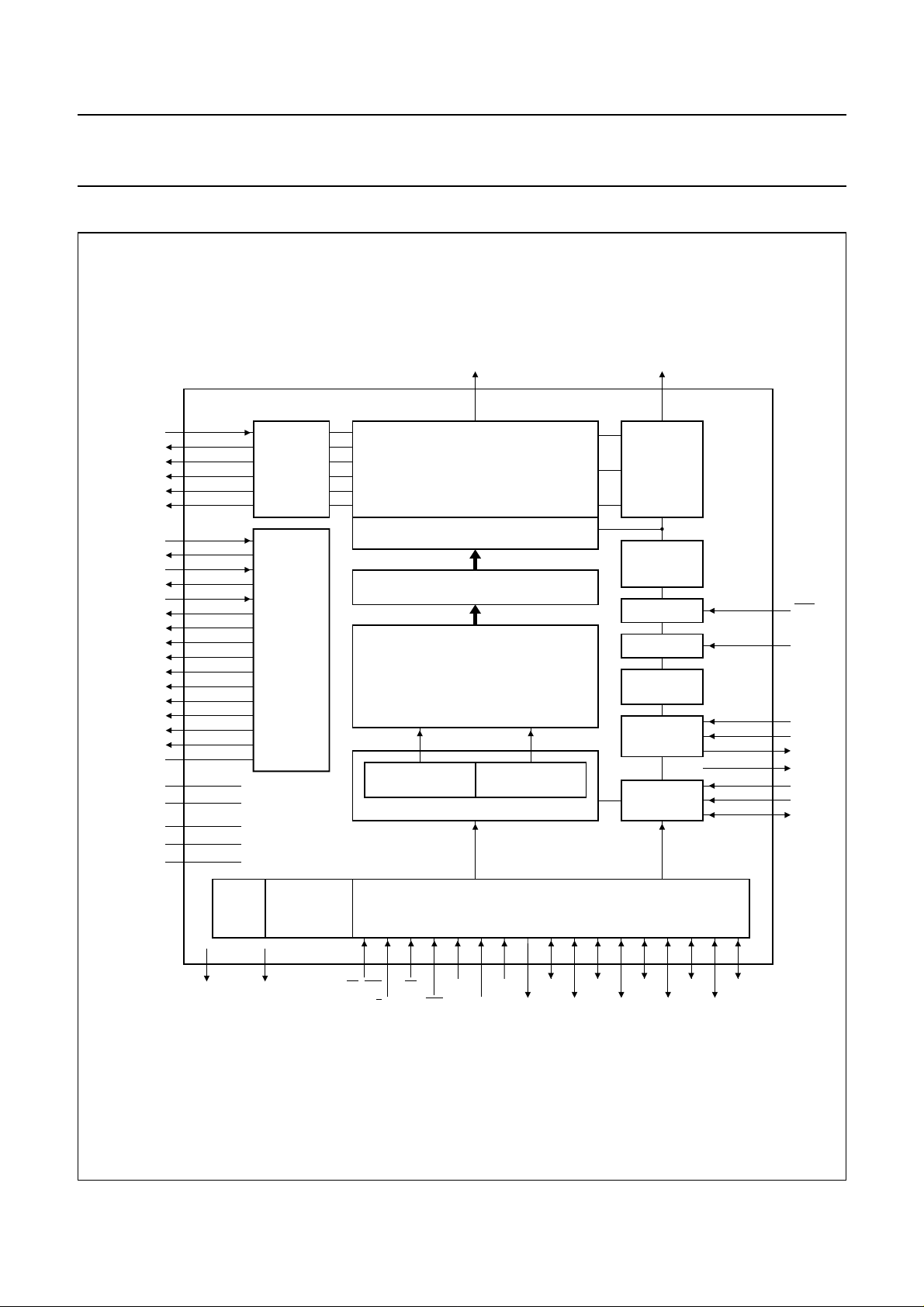

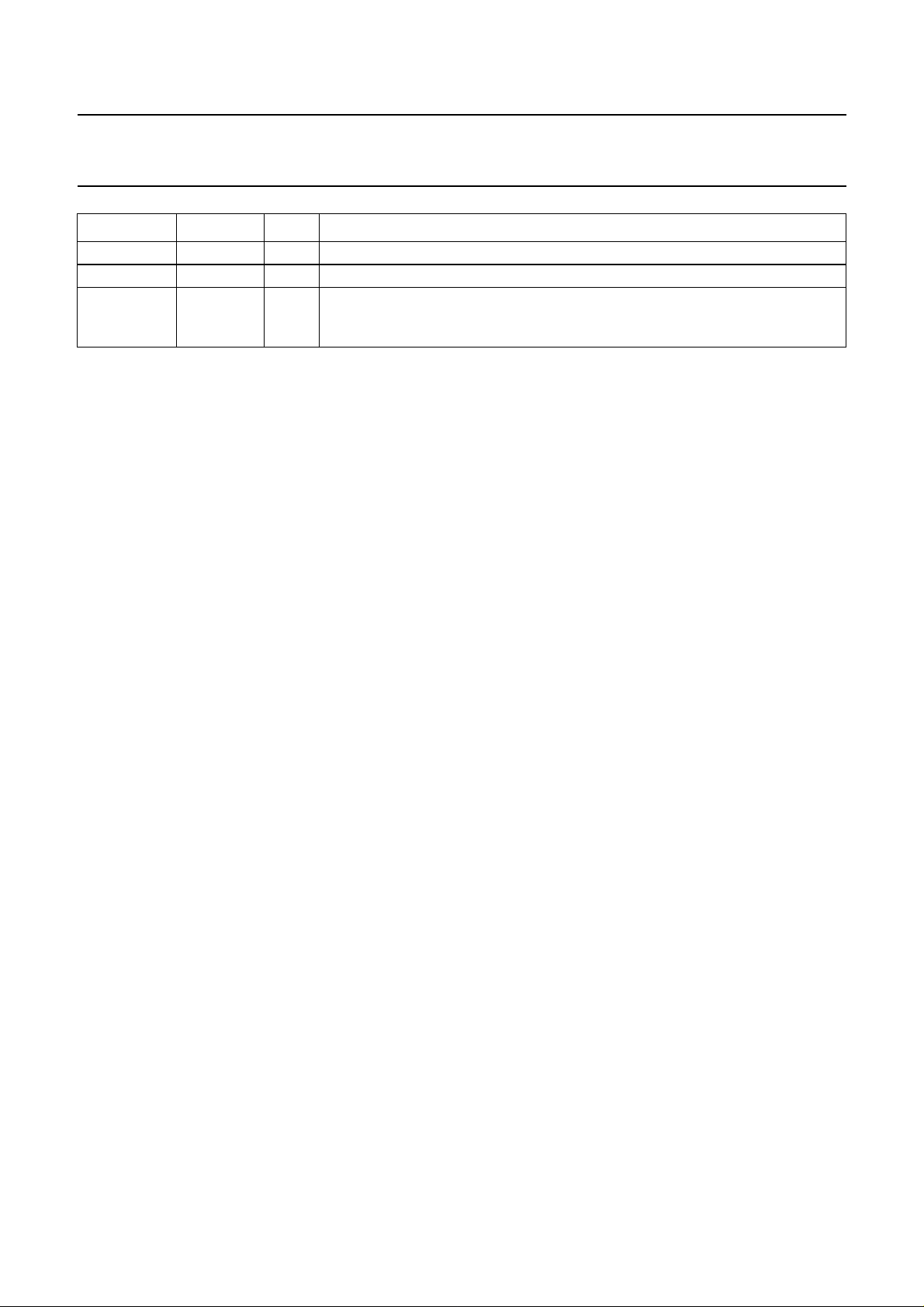

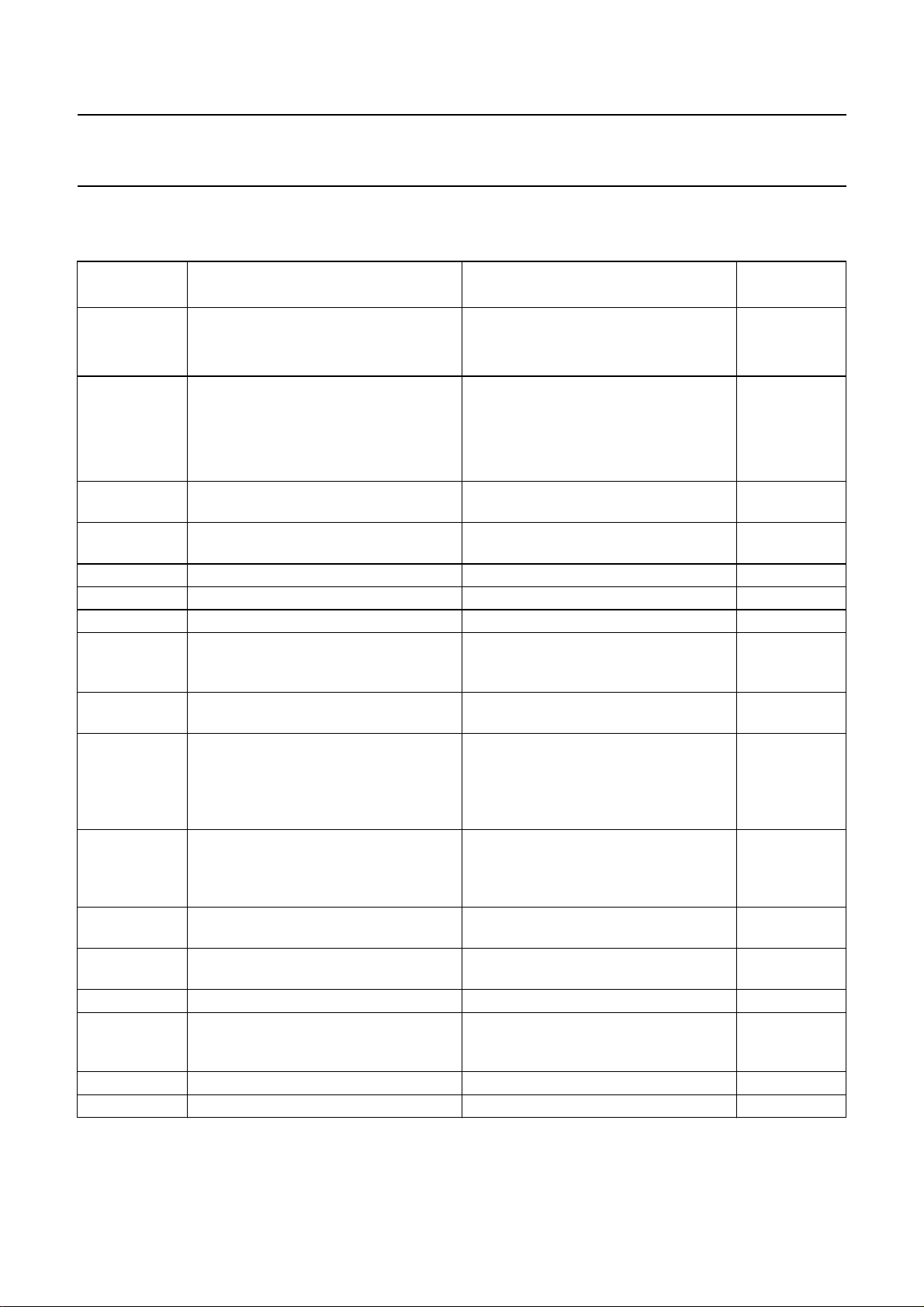

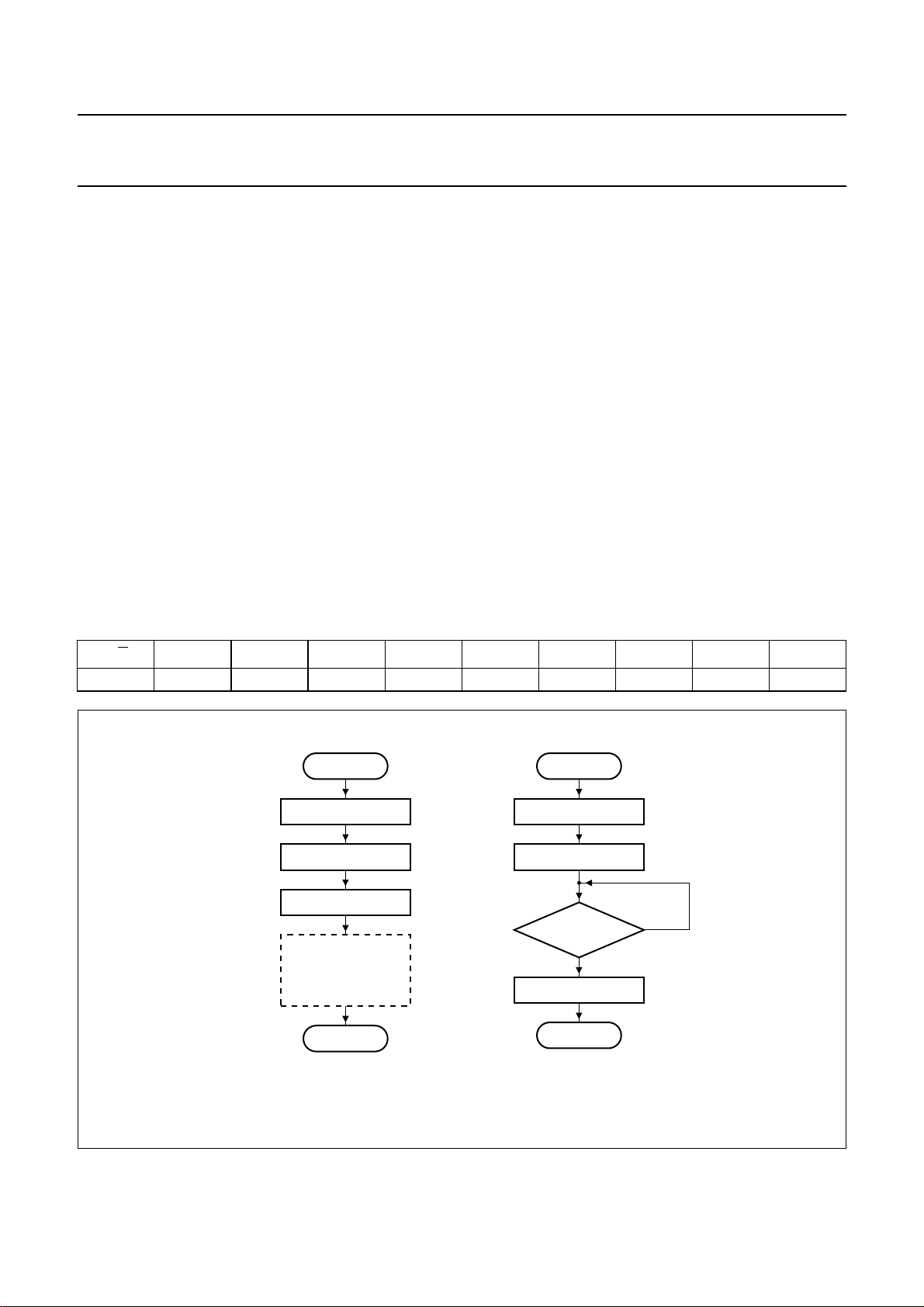

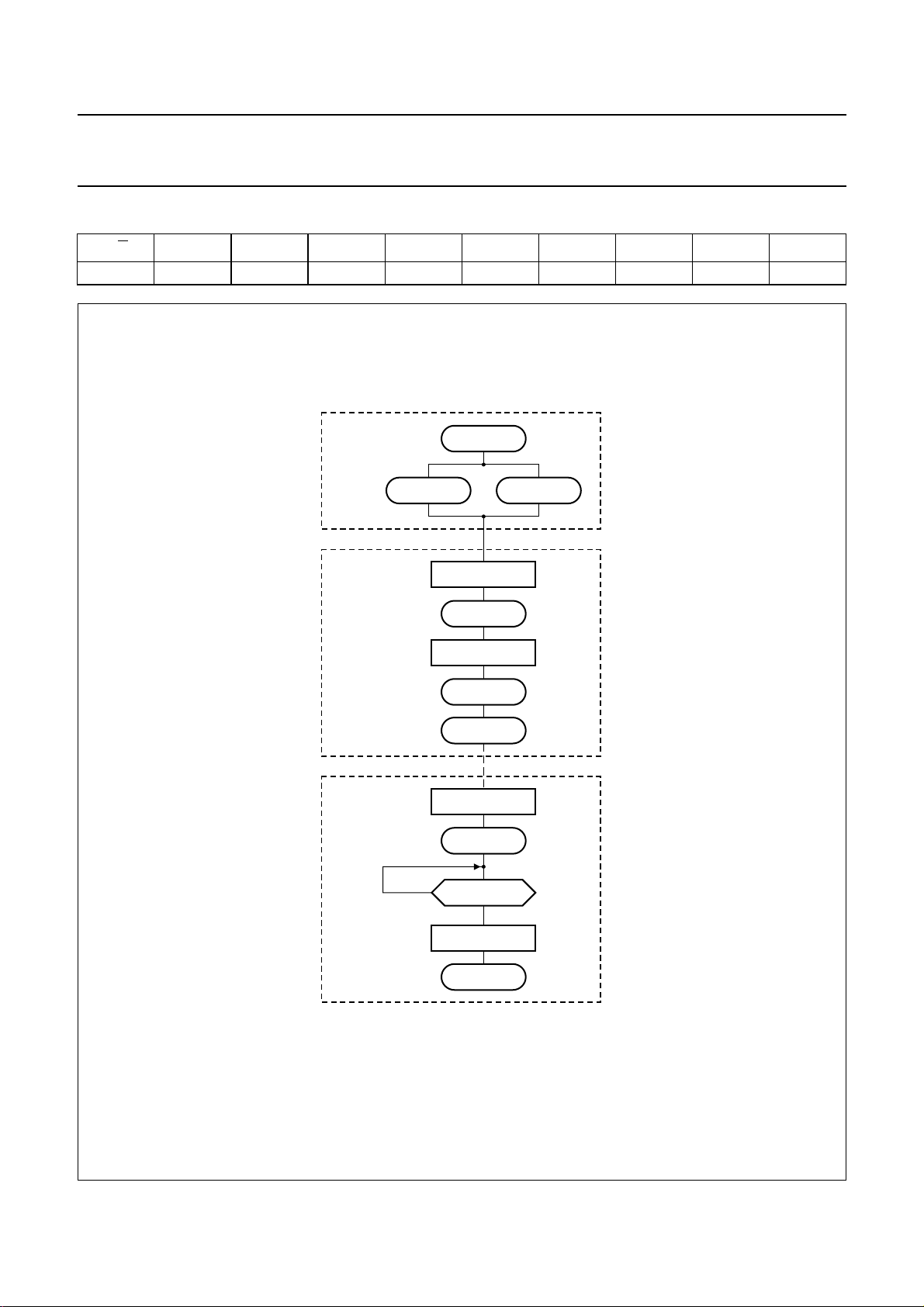

4 BLOCK DIAGRAM

handbook, full pagewidth

V

LCDIN2

V2H

V1H

VC

V1L

V2L

V

LCDSENSE

V

LCDOUT1

V

LCDIN1

V

LCDOUT2

V

DD2

C1+

C1−

C2+

C2−

C3+

C3−

C4+

C4−

C5+

C5−

V

SS2

V

OTP(gate)

V

OTP(drain)

V

DD3

V

DD1

V

SS1

713, 719

731, 732

729, 730

724 to 728

722, 723

720, 721

712

674 to 683

684 to 690

703 to 711

530 to 539

626 to 631

632 to 637

638 to 643

644 to 649

650 to 655

656 to 661

662 to 667

668 to 673

691 to 696

697 to 702

508 to 517

565 to 572

557 to 564

525 to 529

519 to 524

498 to 507

LCD BIAS

LEVEL

GENERATOR

LCD

VOLTAGE

GENERATOR

X AND Y RAM WRITE

ADDRESS COUNTER

PCF8833

C0 to C395

34 to 429

COLUMN DRIVERS

DATA PROCESSING

DATA LATCHES

DISPLAY DATA RAM

132 × 132 × 12-bits

DISPLAY ADDRESS

READ COUNTER

ARBITER

R0 to R131

2 to 33, 430 to 461,

464 to 495, 733 to 768

ROW

DRIVERS

ORTHOGONAL

FUNCTION

GENERATOR

RESET

OSCILLATOR

TIMING

GENERATOR

GREYSCALE

CONTROLLER

COMMAND

DECODER

496

555

578

577

576

575

574

573

625

RES

OSC

T1

T2

T3

T4

T5

T6

T7

256/64 KBYTES

256

COLOUR

LUT

V

DD(tieoff)VSS(tieoff)

TO 4 KBYTES

COLOUR

MAPPING

579, 624 518 549 551 550 552 553 554 548 547 545 543 541 546 544 542 540 497556

CS/SCE RD

D/C/SCLK WR

PS0

Fig.1 Block diagram.

2003 Feb 14 4

MPU INTERFACES

PS2

PS1

SDOUT

D0/SDIND1D2

D4 TE

D3

D6

D5

D7

MGU910

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

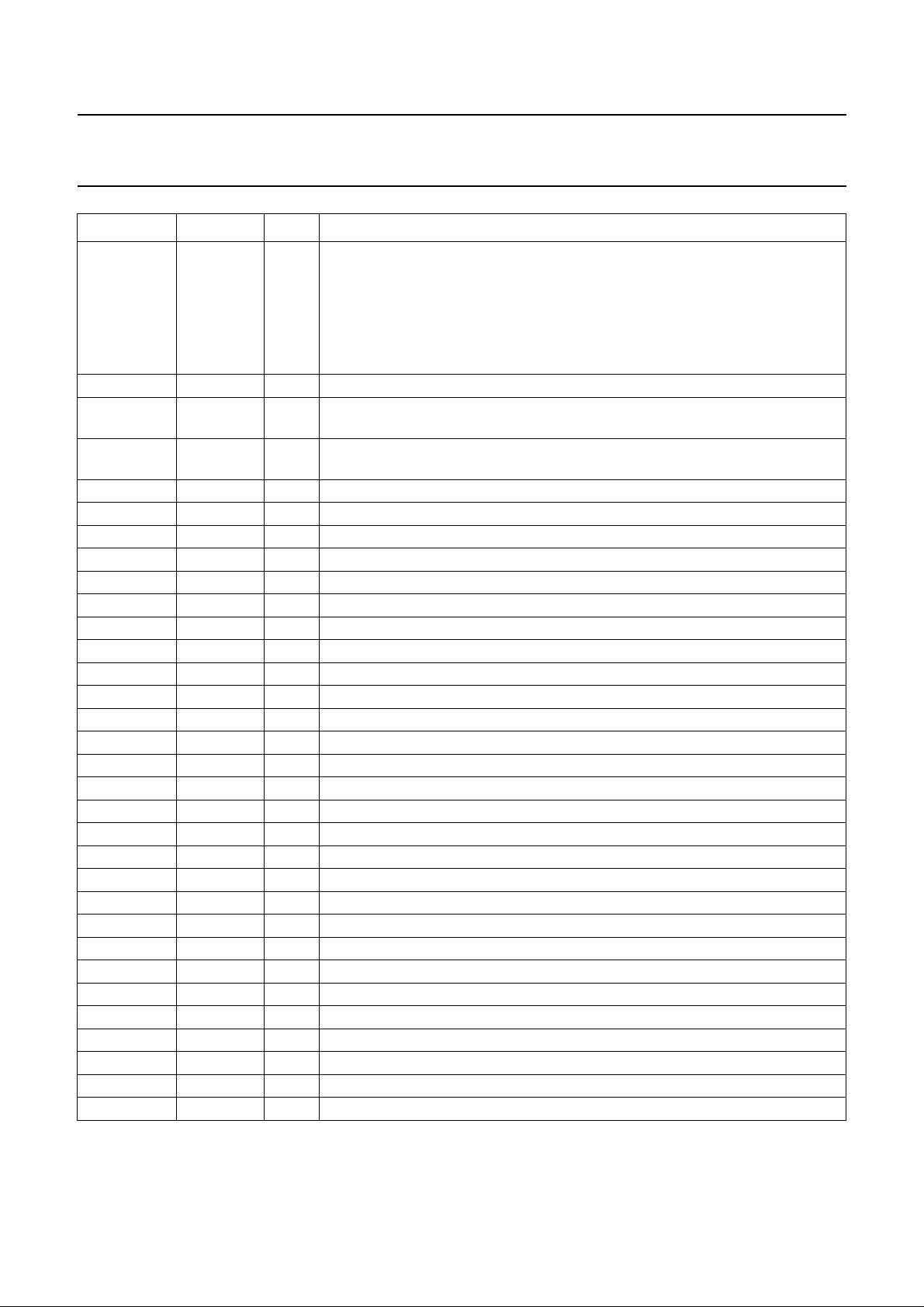

5 PINNING

SYMBOL PAD TYPE DESCRIPTION

R95 to R64 2 to 33 O LCD row driver outputs

C0 to C395 34 to 429 O LCD column driver outputs

R0 to R31 430 to 461 O LCD row driver outputs

R63 to R32 464 to 495 O LCD row driver outputs

RES 496 I external reset; this signal will reset the device and must be applied to properly

initialize the chip (active LOW)

TE 497 O/I tearing line (in Normal mode it is always an output)

V

SS1

V

SS2

CS/SCE 518 I chip select parallel interface or serial chip enable (active LOW)

V

DD1

V

DD3

V

DD2

D7 540 I/O 8-bit parallel data; in Serial mode tie to V

D3 541 I/O 8-bit parallel data; in Serial mode tie to V

D6 542 I/O 8-bit parallel data; in Serial mode tie to V

D2 543 I/O 8-bit parallel data; in Serial mode tie to V

D5 544 I/O 8-bit parallel data; in Serial mode tie to V

D1 545 I/O 8-bit parallel data; in Serial mode tie to V

D4 546 I/O 8-bit parallel data; in Serial mode tie to V

D0/SDIN 547 I/O 8-bit parallel data or serial data input

SDOUT 548 O serial data output; in Parallel mode tie to V

D/

C/SCLK 549 I data/command indicator parallel interface or serial clock

WR 550 I write clock parallel interface; in Serial mode tie to V

RD 551 I read clock parallel interface; in Serial mode tie to V

PS0 552 I set serial or parallel interface mode PS1 and PS2 must tied to either V

PS1 553 I set serial or parallel interface mode PS1 and PS2 must tied to either V

PS2 554 I set serial or parallel interface mode PS1 and PS2 must tied to either V

498 to 507 PS system ground

508 to 517 PS system ground

519 to 524 PS logic supply voltage

525 to 529 PS V

530 to 539 PS

DD2

and V

are the supply voltage pins for the internal voltage generator

DD3

including the temperature compensation circuits; V

connected together but in this case care must be taken to respect the supply

voltage range (see Chapter 13); V

chip. V

can be connected together with V

DD1

must also be taken to respect the supply voltage range; see Chapter 13. V

and V

must not be applied before V

DD3

If the internal voltage generator is not used, pins V

connected to V

V

DD1

V

DD1

V

DD1

DD1

and V

DD2

is used as the supply for the rest of the

DD1

and V

DD2

DD1.

DD2

DD3

and V

can be

DD3

but in this case care

DD2

must be

DD3

.

or V

SS1

SS1

SS1

SS1

SS1

SS1

SS1

DD1

or V

or V

or V

or V

or V

or V

, V

DD1

DD1

DD1

DD1

DD1

DD1

DD1

or D0

SS1

DD1

(active LOW)

DD1

(active LOW)

SS1

SS1

SS1

or

or

or

2003 Feb 14 5

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

SYMBOL PAD TYPE DESCRIPTION

OSC 555 I oscillator input or external oscillator resistor connection; when the on-chip

oscillator is used this input must be connected to V

if used, is connected to this input and the internal oscillatormust be switched off

with a software command; if the oscillator and external clock are all inhibited by

connecting pin OSC to V

, the display is not clocked and may be left in a

SS1

DC state; to avoid this the chip should always be put into Power-down mode

before stopping the clock.

V

DD(tieoff)

V

OTP(drain)

V

OTP(gate)

556 O can be used to tie inputs to V

DD1

557 to 564 PS supply voltage for OTP programming (write voltage), in Application mode must

be tied to V

or left open-circuit

SS1

565 to 572 PS supply voltage for OTP programming, in Application mode must be tied to V

or left open-circuit

T6 573 I test pin; not accessible to user; must be connected to V

T5 574 I test pin; not accessible to user; must be connected to V

T4 575 O test pin; not accessible to user; must be left open-circuit

T3 576 O test pin; not accessible to user; must be left open-circuit

T2 577 I/O test pin; not accessible to user; must be also connected to V

T1 578 I/O test pin; not accessible to user; must be also connected to V

V

SS(tieoff)

V

SS(tieoff)

579 O can be used to tie inputs to V

624 O can be used to tie inputs to V

SS1

SS1

T7 625 I/O test pin; not accessible to user; must be connected to V

C1+ 626 to 631 I positive input pump capacitor voltage multiplier 1

C1− 632 to 637 I negative input pump capacitor voltage multiplier 1

C2+ 638 to 643 I positive input pump capacitor voltage multiplier 1

C2− 644 to 649 I negative input pump capacitor voltage multiplier 1

C3+ 650 to 655 I positive input pump capacitor voltage multiplier 1

C3− 656 to 661 I negative input pump capacitor voltage multiplier 1

C4+ 662 to 667 I positive input pump capacitor voltage multiplier 1

C4− 668 to 673 I negative input pump capacitor voltage multiplier 1

V

LCDOUT1

V

LCDIN1

674 to 683 O output voltage multiplier 1

684 to 690 PS LCD supply input voltage 1

C5+ 691 to 696 I positive input pump capacitor voltage multiplier 2

C5− 697 to 702 I negative input pump capacitor voltage multiplier 2

V

LCDOUT2

V

LCDSENSE

V

LCDIN2

703 to 711 O output voltage multiplier 2

712 I voltage multiplier regulation input; must be connected to V

713 to 719 PS LCD supply input voltage 2

V2L 720, 721 O LCD bias level

V1L 722, 723 O LCD bias level

VC 724 to 728 O LCD bias level

V1H 729, 730 O LCD bias level

; an external clocksignal,

DD1

SS1

SS1

SS1

SS1

SS1

LCDOUT2

SS1

2003 Feb 14 6

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

SYMBOL PAD TYPE DESCRIPTION

V2H 731, 732 O LCD bias level

R96 to R131 733 to 768 O LCD row driver outputs

Dummy 1,462,463,

580 to623,

769

6 INSTRUCTIONS

The PCF8833 communicates with the host using an 8-bit parallel interface or a 3-line serial interface. Processing of

instructions and data sent to the interface do not require the display clock. The display clock and interface clock are

independent from each other. The display clock is derived from the built-in oscillator.

The PCF8833 has 2 types of accesses; those defining the operating mode of the device (instructions) and those filling

the display RAM. Since writing to the RAM occurs more frequently, efficient data transfer is achieved by

autoincrementing the RAM address pointers.

There are 3 types of instructions:

1. For defining display configuration

2. For setting X and Y addresses

3. Miscellaneous.

Commands inthe range of 00Hto AFH not definedin Table 1 and commandDDH have the sameeffect as no operation

(NOP).

All commands in range B0H to B9H and DEH to FFH are forbidden.

2003 Feb 14 7

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to berotated correctly when browsingthrough the pdf in the Acrobat reader. white toforce landscape pages tobe ...

2003 Feb 14 8

2003 Feb 14 8

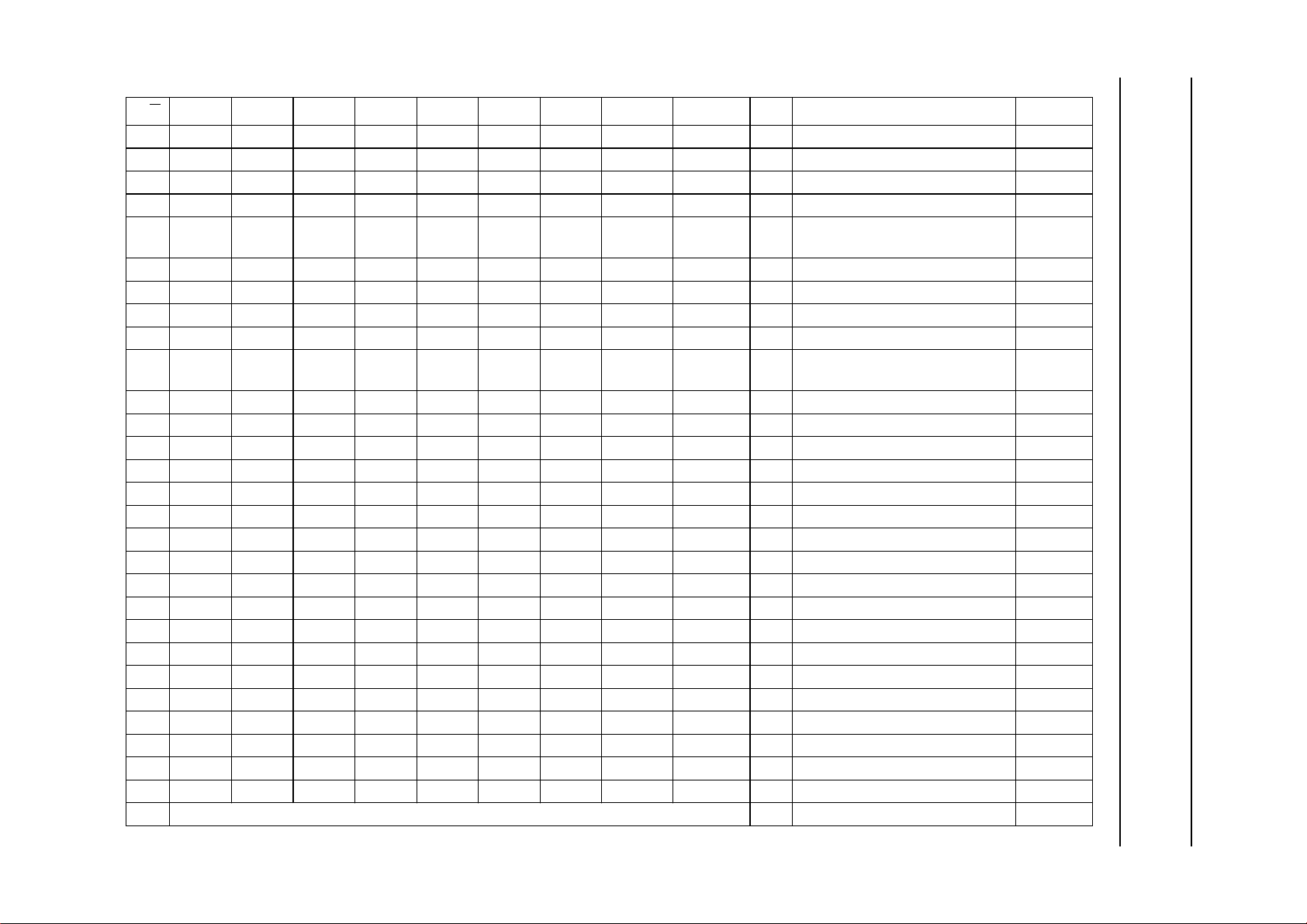

Table 1 Command table; note1

D/C 7 6 5 4 3 2 1 0 DEFAULT OTP DESCRIPTION SECTION

00000000 0 00H−no operation (NOP)

00000000 1 01H−software reset (SWRESET) 6.2.3

00000001 0 02H−booster voltage off (BSTROFF) 6.2.4

00000001 1 03H−booster voltage on (BSTRON) 6.2.5

00000010 0 04H−read display identification

(RDDIDIF)

00000100 1 09H−read display status (RDDST) 6.2.7

00001000 0 10H−Sleep_IN 6.2.8

00001000 1 11H−Sleep_OUT 6.2.9

00001001 0 12H−Partial mode on (PTLON) 6.2.10

00001001 1 13H−normal Display mode on

(NORON)

00010000 0 20H−display inversion off (INVOFF) 6.2.12

00010000 1 21H−display inversion on (INVON) 6.2.13

00010001 0 22H−all pixel off (DALO)

00010001 1 23H−all pixel on (DAL)

00010010 1 25H−set contrast (SETCON) 6.2.16

1 X VCON6VCON5VCON4VCON3VCON2VCON1VCON

00010100 0 28H−display off (DISPOFF) 6.2.17

00010100 1 29H−display on (DISPON) 6.2.18

00010101 02AH−column address set (CASET) 6.2.19

1 xs[7] xs[6] xs[5] xs[4] xs[3] xs[2] xs[1] xs[0] 02H − X address start; 0 ≤xs ≤ 83H

1 xe[7] xe[6] xe[5] xe[4] xe[3] xe[2] xe[1] xe[0] 81H − X address end; xs ≤ xe ≤ 83H

00010101 12BH−page address set (PASET) 6.2.20

1 ys[7] ys[6] ys[5] ys[4] ys[3] ys[2] ys[1] ys[0] 02H − Y address start; 0 ≤ys ≤ 83H

1 ye[7] ye[6] ye[5] ye[4] ye[3] ye[2] ye[1] ye[0] 81H − Y address end; ys ≤ ye ≤ 83H

00010110 02CH−memory write (RAMWR) 6.2.21

1D7D6D5D4D3D2D1 D0 XXH−write data 6.2.21

00010110 12DH−colour set (RGBSET) 6.2.22

1 X X X X R3 R2 R1 R0 00H − red tone 000 6.2.22

1 6 bytes for 6 red tones − 6 red tones 6.2.22

00H − set contrast

0

6.2.1

6.2.6

6.2.11

6.2.14

6.2.15

6.2.16

6.2.19

6.2.19

6.2.20

6.2.20

Philips Semiconductors Objective specification

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

STN RGB - 132 × 132 × 3 driver PCF8833

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to berotated correctly when browsingthrough the pdf in the Acrobat reader. white toforce landscape pages tobe ...

2003 Feb 14 9

2003 Feb 14 9

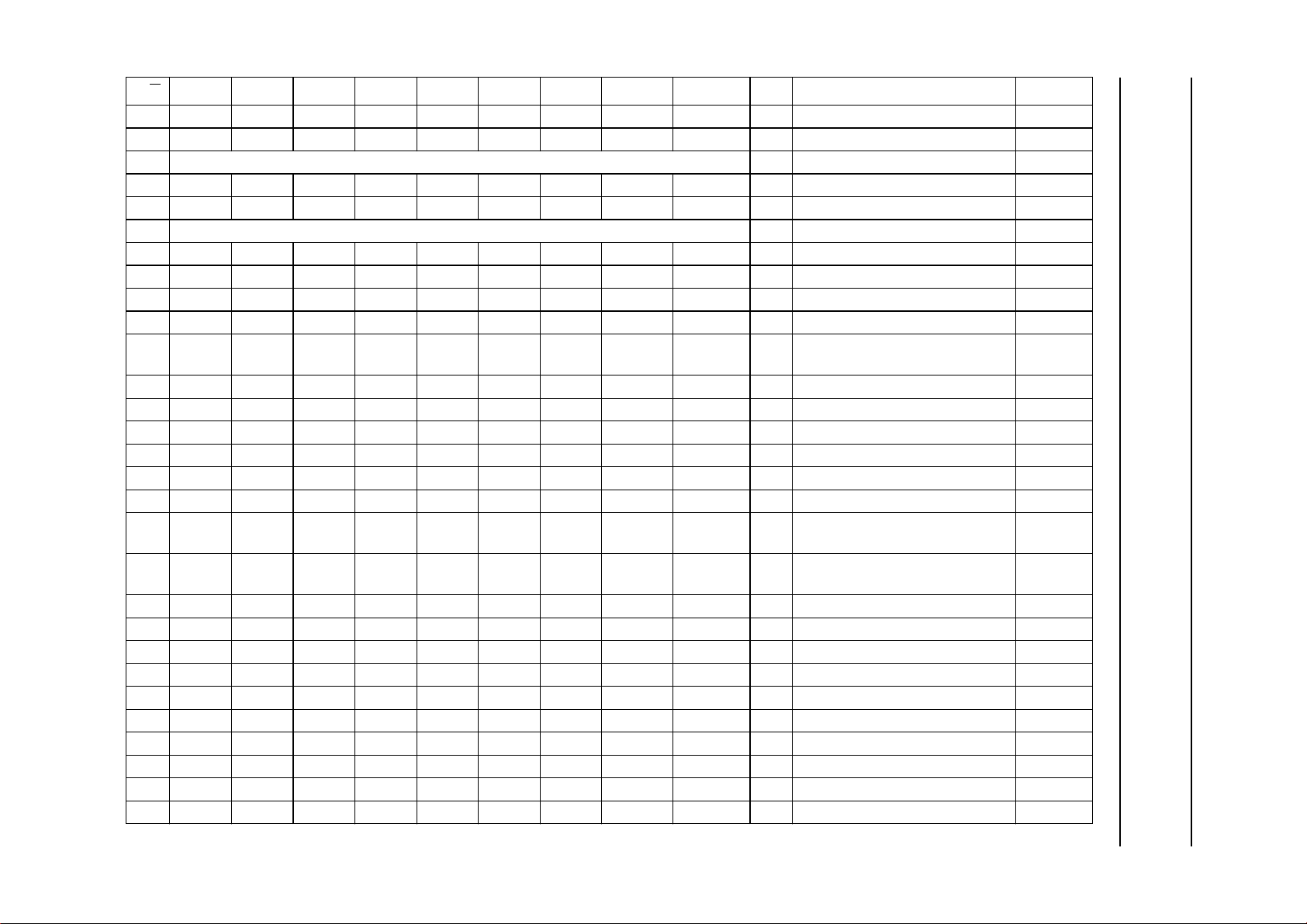

C 7 6 5 4 3 2 1 0 DEFAULT OTP DESCRIPTION SECTION

D/

1 X X X X R3 R2 R1 R0 0FH − red tone 111 6.2.22

1 X X X X G3 G2 G1 G0 00H − green tone 000 6.2.22

1 6 bytes for 6 green tones − 6 green tones 6.2.22

1 X X X X G3 G2 G1 G0 0FH − green tone 111 6.2.22

1 X X X X B3 B2 B1 B0 00H − blue tone 00 6.2.22

1 2 bytes for 2 blue tones − 2 blue tones 6.2.22

1 X X X X B3 B2 B1 B0 0FH − blue tone 11 6.2.22

00011000 0 30H−partial area (PTLAR) 6.2.23

1 AA1S7 AA1S6 AA1S5 AA1S4 AA1S3 AA1S2 AA1S1 AA1S0 00H − PTLAR active area start address

1 AA1E7 AA1E6 AA1E5 AA1E4 AA1E3 AA1E2 AA1E1 AA1E1 1FH − PTLAR active area end address

00011001 1 33H−vertical scroll definition

(VSCRDEF)

1TF

1SA

1BF

7TF6

7SA6

7BF6

TF

SA

BF

TF

5

SA

5

BF

5

TF

4

SA

4

BF

4

TF

3

SA

3

BF

3

TF

2

2

2

SA

BF

1

1

1

TF

SA

BF

0

0

0

00H − top fixed area 6.2.24

82H − scroll area 6.2.24

00H − bottom fixed area 6.2.24

00011010 0 34H−tearing line off (TEOFF) 6.2.25

00011010 1 35H−tearing line on (TEON) 6.2.26

1XXXXXXX X 00H− 6.2.26

00011011 0 36H−memory data access control

(MADCTL)

1 MY MX V LAO RGB X X X 00H − RAM data addressing/data

control

00011011 1 37H−set Scroll Entry Point (SEP)

1 SEP7 SEP6 SEP5 SEP4 SEP3 SEP2 SEP1 SEP0 00H − scroll entry point

00011100 0 38H−Idle mode off (IDMOFF)

00011100 1 39H−Idle mode on (IDMON)

00011101 03AH−interface pixelformat (COLMOD)

1 X X X X X P2 P1 P0 03H − colour interface format

(2)

0 1 0 1 1 0 0 0 0 B0H x

1 X X X X VPR

1 X X X VPR

VPR

4

VPR

8

VPR

3

VPR

7

VPR

2

VPR

6

1

VPR

5

0

08H x V

01H x V

set VOP(SETVOP)

OP

OP

0 1 0 1 1 0 1 0 BRS B4H x Bottom Row Swap (BRS)

6.2.23

6.2.23

6.2.24

6.2.27

6.2.27

6.2.24

6.2.24

6.2.28

6.2.29

6.2.30

6.2.30

6.2.31

6.2.31

6.2.31

6.2.32

Philips Semiconductors Objective specification

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

STN RGB - 132 × 132 × 3 driver PCF8833

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to berotated correctly when browsingthrough the pdf in the Acrobat reader. white toforce landscape pages tobe ...

2003 Feb 14 10

2003 Feb 14 10

C 7 6 5 4 3 2 1 0 DEFAULT OTP DESCRIPTION SECTION

D/

0 1 0 1 1 0 1 1 TRS B6H x Top Row Swap (TRS)

0 1 0 1 1 1 0 0 FINV B9H − super Frame INVersion (FINV)

0 1 0 1 1 1 0 1 DOR BAH − Data ORder (DOR)

0 1 0 1 1 1 1 0 TCDFE BDH − enable/disable DF temp comp

(TCDFE)

0 1 0 1 1 1 1 1 TCVOPE BFH − enable or disable V

OP

temp

comp (TCVOPE)

0 1 1 0 0 0 0 0 EC C0H − Internal or external oscillator

(EC)

0 1 1 0 0 0 0 1 0 C2H x set multiplication factor

(SETMUL)

1 X X X X X X S1 S0 03H x multiplication factor

0 1 1 0 0 0 0 1 1 C3H x set TCVOP slopes A and B

(TCVOPAB)

1 X SLB

SLB

2

SLB

1

0

X SLA

SLA

2

SLA

1

0

34H x

0 1 1 0 0 0 1 0 0 C4H x set TCVOP slopes C and D

(TCVOPCD)

1 X SLD

SLD

2

SLD

1

0

X SLC

SLC

2

SLC

1

0

75H x

0 1 1 0 0 0 1 0 1 C5H x set divider frequency (TCDF)

1 X DFA

1 X DFB

1 X DFC

1 X DFD

DFA

6

DFB

6

DFC

6

DFD

6

DFA

5

DFB

5

DFC

5

DFD

5

DFA

4

DFB

4

DFC

4

DFD

4

DFA

3

DFB

3

DFC

3

DFD

3

DFA

2

DFB

2

DFC

2

DFD

2

DFA

1

1

1

1

DFB

DFC

DFD

0

0

0

0

56H x set divider factor in region A

35H x set divider factor in region B

30H x set divider factor in region C

25H x set divider factor in region D

0 1 1 0 0 0 1 1 0 C6H x set divider frequency 8-colour

mode (DF8colour)

1 X DF8

DF8

6

DF8

5

DF8

4

DF8

3

DF8

2

DF8

1

0

35H x set divider factor in 8-colour

mode

0 1 1 0 0 0 1 1 1 C7H x set bias system (SETBS)

1X X X XVB

3VB2

VB

1

VB

0

0BH x bias systems

01100100 0C8H−temperature read back

(RDTEMP)

01100100 1C9H−N-Line Inversion (NLI)

1 NLI

NLI

7

NLI

6

NLI

5

NLI

4

NLI

3

NLI

2

NLI

1

0

13H x after NLI time slots inversion

0 1 1 0 1 1 0 1 0 DAH x read ID1 (RDID1)

6.2.33

6.2.34

6.2.35

6.2.36

6.2.37

6.2.38

6.2.39

6.2.39

6.2.40

6.2.40

6.2.40

6.2.40

6.2.41

6.2.41

6.2.41

6.2.41

6.2.41

6.2.42

6.2.42

6.2.43

6.2.43

6.2.44

6.2.45

6.2.45

6.2.46

Philips Semiconductors Objective specification

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

STN RGB - 132 × 132 × 3 driver PCF8833

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to berotated correctly when browsingthrough the pdf in the Acrobat reader. white toforce landscape pages tobe ...

2003 Feb 14 11

2003 Feb 14 11

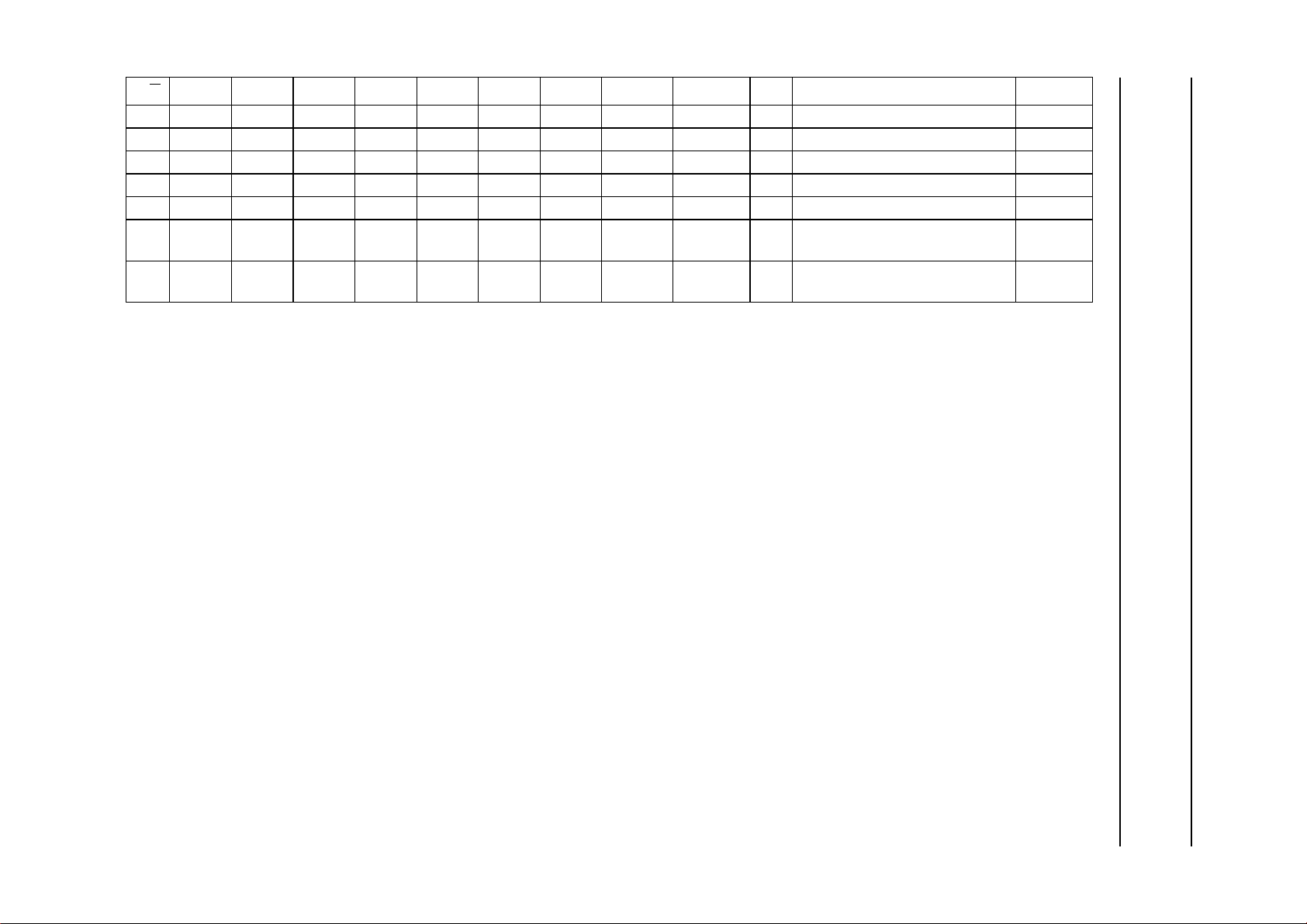

C 7 6 5 4 3 2 1 0 DEFAULT OTP DESCRIPTION SECTION

D/

0 1 1 0 1 1 0 1 1 DBH x read ID2 (RDID2)

0 1 1 0 1 1 1 0 0 DCH x read ID3 (RDID3)

0 1 1 1 0 1 1 1 SFD EFH x select factory defaults

01111000 0 F0H−enter Calibration mode

1 X X ORA

01111000 1 F1H−shift data in OTP shift registers

1 OS7 OS6 OS5 OS4 OS3 OS2 OS1 OS0 XX − multiple data byte; any number

Notes

1. X = don’t care.

2. This function can be set by OTP.

3. If the OTP bit Enable Factory Defaults (EFD) has been programmed to logic 1 (default value is logic 0), then the Set Factory Defaults (SFD)

instruction is ignored and the device will always use the OTP default data.

ORA1ORA

2

X OPE CALMM 00H − set calibration control settings

0

(OTPSHTIN)

of bytes allowed

(3)

6.2.46

6.2.46

6.2.47

15.5

15.5

15.5

15.5

Philips Semiconductors Objective specification

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

STN RGB - 132 × 132 × 3 driver PCF8833

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

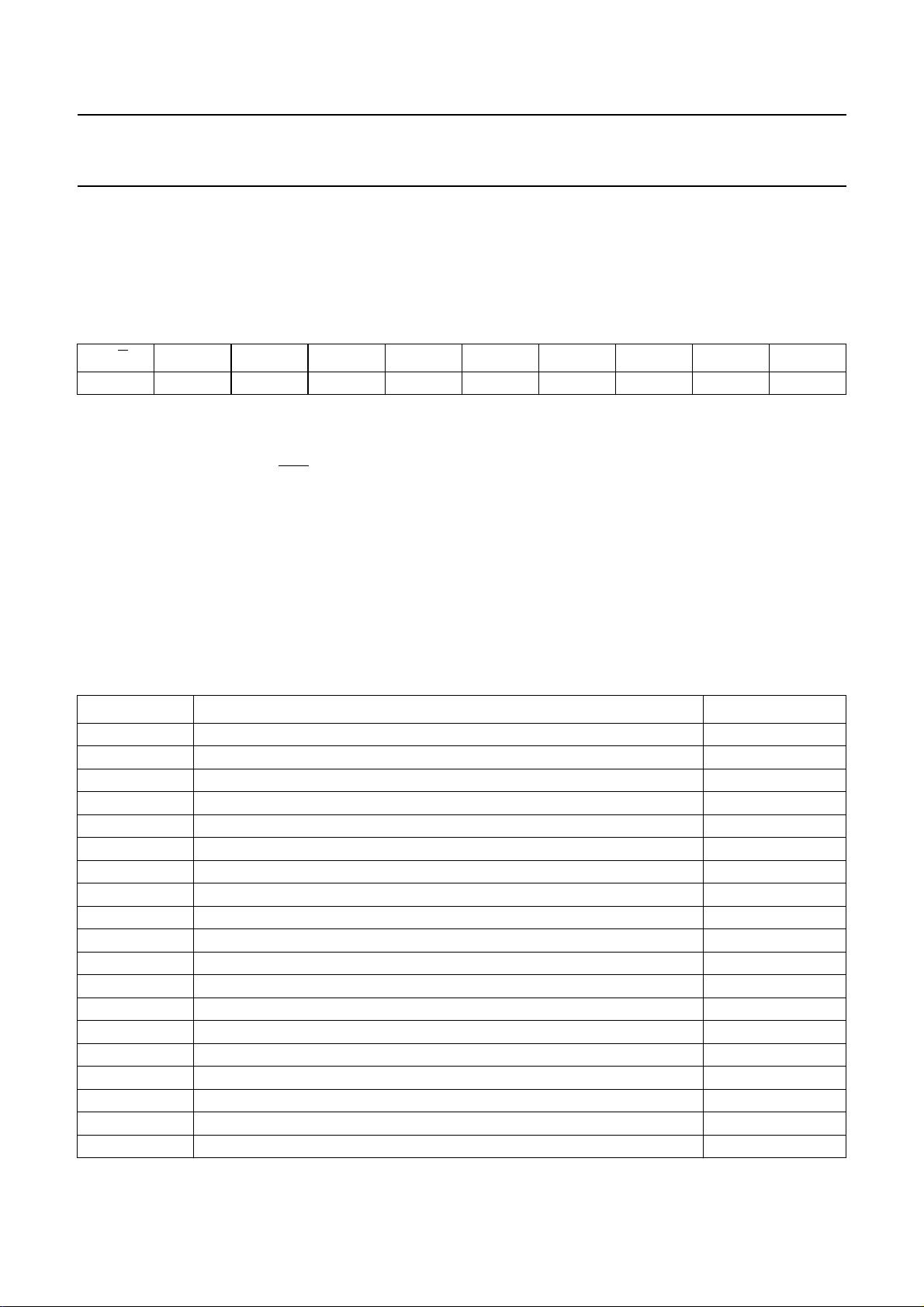

6.1 Exit commands Table 2 Command description

INPUT

COMMAND

Sleep_IN

(SLPIN)

Sleep_OUT

(SLPOUT)

BSTROFF display voltage generation off display is switched on or off by

BSTRON display voltage generation on display is switched on or off by

DISPOFF display off rows and columns are tied to V

DISPON display on DISPOFF

NORON Normal mode on full display is driven by RAM data PTLON SEP

PTLON Partial mode on partial display area is driven by RAM

SEP Scroll mode on NORON

PIXON (DAL) in full Display mode (NORON) all pixels

PIXOFF

(DALO)

IDMOFF Idle mode off full colour resolution storedin theRAM is

IDMON Idle mode on 8-colour mode became active: The MSB

INVOFF inverted display off INVON

INVON inverted display on in Partial mode only pixels of partial area

TEOFF tearing pulse disabled TEON

TEON tearing pulse enabled TEOFF reset

Power-down mode: power-downhas priority over display and

display off

display voltage generation off

exit power-down: after reset; BSTRONand DISPONis set,

display → DISPON/DISPOFF

display voltage

generation → BSTRON/BSTROFF

(refresh from OTP cells if CALMM = 0)

are on; in partial Display mode only

partial area pixels are driven on; pixels

outside partial area are off

all pixel off command INVON is not effective when

PARAMETERS CONDITIONS

booster settings, but the setting is kept

but become active only with Sleep_OUT

DISPON/DISPOFF

DISPON/DISPOFF

SS1

data; display area outside partial area is

off

command INVON is not effective when

DAL is active

DALO is active

written to the display

of data stored in RAM is evaluated only

are inverted; INVON is not effective;

when DAL or DALO are active

EXIT

COMMAND

Sleep_OUT

Sleep_IN reset

BSTRON reset

BSTROFF

DISPON reset

NORON SEP

reset

PTLON reset

PIXOFF

(DALO)

NORON

PTLON SEP

reset

PIXON (DAL)

NORON

PTLON SEP

reset

IDMON

IDMOFF reset

INVOFF reset

2003 Feb 14 12

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2 Function set

6.2.1 NO OPERATION No operation (NOP) has no effect on internal data or settings. However, it can be used to terminate data transfer (read

and write).

Table 3 No operation command bits

D/C76543210DEFAULT

00000000000H

6.2.2 RESET The PCF8833 has ahardware and a software reset. After

power-upa hardwarereset(pin RES)mustbe applied;see

Fig.50. The hardware and software resets give the same

results. After a reset, the chip has the following state:

• All LCD outputs are set to VSS (display off)

• RAM data unchanged

• Power-down mode (Sleep_IN)

• Command register set to default states; see Table 4

• Interface pins are set to inputs.

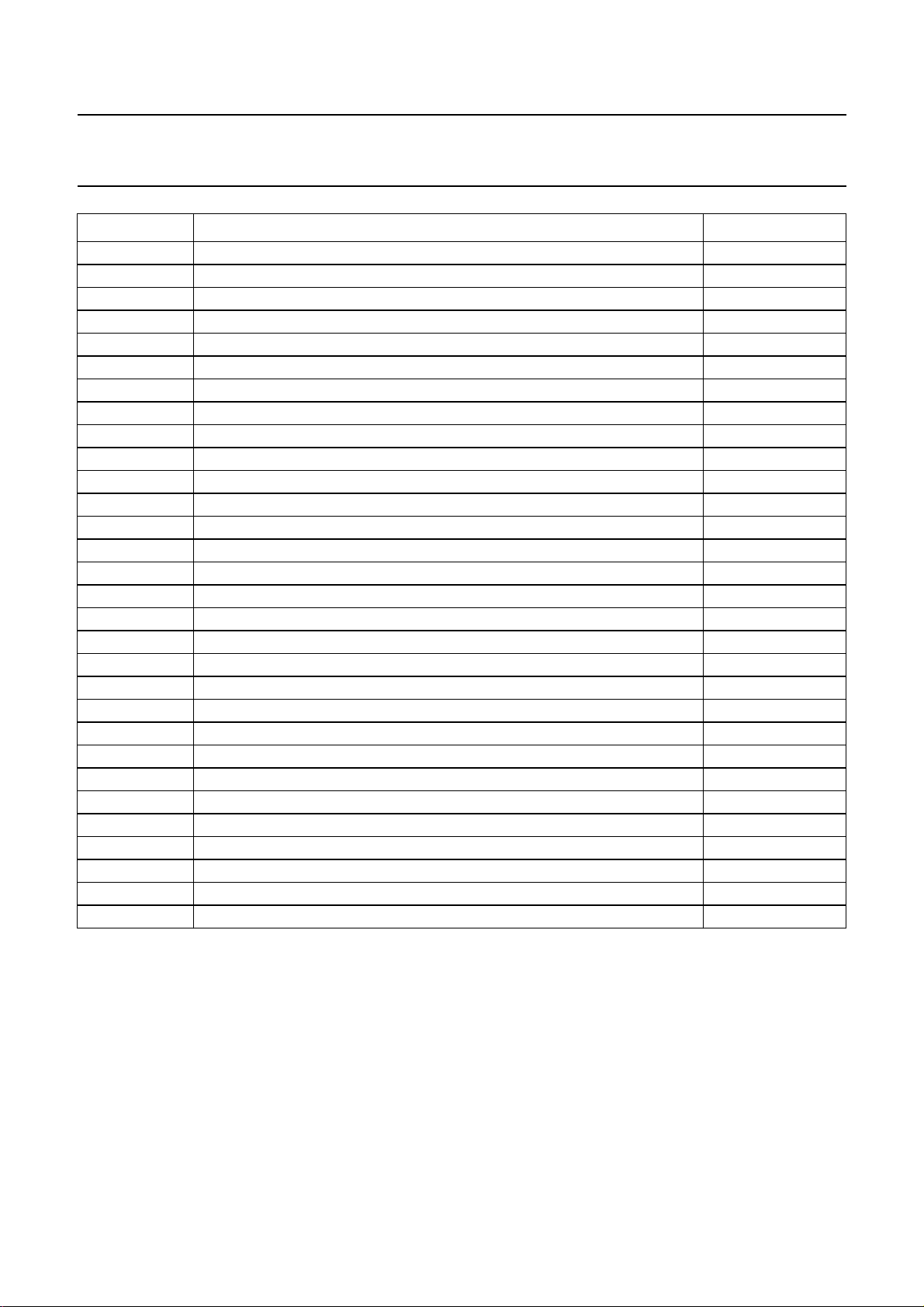

Table 4 Reset state after hardware and software reset

COMMAND DESCRIPTION RESET STATE

Sleep_IN PCF8833 is in Sleep_IN mode (booster and display are switched off) −

INVOFF display inversion is off −

BSTRON when Sleep_OUT is active; booster is switched on −

DISPON when Sleep_OUT is active; display is turned on −

TEOFF tearing effect line pulse is turned off −

IDMOFF Idle mode is turned off (4 kbyte colour mode, not 8-colour mode) −

NORON Normal mode is active, not Scroll or Partial mode −

V RAM write in X direction 0

MY no mirror Y 0

RGB colour order is RGB 0

MX no mirror X 0

LAO line address order (top to bottom) 0

BRS bottom rows are not mirrored; note 1 0

TRS top rows are not mirrored; note 1 0

FINV super frame inversion is on 1

DOR normal data order 0

TCDFE DF temperature compensation switched on 1

TCVOPE VOP temperature compensation switched on 1

EC internal oscillator 0

After a reset, care mustbe taken with respect to the reset

timing constraints (see Fig.50) when the PCF8833 is

powered-up. The power-up must be done by sending the

Sleep_OUT command.

After a power-up the display RAM content is undefined.

Neither a hardware reset nor asoftware resetchanges the

data that is stored in the display RAM. Sending display

data must stop 160 ns before issuing a hardware reset,

otherwise thelast word writtento the displayRAM may be

corrupted. The row and column outputs are tied to V

with a reset because power-down (Sleep_IN) is in the

reset state.

SS1

2003 Feb 14 13

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

COMMAND DESCRIPTION RESET STATE

xs[7:0] x address start 2DEC

xe[7:0] x address end 129DEC

ys[7:0] y address start 2DEC

ye[7:0] y address end 129DEC

RGBSET 256 to 4 kbyte colour LUT see Section 6.2.22

AA1S[7:0] partial area start address 0DEC

AA1E[7:0] partial area end address 31DEC

TF[7:0] top fixed area 0DEC

SA[7:0] scroll area 130DEC

BF[7:0] bottom fixed area 0DEC

SEP[7:0] scroll entry point 0DEC

P[2:0] interface pixel format is 12-bit/pixel 011

VPR[8:0] programming of V

S[1:0] charge pump multiplication factor; note 1 11

SLA[2:0] select slope for segment A; note 1 100

SLB[2:0] select slope for segment B; note 1 011

SLC[2:0] select slope for segment C; note 1 101

SLD[2:0] select slope for segment D; note 1 111

DFA[6:0] frame frequency for segment A is 80 Hz; note 1 56DEC

DFB[6:0] frame frequency for segment B is 130 Hz; note 1 35DEC

DFC[6:0] frame frequency for segment C is 150 Hz; note 1 30DEC

DFD[6:0] frame frequency for segment D is 180 Hz; note 1 25DEC

DF8[6:0] frame frequency for 8-colour mode is 130 Hz; note 1 35DEC

VB[3:0] bias system is F/G

NLI[7:0] inversion is after 19 time slots (76 rows in Full mode); note 1 19DEC

VCON[6:0] no contrast setting is set (twos complement number); note 1 0DEC

SFD OTP programmed data is used; note 1 1

CALMM not in Calibration mode 0

OPE disable OTP programming voltage; note 2 0

ORA[2:0] OTP row address selection 000

voltage; note 1 257DEC

LCD2

= 2.5; note 1 1011

max

Notes

1. These values can be set by the module maker. If the factory defaults OTP bit EFD have been set, the value cannot

be changed via the interface. Otherwise, the OTP data will be used if SFD is set to logic 1, which is the reset state.

2. Calibration modemay notbe entered ifthe SEAL bit has beenset. Programming isonly possiblewhen in Calibration

mode.

2003 Feb 14 14

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.3 SOFTWARE RESET

The software reset (SWRESET) has exactly the same effect as the hardware reset; see Section 6.2.2.

After sending SWRESET any command can be sent immediately without any additional delay in between, for instance:

Sleep_OUT, BSTRON and DISPON, etc.

Table 5 Software reset register bits

D/C76543210DEFAULT

00000000101H

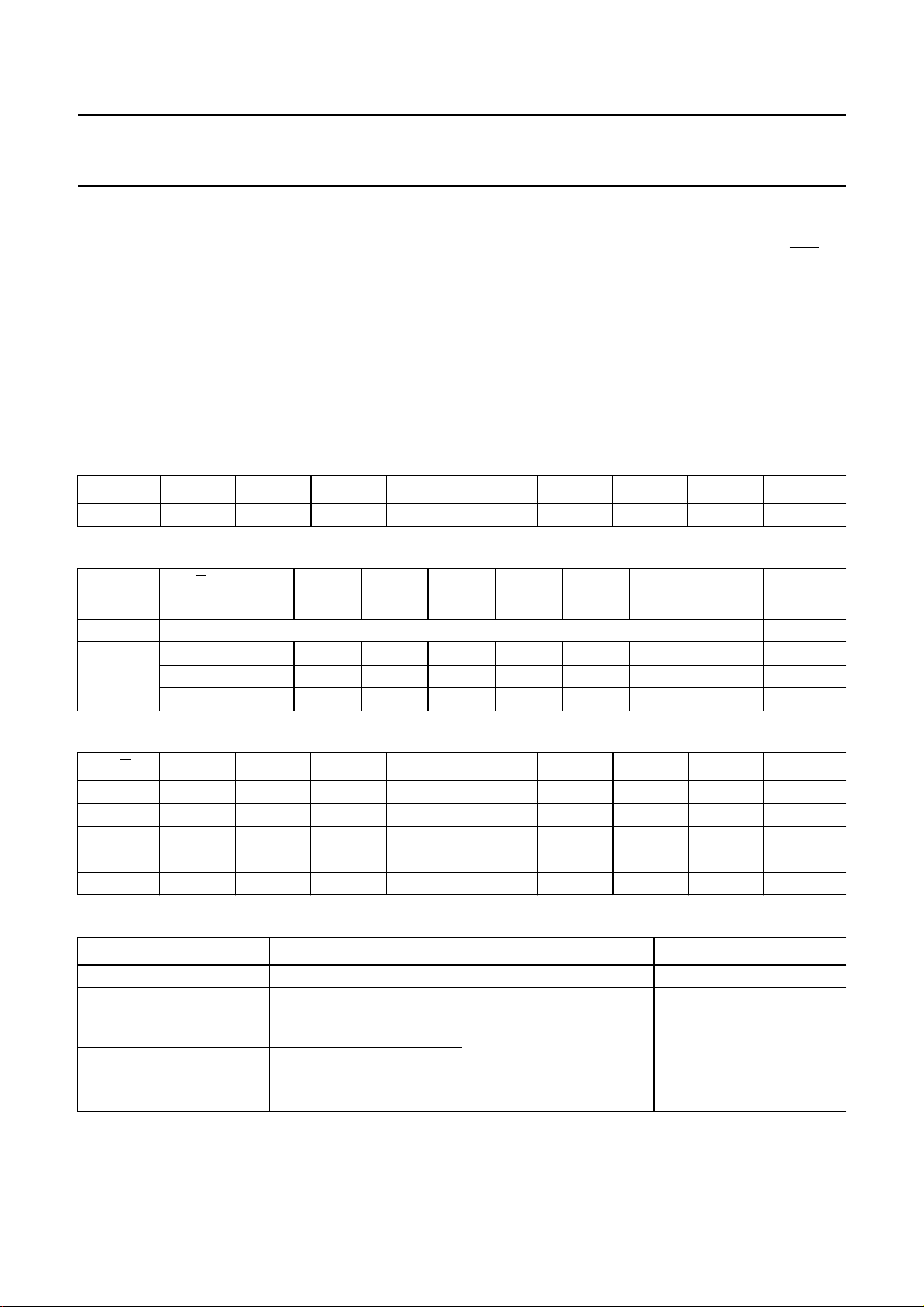

6.2.4 BOOSTER VOLTAGE OFF

The DC-to-DC converters are turned off and pins

V

LCDOUT1

and V

LCDOUT2

become 3-state.

In order to avoid any optical effect on the display, the

sequence given in Fig.2 must be used before the internal

display supply generation circuits are turned off.

The external LCD supply input voltages (V

V

) can be applied while the display voltage

LCDIN2

LCDIN1

and

Command Sleep_IN does not effect the setting of

BSTRON/BSTROFF or DISPON/DISPOFF, but switches

off the DC-to-DC converter (booster) and ties the display

outputs to V

SS1

.

For the effect of possible combinations of commands

Sleep_IN/Sleep_OUT and BSTRON/BSTROFF; see

Table 17 and Fig.4. Figure 7 shows the effects of the

combination of commands BSTRON and BSTROFF with

DISPON and DISPOFF.

generation (BSTROFF) is off. When BSTROFF, DISPON

and Sleep_OUT are set, the external LCD supply input

voltages (V

LCDIN1

and V

) must be applied, otherwise

LCDIN2

the display outputs will be undefined.

Table 6 Booster voltage off register bits

D/C76543210DEFAULT

00000001002H

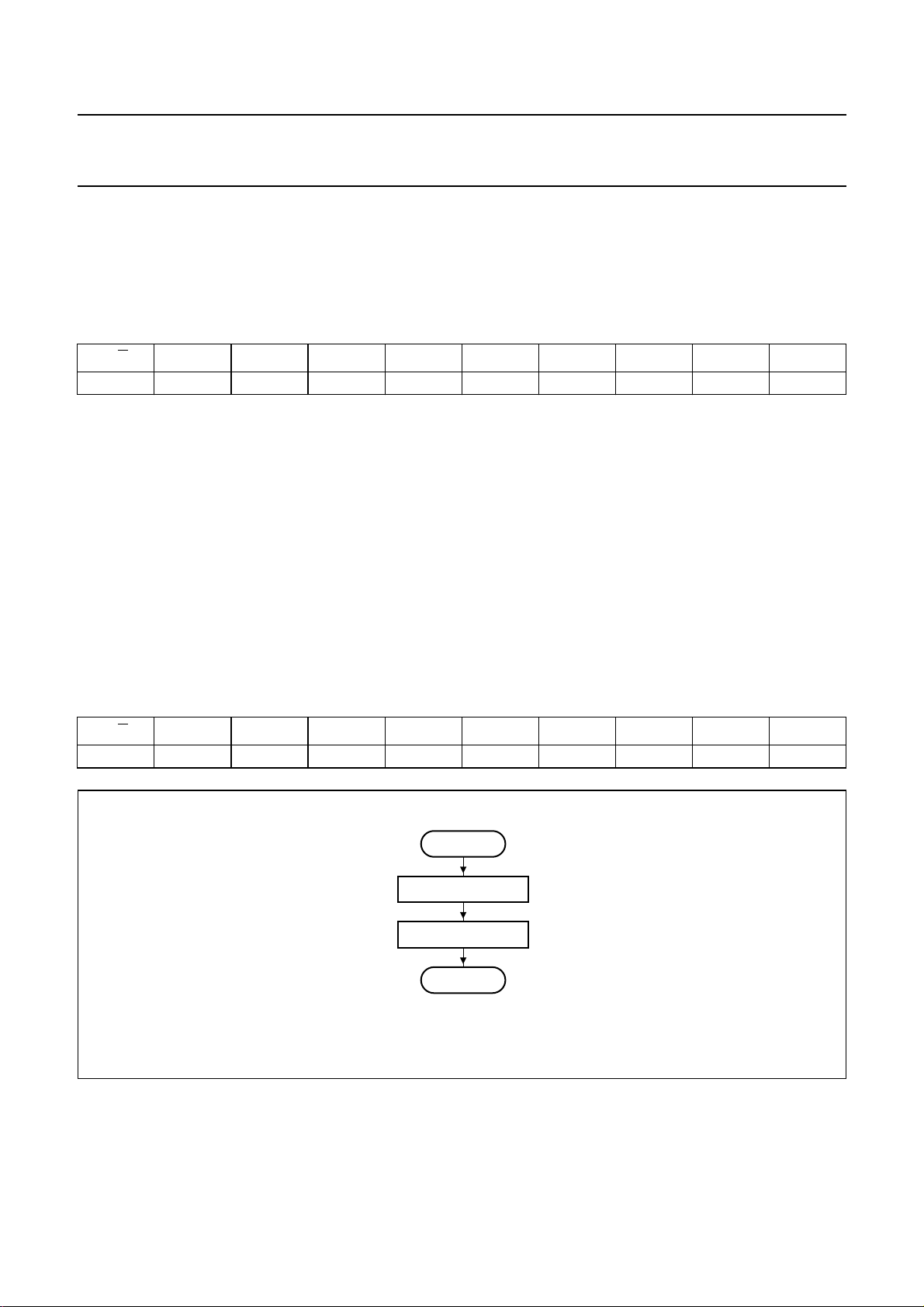

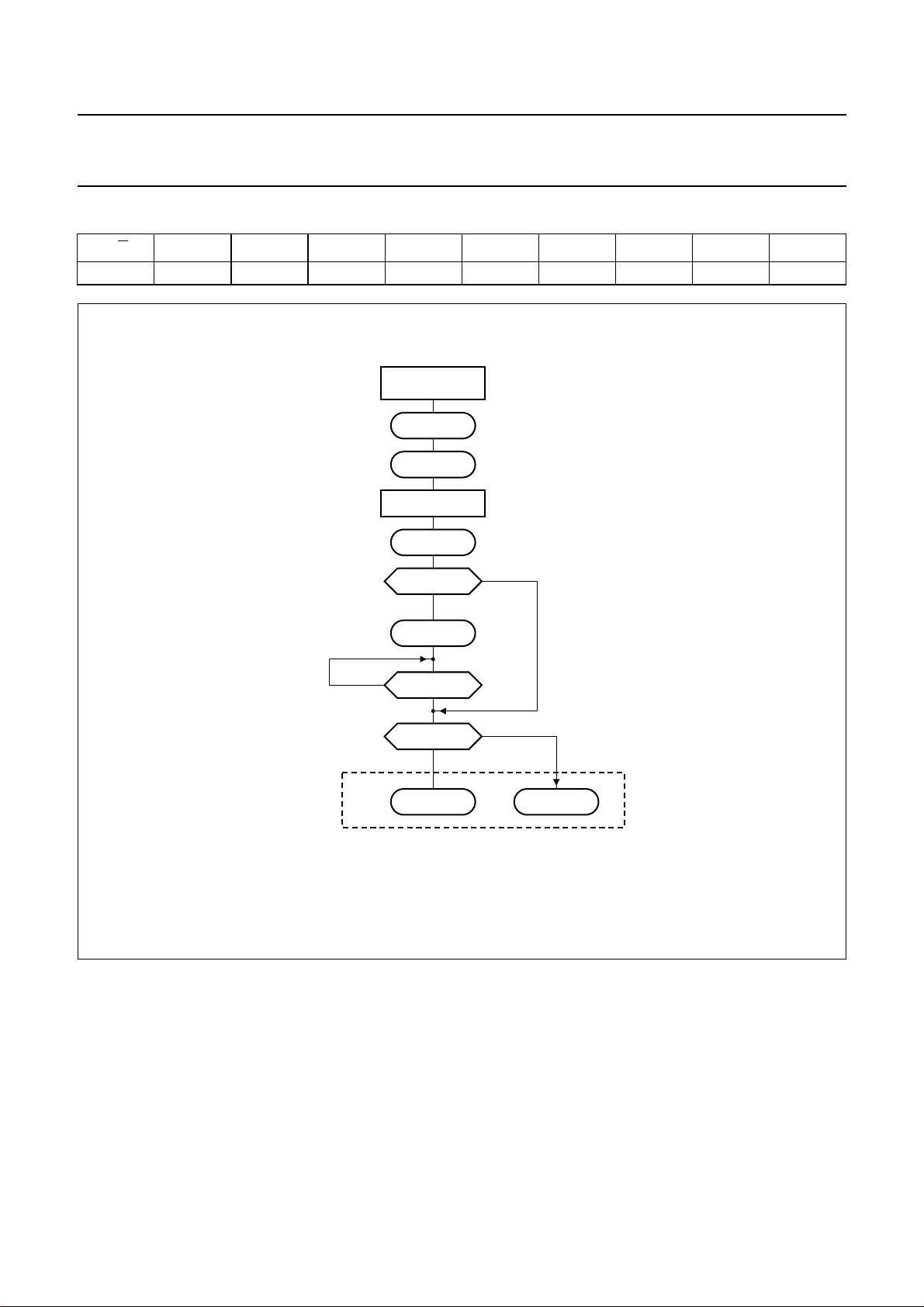

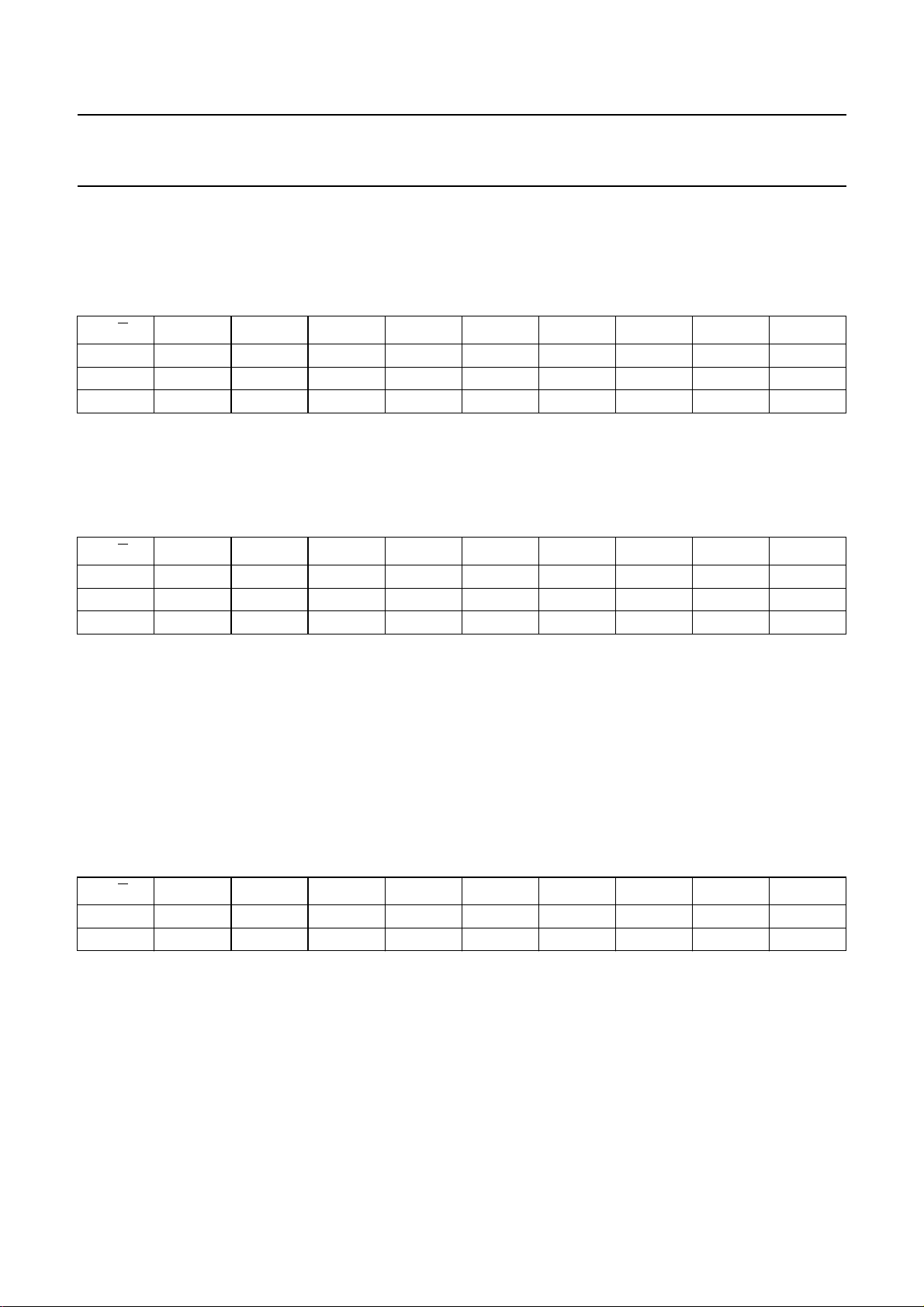

handbook, halfpage

start

send DISPOFF (28H)

send BSTROFF (02H)

end

Fig.2 Booster voltage off flow chart.

2003 Feb 14 15

MGU911

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

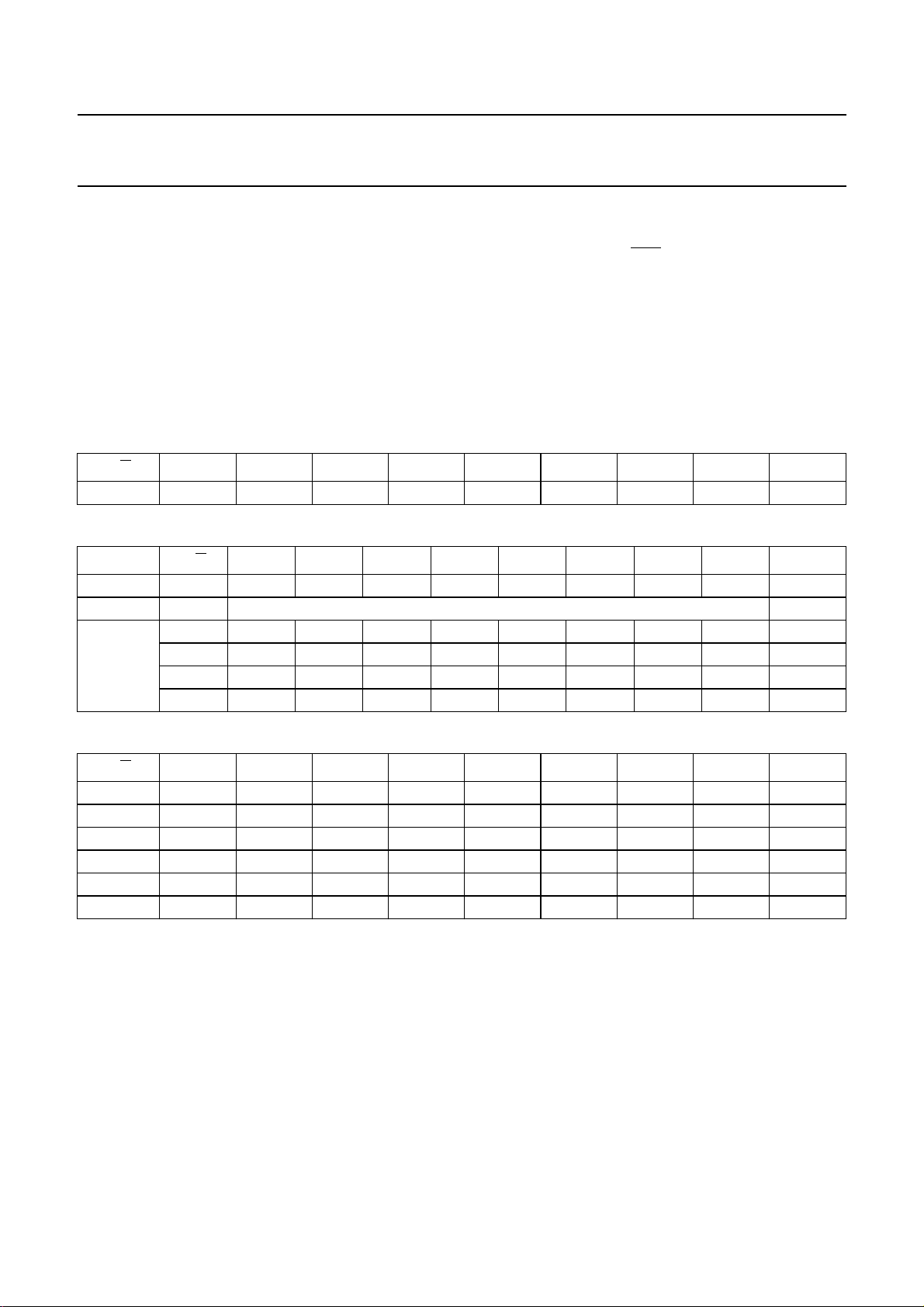

6.2.5 BOOSTER VOLTAGE ON The LCD supply generation circuits will be switched on

whenthe Boostervoltage on(BSTRON) command issent.

The BSTRON commandhas a direct effect only whenthe

PCF8833 is not in Power-down mode (Sleep_OUT is not

active).

With a reset DISPON (see Section 6.2.18) and BSTRON

are set, the PCF8833 will start-up with Sleep_OUT (see

Section 6.2.7) following the built-in start-up sequence

which generates the requested voltages and switches on

the display, unless DISPOFF and/or BSTROFF was sent.

When theLCD supplygeneration circuits areswitched on,

it is necessary to wait for a certain time before the power

circuitsbecome stableand the displaycan beswitchedon.

Because this time is dependent on the required V

LCD

voltage,the externalcomponents used,the appliedsupply

voltage and some other parameters, the PCF8833

monitors the LCD supply generation circuit internally and

will only switch-on the display when the LCD supply

The status of the LCD supply generation circuits can be

monitored with the read display status (RDDST)

command; see Section 6.2.7.

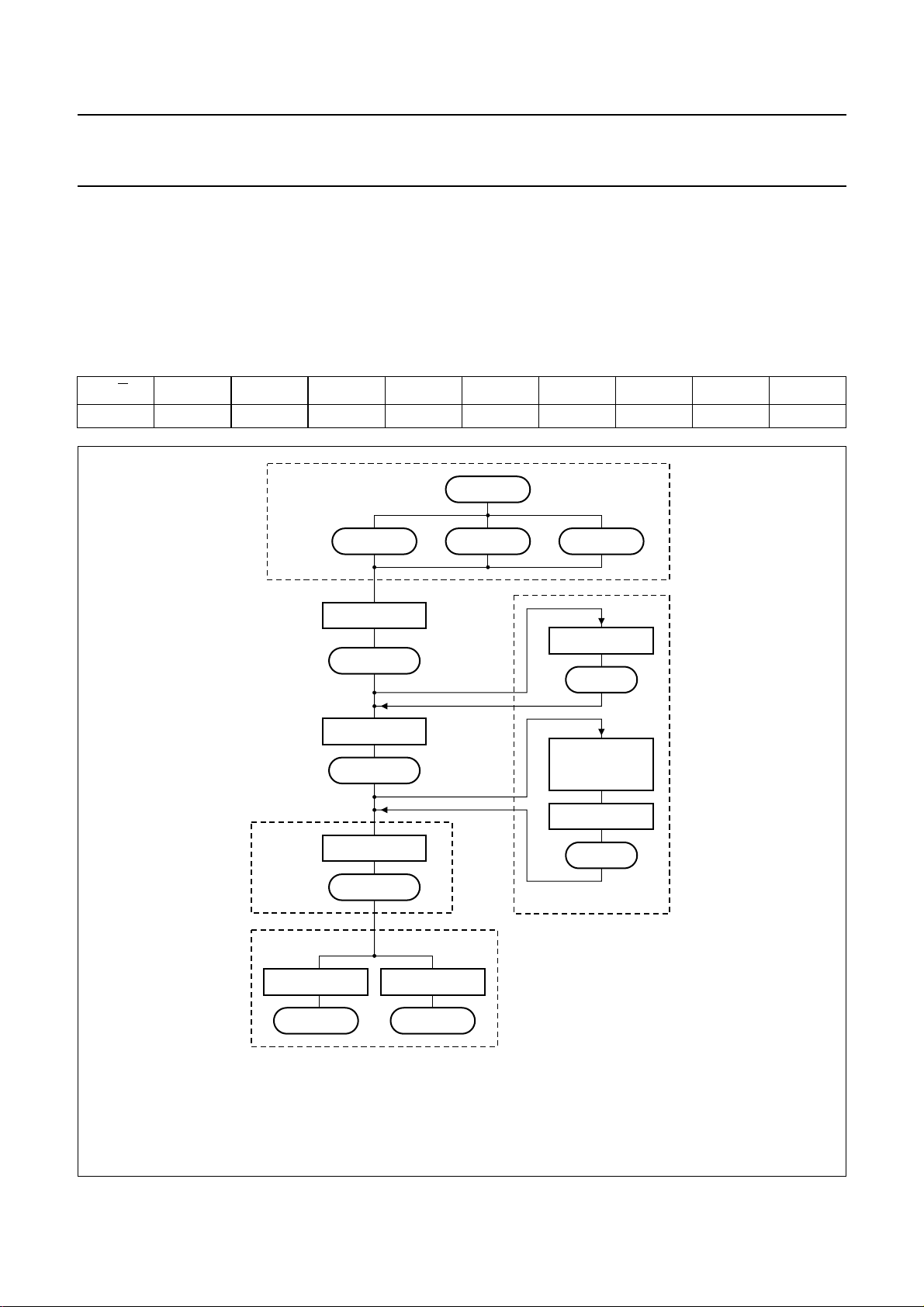

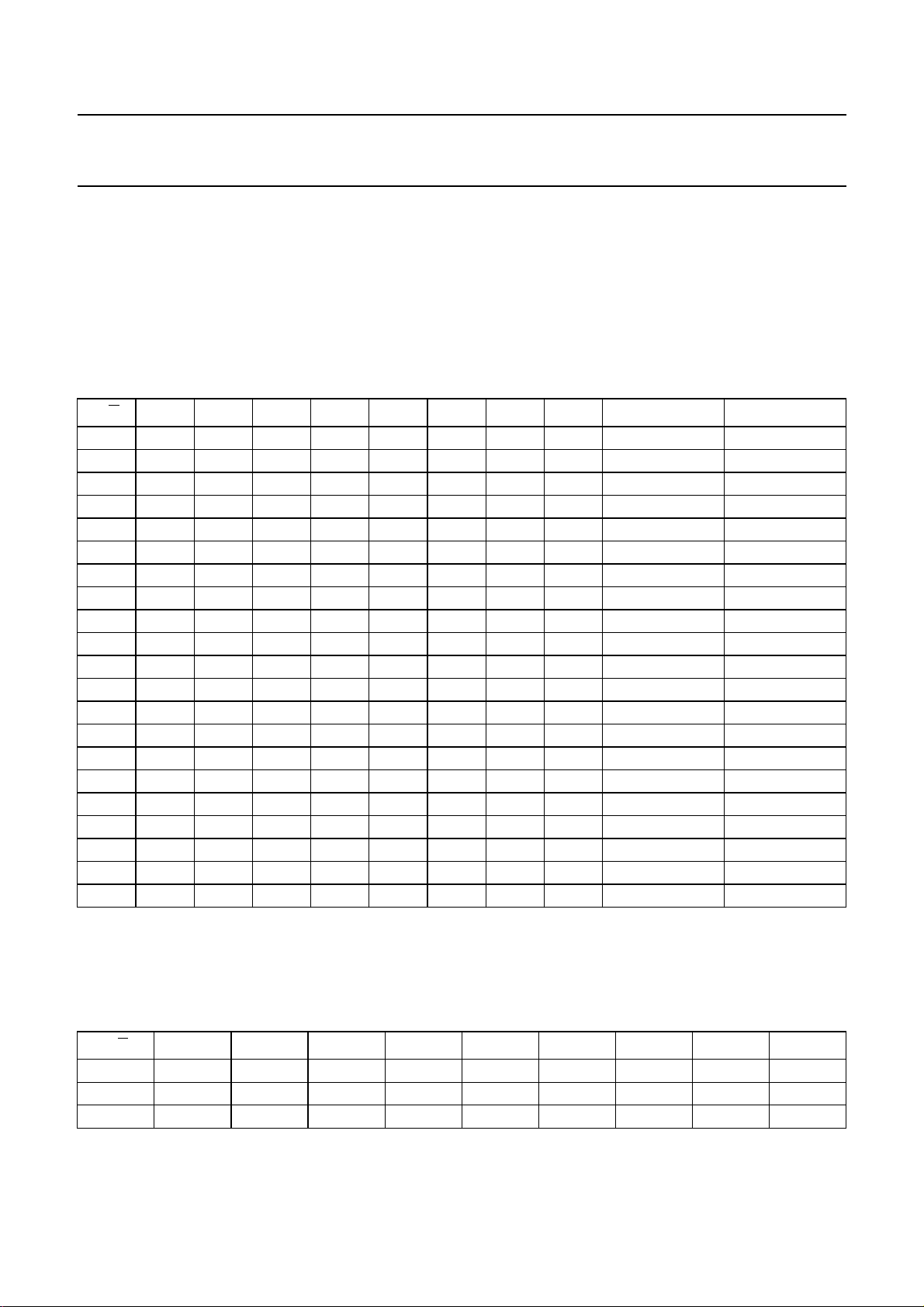

Figure 3 shows two sequences for using the BSTRON

command, assuming BSTROFF and DISPOFF were set

before sending Sleep_OUT.In sequence A the command

to switch the display on (DISPON) issent to the PCF8833

before the BSTRON command is sent. Therefore the

display will only be switched on when the LCD supply

generation circuitgenerates a stable V

. Insequence B

LCD

the RDDST command is used to monitor the LCD supply

generation circuit and, after the D31 bit of the RDDST is

set to logic 1, the DISPON command will be sent;

see Section 6.2.7.

For the effect of possible combinations of commands

Sleep_IN/Sleep_OUT and BSTRON/BSTROFF; see

Table 17 and Fig.4. Figure 7 shows the effects of the

combination of commands BSTRON and BSTROFF with

DISPON and DISPOFF.

generation circuits are stable.

Table 7 Booster voltage on register bits

D/C76543210DEFAULT

00000001103H

handbook, full pagewidth

LCD will be switched on

start

send Sleep_OUT 11H

send DISPON 29H

send BSTRON 03H

when LCD supply

generation circuit

is stable

end

sequence A

Fig.3 Booster voltage on flow charts.

2003 Feb 14 16

start

send Sleep_OUT 11H

send BISTRON 03H

monitor D[31

RDDST 09H

send DISPON 29H

sequence B

]

D31 = 1

end

D31 = 0

MGU912

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.6 READ DISPLAY IDENTIFICATION INFORMATION The Read Display Identification Information (RDDIDIF)

command returns a 24-bit display identification

information. The identification information is valid only

5 ms after applying a hardware reset. Therefore the

RDDIDIF command should not be sent earlier than 5 ms

after a hardware reset.

The input andoutput data format is givenin Table 9. After

the command byte 04H is sent, the read starts with one

dummy clock cycle followed by the 3 status bytes (see

Fig.47).

Table 8 Read display identification information register bits

D/C76543210DEFAULT

0 0000010004H

Table 9 RDDIDIF data format for Serial mode

BIT D/

(S)DIN 0 0 0 0 0 0 1 0 0 04H

(S)DOUT − X (only one dummy clock cycle, not a full byte) X

(S)DOUT − D23 D22 D21 D20 D19 D18 D17 D16 45H

C76543210DEFAULT

− D15 D14 D13 D12 D11 D10 D9 D8 XX

− D7 D6 D5 D4 D3 D2 D1 D0 XX

When less than 25 read clock cycles are sent in Serial

mode, the identification information read must be

interrupted by a hardware reset or rising edge of SCE.

The definition of the display identification bits is given in

Table 11.

Table 10 RDDIDIF data format for Parallel mode

D/

C76543210DEFAULT

0 0000010004H

1 XXXXXXXXXX

1 D23 D22 D21 D20 D19 D18 D17 D16 45H

1 D15 D14 D13 D12 D11 D10 D9 D8 XX

1 D7D6D5D4D3D2D1D0 XX

Table 11 Description of the display identification bits

BIT BIT DESCRIPTION RD BYTE REMARK

D[23:16] manufacturer ID RDID1 hard wired = 45H

D15 driver/module ID

(STN B/W = 0 and

STN Colour = 1)

D[14:8] driver/module version ID

D[7:0] driver/module code RDID3

Note

1. RDID3 will be programmed in OTP cells. This ID can be set to 03H by the module maker.

RDID2 OTP programmed;

see Chapter 15

(1)

OTP programmed;

see Chapter 15

2003 Feb 14 17

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.7 READ DISPLAY STATUS The Read Display Status (RDDST) command returns a

32-bit display status information and can be accessed

when the PCF8833 is in normal Display mode (see

Section 6.2.11), in partial Display mode (see

Section 6.2.23) or in Sleep_IN mode; see Section 6.2.8.

The input and output data format is as follows: After the

command byte 09H is sent, the read starts with one

dummy clock cycle followed by the 4 status bytes (see

Fig.48).

Table 12 Read display status register bits

D/C76543210DEFAULT

00000100109H

Table 13 RDDST data format for Serial mode

BIT D/

(S)DIN 00000100109H

(S)DOUT − X (only one dummy clock cycle, not a full byte) XX

(S)DOUT − D31 D30 D29 D28 D27 D26 0 0 XX

C76543210DEFAULT

− 0 D22 D21 D20 D19 D18 D17 D16 XX

− D15 0 D13 D12 D11 D10 D9 0 XX

− 00000000XX

When less than 33 read clock cycles are sent in Serial

mode the status read must be interrupted by a hardware

reset or a rising edge of SCE.

The definition of the display statusbits isgiven inTable 11.

Table 14 RDDST data format for Parallel mode

D/C76543210DEFAULT

00000100109H

1 XXXXXXXXXX

1 D31 D30 D29 D28 D27 D26 0 0 XX

1 0 D22 D21 D20 D19 D18 D17 D16 XX

1 D15 0 D13 D12 D11 D10 D9 0 XX

100000000XX

2003 Feb 14 18

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

Table 15 Display identification bits description

BIT BIT DESCRIPTION STATUS

D31 booster voltage status logic 1 when BSTRON is selected and when the

LCD supply generation circuits are ready

logic 0 when BSTROFF is selected or when the

LCD supply generation circuits are not ready

D30 Yaddress order logic 1 when MY = 1

logic 0 when MY = 0

D29 X address order logic 1 when MX = 1

logic 0 when MX = 0

D28 vertical/horizontal addressing mode logic 1 when V = 1

logic 0 when V = 0

D27 line address order logic 1 when LAO = 1

logic 0 when LAO = 0

D26 RGB/BGR order logic 1 when RGB = 1

logic 0 when RGB = 0

D[25:23] no function, but can be read D[25:23] = 000

D[22:20] interface pixel format see Section 6.2.30

P2 = D22; P1 = D21 and P0 = D20

D19 Idle mode logic 1 when IDMON is selected

logic 0 when IDMOFF is selected

D18 Partial mode logic 1 when PTLON is selected

logic 0 otherwise

D17 Sleep_IN/OUT logic 1 when Sleep_OUT is selected

logic 0 when Sleep_IN is selected

D16 normal Display mode logic 1 when NORON is selected

logic 0 otherwise

D15 vertical Scroll mode logic 1 when SEP is selected

logic 0 otherwise

D14 no function; but can be read D14 = 0

D13 display inversion logic 1 when INVON is selected

logic 0 when INVOFF is selected

D12 all pixels on logic 1 when DAL is selected

logic 0 otherwise

D11 all pixels off logic 1 when DALO is selected

logic 0 otherwise

D10 display on/off logic 1 when DISPON is selected

logic 0 when DISPOFF is selected

D9 tearing effect line on/off logic 1 when TEON is selected

logic 0 when TEOFF is selected

D[8:0] no function; but can be read D[8:0] = 0:0000:0000

2003 Feb 14 19

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.8 SLEEP_IN By sending the Sleep_IN command, the PCF8833

immediatelyenters the Power-downmode,also referredto

as theSleep mode. In the Sleepmode the outputvoltages

of all LCD driver pins (rows and columns) are at V

SS1

(ground, all pixels are in off state), and the LCD supply

generation circuit and the oscillator are switched off. The

While in Sleep_IN mode all commands and data can be

sent and will be executed as in the Sleep_OUT state,

except some OTP related commands and temperature

readout related commands. In the Sleep_IN mode no

effect on the display can be seen.

The Sleep_IN mode is exited by command Sleep_OUT;

see Section 6.2.9.

Sleep_IN command does not change the state of the

DISPON/DISPOFF and BSTRON/BSTROFF commands,

but has the same effect as DISPOFF and BSTROFF;

see Table 17.

Table 16 Sleep_IN register bits

C76543210DEFAULT

D/

00001000010H

Table 17 Sleep_IN/OUT and BSTR_ON/OFF combination

BSTER_ON/BSTER_OFF Sleep_IN/Sleep_OUT

Booster

(1)

ON ON ON

ON OFF OFF

OFF ON OFF

OFF OFF OFF

Note

1. Booster is the built-in DC-to-DC converter also called voltage multiplier or charge pump.

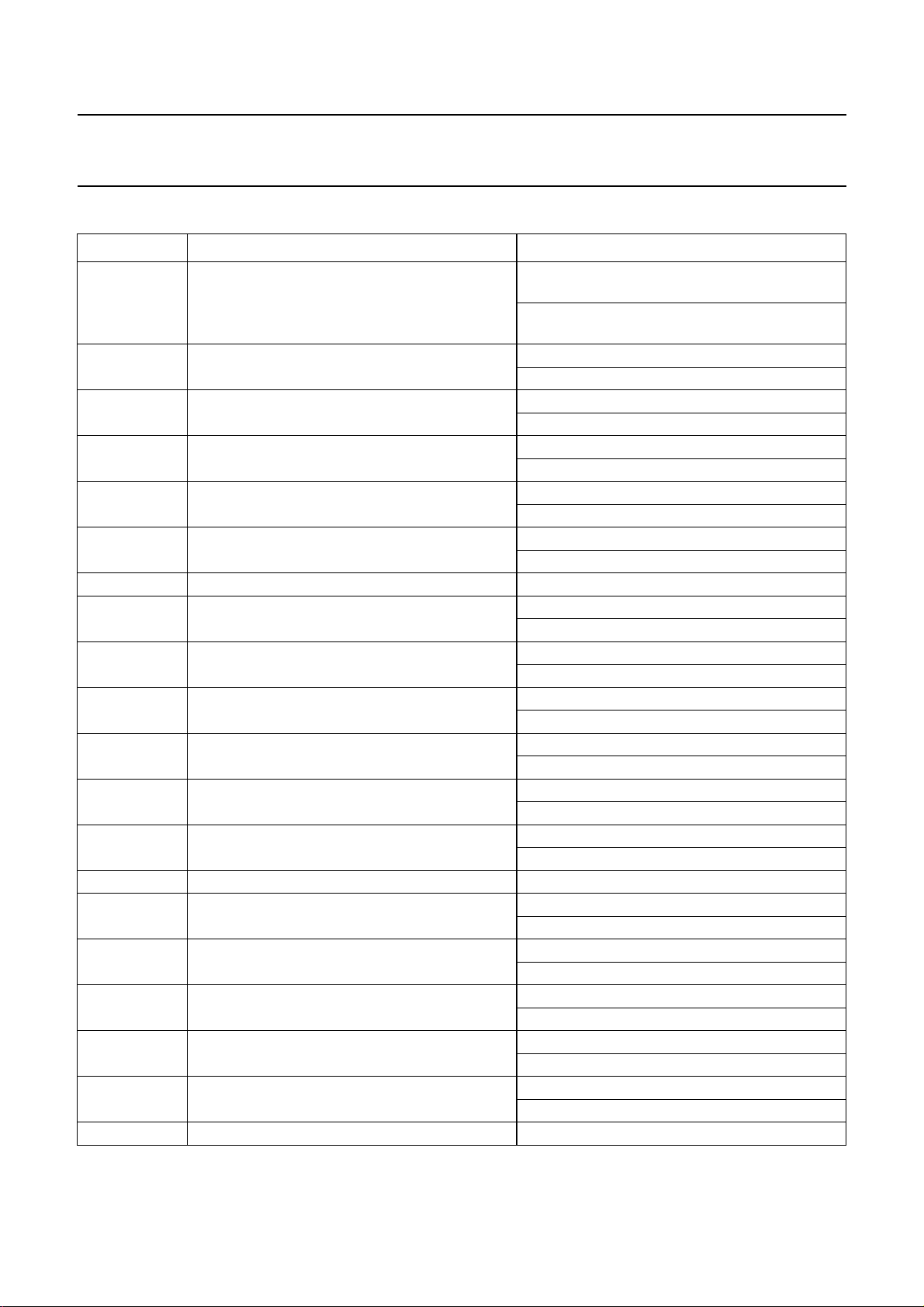

6.2.9 SLEEP_OUT This command must be sent to allow the PCF8833 to

power-up (see Fig.4).

DISPON and BSTRON areset with a reset, the PCF8833

will start-up with Sleep_OUT followingthe built-in start-up

sequence which generates the requested voltages and

switches on the display, unless DISPOFF and/or

BSTROFF was sent after the last reset.

For the effects of possible combinations of commands

Sleep_IN/Sleep_OUT and BSTRON/BSTROFF; see

Table 17.

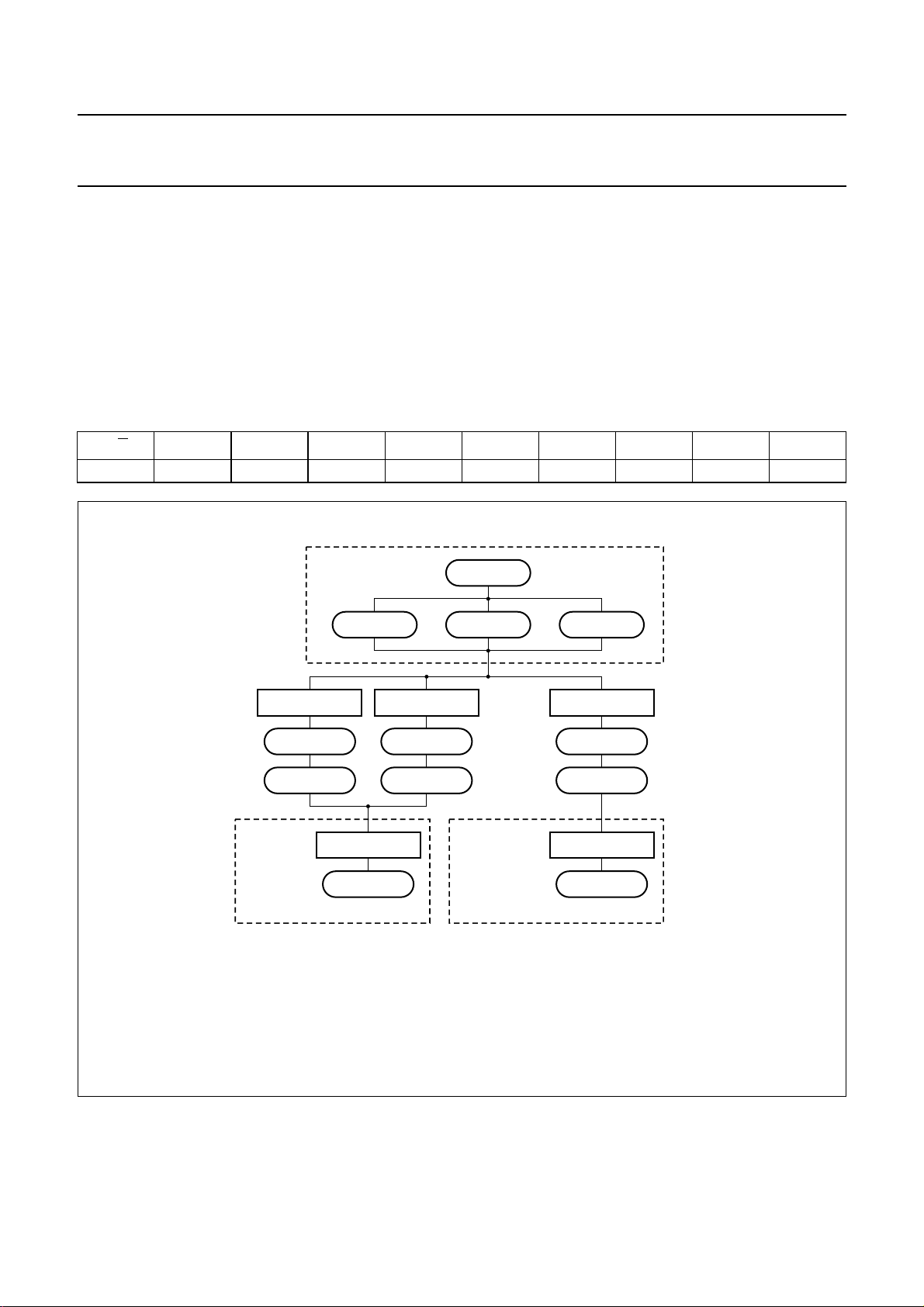

Figure 4 illustratesthe flow when sendingthe Sleep_OUT

command. The display is only switched on, when the

internally generated voltage V

is high enough.

LCD2

This time is self adapting and therefore dependent on

application conditions:

• It is longer for:

– Low V

DD2

– Higher resistors in supply wires and/or external

capacitors

– Higher external capacitors

– Higher required V

LCD2

voltage.

• Some other conditions, which may affect start-up time

are:

– Partial/full mode

– Selected bias system

– Temperature

– Selected temperature coefficients.

2003 Feb 14 20

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

Table 18 Sleep_OUT register bits

D/C76543210DEFAULT

00001000111H

handbook, full pagewidth

D31 = 0

ready

reset

HW or SW

Sleep_IN

D31 = 0

send Sleep_OUT

Sleep_OUT

booster

BSTRON

booster on

wait for D31 bit

D31 = 1

display

DISPON

display on display off

BSTROFF

DISPOFF

D31 is the booster voltage status bit; see Section 6.2.7.

Fig.4 Start-up, when leaving Power-down mode (i.e. after sending Sleep_OUT).

2003 Feb 14 21

MGU913

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.10 PARTIAL MODE ON

Partial mode on (PTLON) turns on the partial Display

mode.Only onepartialdisplay sizecanbe chosen.Normal

mode, Scroll mode, DALO and DAL are exited with this

command. When sending DAL after PTLON, only the

Anormal Displaymodecommand isusedto exitthe Partial

mode. Howthe partial displayarea can be programmed is

given in Section 6.2.23.

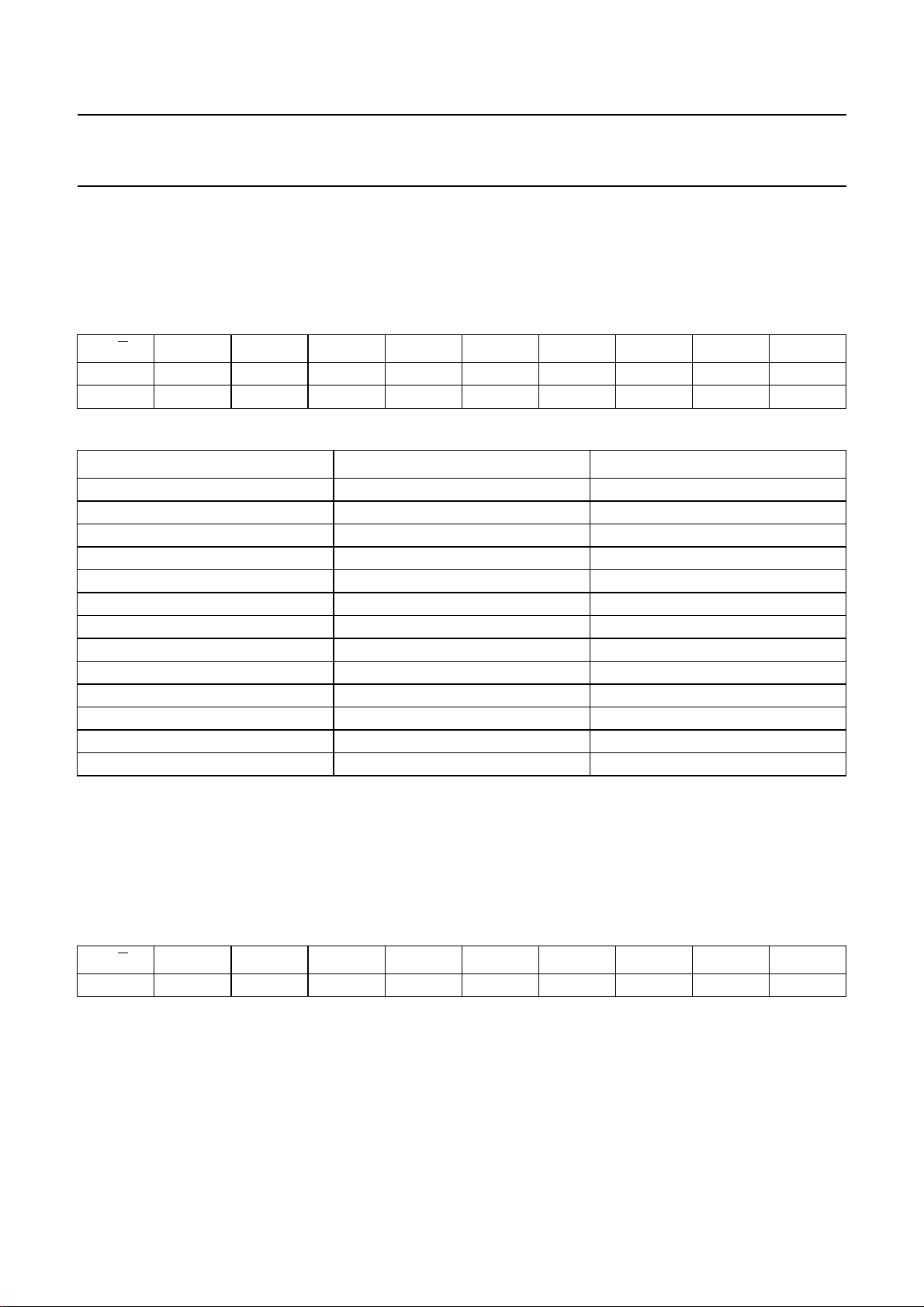

A sequence showing how the command PTLON can be

used is illustrated in Fig.5.

pixels of partial area are driven on.

Table 19 Partial mode on register bits

D/C76543210DEFAULT

00001001012H

handbook, full pagewidth

Initial state

(1)

Sleep_OUT

display on normal displaybooster on

send PTLAR

send DISPOFF

partial area def

display off

send PTLON

wait until

partial mode on

optional

send PTLAR

partial area def

exit partial mode

send NORON send SEP

normal display scroll mode

(1) If theinitial state is Sleep_IN, the same sequenceis valid, butSleep_OUT has to be sentto see theeffect on the display (afterdisplay voltage has

settled).

When sending DALafter PTLON, onlythe pixels ofpartial area are driven on. When sending INVON, in Partial mode only the pixels of partial area are

inverted. INVON is over-ruled by DAL and DALO. Pixels outside partial area always stay off.

display supply

voltage is settled

send DISPON

display on

optional

MGU914

Fig.5 Sequence how PTLON can be used.

2003 Feb 14 22

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.11 NORMAL DISPLAY MODE ON The normal Display mode on command (NORON) turns the display into Normal mode which is also the reset state. An explanation of how the command NORON can be used is illustrated in Fig.6.

Table 20 Normal Display mode on register bits

D/

CD7D6D5D4D3D2D1D0DEFAULT

00001001113H

6.2.12 D

ISPLAY INVERSION OFF

The Display inversionoff command (INVOFF) turns thedisplay into a non-inverted screen without modifying the display

data RAM. Display inversion off is the reset state of the PCF8833.

Table 21 Display inversion off register bits

C76543210DEFAULT

D/

00010000020H

6.2.13 D

ISPLAY INVERSION ON

The Displayinversion on command(INVON) turns thedisplay into an inverted screen without modifying the display data

RAM. The RAM data is read out and inverted while writing to the display.

The display Inversion mode can be switched off by sending the INVOFF command; see Section 6.2.12.

When sending INVON, in Partial mode only, the pixels of a partial area are inverted. INVON is overruled by DAL and

DALO. In Partial mode the pixels outside of the partial are always off.

Table 22 Display inversion on register bits

C76543210DEFAULT

D/

00010000121H

6.2.14 A

LL PIXELS OFF

The All pixels off command (DALO) can be switched off by sending the normal display on command (NORON) (see

Section 6.2.11) or by sending the partial Display mode on command (PTLON); see Section 6.2.10. Furthermore DALO

is left with the command DAL; see Section 6.2.15. When DALOis active all pixels are driven,as if the display RAM was

filled with all zeros (off-state). DALO does not change the data stored in the display RAM. Figure 6 illustrates how DAL

(all pixels on) and DALO (all pixels off) can be used.

All pixels will be switched off regardless of the display data RAM.

Table 23 All pixels off register bits

D/

C76543210DEFAULT

00010001022H

2003 Feb 14 23

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.15 ALL PIXELS ON The All pixels on command (DAL) can be switched off by

sending the normal display on command (NORON); (see

Section 6.2.11) or by sendingthe partial Display mode on

command(PTLON); see Section 6.2.10.FurthermoreDAL

is left with thecommand DALO;see Section 6.2.14.When

DAL is active all pixels are driven, as if the display RAM

was filled with all ones (on-state). DAL does not change

When sending DAL after PTLON, only the pixels of the

partial areaare driven on.When sending INVON in Partial

mode only the pixels of the partial area are inverted.

INVON is over-ruled by DAL andDALO. Pixelsoutside the

partial are always off. Figure 6 illustrates how DAL (all

pixels on) and DALO (all pixels off) can be used.

All pixels will beswitched onregardless ofthe displaydata

RAM.

the data stored in the display RAM.

Table 24 All pixels on register bits

D/C76543210DEFAULT

00010001123H

handbook, full pagewidth

Initial state

(1)

Sleep_OUT

display on all pixel on/offbooster on

send SEP

exit pixel on/off

scroll mode on normal display partial mode on

send DAL/DALO

all pixel on/off

effect in

full display mode

(1) If theinitial stateis Sleep_IN, thesame sequenceis valid, but Sleep_OUThas to besent tosee the effect on the display (afterdisplay voltage

has settled).

When sending DAL after PTLON, only thepixels of partial area aredriven on. When sending INVON,in Partialmode only thepixels ofpartial area

are inverted. INVON is over-ruled by DAL and DALO. Pixels outside partial area always stay off.

send NORON

exit pixel on/off

effect in

partial display mode

send PTLON

exit pixel on/off

send DAL/DALO

all pixel on/off

MGU915

Fig.6 Flowchart representation of DAL and DALO.

2003 Feb 14 24

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.16 SET CONTRAST Usingthe Setcontrast command(SETCON) theV

ofthe VCON[6:0]register onthe V

programmingis explainedin Section 6.2.31.The VCON[6:0]is atwos complement

LCD

number; see Table 26. An overview over the complete programming range of V

voltageand thecontrast ofthe LCDcan beadjusted. The influence

LCD

can be found in Section 15.1.

LCD

Table 25 Set contrast register bits

D/C76543210DEFAULT

00010010125H

1 X VCON

VCON

6

VCON

5

VCON

4

VCON

3

VCON

2

VCON

1

00H

0

Table 26 Possible VCON values

VCON[6:0] DECIMAL EQUIVALENT V

OFFSET

LCD

0111111 63 2520 mV

0111110 62 2480 mV

0111101 61 2440 mV

:::

0000010 2 80 mV

0000001 1 40 mV

0000000 0 0 mV

1111111 −1 −40 mV

1111110 −2 −80 mV

:::

1000010 −62 −2480 mV

1000001 −63 −2520 mV

1000000 −64 −2560 mV

6.2.17 D

The Display off command (DISPOFF) connects all rows and columns to V

ISPLAY OFF

, i.e. all the pixels have a voltage of 0 V.

SS1

Since the reset state of the PCF8833 is Sleep_IN (see Section 6.2.8) the display will be in the off state after a reset.

The DISPOFF command can be switched off by sending the Display on command (DISPON); see Section 6.2.18.

Figure 7 shows the effects of the combination of commands BSTRON and BSTROFF with DISPON and DISPOFF.

Table 27 Display off register bits

D/

C76543210DEFAULT

00010100028H

6.2.18 D

ISPLAY ON

Using the Display on command (DISPON) the rows and columns are driven according to the current display data RAM

content and according to the display timing and settings.

The DISPON command is used to exit the DISPOFF state; see Section 6.2.17.

Figure 4 givesadditional information on the effectof the DISPON/DISPOFFcommand. Figure 7 showsthe effects of the

combination of commands BSTRON and BSTROFF with DISPON and DISPOFF.

2003 Feb 14 25

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

Table 28 Display on register bits

D/C76543210DEFAULT

00010100129H

handbook, full pagewidth

Initial state

Booster off

Booster on

Sleep_OUT

send DISPOFF

display off

send BSTROFF

(2)

D31 = 0

booster off

send BSTRON

booster on

display onbooster on

(1)

D31 = 0

(1) When an external V

mode (Partial mode, Scroll mode, etc.) is not affected by sending DISPON/DISPOFF.

(2) D31 is the booster voltage status bit; see Section 6.2.7.

is applied, BSTROFF needs to be sent after reset (default = booster on). The setting of Display

LCD

wait for D31 bit

D31 = 1

send DISPON

display on

MGU916

Fig.7 Recommendation for using commands BSTRON/BSTROFF in combination with DISPON/DISPOFF.

2003 Feb 14 26

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.19 COLUMN ADDRESS SET The display data RAM parameters xs and xe define the column address range of the display data RAM for writing data.

Parameters xs and xe are defined between 0 and 131 (83H), and xs must be smaller then xe.

Table 29 Column address set register bits

D/C76543210DEFAULT

0001010102AH

1 xs[7] xs[6] xs[5] xs[4] xs[3] xs[3] xs[3] xs[0] 02H

1 xe[7] xe[6] xe[5] xe[4] xe[3] xe[2] xe[1] xe[0] 81H

6.2.20 P

The display data RAM parameters ys[7:0] and ye[7:0] define the page (row) address range of the display data RAM for

writing data. Parameters ys and ye are defined between 0 and 131 (83H), and ys must be smaller then ye.

Table 30 Page address set register bits

6.2.21 M

Data written tothe displaymemory (RAM)is validatedby theMemory write(RAMWR) command.Entering thiscommand

always returns the page address and columnaddress to the start addresses xs[7:0] and ys[7:0] respectively.Content of

the display data RAM is written by the data entered following this command, with the page and/or column address

automatically incremented.The data Writemode turned onby this commandcan be automaticallycancelled by entering

another command.

After a power-up the display RAM contentis undefined. Neither a hardwarereset nor a softwarereset changes the data

stored in display RAM. Sending display data must stop 160 ns before issuing a hardware reset, otherwise the last word

written to the display RAM may be corrupted.

Table 31 Memory write register bits

AGE ADDRESS SET

D/

C76543210DEFAULT

0001110112BH

1 ys[7] ys[6] ys[5] ys[4] ys[3] ys[3] ys[3] ys[0] 02H

1 ye[7] ye[6] ye[5] ye[4] ye[3] ye[2] ye[1] ye[0] 81H

EMORY WRITE

D/

C76543210DEFAULT

0001011012CH

1 D7D6D5D4D3D2D1D0XX

2003 Feb 14 27

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.22 COLOUR SET With the Colour set (RGBSET) command the mapping from the 256-colour interface data is translated to the 4 kbyte

colour RAM dataof the PCF8833 can be changed. The translation tablemust be changed, if necessary,before sending

256 colour data. For the red and green pixel 8 from the available 16 grey scales can be selected. For the blue pixel 4

from the 16 grey scales can be selected. The default or reset state of the colour mapping can be found in Table 32.

If the 256-to-4 kbyte colourmapping needsto bechanged, the wholetable mustbe sent.The mapping of colours isdone

when writing data into the RAM, through the application of the Look-Up Table (LUT).

Table 32 Colour set register bits

C D7 D6 D5 D4 D3 D2 D1 D0 DEFAULT DESCRIPTION

D/

000101101 2DH

1 X X X X R3 R2 R1 R0 00H red tone 000

1 X X X X R3 R2 R1 R0 02H red tone 001

1 X X X X R3 R2 R1 R0 04H red tone 010

1 X X X X R3 R2 R1 R0 06H red tone 011

1 X X X X R3 R2 R1 R0 09H red tone 100

1 X X X X R3 R2 R1 R0 0BH red tone 101

1 X X X X R3 R2 R1 R0 0DH red tone 110

1 X X X X R3 R2 R1 R0 0FH red tone 111

1 X X X X G3 G2 G1 G0 00H green tone 000

1 X X X X G3 G2 G1 G0 02H green tone 001

1 X X X X G3 G2 G1 G0 04H green tone 010

1 X X X X G3 G2 G1 G0 06H green tone 011

1 X X X X G3 G2 G1 G0 09H green tone 100

1 X X X X G3 G2 G1 G0 0BH green tone 101

1 X X X X G3 G2 G1 G0 0DH green tone 110

1 X X X X G3 G2 G1 G0 0FH green tone 111

1 X X X X B3 B2 B1 B0 00H blue tone 00

1 X X X X B3 B2 B1 B0 04H blue tone 01

1 X X X X B3 B2 B1 B0 0BH blue tone 10

1 X X X X B3 B2 B1 B0 0FH blue tone 11

6.2.23 P

ARTIAL AREA

The Partialarea command (PTLAR) sets thepartial display areaand displaysthe RAM contentof this area.In thepartial

Display mode the drive voltage can be reduced.

Table 33 Partial area register bits

D/

C76543210DEFAULT

00011000030H

1 AA1S

1 AA1E

AA1S

7

AA1E

7

AA1S

6

AA1E

6

AA1S

5

AA1E

5

AA1S

4

AA1E

4

AA1S

3

AA1E

3

AA1S

2

AA1E

2

AA1S

1

1

AA1E

0

0

tbf

tbf

2003 Feb 14 28

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

The following steps must be followed to enter the Partial

mode:

• Set VOP (when the MMOTP cells are used the VOP for

the Partial mode is predefined)

• Set bias system (when the MMOTP cells are used the

bias system for the Partial mode is predefined)

• Set start address ofactive areaAA1S[7:0]; canbe set in

multiples of 4

• Set end address of active area AA1E[7:0] + 1; can be

set in multiples of 4

• Enter Partial mode (PTLON).

handbook, full pagewidth

AA1S[7:0] = 4

32

rows

AA1E[7:0] +1 = 36

RAM display

When setting the addresses the following conditionsmust

be ensured:

• (AA1E + 1) − AA1S = 32(only 1 partial display size

setting is possible)

• AA1 ≥ 0 and AA1E ≤ 131.

Figure 8 shows how to use the Partial mode with Line

Address Order (LAO) set to logic 0. Figure 9 gives an

example of Partial mode with LAO set to logic 1, and

Fig.10 shows the position of thepartial areawhen thestart

address of the active area is AA1S ≥ (131 + 1) − 31, i.e.

AA1S ≥ 101 (AA1S must be set in multiples of 4).

Figure 11 shows how the Partial mode can be used.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

ROW 0

ROW 1

ROW 2

ROW 3

ROW 4

ROW 5

ROW 6

ROW 7

ROW 8

ROW 9

ROW 10

ROW 11

ROW 12

ROW 13

ROW 24

ROW 25

ROW 26

ROW 27

ROW 28

ROW 29

ROW 30

ROW 31

ROW 32

ROW 33

ROW 34

ROW 35

ROW 36

ROW 37

ROW 38

ROW 39

ROW 40

ROW 41

ROW 42

partial areapartial area

Fig.8 Partial Display mode for LAO = 0.

2003 Feb 14 29

127

128

129

130

131

ROW 127

ROW 128

ROW 129

ROW 130

ROW 131

MGU917

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

AA1E[7:0] +1 = 128

32

rows

AA1S[7:0] = 96

RAM display

0

1

2

3

4

5

6

7

8

9

10

11

12

13

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

127

128

129

130

131

ROW 0

ROW 1

ROW 2

ROW 3

ROW 4

ROW 5

ROW 6

ROW 7

ROW 8

ROW 9

ROW 10

ROW 11

ROW 12

ROW 13

ROW 24

ROW 25

ROW 26

ROW 27

ROW 28

ROW 29

ROW 30

ROW 31

ROW 32

ROW 33

ROW 34

ROW 35

ROW 36

ROW 37

ROW 38

ROW 39

ROW 40

ROW 41

ROW 42

ROW 127

ROW 128

ROW 129

ROW 130

ROW 131

partial areapartial area

MGU918

Fig.9 Partial Display mode for LAO = 1.

2003 Feb 14 30

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

AA1E[7:0] +1 = 28

AA1S[7:0] = 128

32

rows

RAM display

0

1

2

3

4

5

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

127

128

129

130

131

ROW 0

ROW 1

ROW 2

ROW 3

ROW 4

ROW 5

ROW 27

ROW 28

ROW 29

ROW 30

ROW 31

ROW 32

ROW 33

ROW 34

ROW 35

ROW 36

ROW 37

ROW 38

ROW 39

ROW 40

ROW 41

ROW 42

ROW 43

ROW 44

ROW 45

ROW 46

ROW 47

ROW 48

ROW 49

ROW 50

ROW 51

ROW 52

ROW 53

ROW 127

ROW 128

ROW 129

ROW 130

ROW 131

partial areapartial area

MGU919

Fig.10 Partial Display mode for LAO = 0 and AA1S[7:0] = 128.

2003 Feb 14 31

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

Initial state

optional

exit partial mode

(1)

send PTLAR

partial area def

send PTLON

partial mode on

send PTLAR

partial area def

Sleep_OUT

display on normal displaybooster on

send DISPOFF

display off

wait until

display supply

voltage is settled

send DISPON

display on

optional

MGU920

send NORON send SEP

normal display scroll mode

(1) If the initial state is Sleep_IN, the same sequence is valid, but Sleep_OUT has to be sent to see the effect on the display (after the display

voltage has settled).

When sending DAL after PTLON, only thepixels of partial area aredriven on. When sending INVON,in Partialmode only thepixels ofpartial area

are inverted. INVON is over-ruled by DAL and DALO. Pixels outside partial area always stay off.

Fig.11 Recommended sequence for setting Partial mode.

2003 Feb 14 32

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

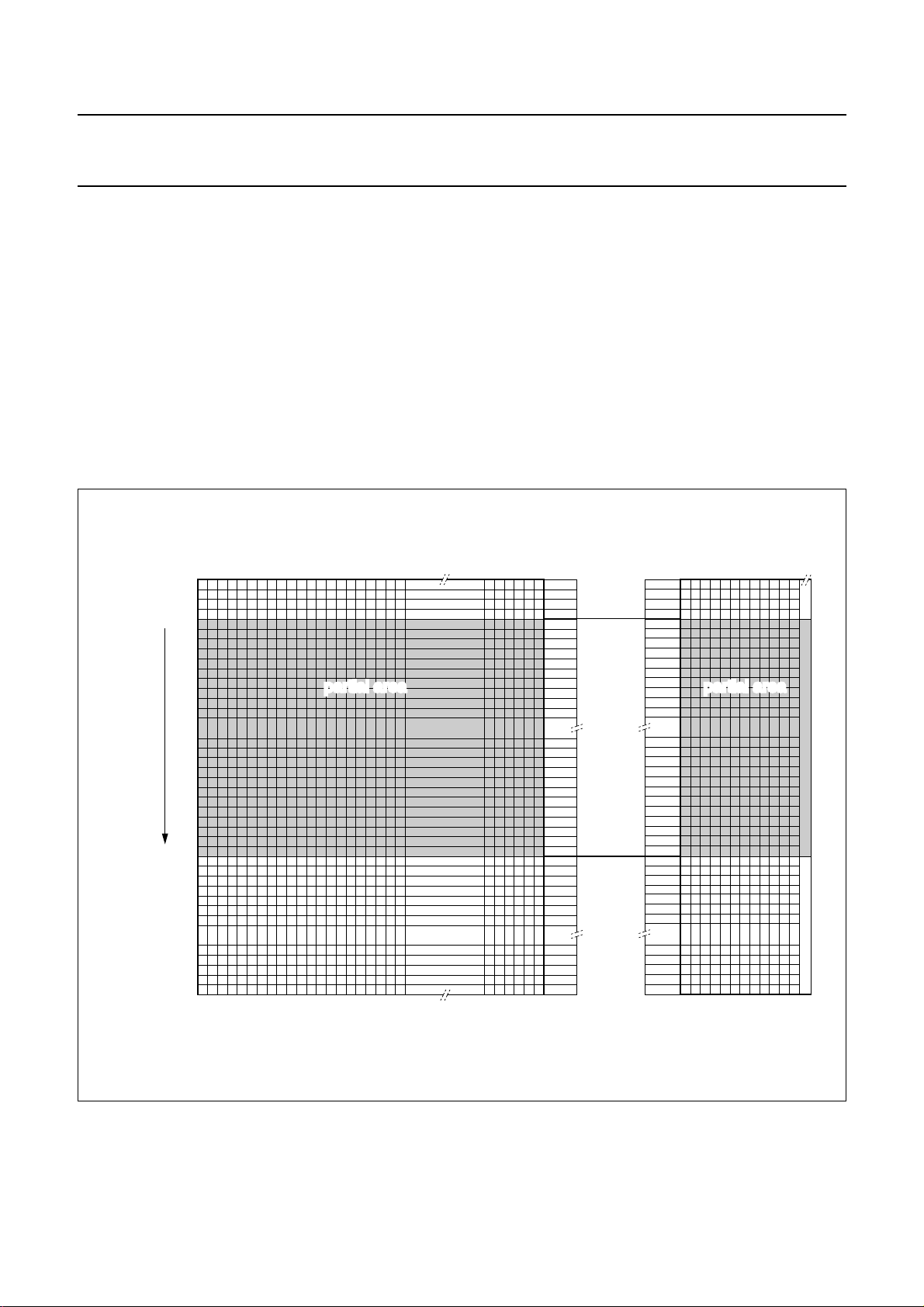

6.2.24 VERTICAL SCROLLING DEFINITION In thePCF8833 three differentscrolling modes can be used.These scrolling modesdiffer from eachother in theway the

RAM to display mapping is done. The vertical scrolling is defined as follows:

• Vertical scrolling definition (VSCRDEF) command

• TF[7:0] defines the number of lines for the top fixed area on the display, there is no top fixed area when TF[7:0] = 0

• SA[7:0] defines the number of lines for the scrolling area on the display

• BF[7:0] defines the number of lines for the bottom fixed area on the display, there is no bottom fixed area when

BF[7:0] = 0.

Figure 12 illustrates the 4 scrolling configurations that can be defined.

Table 34 Vertical scrolling definition register bits

D/C76543210DEFAULT

00011001133H

1TF

1SA

1BF

7TF6

7SA6

7BF6

TF

SA

BF

5

5

5

TF

SA

BF

4

4

4

TF

SA

BF

3

3

3

TF

SA

BF

2

2

2

TF

SA

BF

1

1

1

TF

SA

BF

0

0

0

00H

82H

00H

handbook, full pagewidth

centre screen scroll bottom screen scroll top screen scroll whole screen scroll

Fixed area (RAM content displayed)

Scrolling area

Fig.12 Scrolling modes on the display.

There are 3 different scrolling modes, which are selected as follows:

1. TF + SA + BF = 130 rolling Scroll mode; see Section 6.2.24.1

2. TF + SA + BF = 131 non-rolling Scroll mode; see Section 6.2.24.2

3. TF + SA + BF = 132 non-rolling Scroll mode; see Section 6.2.24.3.

The recommended sequence for setting up the scroll modes is illustrated in Fig.13.

MGU921

2003 Feb 14 33

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

Initial state

set a new scroll area

(1)

Sleep_OUT

display on

send VSCRDEF

scroll area def

send SEP

scroll mode on

send NORON

normal display

send VSCRDEF

scroll area def

normal displaybooster on

send SEP

scroll mode on

exit scroll mode

send NORON

normal display partial mode

(1) If theinitial state isSleep_IN, the same sequence isvalid, but Sleep_OUThas to besent to see the effect on the display(after the

display voltage has settled).

send PLTON

MGU922

Fig.13 Recommended sequence for setting up Scroll modes.

2003 Feb 14 34

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.24.1 Rolling Scroll mode

The RAM-to-display mapping for the rolling Scroll mode

when a 132 × 130 (columns × rows) display is connected

to the PCF8833 is illustrated in Fig.14. In this case rows

0 and 131 must beleft open. When a132 × 132 display is

connected, there will be a one-to-one mapping between

the RAM and the display, and there will be no unused

rows.

The rolling Scroll mode is activated when the Set Entry

Scroll Point (SEP) is set; see Table 35.

Figure 15 gives an example for when the PCF8833 is

working in the rolling Scroll mode.

When the rolling Scroll mode is used the following

sequence can be applied:

• After the desired time interval increment the scroll

address to SEP + n for a n-line step

• Keep incrementing the scroll address (SEP) at regular

intervals.

The rolling Scroll mode is left when the normal Display

mode on (NORON) or the partial Display mode on

(PTLON) is selected.

Table 35 Set entry scroll point register bits

D/C7D6543210DEFAULT

00011011137H

1 SEP7 SEP6 SEP5 SEP4 SEP3 SEP2 SEP1 SEP0 00H

handbook, full pagewidth

]

TF[7:0

RAM (132 x 132)

display (132 x 130)

0

1

2

3

4

5

6

7

8

0

0

1

2

3

4

5

6

7

8

TF[7:0

]

]

SA[7:0

121

2 unused

rows

BF[7:0

]

122

123

124

125

126

127

128

129

130

131

Fig.14 RAM to display mapping for the rolling Scroll mode (TF + SA + BF = 130) for LAO = 0.

2003 Feb 14 35

120

121

124

125

126

127

128

129

130

131

131

MGU923

SA[7:0

BF[7:0

]

]

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

TF = 8

2 unused

rows

BF = 8

RAM (132 x 132) display (132 x 130)

0

1

2

3

4

5

6

7

8

]

SEP[7:0

121

122

123

124

125

126

127

128

129

130

131

SEP

120

121

SEP−1

124

125

126

127

128

129

130

131

131

MGU924

0

0

1

2

3

TF = 8

4

5

6

7

SA = 114

8

9

BF = 8

Fig.15 The rolling Scroll mode (TF + SA + BF = 130) for LAO = 0.

2003 Feb 14 36

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.24.2 Non-rolling Scroll mode

The RAM-to-display mapping for the non-rolling Scroll

mode when a 132 × 130 (columns × rows) display is

connected to the PCF8833 is illustrated in Fig.16. In this

case unused rows and columns are to be left open, for

instance row 0 and 131. If a 132 × 132 display is

connected to the PCF8833 the content of row 0 and 131

will bethe sameas the contentwhich isdisplayed in row 1

and 130, respectively. By doing so, the display data RAM

will have 1 row in the background, whose content can be

updated when it is not displayed.

The non-rolling Scroll mode is activated when the Set

Entry Scroll point is set; see Table Fig.36.

An example is given in Figure 17 for the case when the

PCF8833 is working in the non-rolling Scroll mode

(TF + SA + BF = 131).

When the non-rolling Scroll mode is used the following

sequence can be applied:

• Fill the background memory

• After the desired time interval increment the scroll

address to SEP + n for a n-line step

• Keep filling the background memory and incrementing

scroll address (SEP) at regular intervals to obtain a

smooth scrolling.

Thenon-rolling Scrollmodeis leftwhenthe normalDisplay

mode on (NORON) or the partial Display mode on

(PTLON) is selected.

Table 36 Set entry scroll point register bits

D/C76543210DEFAULT

00011011137H

1 SEP7 SEP6 SEP5 SEP4 SEP3 SEP2 SEP1 SEP0 00H

handbook, full pagewidth

]

TF[7:0

]

SA[7:0

1 buffer

row

1 unused

row

]

BF[7:0

RAM (132 x 132)

display (132 x 130)

120

121

124

125

126

127

128

129

130

131

131

MGU925

0

0

1

2

3

4

5

6

7

8

TF[7:0

SA[7:0

BF[7:0

]

] −

1

]

0

1

2

3

4

5

6

7

8

121

122

123

124

125

126

127

128

129

130

131

Fig.16 RAM to display mapping for the non-rolling Scroll mode (TF + SA + BF = 131) for LAO = 0.

2003 Feb 14 37

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

TF = 8

1 buffer row

1 unused row

BF = 8

RAM (132 x 132) display (132 x 130)

0

1

2

3

4

5

6

7

8

]

SEP[7:0

121

122

123

124

125

126

127

128

129

130

131

SEP

121

122

SEP−2

124

125

126

127

128

129

130

131

131

MGU926

0

0

1

2

3

4

5

6

7

8

9

TF = 8

SA − 1 = 114

BF = 8

Fig.17 The non-rolling Scroll mode (TF + SA + BF = 131) for LAO = 0.

6.2.24.3 Non-rolling Scroll mode

The RAM-to-display mapping for the non-rolling Scroll

mode when a 132 × 130 (columns × rows) display is

connected to the PCF8833 is illustrated in Fig.18. In this

case unused rows and columns are to be left open, for

instance row 0 and 131. If a 132 × 132 display is

connected to the PCF8833 the content of row 0 and 131

will be the same as the content which is displayed in row

1 and 130,respectively. Bydoing sothe displaydata RAM

will have2 rows in the background,whose content can be

updated when they are not displayed.

The non-rolling Scroll mode is activated when the Set

Entry Scroll Point is set; see Table Fig.37.

Figure 19 shows an example for when the PCF8833 is

working in the non-rolling Scroll mode

(TF + SA + BF = 132).

When the non-rolling Scroll mode is used the following

sequence can be applied.

• Fill the background memory

• After the desired time interval increment the scroll

address to SEP + n for a n-line step

• Keep filling the background memory and incrementing

scroll address (SEP) at regular intervals to obtain a

smooth scrolling.

Thenon-rolling Scrollmodeis leftwhenthe normalDisplay

mode on (NORON) or the partial Display mode on

(PTLON) is selected.

2003 Feb 14 38

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

Table 37 Set entry scroll point register bits

D/C76543210DEFAULT

00011011137H

1 SEP7 SEP6 SEP5 SEP4 SEP3 SEP2 SEP1 SEP0 00H

handbook, full pagewidth

]

TF[7:0

]

SA[7:0

2 buffer

rows

]

BF[7:0

RAM (132 x 132)

display (132 x 130)

120

121

124

125

126

127

128

129

130

131

131

MGU927

0

0

1

2

3

4

5

6

7

8

TF[7:0

SA[7:0

BF[7:0

]

] −

2

]

0

1

2

3

4

5

6

7

8

121

122

123

124

125

126

127

128

129

130

131

Fig.18 RAM to display mapping for the non-rolling Scroll mode (TF + SA + BF = 132) for LAO = 0.

2003 Feb 14 39

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

handbook, full pagewidth

TF = 8

2 buffer rows

BF = 8

RAM (132 x 132) display (132 x 130)

0

1

2

3

4

5

6

7

8

]

SEP[7:0

121

122

123

124

125

126

127

128

129

130

131

SEP

122

123

SEP−3

124

125

126

127

128

129

130

131

131

MGU928

0

0

1

2

3

4

5

6

7

8

9

TF = 8

SA − 2 = 114

BF = 8

Fig.19 The non-rolling Scroll mode (TF + SA + BF = 132) for LAO = 0.

2003 Feb 14 40

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.24.4 Effect of LAO on scroll modes

An exampleof when the PCF8833is working inthe non-rolling Scroll mode(TF + SA + BF = 132) with the Line Address

Order (LAO) bit set to logic 1, is illustrated in Fig.20. The Scroll modes described in Sections 6.2.24.1and 6.2.24.2 also

work on the same principle when the LAO bit is set to logic 1.

handbook, full pagewidth

BF = 8

2 buffer rows

TF = 8

RAM (132 x 132) display (132 x 130)

0

1

2

3

4

5

6

7

8

9

10

]

SEP[7:0

123

124

125

126

127

128

129

130

131

SEP+3

123

SEP−1

SEP

124

125

126

127

128

129

130

131

131

MGU929

0

0

1

2

3

4

5

6

7

8

9

BF = 8

SA − 2 = 114

TF = 8

Fig.20 The non-rolling Scroll mode (TF + SA + BF = 132); with LAO = 1.

2003 Feb 14 41

Philips Semiconductors Objective specification

STN RGB - 132 × 132 × 3 driver PCF8833

6.2.25 TEARING EFFECT LINE OFF The Tearing effect line off (TEOFF) command ties the TE pin LOW.

Table 38 Tearing effect line off register bits