Philips PCF85102C-2, PCF85103C-2 Service manual

INTEGRATED CIRCUITS

DATA SH EET

PCF85102C-2; PCF85103C-2

256 × 8-bit CMOS EEPROMs with

2

I

C-bus interface

Product specification

File under Integrated Circuits, IC12

2000 Feb 15

Philips Semiconductors Product specification

256 × 8-bit CMOS EEPROMs with

2

I

C-bus interface

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

5 DEVICE SELECTION

6 BLOCK DIAGRAM

7 PINNING

7.1 Pin description PCF85102C-2

7.2 Pin description PCF85103C-2

8I

8.1 Bus conditions

8.2 Data transfer

8.3 Device addressing

8.3.1 Remark

8.4 Write operations

8.4.1 Byte/word write

8.4.2 Page write

8.5 Read operations

8.5.1 Remark

2

C-BUS PROTOCOL

PCF85102C-2; PCF85103C-2

9 LIMITING VALUES

10 CHARACTERISTICS

11 I2C-BUS CHARACTERISTICS

12 WRITE CYCLE LIMITS

13 PACKAGE OUTLINES

14 SOLDERING

14.1 Introduction

14.2 Through-hole mount packages

14.2.1 Soldering by dipping or by solder wave

14.2.2 Manual soldering

14.3 Surface mount packages

14.3.1 Reflow soldering

14.3.2 Wave soldering

14.3.3 Manual soldering

15 DEFINITIONS

16 LIFE SUPPORT APPLICATIONS

17 PURCHASE OF PHILIPS I2C COMPONENTS

2000 Feb 15 2

Philips Semiconductors Product specification

256 × 8-bit CMOS EEPROMs with

2

I

C-bus interface

1 FEATURES

• Low power CMOS:

– maximum operating current: 2.0 mA

– maximum standby current 10 µA (at 6.0 V),

typical 4 µA.

• Non-volatile storage of:

– 2 kbits organized as 256 × 8-bit.

• Single supply with full operation down to 2.5 V

• On-chip voltage multiplier

• Serial input/output I2C-bus

• Write operations:

– byte write mode

– 8-byte page write mode

(minimizes total write time per byte).

• Read operations:

– sequential read

– random read.

• Internal timer for writing (no external components)

• Power-on reset

• High reliability by using a redundant storage code

• Endurance: 1000000 Erase/Write (E/W) cycles at

T

=22°C

amb

• 10 years non-volatile data retention time

• Standard industrial pinning (pin 7 not connected)

• Up to sixteen EEPROMs addressable in one I2C-bus

using both PCF85102 and PCF85103 in combination.

PCF85102C-2; PCF85103C-2

2 GENERAL DESCRIPTION

The PCF85102C-2 andPCF85103C-2 (further referred to

as PCF8510xC-2) are 2 kbits (256 × 8-bit) floating gate

Electrically Erasable Programmable Read Only Memories

(EEPROMs). Power consumption is low due to the full

CMOS technology used. The programming voltage is

generated on-chip, using a voltage multiplier.

The PCF8510x-2 is pin compatible to widely used

industrial pinning (pin 7 not connected).

As data bytes are received and transmitted via the serial

I2C-bus, a package using eight pins is sufficient. Up to

sixteen PCF8510xC-2 devices may be connected to the

I2C-bus. This is possible with the introduction of a second

device selection code. Chip select is accomplished by

three address inputs (A0, A1 and A2) for each

PCF8510xC-2 type.

3 QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

I

DDR

I

DDW

I

DDstb

supply voltage 2.5 6.0 V

supply current read f

supply current E/W f

= 100 kHz

SCL

V

= 2.5 V − 60 µA

DD

V

= 6.0 V − 200 µA

DD

= 100 kHz

SCL

V

= 2.5 V − 0.6 mA

DD

V

= 6.0 V − 2.0 mA

DD

standby supply current VDD= 2.5 V − 3.5 µA

= 6.0 V − 10 µA

V

DD

2000 Feb 15 3

Philips Semiconductors Product specification

256 × 8-bit CMOS EEPROMs with

2

I

C-bus interface

4 ORDERING INFORMATION

TYPE

NUMBER

PCF85102C-2P DIP8 plastic dual in-line package; 8 leads (300 mil) SOT97-1

PCF85103C-2P

PCF85102C-2T SO8 plastic small outline package; 8 leads;

PCF85103C-2T

5 DEVICE SELECTION Table 1 Device selection code

SELECTION DEVICE CODE CHIP ENABLE R/W

Bit b7

PCF85102-C 1 0 1 0 A2 A1 A0 R/

PCF85103-C 0 0 1 0 A2 A1 A0 R/

Note

1. The Most Significant Bit (MSB) ‘b7’ is sent first.

NAME DESCRIPTION VERSION

body width 3.9 mm

(1)

b6 b5 b4 b3 b2 b1 b0

PACKAGE

PCF85102C-2; PCF85103C-2

SOT96-1

W

W

2000 Feb 15 4

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2000 Feb 15 5

V

DD

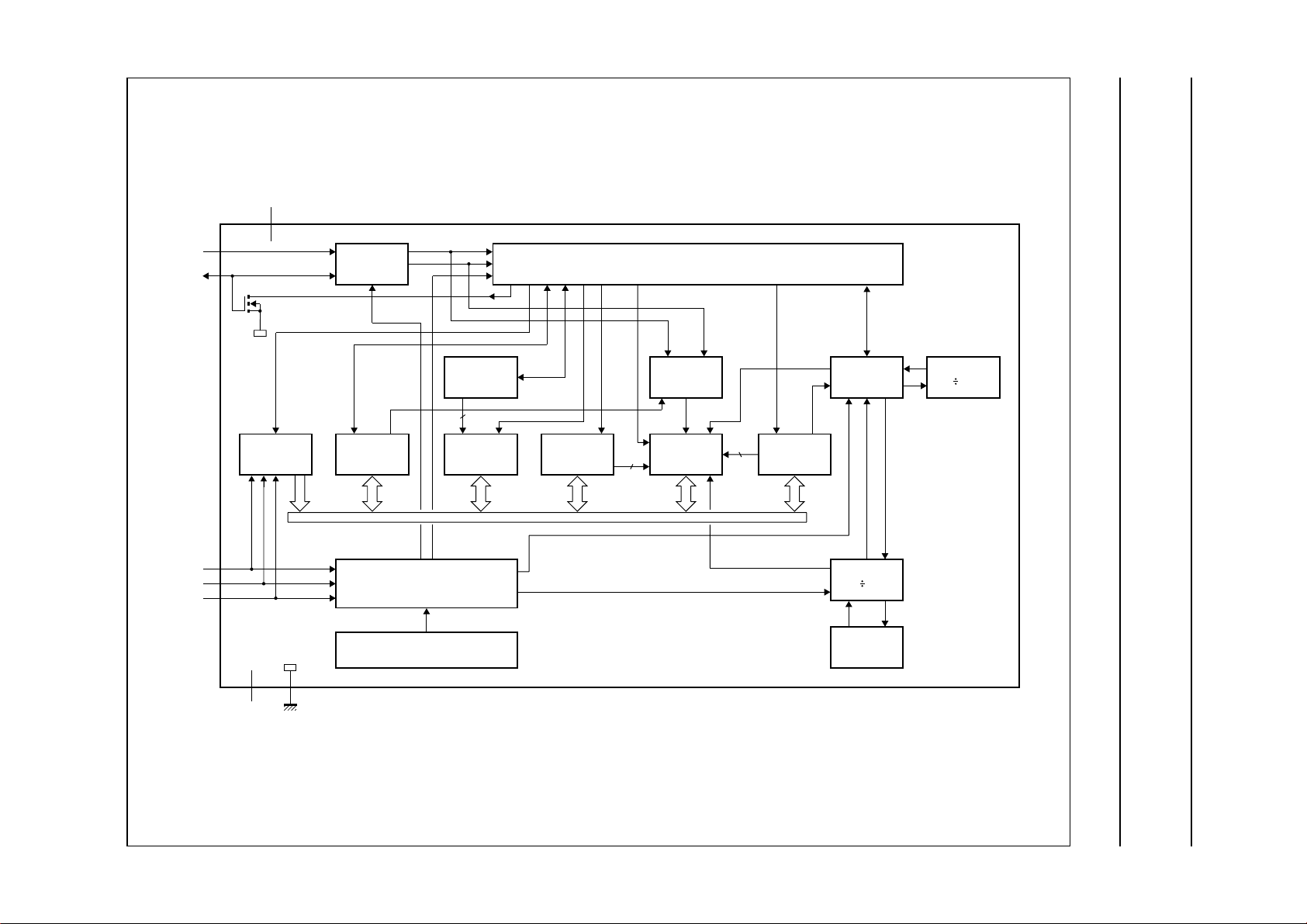

6 BLOCK DIAGRAM

256 × 8-bit CMOS EEPROMs with

I

2

C-bus interface

Philips Semiconductors Product specification

SCL

SDA

A2

A1

A0

6

5

3

2

1

n

ADDRESS

SWITCH

7

n.c.

8

INPUT

FILTER

SHIFT

REGISTER

BYTE

COUNTER

3

BYTE

LATCH

(8 bytes)

ADDRESS

POINTER

2

C-BUS CONTROL LOGIC

I

ADDRESS

HIGH

REGISTER

EEPROM

8

4

EE

CONTROL

SEQUENCER

DIVIDER

( 128)

PCF85102C-2; PCF85103C-2

TEST MODE DECODER

PCF85102C-2;

POWER-ON-RESET

4

V

SS

PCF85103C-2

TIMER

( 16)

OSCILLATOR

MGL967

The pin numbers in this block diagram refer to the PCF85102C-2.

For PCF85103C-2, please see Chapter 7.

Fig.1 Block diagram.

handbook, full pagewidth

Philips Semiconductors Product specification

256 × 8-bit CMOS EEPROMs with

2

I

C-bus interface

7 PINNING

PCF8510xC-2 has standard industrial pinning which will be compatible for most applications.

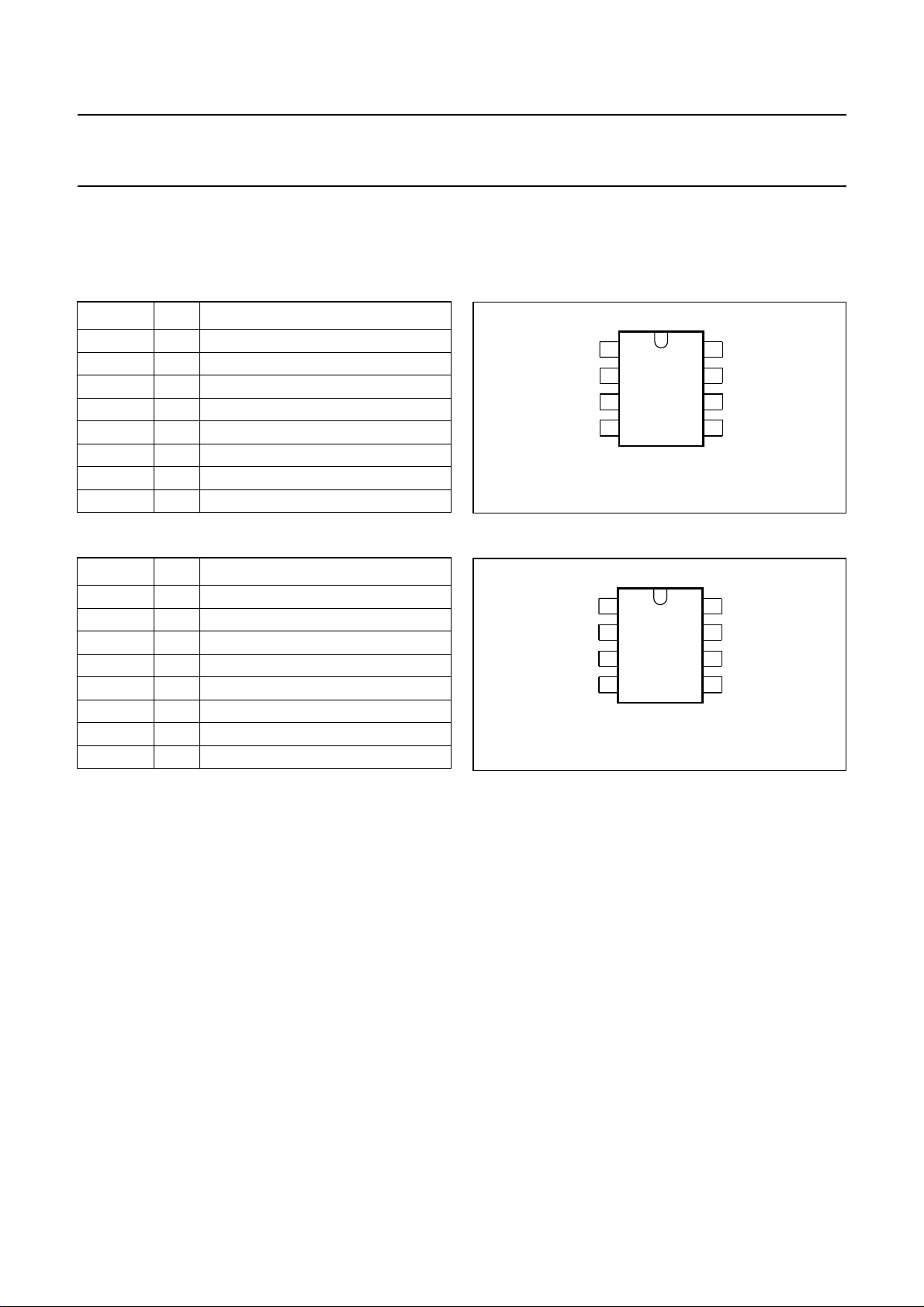

7.1 Pin description PCF85102C-2

SYMBOL PIN DESCRIPTION

A0 1 address input 0

handbook, halfpage

A1 2 address input 1

A2 3 address input 2

V

SS

SDA 5 serial data input/output (I

SCL 6 serial clock input (I

4 negative supply voltage

2

C-bus)

2

C-bus)

n.c. 7 not connected

V

DD

8 positive supply voltage

7.2 Pin description PCF85103C-2

SYMBOL PIN DESCRIPTION

WP 1 address input 0

handbook, halfpage

A1 2 address input 1

A2 3 address input 2

V

SS

SDA 5 serial data input/output (I

SCL 6 serial clock input (I

4 negative supply voltage

2

C-bus)

2

C-bus)

n.c. 7 not connected

V

DD

8 positive supply voltage

PCF85102C-2; PCF85103C-2

1

A0

2

A1

PCF85102C-2

3

A2

V

4

SS

Fig.2 Pin configuration PCF85102C-2.

1

WP

2

A1

PCF85103C-2

3

A2

V

4

SS

Fig.3 Pin configuration PCF85103C-2.

MGL968

MGL969

V

8

DD

n.c.

7

SCL

6

5

SDA

V

8

DD

n.c.

7

SCL

6

5

SDA

2000 Feb 15 6

Loading...

Loading...