Page 1

查询PCF5079供应商

INTEGRATED CIRCUITS

DATA SH EET

PCF5079

Dual-band power amplifier

controller for GSM, PCN and DCS

Product specification

File under Integrated Circuits, IC17

2001 Nov 21

Page 2

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 QUICK REFERENCE DATA

5 BLOCK DIAGRAM

6 PINNING

6.1 Pin description

6.2 Pin configurations

7 FUNCTIONAL DESCRIPTION

7.1 General

7.2 Power-up mode

7.3 OP4 (integrator)

7.4 Start-up and initial conditions

7.5 Home position voltage

7.6 End of burst

7.7 Considerations for ramp-down

7.8 Configurations

7.9 Summary of current and voltage definitions

7.10 Timing

8 LIMITING VALUES

9 ELECTROSTATIC DISCHARGE (ESD)

10 DC CHARACTERISTICS

11 OPERATING CHARACTERISTICS

12 APPLICATION INFORMATION

12.1 Ramp control

12.2 PA protection against mismatch

12.3 Detected voltage measurement

12.4 Application examples

PCF5079

13 PACKAGE OUTLINES

14 SOLDERING (TSSOP10)

14.1 Introduction to soldering surface mount

packages

14.2 Reflow soldering

14.3 Wave soldering

14.4 Manual soldering

14.5 Suitability of surface mount IC packages for

wave and reflow soldering methods

15 SOLDERING (HVSON10)

15.1 Soldering information

15.2 PCB design guidelines

15.2.1 Perimeter pad design

15.2.2 Thermal pad and via design

15.2.3 Stencil design for perimeter pads

15.2.4 Stencil design for thermal pads

15.2.5 Stencil thickness

16 DATA SHEET STATUS

17 DEFINITIONS

18 DISCLAIMERS

2001 Nov 21 2

Page 3

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

1 FEATURES

• Compatible with baseband interface family PCF5073x

• Two power sensor inputs

• Temperature compensation of sensor signal

• Active filter for Digital-to-Analog Converter (DAC) input

• Power Amplifier (PA) protection against mismatching

• Bias current source for detector diodes

• Generation of pre-bias level for PA at start of burst

(home position)

• Compatible with a wide range of silicon PAs

• Compatible with multislot class 12

• Dual output with internal switch

• Two different transfer functions

• Possibility to adapt dynamic transfer functions

• Very small outline package (3 × 3 mm).

PCF5079

2 APPLICATIONS

• Global System for Mobile communication (GSM)

• Personal Communications Network (PCN) systems.

3 GENERAL DESCRIPTION

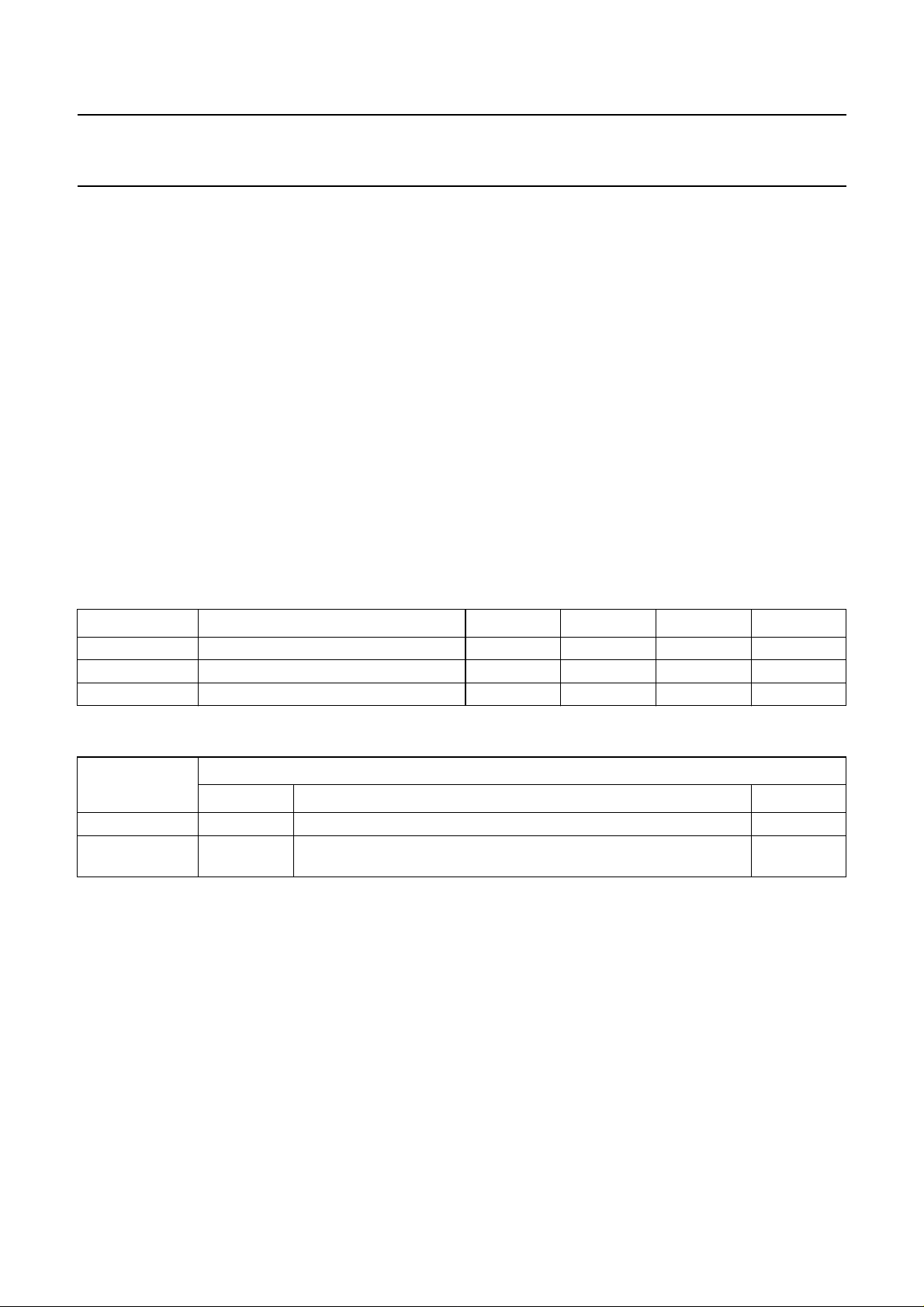

This CMOSdevice integrates an amplifier for the detected

RF voltage from the sensor, an integrator and an active

filter to build a PA control loop for cellular systems with a

small number of passive components.

4 QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DD

I

DD(tot)

T

amb

ORDERING INFORMATION

TYPE NUMBER

PCF5079T/C/1 TSSOP10 plastic thin shrink small outline package; 10 leads; body width 3 mm SOT552-1

PCF5079HK/C/1 HVSON10 plastic, heatsink very thin small outline package; no leads;

supply voltage 2.5 3.6 5.0 V

total supply current −−10 mA

ambient temperature −40 − +85 °C

PACKAGE

NAME DESCRIPTION VERSION

SOT650-1

10 terminals; body 3 × 3 × 0.90 mm

2001 Nov 21 3

Page 4

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

5 BLOCK DIAGRAM

handbook, full pagewidth

S1

C4

OP1

OP1

RF

V

DD

RF

in

I

30 µA

C1

6 pF

C2

6 pF

C3

16.6 pF

10 µA

RF

V

out

10 pF

PU

6

SS

PA

D2

VS2 VS1 VCD1VCG

4523

bias2Ibias1

30 µA

V

V

AUXDAC3

PCF5073x

DD

PU

G = 0.3

V

home

7

VDAC

filter

DD

V

V

DD

SS

PA

in

S5

20 kΩ

BAND GAP

AND CURRENT

REFERENCE

S3S4

R4

10

R1

V

V

DD

SS

D1

10 µA

V

prebias

6 kΩ

VINT(N)

PU

OP4

OP4

OP4

IN

VDAC

CINT1

CINT2

PU

V

DD

RF

out

SF

SF

PU

PU

ref

PCF5079

phases

D

G

D

OP4

D

G

OP4

G

CONTROL

LOGIC

8 9

PU BS

PU/PD

commands

MGT325

PCF5079

Fig.1 Block diagram.

2001 Nov 21 4

Page 5

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

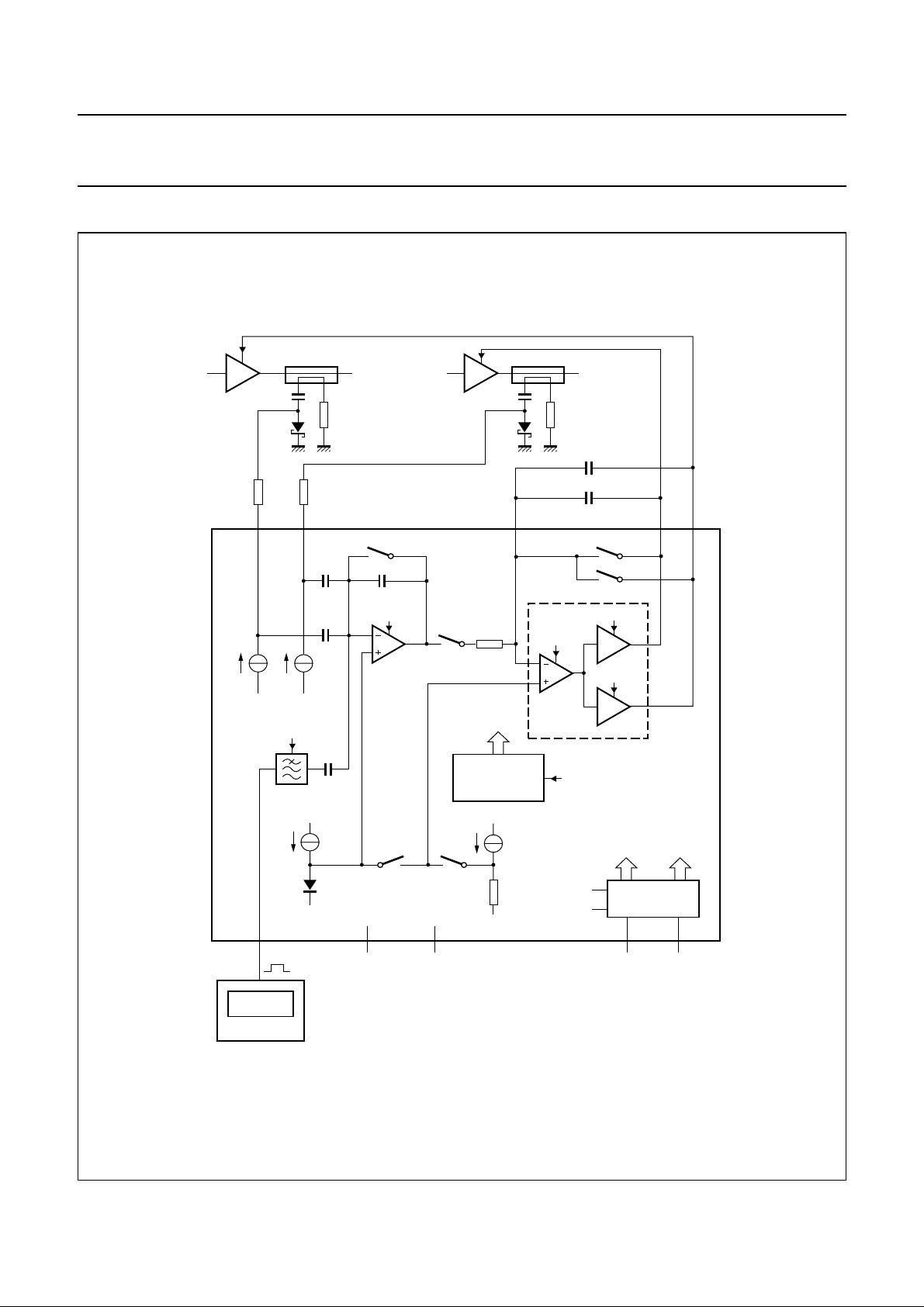

6 PINNING

6.1 Pin description

SYMBOL PIN TYPE

VCG 1 O and A PA control voltage output (GSM)

VINT(N) 2 I and A negative integrator input

VCD 3 O and A PA control voltage (DCS)

VS1 4 I/O and A sensor signal input 1

VS2 5 I/O and A sensor signal input 2

V

SS

6 G reference ground

VDAC 7 I and A DAC input voltage

PU 8 I and D power-up input

BS 9 I and D band selection input

V

DD

10 P positive supply voltage

Note

1. O = output, I = input, I/O = input/output, A = analog, D = digital, P = power supply and G = ground

(1)

DESCRIPTION

PCF5079

6.2 Pin configurations

handbook, halfpage

VCG

VINT(N)

VCD

VS1

VS2

1

2

3

PCF5079T

4

5

MGT326

V

10

DD

9

BS

8

PU

7

VDAC

V

6

SS

Fig.2 Pin configuration (top view) for PCF5079T,

pins are numbered counter-clockwise.

handbook, halfpage

VS2

VS1

VCD

VINT(N)

VCG

5

4

3

PCF5079HK

2

1

6

7

8

9

10

MGU268

Fig.3 Pin configuration (bottom view) for

PCF5079HK, pins are numbered clockwise.

V

SS

VDAC

PU

BS

V

DD

2001 Nov 21 5

Page 6

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

7 FUNCTIONAL DESCRIPTION

7.1 General

The PCF5079 contains an integrated amplifier for the

detected RF voltage from the sensor, an integrator and an

active filter to build up a PA control loop for cellular

systems with a small number of passive components

suitable for dual-band applications. The active band can

be selected by means of the dedicated input BS.

The sensor amplifier can amplify signals from an

RF powerdetector in a range oflessthan−20 to +15 dBm.

This can comply to the PA output power range of

GSM900/1800/1900 systems when, for example, a

directional coupler with 20 dB attenuation is used for

GSM900 and a directional coupler with 18 dB attenuation

is used for GSM1800.

The external Schottky diodes for power detection (sensor)

are biased by an integrated current source of 30 µA.

Variationsof the forwardvoltagewith temperature haveno

influence on the measured signal because they are

cancelled by the switched capacitor amplifier OP1.

An external DAC with at least 10-bit resolution (for

example, AUXDAC3 of baseband interface family

PCF5073x) is necessary to control the loop.

PCF5079

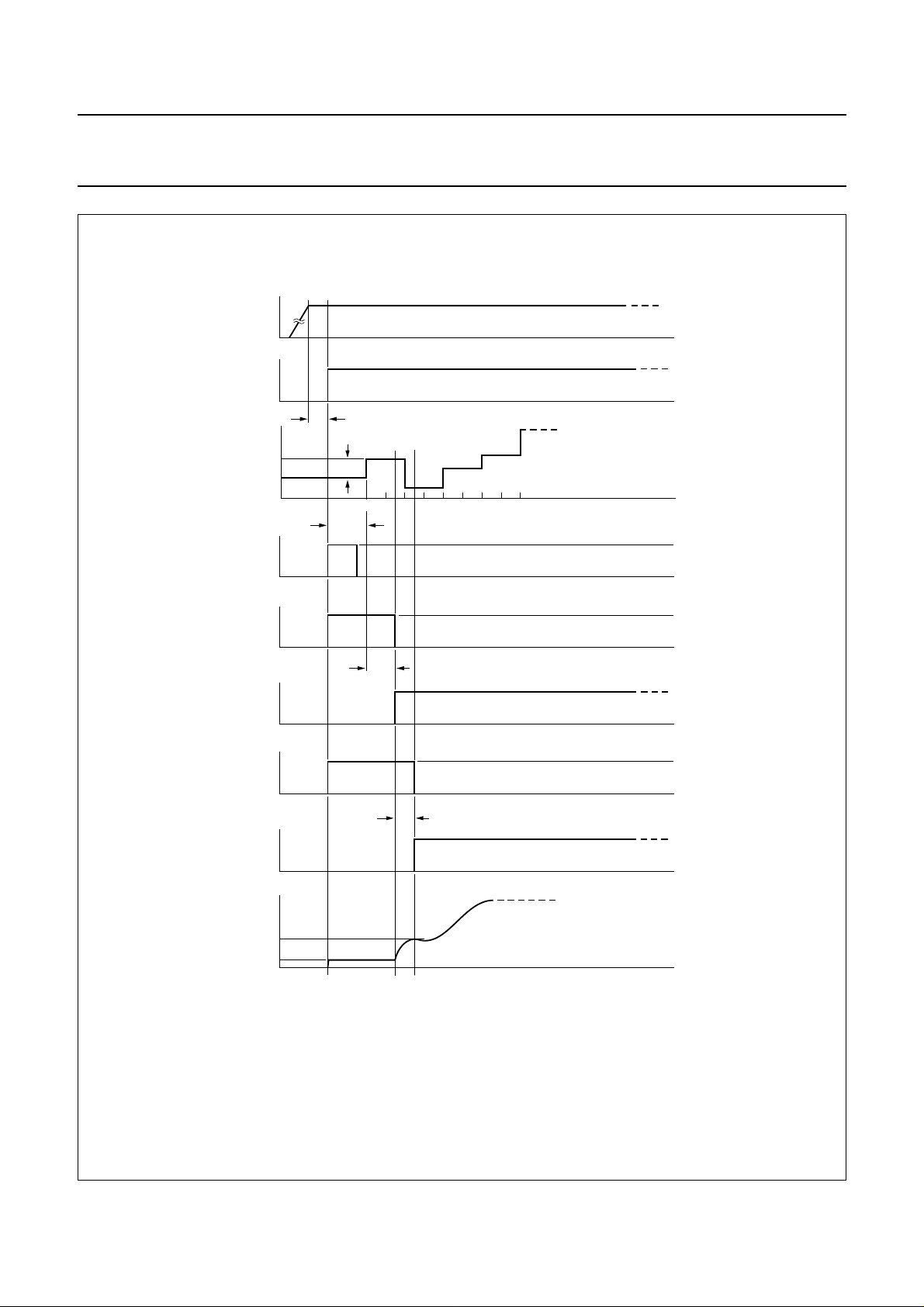

7.4 Start-up and initial conditions

ThePCF5079 is designedto operate in bursts,as required

in TDMA systems. Referring to Fig.4, for each time slot to

be transmitted the PCF5079 must be enabled by setting

signal PU to logic 1. Once pin PU is active, BS is taken

into account to allow correct initialisation of switches S1,

SFD,SFG, S3, S4 and S5, and of the configuration signals

PUG and PUD.

Thefeedback switch across theunuseddriver is kept open

andthe output voltagefromthe unused driveristied to V

to maintain the off state of the unused PA.

When pin PU is set to logic 1, at least 5 µs after VDD has

reacheditsfinal value, switches S1, theappropriateswitch

SFD or SFGand S3 are closed, and switches S4 and S5

are opened. Because switch S1 is closed, the forward

voltage of Schottky diodes D1 and D2 is sampled on

capacitors C1 and C2 respectively.

Moreover, the control voltage on pin VCD or VCG is

initially forced to be at the pre-bias voltage because the

appropriate switch SFDor SFGand S3 are closed, and S4

is opened.

After a fixed time, defined on-chip, switch S1 is opened

and the circuit is ready.

SS

An integrated active filter smooths thevoltage steps of the

DAC during ramp-up and ramp-down.

The operation principle is the same, independently of the

selected standard. The DAC signal and the sensor signal

areadded by amplifierOP1. The voltage differenceof both

signals is integrated by operational amplifier OP4

dedicated to the selected standard, which delivers the

PA control voltage on an external capacitance, CINT1 or

or CINT2, between pins VINT(N) and VCD or VCG,

respectively. The shape of the rising and falling power

burst edges can be determined by means of the DAC

voltage.

7.2 Power-up mode

The device includes a power-up input (pin PU) to switch

the ICon during time slotsthatareused in TDMA systems,

and to switch the IC off during the unused slots to reduce

current consumption.

7.3 OP4 (integrator)

The operational amplifier OP4 (integrator) consists of a

shared input stage, OP4IN and a dedicated output driver

for each standard, OP4G and OP4D. Depending on the

status of input BS, one driveris active andthe other iskept

in power-down mode during active time slots.

Once switch S1 is open, a ramp signal applied at

pin VDAC(at least 20 µsafter the transitionof pin PU from

logic 0 to logic 1)with an amplitude of atleast 70 mV,from

CODE

switch S3 and closing of switch S4 on the home voltage,

with a delay of 3 µs maximum with respect to the ramp.

After switch S3 opens (in a fixed amount of time), the

control voltage on pin VCD or pin VCG rises to the home

position to bias the PA to the beginning of the activerange

of its control curve. During this time (typically 2 µs), the

appropriate switch SFDor SFGremains closed. When the

appropriate switch SFD or SFG is opened, switch S5 is

closed, allowing the transfer of any signal coming from

amplifier OP1. After this preset, the control voltage is free

to increase according to the control loop if the RF input is

enabled (see Fig.12).

For higher DAC ramp steps, the delay of switch S3

opening (S4 closing) is reduced while the delay between

switch SFD(SFG) opening with respect to S3 opening

(S4 closing) remains unchanged.

START

to CODE

, determines the opening of

KICK

2001 Nov 21 6

Page 7

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

handbook, full pagewidth

CODE

CODE

V

V

VDAC

KICK

START

DD

PU

S1

t

>5 µs

d1

>70 mV

t

d2

>20 µs

0

462

8 . . .

time

time

time (QB)

time

PCF5079

closed

open

SFD, SF

V

VCD, VVCG

V

V

prebias

S3

S4

S5

home

closed

open

t

d3

<3 µs

(max)

G

t

d4

2 µs (typ)

time

time

time

time

time

MGT327

closed

open

closed

open

closed

open

The maximum value of CODE

CODE

have to be chosen to get the best ramp shape and spectrum performance.

applied for two quarter-bits ensures a start-up ofthecontrolvoltagewithverylowjitter and high repetitivity. The codes following CODE

START

is limited by the isolation requirement of the PA used in the application. The pulse determined byCODE

START

Fig.4 Start-up and initialization timing diagram.

2001 Nov 21 7

KICK

minus

KICK

Page 8

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

7.5 Home position voltage

Internally, a forward voltage of an on-chip silicon diode is

provided as adefault home position.This voltage matches

the requirements at the control input of most PAs and

exhibits the same temperature coefficient.

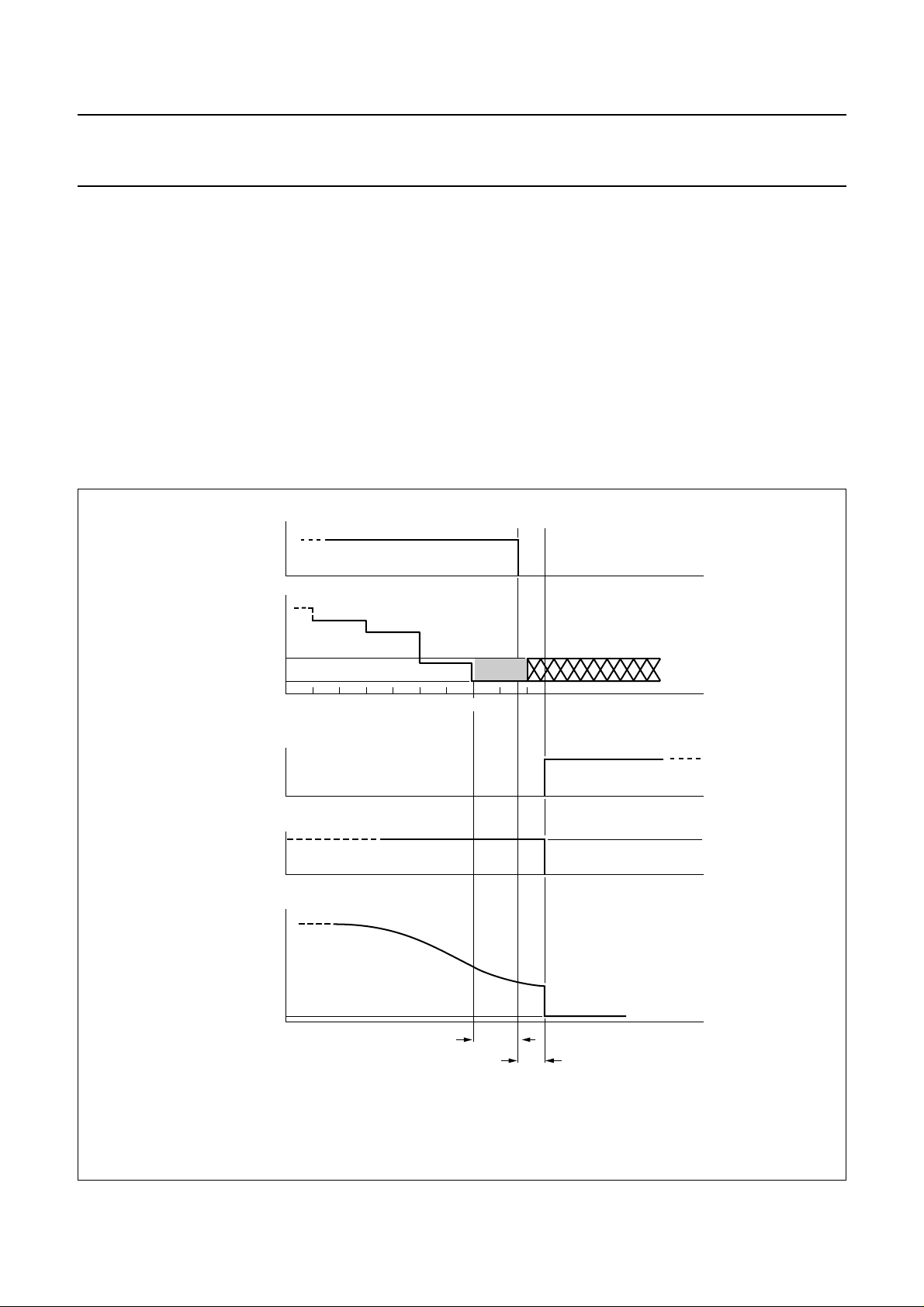

7.6 End of burst

The ramp-down should drive the PA from conduction to

shut off in a controlled way (see Fig.5). To get this result,

correctDACprogramming is required, sothatthelast code

of the DAC ramp-down (CODE

code of theramp-up (CODE

corresponding to the difference between start and end

handbook, full pagewidth

V

VDAC

) is lower than the initial

END

). In thisway, the energy

START

PU

PCF5079

codes, applied for a certain number of Quarter-Bits (QB),

is used to balance the energy stored in thesumming node

duringthe time intervalbetween the start ofcontrol voltage

on pin VCD or VCG ramping-up and the feedback of a

detected ramp to the sensor input. Also a very slow

ramp-down is avoided when the PA switches off and the

loop gain becomes zero.

The amount of energy required at the end of the

ramp-down depends on the overall loop gain and on the

time needed to reach PA conduction from the home

position. At the end of a burst, when pin PU is set to

logic 0, control voltage on pin VCD or VCG is forced

to VSS.

time

CODE

START

CODE

S1, S3

S4, S5

V

VCD, VVCG

END

. . . i−8i−6i−4i−2i

V

SS

(1)

t

A

time (QB)

closed

open

time

closed

open

time

t

d5

<

1 µs

time

MGT328

(1) The exact duration oftAdepends onbothPCF5079 and the application loopcharacteristics.The contribution of PCF5079 isduemainly to the group

delay of the low-pass filter on the VDAC input (see Fig.11).

Fig.5 End of burst timing diagram.

2001 Nov 21 8

Page 9

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

7.7 Considerations for ramp-down

Referring to Fig.5, the i-th code can be programmed to

have either the CODE

code between, depending on the application preferences.

Thesecodes do not produceanypower at the outputofthe

PA, as CODE

START

isolation. The proper conclusion of the ramp-down is

ensured by choosing CODE

discharge of the integration capacitance is controlled until

the control voltage on pin VCD or VCG goes below the PA

conduction threshold and by applying at this time the PU

transition from logic 1 to logic 0.

At the beginning of a burst, the VDACsignal steps applied

at OP1 are not compensated by any signal at the sensor

input up to when pin VCD or VCG voltage is greater than

the PA conduction threshold voltage. In any case, the

initial DAC voltage steps are stored in the capacitance of

amplifier OP1. CODE

energy inside the shaded zone cancels the energy

accumulated in the summing node (OP1) at the start of a

burst and not balanced by a feedback signal at the sensor

input.

The exact value of the energy required depends on the

specific PA, on the characteristics of the overall loop and

on the values chosen for the settable parameters inside

the loop.

A rough idea can be derived with a simplified analysis of a

ramp-up, ramp-down cycle using the following

simplifications:

• The starting conditions for OP1 and OP4 are biasing at

V

with zero charge on capacitances

home

• The initial rising of pin VCD or VCG voltage from V

is caused only by the integration of the constant

CODE

KICK

• VDAC is treated as applied directly at the summing

node, initially neglecting the transmission delay through

the internal low-pass filter.

or CODE

END

value or any

START

has been chosen to keep the PA

< CODE

END

has to be chosen so that the

END

START

so that the

home

PCF5079

Timet

Now, to define the quantity

∆V

the current/voltage equations around the integrator OP4

can be solved by forcing the current through R1 to be

equal to the current through the integration capacitance

and calculating the ∆V generated on C

∆V

where

iτ()

Substituting equation (4) into equation (3)

∆ V

Under the hypothesis the voltage is constant:

∆V

Equation (6) can be used to calculate time t

conduction of the PA is reached, considering that

tt

t

Time t

the PA and by ∆V

the energy contained in the shaded zone (Fig.5)is at least

equal to the energy accumulated at the beginning:

∫

where k is the number of quarter-bits during which

CODE

canbe calculated with theprecedingsimplification.

1

KICK

CINT

CINT

CINT

1

t

1

V

0

CODE

1

--------------C

CINT

×

g

d∆VKICK

=

------------------------------ R1

1

----------------------------C

CINT

1

----------------------------C

CINT

V

1

home

R1 C

×

CINT

depends on the time constant of the integrator, by

1

2

(t) dt = k QB CODE

out

OP1

is applied.

END

CODE

–=

KICK

t

i τ()τd

×=

∫

0

×∆V

R1×

×∆V

R1×

∆V

CINTVconduction

V

conductionVhome

×=

----------------------------------------------g

d

. The condition to be fulfilled is that

KICK

START

, then

INT

t

× dτ=

g

∫

0

g

d

KICK

d

× t×=

KICK

=+⇒=

–

∆V

×

KICK

CODE

××

–()

END

at which the

1

START

(2)

(3)

(4)

(5)

(6)

(7)

(8)

2

(9)

Generally, the integrator OP4 input can be expressed as

V

in integrator()

where g

and gdare respectively the gains of sensor input

s

×g

s

s

∆V

×–=

d

VDAC

(1)

g

∆V

and DAC input in the summing amplifier OP1.

Equation (1) holds for closed loop operation. In the time

interval between therising of pin VCD orVCG voltage due

to CODE

(t = 0) and when V

KICK

conduction

for the PA is

reached(t = t1),∆Vsis 0and operation isopen loop. Inthis

time interval, a charge accumulates in the summing node,

which remains uncompensated.

2001 Nov 21 9

Page 10

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

7.8 Configurations

Table 1 Operating conditions

POWER-UP INPUT (PU) OPERATING MODE

0 disabled; reset

1 enabled

Table 2 Band selection configuration

BAND SELECT

INPUT (BS)

(1)

0 GSM OP4G → active;

1 DCS OP4D → active;

Note

1. BS input has to be set before the PU transition logic 0 to logic 1.

7.9 Summary of current and voltage definitions

Refer to Figs 1, 4 and 12.

BAND DRIVER SWITCHES CONTROL VOLTAGE

OP4D → power-down

OP4G → power-down

→ working;

SF

G

SFD→ open

SFD→ working;

SFG→ open

PCF5079

V

→ working;

VCG

V

→ V

VCD

V

→ working;

VCD

V

→ V

VCG

SS

SS

SYMBOL DESCRIPTION

V

VS1

V

VS2

V

VDAC

V

VCG

V

VCD

V

home

V

prebias

I

bias1

I

bias2

RF

RF

in

out

sensor signal of incident RF power or power sensor 1 signal

sensor signal of reflected RF wave or power sensor 2 signal

DAC voltage

control voltage of PA

control voltage of PA

home position voltage

prebias reference voltage; used at the start-up

bias current for detector diode D1

bias current for detector diode D2

input signal to the power amplifier

output signal from the power amplifier

7.10 Timing

Refer to Figs 4 and 5.

SYMBOL DEFINITION MIN. MAX. UNIT

t

d1

t

d2

t

d3

t

d4

t

d5

delay time; VDD application to PU input transition logic 0 to 1 5.0 −µs

delay time; PU input transition logic 0 to 1 to V

V

ramp-up detection time − 3.0 µs

VDAC

delay time; ramp-up detected to V

VCD

, V

VCG=Vhome

ramp-up 20 −µs

VDAC

− 2.6 µs

delay time; PU input transition logic 1 to 0 to end of burst − 1.0 µs

2001 Nov 21 10

Page 11

Philips Semiconductors Product specification

Dual-band power amplifier controller for

PCF5079

GSM, PCN and DCS

8 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

V

I

V

VS1

V

VS2

I

I

P

tot

V

es

T

stg

T

amb

supply voltage 2.5 +6.0 V

DC input voltage on all pins except VS1 and VS2 −0.5 VDD+ 0.5 V

,

DC input voltage on pins VS1 and VS2 −3.0 VDD+ 0.5 V

DC current into any signal pin −10 +10 mA

total power dissipation

TSSOP10 package − 315

HVSON10 package − 844

electrostatic handling voltage human body model; note 3 2000 − V

machine model; note 4

pins 4 and 5 150 − V

all other pins 200 − V

storage temperature −65 +150 °C

ambient temperature −40 +85 °C

(1)

(2)

mW

mW

Notes

TjT

–

1. Where and the thermal resistance between junction and ambient R

2. Where R

P

tot

th(j-a)

=

amb

----------------------R

th(j-a)

= 77 K/W on JEDEC 2S2P board (100 × 100 mm).

= 206.3 K/W.

th(j-a)

3. Human body model: C = 100 pF; R = 1.5 kΩ.

4. Machine model: C = 200 pF; L = 0.75 µH; R = 0 Ω.

9 ELECTROSTATIC DISCHARGE (ESD)

The PCF5079 is compliant to the General Quality Specification for integrated circuits

“SNW-FQ-611D”

under the stress

condition EDSH (human body) and the stress condition ESDM (machine model).

10 DC CHARACTERISTICS

VDD= 2.5 to 5 V; T

= −40 to +85 °C; unless otherwise specified.

amb

SYMBOL PARAMETER CONDITION MIN. TYP. MAX. UNIT

Supply

V

DD

I

DD(op)

I

DD(idle)

supply voltage 2.5 3.6 5.0 V

total operating current no load on pins VCD or VCG −−10 mA

total idle current no load on pinsVCD or VCG;

−−10 µA

note 1

Logic inputs (pins PU and BS)

V

IL

V

IH

I

LL

LOW-level input voltage 0 − 0.3 V

HIGH-level input voltage VDD= 2.5 to 3.7 V 0.9 − V

V

= 3.7 to 5.0 V 0.95 − V

DD

DD

DD

V

V

LOW-level input leakage current VIL=0V −5 − +5 µA

2001 Nov 21 11

Page 12

Philips Semiconductors Product specification

Dual-band power amplifier controller for

PCF5079

GSM, PCN and DCS

SYMBOL PARAMETER CONDITION MIN. TYP. MAX. UNIT

I

LH

C

I

Sensor inputs and bias current source (pins VS1 and VS2)

V

VS2

V

VS1

I

bias1

I

bias2

TC

Ibias1

TC

Ibias2

Internal home position voltage

V

home

TC

Vhome

Note

1. A resistive load on pins VCD or VCG to ground (VSS) does not result in additional current consumption.

HIGH-level input leakage current VIH= 5.0 V −5 − +5 µA

input capacitance − 10 − pF

input voltage −3 − V

input voltage −3 − V

,

bias current source for detector

diodes D1 and D2

,

temperature coefficient of

I

and I

bias1

bias2

internal home position voltage T

temperature coefficient for V

home

VI=0V; T

V

=2.5V 172839µA

DD

=5.0V 213345µA

V

DD

=25°C; see Fig.6

amb

− 0.07 − mA/K

=25°C 0.550 0.600 0.650 V

amb

−−2.1 − mV/K

DD

DD

V

V

35

handbook, halfpage

I

bias

(µA)

33

31

29

27

2.5 3.5 4.5345

Fig.6 Typical value of I

VDDat T

amb

bias

=25°C.

MGT332

V

(V)

DD

as a function of

2001 Nov 21 12

Page 13

Philips Semiconductors Product specification

Dual-band power amplifier controller for

PCF5079

GSM, PCN and DCS

11 OPERATING CHARACTERISTICS

VDD= 2.5 to 5 V; T

SYMBOL PARAMETER CONDITION MIN. TYP. MAX. UNIT

Integrator (OP4G and OP4D)

V

DD

B

G

supply voltage 2.5 3.6 5.0 V

gain bandwidth CL= 120 pF; note 1 − 4 − MHz

PSRR power supply ripple rejection f = 217 Hz; V

SR

SR

V

O(min)

V

O(max)

pos

neg

positive slew rate VDD= 3 V; note 2 2.0 3.2 − V/µs

negative slew rate VDD= 3 V; note 2 2.0 3.2 − V/µs

minimum output voltage T

maximum output voltage RL= 350 Ω; see Fig.8 0.85VDD−−V

Capacitors C1, C2 and C4

M matching ratio accuracy

between C1, C2 and C4

Low-pass filter for DAC signal (3rd-order Bessel filter)

f

3dB

t

d(group)

corner frequency 70 100 130 kHz

group delay time see Fig.11 1.8 3.0 4.2 µs

= −40 to +85 °C; unless otherwise specified.

amb

amb

= 3 V; note 1 50 55 − dB

DD

= 25 °C; see Fig.7 −−0.2 V

− 1 − %

Notes

1. Guaranteed by design.

2. Slew rates are measured between 10% and 90% of output voltage interval with a load of 40 pF to ground.

0.258

handbook, halfpage

TC

(mV/K)

0.256

0.254

0.252

0.250

2.5 3.5 4.5345

MGT333

V

(V)

DD

13

handbook, halfpage

I

L

(mA)

11

9

7

5

2.5 3.5 4.5345

MGT334

V

(V)

DD

Fig.7 Temperature coefficient of V

O(min)

as a

function of VDD.

2001 Nov 21 13

Fig.8 Minimum load current as a function of VDD.

Page 14

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

handbook, halfpage

V

or V

VCD

VCG

V

DD

0.96

0.92

0.88

0.84

0.80

1

300 1300

500 700 900 1100

MGT335

RL (Ω)

handbook, halfpage

V

or V

VCD

VCG

V

DD

0.9

0.8

0.7

0.6

PCF5079

1

(1)

(2)

(3)

2.5 3.5 4.5345

MGT336

V

(V)

DD

V

= 2.5 V.

DD

or V

V

Fig.9 Minimum as a function

VCD

------------------------------------

of RL.

handbook, halfpage

4

delay

(µs)

3

2

1

VCG

V

DD

MGW101

(1) IL= 6 mA.

(2) IL= 8 mA.

(3) IL=10mA.

or V

V

Fig.10 Minimum as a function

VCD

------------------------------------

of VDD.

VCG

V

DD

0

3

10

4

10

5

10

f (Hz)

6

10

Fig.11 Low-pass filter group delay at pins VCD

and VCG (typical values).

2001 Nov 21 14

Page 15

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

12 APPLICATION INFORMATION

handbook, full pagewidth

RF

out

(dBc)

−10

−20

−30

−40

−50

−60

−70

−80

V

VDAC

typ <0.9V

DD

of PCF5073x

CODE

KICK

CODE

START

V

VCD, VVCG

typ >0.85V

with RL = 350 Ω

PA conduction

DD

threshold

0

−28 −18 −10 0 +543 +553 +561 +571

0246810121416 16+n

nx (2 × QB)

18+n

20+n

22+n

24+n

26+n

28+n

30+n

32+n

time (µs)

CODE

END

CODE

START

time (2 × QB)

PCF5079

(1)

V

prebias

APEDAC3

(PCF5073x)

PU

(PCF5079)

RF

in

(1) The software design must guarantee that CODE

0246810121416 16+n

nx (2 × QB)

>20 µs

is applied before the PU transition from logic 0 to logic 1.

START

18+n

20+n

22+n

24+n

t

A

26+n

(2)

28+n

32+n

30+n

<1 µs

time (2 × QB)

time

time

time

MGT329

(2) The exact duration of tA depends on both PCF5079 and the application loop characteristics. The duration should be long enough to ensure that

V

VCD,VVCG

input (see Fig.11).

is below the PA conduction threshold. The contribution of PCF5079 is mainly due to the group delay of the low-pass filter on the VDAC

Fig.12 Timing diagram for one time slot with PCF5073x family.

2001 Nov 21 15

Page 16

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

handbook, full pagewidth

R1

1 kΩ

RF SECTION

R2

1 kΩ

CINT1

< 50 pF

CINT2

< 50 pF

VCG

VINT(N)

VCD

VS1

VS2

1

2

3

4

5

PCF5079

PCF5079

V

DD

10

BS

9

PU

8

VDAC

7

V

SS

6

0 to 2.3 V

AUXDAC3

PCF5073x

MGT337

Fig.13 Diagram showing external components required.

handbook, halfpage

V

VCD, VVCG

I

L

R

350 Ω

L

120 pF

MGT338

Fig.14 Worst case load on control voltage pins

VCG and VCD.

12.1 Ramp control

CODE

KICK

and V

define the starting conditions for

home

ramping-up. Ramping-up and ramping-down are defined

by V

VDAC

. CODE

and CODE

END

define the correct

START

shut-off of the power module.

The non-linear behaviour of the control curves of the

power modules has a large influence on the loop. Starting

conditions in the flat area of the control curve are critical

and need some attention. Initially the voltage on

pins VCD (VCG) will be at the home position.

Successively, the integrator is moved into the active part

of the control curve.

This is achieved by integrating CODE

KICK

. When

VCD (VCG) voltage has reached the active region of the

control curve, the loop is closed and the circuit can follow

the ramping function generated at pin VDAC. The top

value of VDAC voltage determines the power of the

transmit burst. Ramping-down is started according to the

decrease of VDAC voltage. The loop follows the leading

function for ramping-down until the RF sensor leaves its

active region. The reason for CODE

START

and CODE

END

is to shorten the tail of the slope.

2001 Nov 21 16

Page 17

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

12.2 PA protection against mismatch

High VSWR at the PA output may occur insystems where

the PA is connected to the antenna via couplers and

switcheswith low insertion loss,dependingonthe antenna

matching. The incident and reflected power have to be

monitored and care has to be taken to prevent the

summedRF power doesnotexceed the definedmaximum

value at the PA output.

handbook, full pagewidth

RFin HB

RFin LB

PA

band select

PCF5079

As two sensor inputs are available in the PCF5079, two

different detector signals can be combined: one for direct

path and onefor reflectedpath. These two voltages, fed to

the sensor inputs, are summed inside the PCF5079

resultingin a decrease inthePA output power if thereisan

increase of the VSWR at the antenna port (see Fig.15).

switch

VS1

broad band

coupler

C1

D1 D2

C2

RF

out

VS2

R2R1

MGT330

Fig.15 Example of PA mismatch protection circuit.

Table 3 Table of components (see Fig.15)

SYMBOL COMPONENT DESCRIPTION

D1, D2 detector diode Philips 1PS79SB62

R1, R2 resistor R = 1 kΩ (decoupling versions)

C1, C2 capacitor C = 39 pF

− band select switch Motorola; Alpha Industries; M/A; COM GaAs MMIC; or discrete pin diode,

e.g. Philips BAP51-03

− broad band coupler Murata LCD20 series; TDK HHM 20, 22 series

2001 Nov 21 17

Page 18

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

12.3 Detected voltage measurement

RF GMSK

MODULATED

SIGNAL

GSM: 39 pF

DCS: 8.2 pF

1 kΩ

PCF5079

V

DD

PROBE

MGU223

PCF5079

handbook, full pagewidth

V

10

VS1, VVS2

10

10

1

−1

−2

−20 −15 −10 −5 5 10 15

Fig.16 Set-up for measuring detected voltage for 900 MHz and 1800 MHz working.

(1)

(2)

0

MGU224

Pin (dBm)

(1) DCS.

(2) GSM.

Fig.17 Detected voltage as a function of incident power for 1PS79SB62 detector diodes.

2001 Nov 21 18

Page 19

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

12.4 Application examples

handbook, full pagewidth

PA

MODULE

GSM1800 GSM900

RF

in

RF

PCF5079

in

V

apc

BS

RF

out

R1

0 to 2.3 V

D1D2

R2

VS1VS2

PCF5079

VSSVDAC

AUXDAC3

PCF5073x

VCD

CINT1

VINT(N)VCD

PU BS V

MGT331

109876

12345

VCG

DD

RF

out

Fig.18 Application example of a dual-band PA module with single control input.

2001 Nov 21 19

Page 20

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

outGSM

RF

47 Ω

Murata

LDC15H200J0897

(1)

47 Ω

outDCS

RF

Murata

LDC15H180J1747

PCF5079

MGT757

47 Ω

68 Ω

(1)

TXGSM

8

S1

100 nF

V

HIGH GAIN

S2

100 nF

V

57

12

220 µF

+3.6 V

handbook, full pagewidth

inGSM

RF

39

9

123

4

101114

MODULE

BGY280

UHF AMPLIFIER

6

16

inDCS

RF

pF

TXDCS

C1

V

C2

V

15 13

1 kΩ

1PS79SB62

47 pF47 pF

14

VINT(N)

VCD VCG VS1VS2

53 2

BS

PCF5079

9

8

7

PU

VDAC

power-up

band select

control voltage

10 6

8.2

V

V

pF

SS

DD

1PS79SB62

1 kΩ

Fig.19 Application diagram.

+2.4 to 6 V

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2001 Nov 21 20

(1) Precise value depends on the PCB design.

Page 21

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

13 PACKAGE OUTLINES

TSSOP10: plastic thin shrink small outline package; 10 leads; body width 3 mm

10

D

c

y

Z

6

E

H

E

PCF5079

SOT552-1

A

X

v M

A

A

pin 1 index

15

e

DIMENSIONS (mm are the original dimensions)

A

A

UNIT

max.

mm

1.10

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

OUTLINE

VERSION

SOT552-1

1

0.15

0.05

A2A3b

0.95

0.25

0.80

IEC JEDEC EIAJ

p

0.30

0.15

w M

b

p

(1)E(2)

ceD

0.23

3.10

0.15

3.10

2.90

2.90

REFERENCES

2.5 5 mm0

scale

0.50

L

p

wyv

0.1 0.10.10.95

EUROPEAN

PROJECTION

(A3)

A

θ

(1)

θ

Z

0.67

6°

0.34

0°

ISSUE DATE

99-07-29

2

A

1

L

detail X

LH

E

5.00

4.80

L

0.70

0.40

p

2001 Nov 21 21

Page 22

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

HVSON10: plastic, heatsink very thin small outline package; no leads;

10 terminals; body 3 x 3 x 0.90 mm

X

A

D

B

E

PCF5079

SOT650-1

y

C

1

y

C

A

4

A

terminal 1

index area

L

10

D

DIMENSIONS (mm are the original dimensions)

A

UNIT

mm

max.

A

0.85

0.60

b

4

0.30

0.18

D

3.20

2.80

D

2.55

2.25

h

3.20

2.80

detail X

M

6

vB

w

E

Bottom view

L

0.50

0.30

M

h

0.2v0.1

w

ye

0.05 0.1

y

1

0 2 mm1

scale

b

51

e

h

E

E

h

1.75

0.50.90

1.45

OUTLINE

VERSION

SOT650-1 MO-229

IEC JEDEC EIAJ

REFERENCES

2001 Nov 21 22

EUROPEAN

PROJECTION

ISSUE DATE

01-01-22

Page 23

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

14 SOLDERING (TSSOP10)

14.1 Introduction to soldering surface mount

packages

Thistext gives a verybriefinsightto a complex technology.

A more in-depth account of soldering ICs can be found in

our

“Data Handbook IC26; Integrated Circuit Packages”

(document order number 9398 652 90011).

There is no soldering method that is ideal for all surface

mount IC packages.Wave soldering isnot always suitable

for surface mount ICs, or for printed-circuit boards with

high population densities. In these situations reflow

soldering is often used.

14.2 Reflow soldering

Reflow soldering requires solder paste (a suspension of

fine solder particles, flux and binding agent) to be applied

tothe printed-circuit boardbyscreen printing, stencillingor

pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example,

infrared/convection heating in a conveyor type oven.

Throughput times (preheating,soldering andcooling) vary

between 100 and 200 seconds depending on heating

method.

Typical reflow peak temperatures range from

215 to 250 °C. The top-surface temperature of the

packages should preferable be kept below 230 °C.

PCF5079

If wave soldering is used the following conditions must be

observed for optimal results:

• Use a double-wave soldering method comprising a

turbulent wave with high upward pressure followed by a

smooth laminar wave.

• For packages with leads on two sides and a pitch (e):

– larger than or equal to 1.27 mm, the footprint

longitudinal axis is preferred to be parallel to the

transport direction of the printed-circuit board;

– smaller than 1.27 mm, the footprint longitudinal axis

must be parallel to the transport direction of the

printed-circuit board.

The footprint must incorporate solder thieves at the

downstream end.

• Forpackageswith leads on foursides,thefootprint must

be placed at a 45° angle to the transport direction of the

printed-circuit board. The footprint must incorporate

solder thieves downstream and at the side corners.

During placement andbefore soldering,the package must

be fixed with a droplet of adhesive. The adhesive can be

applied by screen printing, pin transfer or syringe

dispensing. The package can be soldered after the

adhesive is cured.

Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal

of corrosive residues in most applications.

14.3 Wave soldering

Conventional single wave soldering is not recommended

forsurfacemount devices (SMDs) orprinted-circuitboards

with a high component density, as solder bridging and

non-wetting can present major problems.

To overcome these problems the double-wave soldering

method was specifically developed.

2001 Nov 21 23

14.4 Manual soldering

Fix the component by first soldering two

diagonally-opposite end leads. Use a low voltage (24 V or

less) soldering iron applied to the flat part of the lead.

Contact time must be limited to 10 seconds at up to

300 °C.

When using a dedicated tool, all other leads can be

soldered in one operation within 2 to 5 seconds between

270 and 320 °C.

Page 24

Philips Semiconductors Product specification

Dual-band power amplifier controller for

PCF5079

GSM, PCN and DCS

14.5 Suitability of surface mount IC packages for wave and reflow soldering methods

PACKAGE

BGA, LFBGA, SQFP, TFBGA not suitable suitable

HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, SMS not suitable

(3)

PLCC

LQFP, QFP, TQFP not recommended

SSOP, TSSOP, VSO not recommended

Notes

1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum

2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink

3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction.

4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm;

5. Wave soldering is only suitable for SSOP andTSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is

, SO, SOJ suitable suitable

temperature (with respect to time) and body size of the package, there is a risk that internal or external package

cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the

Drypack information in the

(at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

The package footprint must incorporate solder thieves downstream and at the side corners.

it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

“Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods”

SOLDERING METHOD

WAVE REFLOW

(2)

(3)(4)

(5)

suitable

suitable

suitable

(1)

.

2001 Nov 21 24

Page 25

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

15 SOLDERING (HVSON10)

15.1 Soldering information

Informationcontainedwithin this chapter is ofapreliminary

nature and may change without notice.

15.2 PCB design guidelines

These guidelines are to help the user in developing the

properPCB design. For thesurfacemount process referto

“Data Handbook IC26; Integrated Circuit Packages”

(document order number 9398 652 90011).

15.2.1 PERIMETER PAD DESIGN

Referring to Fig.20, dimensions Z and G are respectively

the outside to outside and the inside to inside pad

dimensions.

PCF5079

The dimensions X and Y indicate respectively the width

and the length of the pad. Note that the calculated

X dimension is the maximumvalue in orderto avoid solder

bridging between adjacent pads.The calculated

Y dimension is the minimum value and therefore pad

design should start with this value and the pad length at

the outside be extended if more solder joint fillets are

required.

The dimension ‘Cpl’ defines the minimum distance

between the inner tip of the pad and the outer edge of the

thermal pad. It is suggested that this dimension be fixed at

0.15 mm to avoid solder bridging issues between the

thermal pad and the perimeter pads.

handbook, full pagewidth

G =

3.46

Z =

Dimensions in mm.

The solder mask opening dimension should be larger than the pad dimension by 125 to 150 µm.

3.27

2.09

X = 0.28

1.20

1.00

2.00 REF

1.20

1.00

0.50

TYP

Fig.20 HVSON10 PCB pattern.

Y =

0.33

0.30

0.69

0.55

thermal via

Cpl = 0.15

MGW498

15.2.2 THERMAL PAD AND VIA DESIGN

The size of the thermal pad should at least match the size

of the exposed die-attach paddle. However, in some

cases, the die-attachpaddle sizemay need to be modified

to avoid solder bridging between the thermal pad and the

perimeter pads. In order to effectively transfer heat from

2001 Nov 21 25

the top metal layer to the inner or bottom layers of the

PCB, thermal vias should be incorporated into the thermal

paddesign. The numberof thermal vias will depend on the

application and on the power dissipation and electrical

requirements. It is recommended to incorporate an array

of thermal vias at a pitch of 1.0 to 1.2 mm with the via

diameter between 0.3 and 0.33 mm.

Page 26

Philips Semiconductors Product specification

Dual-band power amplifier controller for

GSM, PCN and DCS

15.2.3 STENCIL DESIGN FOR PERIMETER PADS

For optimum paste release the area and aspect ratios of

the stencil should be greater than 0.66 and 1.5

respectively.

Area ratio

Aspect ratio

where:

L = aperture length

W = aperture width

T = stencil thickness.

area of aperture opening

----------------------------------------------------------------aperture wall area

aperture width

==

------------------------------------------stencil thickness

W

----T

LW×

==

-------------------------2T(L + W)

PCF5079

15.2.4 STENCIL DESIGN FOR THERMAL PADS

In order to remove the heat effectively from the package

and to enhance electrical performance the die-attach

paddle needs to be soldered to the PCB thermal pad,

preferably with minimum voids.

It is therefore recommended that smaller, multiple

openings in a stencil should be used instead of one large

openingfor printing solderpaste in thethermal pad region.

Thisresultstypically in 50% to80%solderpaste coverage.

Two examples are shown in Fig.21.

15.2.5 STENCIL THICKNESS

A stencil thicknessof 0.125 to 0.150 mmis recommended

but this value needs to be optimized by the userto findthe

proper thickness according to application requirements.

handbook, full pagewidth

a. Outline of 0.4 mm2 2 × 2 array giving

44% solder paste coverage.

Fig.21 Examples of thermal pad stencil design.

MGW499

b. Outline of 1.2 mm2 2 × 1 array giving

60% solder paste coverage.

2001 Nov 21 26

Page 27

Philips Semiconductors Product specification

Dual-band power amplifier controller for

PCF5079

GSM, PCN and DCS

16 DATA SHEET STATUS

PRODUCT

DATA SHEET STATUS

Objective data Development This data sheet contains data from the objective specification for product

Preliminary data Qualification This data sheet contains data from the preliminary specification.

Product data Production This data sheet contains data from the product specification. Philips

Notes

1. Please consult the most recently issued data sheet before initiating or completing a design.

2. The product status of the device(s) described in this data sheet may have changed since this data sheet was

published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

(1)

STATUS

(2)

development. Philips Semiconductors reserves the right to change the

specification in any manner without notice.

Supplementary data will be published at a later date. Philips

Semiconductors reserves the right to change the specification without

notice, in order to improve the design and supply the best possible

product.

Semiconductors reserves the right to make changes at any time in order

to improve the design, manufacturing and supply. Changes will be

communicated according to the Customer Product/Process Change

Notification (CPCN) procedure SNW-SQ-650A.

DEFINITIONS

17 DEFINITIONS

Short-form specification The data in a short-form

specification is extracted from a full data sheet with the

same type number and title. For detailed information see

the relevant data sheet or data handbook.

Limiting values definition Limiting values given are in

accordance with the Absolute Maximum Rating System

(IEC 60134). Stress above one or more of the limiting

values may cause permanent damage to the device.

These are stress ratings only and operation of the device

atthese or at anyotherconditions above those giveninthe

Characteristics sections of the specification is not implied.

Exposure to limiting values for extended periods may

affect device reliability.

Application information Applications that are

described herein for any of these products are for

illustrative purposes only. Philips Semiconductors make

norepresentationor warranty that such applicationswillbe

suitable for the specified use without further testing or

modification.

18 DISCLAIMERS

Life support applications These products are not

designed for use in life support appliances, devices, or

systems where malfunction of these products can

reasonably be expectedto result inpersonal injury. Philips

Semiconductorscustomersusing or selling these products

for use in such applications do so at their own risk and

agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Right to make changes Philips Semiconductors

reserves the right to make changes, without notice, in the

products, including circuits, standard cells, and/or

software, described or contained herein in order to

improve design and/or performance. Philips

Semiconductors assumes no responsibility or liability for

theuseof any of theseproducts,conveysno licence or title

under any patent, copyright, or mask work right to these

products,and makes no representationsor warranties that

these products are free from patent, copyright, or mask

work right infringement, unless otherwise specified.

2001 Nov 21 27

Page 28

Philips Semiconductors – a w orldwide compan y

Contact information

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2001

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed

without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license

under patent- or other industrial or intellectual property rights.

Printed in The Netherlands 403506/01/pp28 Date of release: 2001 Nov 21 Document order number: 9397 750 07095

SCA73

Loading...

Loading...