Philips PCF5078, PCF5078T Datasheet

INTEGRATED CIRCUITS

DATA SH EET

PCF5078

Power amplifier controller for GSM

and PCN systems

Product specification

File under Integrated Circuits, IC17

1999 Apr 12

Philips Semiconductors Product specification

Power amplifier controller for GSM and

PCF5078

PCN systems

FEATURES

• Compatible with baseband interface family PCF5073x

• Two power sensor inputs

• Temperature compensation of sensor signal

• Active filter for DAC input

• Power Amplifier (PA) protection against mismatching

• Bias current source for detector diodes

• Generation of pre-bias level for PA at start of burst

(home position)

• Possibility to adapt home position by external

components

• Applicable for a wide range of silicon and GaAs power

amplifiers.

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DD

I

DD(tot)

T

amb

supply voltage 2.4 3.6 5.0 V

total supply current −−6mA

operating ambient temperature −40 − +85 °C

APPLICATIONS

• Global System for Mobile communication (GSM)

• Personal Communications Network (PCN) systems.

GENERAL DESCRIPTION

This CMOS device integrates an amplifier for the detected

RF voltage from the sensor, an integrator and an active

filter to build a PA control loop for cellular systems with a

small amount of passive components.

ORDERING INFORMATION

TYPE

NUMBER

PCF5078T TSSOP8 plastic thin shrink small outline package; 8 leads; body width 3.0 mm SOT505-1

NAME DESCRIPTION VERSION

PACKAGE

1999 Apr 12 2

Philips Semiconductors Product specification

Power amplifier controller for GSM and

PCN systems

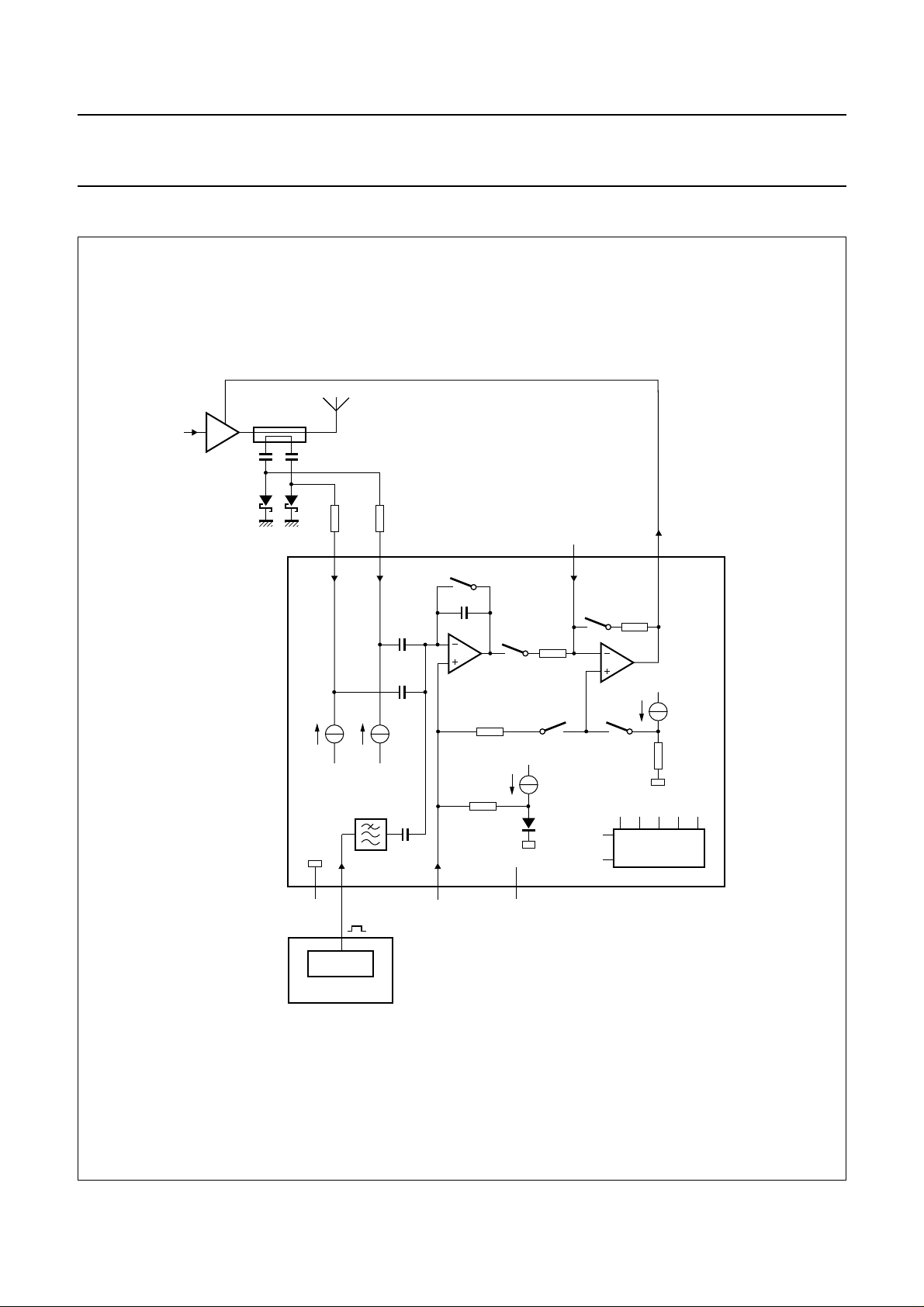

BLOCK DIAGRAM

handbook, full pagewidth

antenna

VS2 VS1 VC

3421

C1

6 pF

C2

6 pF

30 µA

V

V

DD

DD

C3

5 pF

56 7

SS

VDAC

VHOME

RF

PA

sensor

D1 D2

30 µA

V

S1

C4

10 pF

OP1

R6

15 kΩ

R3

50 kΩ

S5

PCF5078

V

DD

8

V

DD

R1

20 kΩ

10 µA

V

home

VINT

VDAC

PCF5078

R2

1 kΩ

V

S1

S2S2S3S3S4S4S5

CONTROL

LOGIC

DD

10 µA

V

prebias

R4

6 kΩ

MGS193

OP4

V

DD

AUXDAC3

PCF5073x

Fig.1 Block diagram.

1999 Apr 12 3

Philips Semiconductors Product specification

Power amplifier controller for GSM and

PCN systems

PINNING

SYMBOL PIN DESCRIPTION

VC 1 PA control output voltage

VINT 2 negative integrator input

VS1 3 sensor signal input 1

VS2 4 sensor signal input 2

V

SS

VDAC 6 DAC input voltage

VHOME 7 home position input voltage

V

DD

handbook, halfpage

5 ground supply

8 supply voltage

VC

1

VINT VHOME

2

PCF5078

3

VS1

4

VS2

MGS194

8

7

6

5

V

DD

VDAC

V

SS

Fig.2 Pin configuration.

PCF5078

An external Digital-to-Analog Converter (DAC) with10-bit

resolution is necessary to control the loop e.g. the

AUXDAC3 of the baseband interface family PCF5073x.

An integrated active filter smooths the voltage steps of the

DAC and avoids a feedthrough of the DAC harmonics into

the modulation spectra of the PA.

The DAC signal and the sensor signal are added by

operational amplifier OP1. The voltage difference of both

signals is integrated by operational amplifier OP4, which

provides the PA control voltage on pin VC. The integration

is performed by means of an external capacitance C

connected between pins VINT and VC.

The shape of the rising and falling power burst edges can

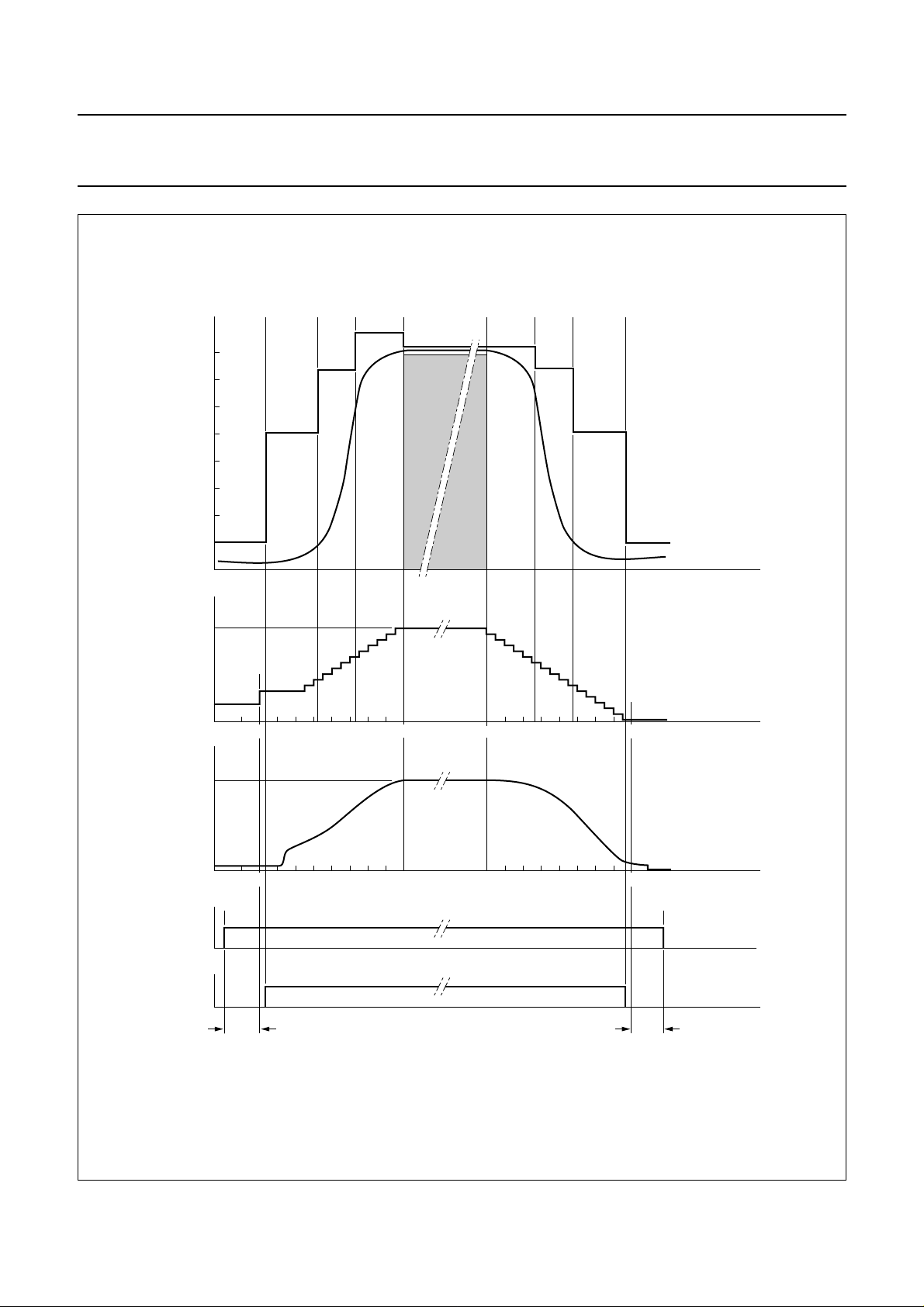

be determined by means of the DAC voltage (see Fig.3).

Power-down mode

During the not used time slots in Time Division Multiple

Access (TDMA) systems, the PCF5078 must be turned off

by switching off the supply voltage on pin V

DD

Initial conditions and start-up

The PCF5078 has been designed to operate in bursts as

required in TDMA systems. For each time slot to be

transmitted it must be powered-up by switching on the

supply voltage. This allows a proper initialization of

switches S1 to S5.

VINT

.

FUNCTIONAL DESCRIPTION

General

The PCF5078 integrates an amplifier for the detected RF

voltage from the sensor, an integrator and an active filter

to build a PA control loop with a small amount of passive

components.

The sensor amplifier is able to amplify signals from a RF

power detector in a range of −20 to +15 dBm. This

complies to the PA output power range of GSM and PCN

systems when a directional coupler with 20 dB attenuation

is used.

The Schottky diode for power detection (sensor) is biased

by an integrated current source of 30 µA. Variations of the

forward voltage of the diodes with the temperature have no

influence on the measured signal, because they are

cancelled by sampling around the switched capacitor

operational amplifier OP1 (see Fig.1).

During start-up switches S1, S2 and S3 are closed and

switches S4 and S5 are opened (see Fig.4).

The forward voltages on the Schottky diodes are sampled

on capacitors C1 and C2, respectively, because switch S1

is closed. Moreover, the control voltage on pin VC is

initially forced to pre-bias level V

prebias

because

switches S2 and S3 are closed and switch S4 is opened.

Switch S1 is opened after a fixed time the supply voltage

has been switched on and then the circuit is ready. This

time is defined on-chip and can be maximum 45 µs. Once

switch S1 is open, a ramp signal with a minimum

amplitude of 25 mV applied on pin VDAC determines

opening of switch S3 and closing of switch S4 with a delay

of maximum 3 µs with respect to the start of the ramp.

After opening switch S3, the control voltage on pin VC

rises in a fixed amount of time to the home position level

so biasing the PA to the beginning of the active range of its

control curve. Switch S2 remains closed during this typical

time of 2 µs. When switch S2 is opened, switch S5 is

closed allowing the transfer of any signal coming from

amplifier OP1.

1999 Apr 12 4

Philips Semiconductors Product specification

Power amplifier controller for GSM and

PCN systems

After this preset, the control voltage is free to increase

according to the control loop if RF input is present

(see Fig.3).

For higher DAC ramp steps the delay time of opening

switch S3 (and closing switch S4) is reduced. On the

contrary, the delay time between opening switch S2 with

respect to opening switch S3 (and closing switch S4)

remains unchanged.

For a correct start-up it is required that the rising time of the

supply voltage is maximum 20 µs.

End of a burst

For a proper down ramp, the final value of the DAC input

voltage should be below the value at the beginning of the

burst and so be able to really shut-off the PA (see Fig.5).

This means the code programmed for the last bit of the

DAC down ramp (CODE

initial value of the up ramp (CODE

last code must be maintained until the supply voltage has

been switched off.

When the voltage on pin VC is detected to be lower than

V

to V

opening switches S4 and S5.

a built-in mechanism forces the voltage on pin VC

VHOME

by closing switches S1, S2 and S3 and by

prebias

) has to be lower than the

END

). Moreover, the

START

PCF5078

PA protection against mismatching

A second sensor amplified input is integrated into the

PCF5078 for measuring the reflected wave of the

directional coupler. The signal is added to the measured

RF power signal (see Fig.3). When mismatching at the

output of the PA occurs the power is reduced. A high

Voltage Standing W ave Ratio (VSWR) at the output of the

PA often occurs in systems where the PA is connected to

the antenna via switches with low attenuation instead of

using a duplex filter.

Home position voltage

A forward voltage of an on-chip silicon diode is provided as

the default home position voltage V

matches the requirements at the control input of most PAs

and exhibits the same temperature coefficient.

However, if another value is needed for a certain PA the

level can be adjusted by connecting external components

to pin VHOME (see Figs 10 and 11). The home position

voltage can be set between 200 and 1000 mV when using

a capacitor of 50 pF connected between pins VINT

and VC.

. This voltage

home

For proper operation, the supply voltage should be

switched off at least 15 µs later with respect to the end of

the down ramp on pin VDAC.

1999 Apr 12 5

Philips Semiconductors Product specification

Power amplifier controller for GSM and

PCN systems

handbook, full pagewidth

0

RF

out

(dBc)

−10

−20

−30

−40

−50

−60

−70

V

VDAC

<0.9V

−80

DD

−28 −18 −10 0

+543 +553 +561 +571

PCF5078

time (µs)

CODE

START

<0.9V

V

prebias

V

V

RF

VC

DD

DD

CODE

END

1614121086420

1614121086420

in

32

3028262422201816

3028262422201816

DAC bits at 560 kHz

32

DAC bits at 560 kHz

>15 µs>45 µs

time

time

MGS197

Fig.3 Timing diagram.

1999 Apr 12 6

Loading...

Loading...