Philips PCF1178CT, PCF1178CU-10 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

PCF1178C

4-digit duplex LCD car clock

Product specification

Supersedes data of September 1993

File under Integrated Circuits, IC16

1997 Apr 16

Philips Semiconductors Product specification

4-digit duplex LCD car clock PCF1178C

FEATURES

• Internal voltage regulator is electrically programmable

for various LCD voltages

• Time calibration is electrically programmable

(no trimming capacitor required)

• LCD voltage adjusts with temperature for good contrast

• 4.19 MHz oscillator

• 12-hour or 24-hour mode

• Operating ambient temperature: −40 to +85 °C

GENERAL DESCRIPTION

The PCF1178C is a single chip, 4.19 MHz CMOS car clock

circuit providing hours, minutes and seconds functions.

It is designed to drive a 4-digit duplex liquid crystal display

(LCD).

Two external single-pole, single-throw switches will

accomplish all time setting functions. Time calibration and

voltage regulator are electrically programmable via an

on-chip EEPROM. The circuit is battery-operated via an

internal voltage regulator and an external resistor.

• 28-lead plastic SMD (SO28)

• 1 Hz set mode.

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

PCF1178CT SO28 plastic small outline package; 28 leads; body width 7.5 mm

PCF1178CU − uncased chip in tray

PCF1178CU/10 − chip-on-film frame carrier (FFC)

PCF1178CU/5 − unsawn wafer

(2)

(2)

(2)

(1)

SOT136-1

−

−

−

Notes

1. See Fig.1 and Chapter “Package outline” for pin layout and package details.

2. See Chapter “Chip dimensions and bonding pad locations” for pad layout and package details.

1997 Apr 16 2

Philips Semiconductors Product specification

4-digit duplex LCD car clock PCF1178C

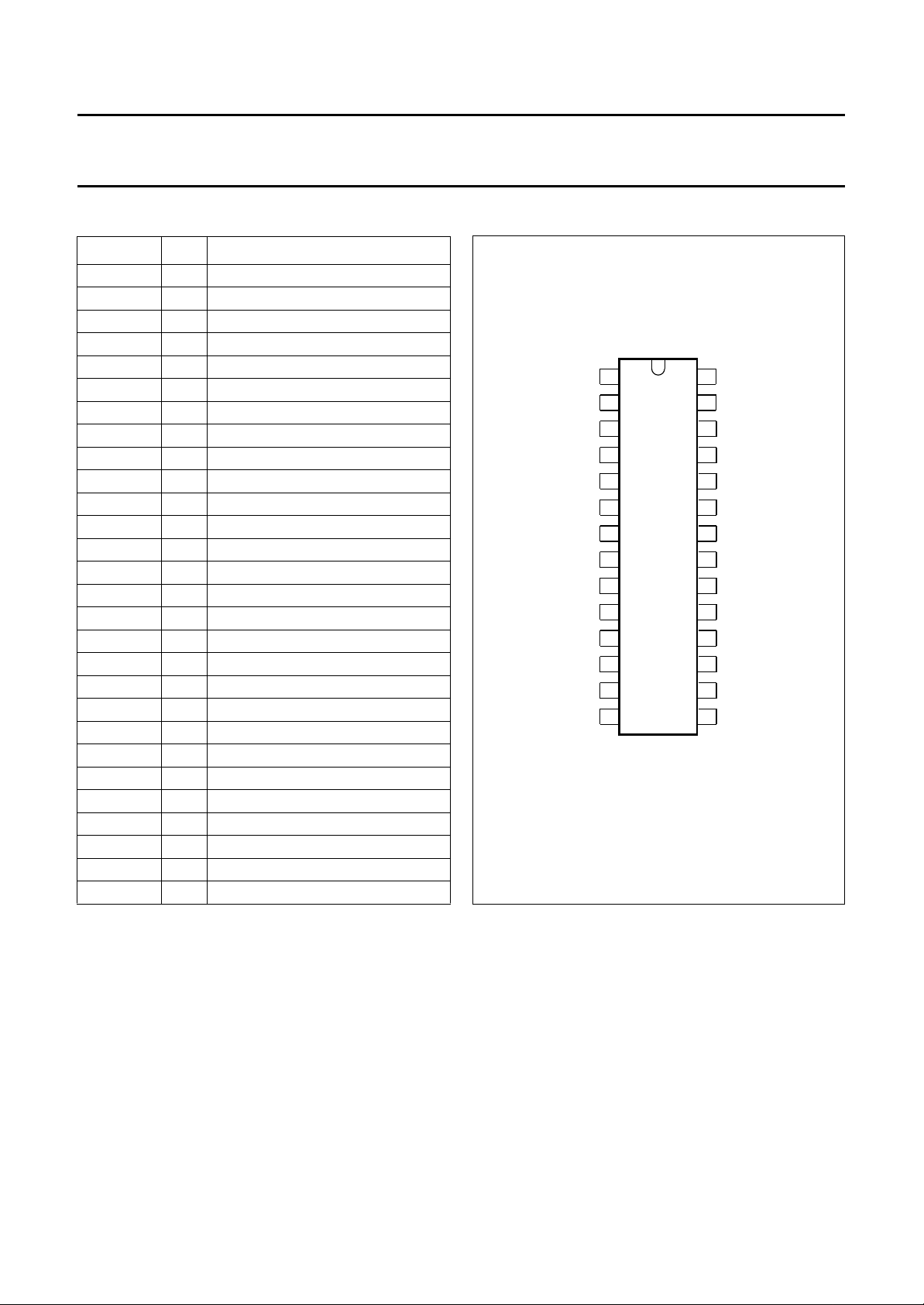

PINNING

SYMBOL PIN DESCRIPTION

BP1 1 backplane 1

BP2 2 backplane 2

AM/PM 3 segment driver

A2/ADEG1 4 segment driver

B1/C1 5 segment driver

F2/E2 6 segment driver

G2/D2 7 segment driver

B2/C2 8 segment driver

A4/COL 9 segment driver

F3/E3 10 segment driver

G3/AD3 11 segment driver

B3/C3 12 segment driver

F4/E4 13 segment driver

G4/D4 14 segment driver

B4/C4 15 segment driver

S2 16 minute adjustment input

SEL 17 EEPROM select input

FLASH 18 colon option input

V

DD

19 positive supply voltage

ENABLE 20 enable input (for S1 and S2)

TS 21 test speed-up mode input

V

PP

22 programming voltage input

MODE 23 12/24-hour mode select input

V

SS

24 negative supply voltage

OSC OUT 25 oscillator output

OSC IN 26 oscillator input

DATA 27 EEPROM data input

S1 28 hour adjustment input

AM/PM

A2/ADEG1

A4/COL

G3/AD3

Fig.1 Pin configuration, PCF1178CT, (SO28).

BP1

BP2

B1/C1

F2/E2

G2/D2

B2/C2

F3/E3

B3/C3

F4/E4

G4/D4

1

2

3

4

5

6

7

PCF1178CT

8

9

10

11

12

13

MSB229

28

27

26

25

24

23

22

21

20

19

18

17

16

1514

S1

DATA

OSC IN

OSC OUT

V

SS

MODE

V

PP

TS

ENABLE

V

DD

FLASH

SEL

S2

B4/C4

1997 Apr 16 3

Philips Semiconductors Product specification

4-digit duplex LCD car clock PCF1178C

FUNCTIONAL DESCRIPTION AND TESTING

Outputs

The circuit outputs 1 : 2 multiplexed data (duplex) to the

LCD. Generation of BP1 and BP2 (three-level backplane

signals) and the output signals are shown in Fig.4.

F2

E2

A2

G2

AM

E1

A1

G1

B1

C1

PM

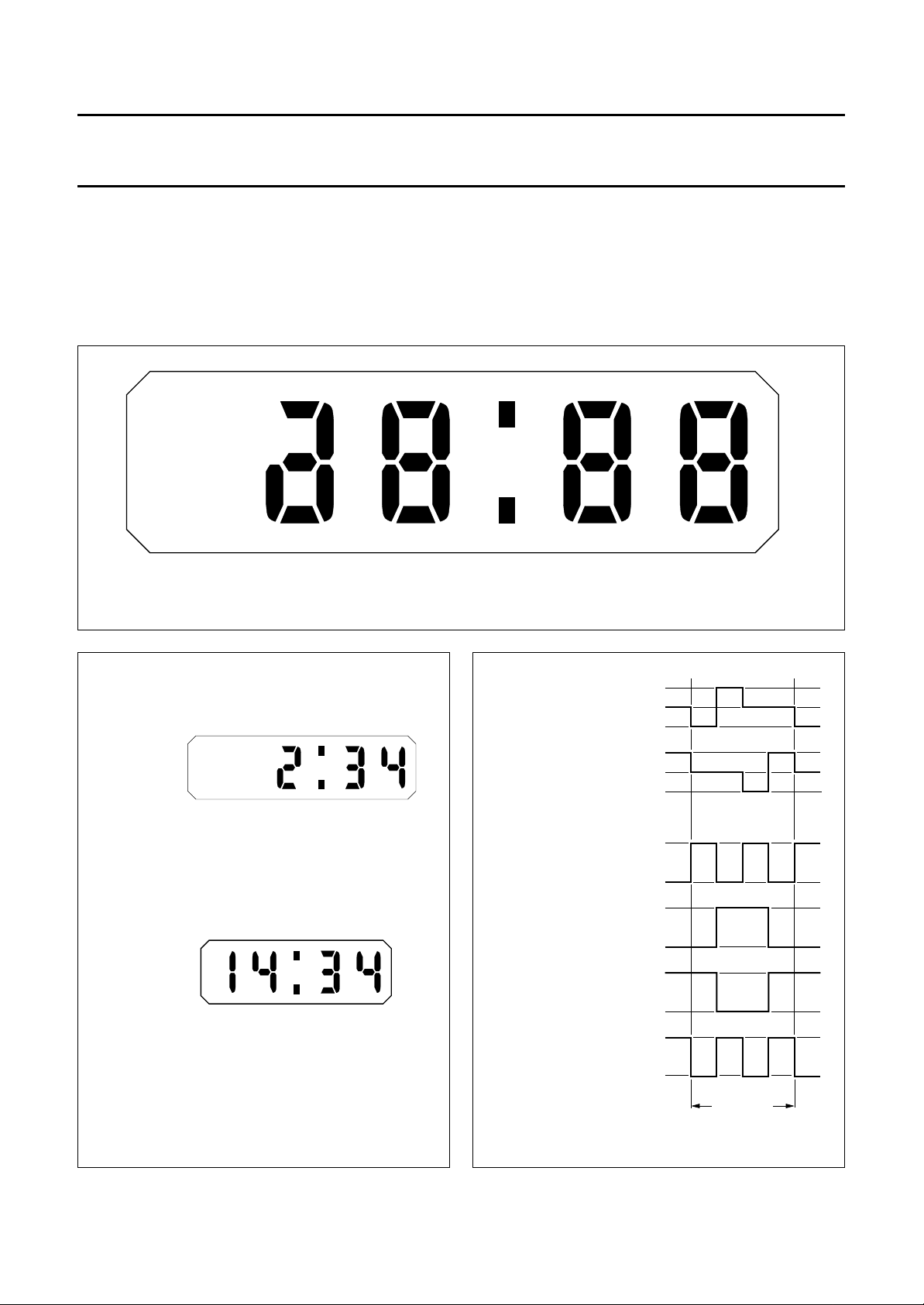

D1

Fig.2 Segment designation of LCD.

D2

The average voltages across the segments are:

B2

C2

1. V

2. V

ON(RMS)

OFF(RMS)

COL

= 0.79 V

= 0.35 VDD.

F3

E3

A3

G3

D3

DD

B3

C3

F4

E4

A4

G4

D4

MLB251

B4

C4

TIME

TIME

PM

(a)

a. 12-hour mode.

(b)

b. 24-hour mode.

MSA994

MSA993

BP1

BP2

SEGMENT1SEGMENT

ON ON

OFF ON

ON OFF

OFF OFF

2

MSB226

V

DD

VDD/2

V

DD

VDD/2

V

DD

V

DD

V

DD

V

DD

0

0

0

0

0

0

15.625 ms

Fig.3 Typical displays.

1997 Apr 16 4

Fig.4 Backplane and output signals.

Philips Semiconductors Product specification

4-digit duplex LCD car clock PCF1178C

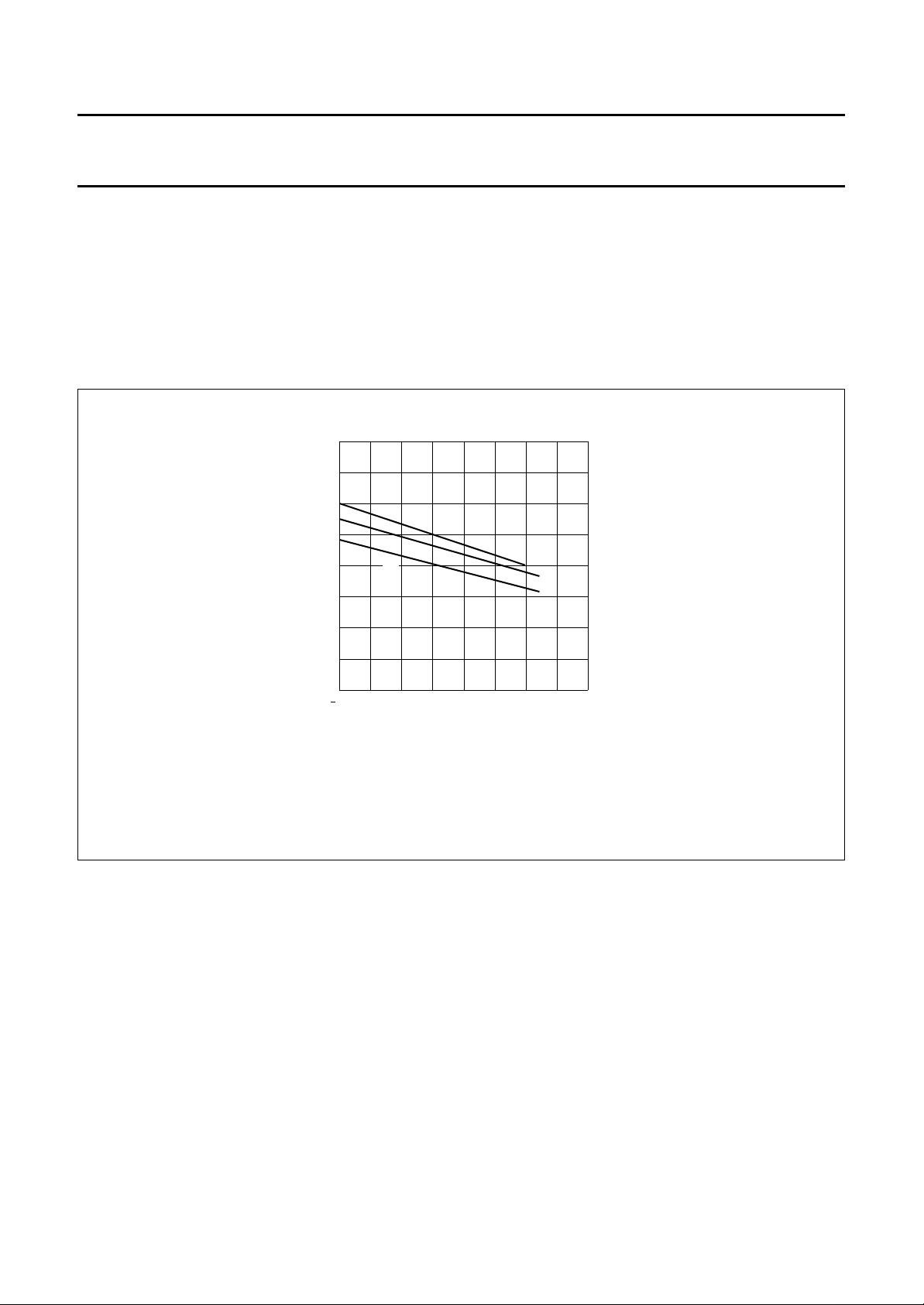

LCD voltage (see Fig.5)

The adjustable voltage regulator controls the supply

voltage (see Section “LCD voltage programming”) in

relation to temperature for good contrast, for example

when VDD= 4.5 V at +25 °C, then:

VDD= 3 to 4 V at +85 °C.

VDD=5to6Vat−40 °C.

−8

V

SS

(V)

−6

−4

−2

0

40 0 40 120

(1) Programmed to 4.0 V at 25 °C (value within the specified operating range).

(2) Programmed to 4.5 V at 25 °C (value within the specified operating range).

(3) Programmed to 5.0 V at 25 °C (value within the specified operating range).

(3)

(2)

(1)

Fig.5 Regulated voltage as a function of temperature (typical).

80

MSA995

o

T ( C)

1997 Apr 16 5

Philips Semiconductors Product specification

4-digit duplex LCD car clock PCF1178C

12/24-hour mode

Operation in 12-hour or 24-hour mode is selected by

connecting MODE to VDD or VSS respectively. If MODE is

left open-circuit and a reset occurs, the mode will change

from 12-hour to 24-hour mode or vice versa.

Power-on

After connecting the supply, the start-up mode is:

MODE connected to V

: 12-hour mode, 1:00 AM.

DD

MODE connected to VSS: 24-hour mode, 0:00.

MODE left open-circuit: 24-hour mode, 0:00 or 1:00.

Colon

If FLASH is connected to V

the colon pulses at 0.5 Hz.

DD

If FLASH is connected to VSS the colon is static.

Time setting

Switch inputs S1 and S2 have a pull-up resistor to facilitate

the use of single-pole, single-throw contacts. A debounce

circuit is incorporated to protect against contact bounce

and parasitic voltages.

Set enable

Inputs S1 and S2 are enabled by connecting ENABLE to

or disabled by connecting to VSS.

V

DD

Set hours

When S1 is connected to V

the hours displayed

SS

advances by one and after one second continues with one

advance per second until S1 is released (auto-increment).

Set minutes

When S2 is connected to V

the time displayed in

SS

minutes advances by one and after one second continues

with two advances per second until S2 is released

(auto-increment). In addition to minute correction, the

seconds counter is reset to zero.

Segment test/reset

When S1 and S2 are connected to V

, all LCD segments

SS

are switched ON. Releasing switches S1 and S2 resets the

display. No reset occurs when DATA is connected to V

SS

(overlapping S1 and S2).

Test mode

When TS is connected to V

, the device is in normal

DD

operating mode. When connecting TS to VSS all counters

(seconds, minutes and hours) are stopped, allowing quick

testing of the display via S1 and S2 (debounce and

auto-increment times are 64 times faster). TS has a

pull-up resistor but for reasons of safety it should be

connected to VDD.

EEPROM

V

has a pull-up resistor but for reasons of safety it should

PP

be connected to VDD.

LCD voltage programming

To enable LCD voltage programming, SEL is set to

open-circuit and a level of V

− 5 V is applied to VPP (see

DD

Fig.6). The first pulse (tE) applied to the DATA input clears

the EEPROM to give the lowest voltage output. Further

pulses (tL) will increment the output voltage by steps of

typically 150 mV (T

=25°C). For programming,

amb

measure VDD− VSS and apply a store pulse (tW) when the

required value is reached. If the maximum number of steps

(n = 31) is reached and an additional pulse is applied the

voltage will return to the lowest value.

Time calibration

To compensate for the tolerance in the quartz crystal

frequency which has been positively offset (nominal

−6

deviation +60 × 10

) by capacitors at the oscillator input

and output, a number (n) of 262144 Hz pulses are

inhibited every second of operation.

1997 Apr 16 6

Loading...

Loading...