Philips PCD5091HZ-D94-F5, PCD50911H-F1, PCD50912H-F1, PCD5091H-C94-F4, PCD5091H-C94-F5 Datasheet

...

DATA SH EET

Objective specification

Supersedes data of 1996 Oct 30

File under Integrated Circuits, IC17

1997 Jul 21

INTEGRATED CIRCUITS

PCD5091

DECT baseband controller

1997 Jul 21 2

Philips Semiconductors Objective specification

DECT baseband controller PCD5091

CONTENTS

1 FEATURES

1.1 DSP software features

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

4 BLOCK DIAGRAM

5 PINNING INFORMATION

5.1 Pinning

5.2 Pin description

6 FUNCTIONAL DESCRIPTION

7 PACKAGE OUTLINES

8 SOLDERING

8.1 Introduction

8.2 Reflow soldering

8.3 Wave soldering

8.4 Repairing soldered joints

9 DEFINITIONS

10 LIFE SUPPORT APPLICATIONS

11 PURCHASE OF PHILIPS I2C COMPONENTS

1997 Jul 21 3

Philips Semiconductors Objective specification

DECT baseband controller PCD5091

1 FEATURES

• 80C51 ports P0, P1, P2 and P3 available for interfacing

to display, keyboard, I2C-bus, interrupt sources and/or

external memory. Integrated 64 kbyte ROM, 3 kbytes of

data memory and 1 kbyte SDR-RAM. External program

memory is addressable up to 128 kbytes

• +2.7 to +5 V port (P0 to P3) interface

• TDMA frame (de)multiplexing. Transmission or

reception can be programmed for any slot

• Ciphering, scrambling, CRC checking/generation and

protected B-fields

• Speech and data buffering space for six handsets

• Local call and B-field loop-back

• Two interrupt lines for BML and DSP to interrupt 80C51

• On-chip, three-channel time-multiplexed 8-bit

Analog-to-Digital Converter (ADC) for RSSI

measurement, one for battery voltage measurement

and one channel available for other purposes

• On-chip 8-bit Digital-to-Analog Converter (DAC) for

electronic potentiometer function

• Phase error measurement and phase error correction by

hardware

• DACs and ADCs for dynamic earpiece and dynamic or

electret microphone

• On-chip reference voltage

• On-chip supply for electret microphone

• Very low ohmic buzzer output

• Serial interface to external ADPCM CODEC (PCD5032)

or 8 kHz u-law samples

• Speech switch for Digital Telephone Answering

Machine (DTAM) connected to SPI interface

• IOM-2 interface (Siemens registered trademark)

• Serial interface to synthesizer for frequency

programming

• Programmable polarity and timing of radio-control

signals

• GMSK pulse shaper

• Easy interfacing with radio circuits, operating at other

supply voltage (RF supply pin with level shifter for RF

signals)

• On-chip comparator for use as data-slicer

• Low power oscillator with integrated frequency

adjustment

• QFP100 and LQFP100 packages

• Power-on-reset

• Programmable power-down modes

• Low supply voltage (2.7 to 3.6 V)

• CMOS technology.

1.1 DSP software features

• ADPCM encoding and decoding complying with G.721

• Volume control

• Speech filters

• Programmable gain in speech paths

• Side tone and soft mute

• Two tone (DTMF) generators

• Automatic gain control

• Hands-free operation

For each DSP software version a separate manual is

available in which detailed information is provided on how

parameters must be set. For further information please

contact Philips Semiconductors.

2 GENERAL DESCRIPTION

The PCD5091 is designed for GAP-compliant handsets

with speaker-phone option. It has an embedded 80C51

microcontroller with twice the performance of the classic

architecture, 64 kbytes of PROM program memory and

3 kbytes of data memory on-chip. In addition there is

1 kbyte of on-chip data memory that is shared with on-chip

Burst Mode Logic (BML) and DSP, the System Data RAM

(SDR).

3 ORDERING INFORMATION

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

PCD5091H QFP100 plastic quad flat package; 100 leads (lead length 1.95 mm);

body 14 × 20 × 2.8 mm

SOT317-2

PCD5091HZ LQFP100 plastic low profile quad flat package; 100 leads; body 14 × 14 × 1.4 mm SOT407-1

1997 Jul 21 4

Philips Semiconductors Objective specification

DECT baseband controller PCD5091

4 BLOCK DIAGRAM

handbook, full pagewidth

MGD800

R_SLICED

R_DATAM

R_DATAP

T_DATA

T_PWR_RMP

T_ENABLE

ANT_SW1

ANT_SW0

S_PWR

VCO_BND_SW

S_DATA

S_CLK

S_ENABLE

SYNTH_LOCK

REF_CLK

R_ENABLE

R_PWR

SLICE_CTR

LEVEL

SHIFTER

AGM

V

DDA

BURST

MODE

LOGIC

(BML)

CLOCK

GENERATOR

(CLG)

XTAL

OSCILLATOR

(XOSC)

TIMING CONTROL

BLOCK

(TICB)

WATCHDOG

TIMER

(WDT)

ISB BUS

CONTROLLER

(IBC)

RESET

GENERATOR

(RGE)

DIGITAL

CONTROL

OF

ANALOG

(DCA)

80CL51- CORE

ROM

(64 kBYTES)

AB-MICROCONTROLLER

INTERFACE (ABCIF)

PORT 0

8

8 8 8

PORT 1 PORT 2

PORT 3

AUX-RAM

(3 kBYTES)

MICROCONTROLLER-RAM

(256 BYTES)

I

2

C-BUS

SYSTEM

DATA

RAM

(SDR)

(1 kBYTE)

DIGITAL

SIGNAL

PROCESSOR

(DSP)

DIGITAL

DECIMATING

FILTER

(DDF)

DIGITAL

NOISE

SHAPER

(DNS)

4f

s

4f

s

ANALOG VOLTAGE

REFERENCE

(AVR)

POWER-ON-RESET

(POR)

ANALOG

VOLTAGE

SOURCE

(AVS)

PEAK-HOLD

SUBTRACT

MUX

3 : 1

V

ADC

AUXILIARY ADC (AAD)

V

ref

Σ ∆

1-BIT ADC

ATS

1-BIT ADC

ARD

ARF

ARA

AMP

V

ref

TEST CONTROL BLOCK

(TCB)

SPEECH INTERFACE

IOM/ADPCM

(SPI)

BUZZER BUFFER

(ABB)

CODEC

V

DD

V

DD

V

DD

V

DD

V

DDA

CDC-on

108f

s

108f

s

V

DD_RF

V

DD

PSE

EA

ALE

A16

V

DD

V

DDA

T_GMSK

DPLL_DATA

GP_CLK7

XTAL1

V

DDO

V

SSO

XTAL2

CLK100

EN_WATCHDOG RESET_OUT M_RESET VBGP

VANLO

VBAT

RSSI_AN

VANLI

V

ref

VMIC

MICM

MICP

LIFM

LIFP

EARM

EARP

BZM

BZP

CLK3

DCK

FS1

DI

DO

TST2

TST1

V

DD_RF

2 ×

V

DD3V

3 ×

V

DD5V

5 ×

V

SS

V

SSA

V

DDA

PORT 0.0 to

PORT 0.7

PORT 1.0 to

PORT 1.7

PORT 2.0 to

PORT 2.7

PORT 3.0 to

PORT 3.7

V

DD

digital pins

analog pins

MICROCONTROLLER

PCD5091

IB-BUS

Fig.1 Block diagram.

1997 Jul 21 5

Philips Semiconductors Objective specification

DECT baseband controller PCD5091

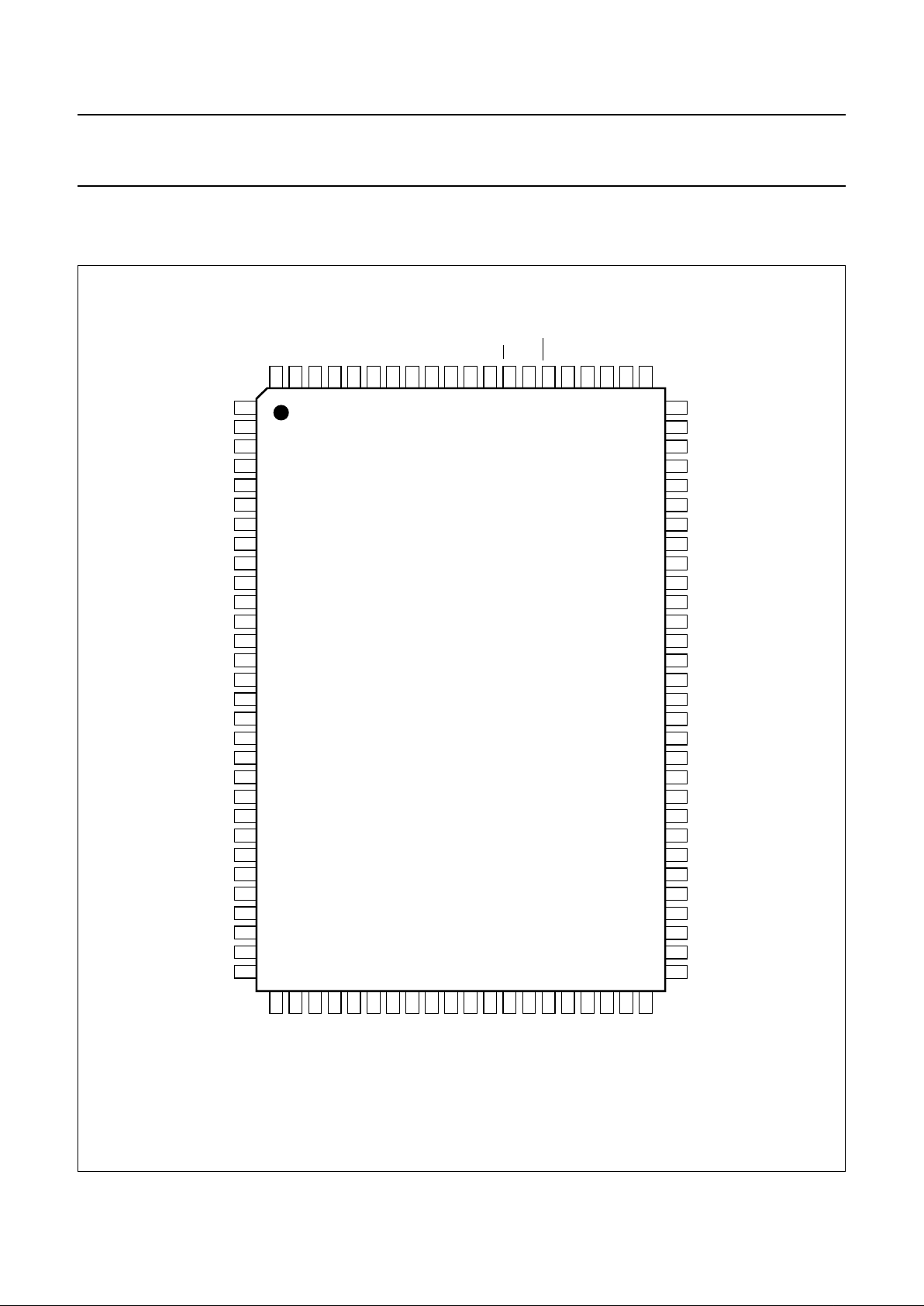

5 PINNING INFORMATION

5.1 Pinning

Fig.2 Pin configuration (QFP100).

handbook, full pagewidth

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

TST2

TST1

V

SS4

V

DD5V_2

A16

P2.2

P2.1

P2.0

P3.7

P3.6

P3.5

P3.4

P3.3

P3.2

P3.1

P3.0

V

SS3

V

SS2

BZP

BZM

V

DD3V_2

P1.7

P1.6

P1.5

P1.4

P1.3

V

DD5V_1

R_SLICED

DPLL_DATA

GP_CLK7

ANT_SW1

ANT_SW0

CLK100

T_ENABLE

T_PWR_RMP

T_DATA

T_GMSK

VCO_BND_SW

SYNTH_LOCK

S_ENABLE

S_DATA

S_CLK

S_PWR

REF_CLK

V

SS1

V

DD_RF

V

DD3V_1

SLICE_CTR

R_PWR

R_DATAP

R_DATAM

R_ENABLE

RSSI_AN

VANLI

VBAT

CLK3

DCK

DI

FS1

DO

XTAL2

XTAL1

VANLO

V

SSO

V

DDO

LIFM

LIFP

V

SSA

MICM

MICP

VMIC

V

ref

VBGP

V

DDA

EARM

EARP

EN_WATCHDOG

P1.0

P1.1

P1.2

RESET_OUT

M_RESET

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

V

DD5V_3VSS5

EA

ALE

PSE

P2.7

P2.6

P2.5

P2.4

P2.3

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

100

99989796959493929190898887868584838281

31323334353637383940414243444546474849

50

MBH938

PCD5091

Loading...

Loading...