Philips ne5037 DATASHEETS

Philips Semiconductors Linear Products Product specification

NE50376-Bit A/D converter (parallel outputs)

582

August 31, 1994 853-0939 13721

DESCRIPTION

The NE5037 is a low cost, complete successive-approximation

analog-to-digital (A/D) converter, fabricated using Bipolar/I

2

L

technology. With an external reference voltage, the NE5037 will

accept input voltages between 0V and V

REF

. An external START

pulse of at least 300ns in duration will provide the 6-bit result of the

conversion in parallel format. Full conversion with no missing codes

occurs in 9µs.

FEATURES

•TTL-compatible inputs and outputs

•3-State output buffer

•Easy interface to CMOS microprocessors

•Fast conversion—9µs

•Guaranteed no missing codes over full temp range

•Single-supply operation, +5V

•Positive true binary outputs

•High-impedance analog inputs

APPLICATIONS

•Temperature control

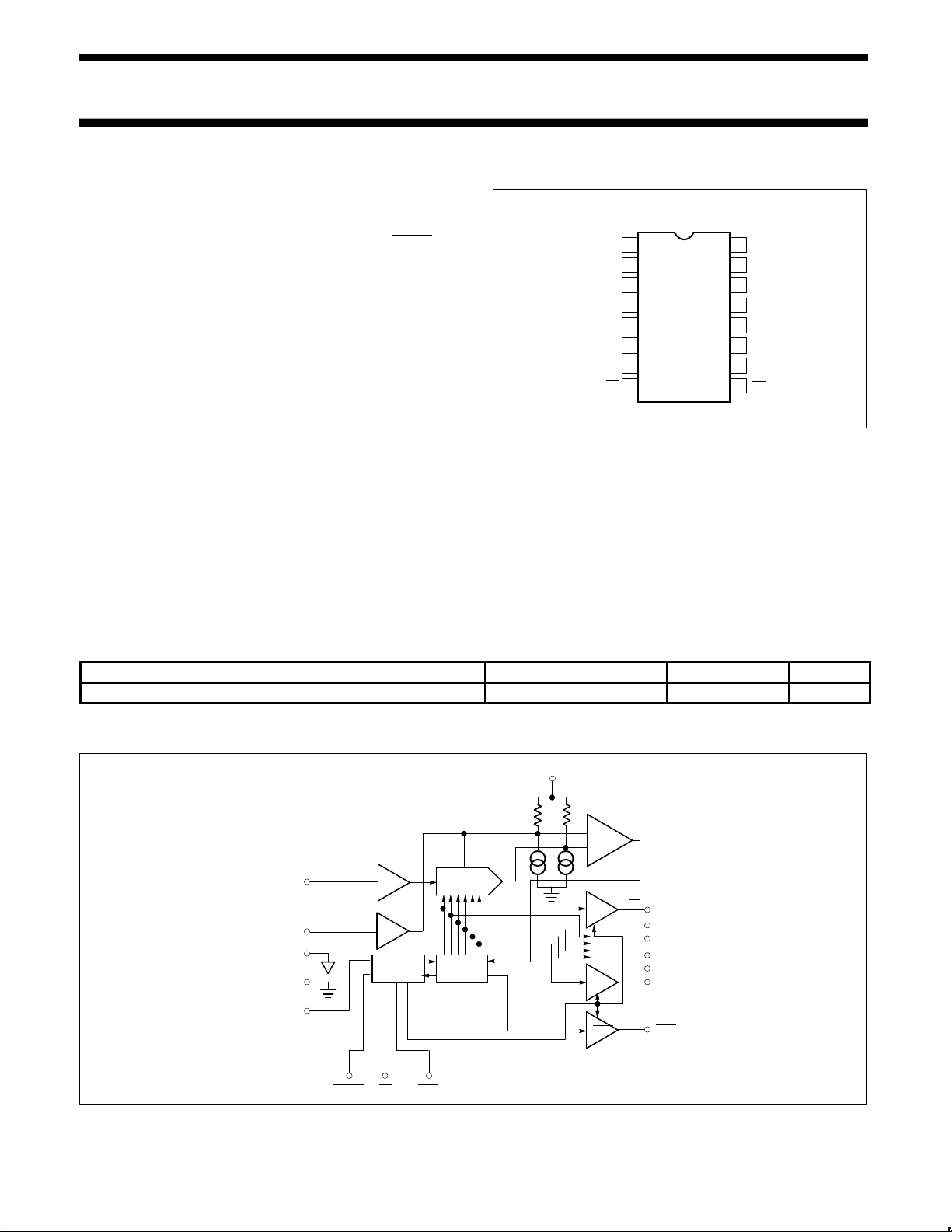

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

16

15

N Package

V

CC

V

REF

V

IN

ANALOG GND

DIGITAL GND

CLK

START

CS

B5 (MSB)

B

3

B

4

B

2

B

1

B

0

EOC

EO

TOP VIEW

•µP-based appliances

•Light level monitors

•Head position sensing

•Electronic toys

•Joystick interface

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

16-Pin Plastic Dual In-Line Package (DIP) 0 to +70°C NE5037N 0406C

BLOCK DIAGRAM

V

REF

V

IN

A

GND

2

3

4

D

GND

CLK

5

6

CONTROL

LOGIC

SAR

V/I

V/I

7 8

9

I

IN

6–BIT

DAC

1/2

LSB

I

O

COM

DB

DB

EOC

DB

O

11

10

EOC

EOCCSSTART

16

DB

5

V

CC

1

Philips Semiconductors Linear Products Product specification

NE50376-Bit A/D converter (parallel outputs)

August 31, 1994

583

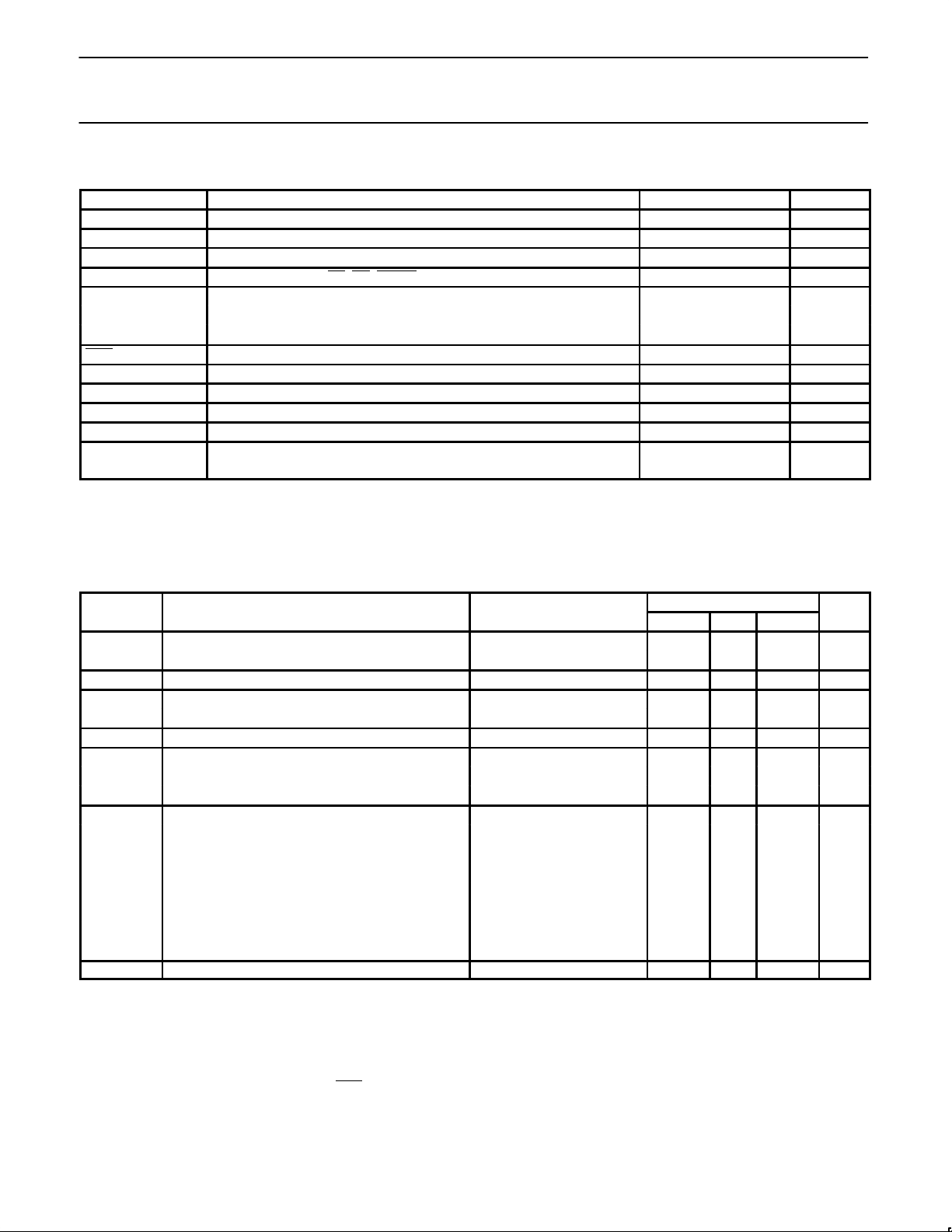

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNIT

V

CC

Power supply voltage 7 V

V

REF

Reference voltage 7 V

V

IN(Analog)

Analog input voltage 7 V

V

IN(Digital)

Digital input voltage (CS, OE, START, CLK) 7 V

D

OUT

Data outputs (DB0 to DB5)

3-state mode 7 V

Enabled mode (each output) 5 mA

EOC End of conversion V

CC

∆

GND

Analog GND to digital GND ±1 V

T

A

Operating temperature range 0 to 70 °C

T

STG

Storage temperature range -65 to 150 °C

T

SOLD

Lead soldering temperature (10 seconds) 300 °C

P

D

Maximum power dissipation, TA=25°C (still-air)

1

N package 1450 mW

NOTES:

1. Derate above 25°C at the following rates:

N package=11.6mW/°C

DC ELECTRICAL CHARACTERISTICS

VCC=5.0V; V

REF

=2.0V; Clock=1MHz; 0°C ≤ T

A

≤ 70°C unless otherwise specified. Typical values are specified at 25°C

LIMITS

SYMBOL

PARAMETER

TEST CONDITIONS

Min Typ Max

UNIT

Resolution 6 6 6 Bits

Relative accuracy

1,2

1/4 1/2 LSB

V

CC

Positive supply voltage +4.75 +5.0 +5.50 V

ε

FS

Full-scale gain error

2,3,4

V

REF

=2.0V, TA=25°C ±1 ±2 LSB

ε

ZS

Zero-scale offset error

2

V

REF

=2.0V, TA=25°C ±1/2 -1/2, +2 LSB

PSR Power supply rejection, Max change in full-scale

2

V

REF

=2.0V, 4.75V≤VCC≤5.5V ±1/2 ±1 LSB

I

IN

Analog input bias current 0≤VIN≤2.5V 1 10 µA

I

REF

Reference bias current 0≤V

REF

≤2.5V 1 10 µA

R

IN

Analog input resistance 3 30 MΩ

V

IH

Logic ”1’ input voltage 2.0 V

V

IL

Logic ”0’ input voltage 0.8 V

I

IH

Logic ”1’ input current 10 µA

I

IL

Logic ”0’ input current 1 10 µA

I

OH

Logic ”1’ output current

5

2.4V≤V

OH

300 µA

I

OL

Logic ”0’ output current

5

VOL≤0.4V 1.6 mA

I

OZ

3-State leakage current ±0.1 ±40 µA

I

CC

Positive supply current 18 24 mA

P

D

Power dissipation 132 mW

NOTES:

1. Relative accuracy is defined as the deviation of the code transition points from the ideal code transition points on a straight line drawn from

zero-scale to full-scale of the device.

2. Specifications given in LSBs refer to the weight of the least significant bit at the 6-bit level which is 1.56% of the full-scale voltage.

3. Full-scale gain error is the deviation of the full-scale code transition point (111110 to 111111) from its ideal value.

4. The analog input voltage (V

IN

) range is 0V to V

REF

nominally, with the output remaining at 111111 even though the input may increase from

V

REF

to VCC. (For optimum performance, V

REF

can be any value from 1.5V to 2.5V.)

5. The data outputs have active pull-ups. The EOC

line is open-collector with a nominal 5kΩ internal pull-up resistor.

Philips Semiconductors Linear Products Product specification

NE50376-Bit A/D converter (parallel outputs)

August 31, 1994

584

AC ELECTRICAL CHARACTERISTICS

VCC=5.0V; V

REF

=2.0V; Clock=1MHz; 0°C ≤ T

A

≤ 70°C unless otherwise specified. Typical values are specified at 25°C (Refer to AC test

figures.)

LIMITS

SYMBOL

PARAMETER

TO

FROM

TEST CONDITIONS

Min Typ Max

UNIT

f

MAX

Maximum clock frequency 1 MHz

t

W

Start pulse width 300 ns

Minimum positive/negative

clock pulse width

300 ns

t

CONV

Conversion time 9 Clock cycles

t

P (OUT DATA)

Propagation delay

1

Data out OE TA=25°C tR=tF≤20ns 500 ns

t

P (OUT EOC)

Propagation delay

2

EOC Clock TA=25°C tR=tF≤20ns 800 ns

t

P (3-STATE)

Propagation delay, 3-State 3-State Data OE TA=25°C tR=tF≤20ns 500 ns

NOTES:

1. Propagation delay of data outputs is defined as the delay in the data outputs reading their final value after the low going edge of OE.

2. Propagation delay of EOC

is defined as the delay in EOC going low, following the low going edge of the 9th clock pulse after the start pulse.

CIRCUIT DESCRIPTION

NE5037 is a complete 6-bit, parallel output, microprocessor

compatible, A/D converter which incorporates the

successive-approximation method. The chip includes the internal

control logic, the successive-approximation register (SAR), 6-bit

DAC, comparator and output buffers. An externally-generated clock

source (max frequency=1MHz) must be provided to Pin 6. An

external reference voltage supplied to Pin 2 sets the full-scale range

of the A/D converter.

The CS

pin must be at a low level prior to the start of the conversion

process. Upon receipt of a START

pulse, the internal control logic

resets the SAR. On the first low-going edge of the clock pulse,

successive approximation conversion commences. Successive bits

beginning with the MSB (D5) are supplied to the input of the internal

6-bit current output DAC by the I

2

L successive approximation

register.

The comparator determines whether the output current of the DAC

is greater or less than the input current, which is converted from the

unknown analog input voltage through the V/I converter. If the DAC

output is greater, that bit of the DAC is set to ”0’ and the

corresponding output buffer goes to ”0’ simultaneously. If it is less, it

stays at ‘1’ and the output buffer also stays at ‘1’. On successive

clock pulses, successive bits of the DAC are tried and the

corresponding output buffer represents the bits of the DAC. On the

eighth low-going edge of the clock pulse (after the receipt of the start

pulse), the EOC

pin goes low, thereby indicating that the conversion

is complete. The output data is now valid. In order to access the

result of the conversion, the OE

pin must be set to a low level. EOC

is reset to a high state when OE is low. When OE is in a ”1’ state,

the output buffers are in a high impedance state.

Refer to Figure 1 for the timing diagram.

DON’T CARE

CS

START

CLK

OE

EOC

DATA

OUTPUTS

HIGH

IMPEDANCE

DATA

READY

HIGH

AVAILABLE

HIGH

IMPEDANCE

HIGH

IMPEDANCE

HIGH

AVAILABLE

Figure 1. Timing Diagram

Loading...

Loading...