INTEGRATED CIRCUITS

74F573

Octal transparent latch (3-State)

74F574

Octal transparent latch (3-State)

Product specification

IC15 Data Handbook

1989 Oct 16

Philips Semiconductors Product specification

74F573/74F574Latch/flip-flop

74F573 Octal Transparent Latch (3-State)

74F574 Octal D Flip-Flop (3-State)

FEA TURES

•74F573 is broadside pinout version of 74F373

•74F574 is broadside pinout version of 74F374

•Inputs and Outputs on opposite side of package allow easy

interface to Microprocessors

•Useful as an Input or Output port for Microprocessors

•3-State Outputs for Bus interfacing

•Common Output Enable

•74F563 and 74F564 are inverting version of 74F573 and 74F574

respectively

•3-State Outputs glitch free during power-up and power-down

•These are High-Speed replacements for N8TS805 and N8TS806

DESCRIPTION

The 74F573 is an octal transparent latch coupled to eight 3-State

output buffers. The two sections of the device are controlled

independently by Enable (E) and Output Enable (OE

The 74F573 is functionally identical to the 74F373 but has a

broadside pinout configuration to facilitate PC board layout and

allow easy interface with microprocessors.

The data on the D inputs is transferred to the latch outputs when the

Enable (E) input is High. The latch remains transparent to the data

input while E is High and stores the data that is present one setup

time before the High-to-Low enable transition.

The 3-State output buffers are designed to drive heavily loaded

3-State buses, MOS memories, or MOS microprocessors. The

active Low Output Enable (OE

independent to the latch operation. When OE

transparent data appears at the outputs. When OE

outputs are in high impedance “off” state, which means they will

neither drive nor load the bus.

) controls all eight 3-State buffers

) control gates.

is Low, the latched or

is High, the

The 74F574 is functionally identical to the 74F374 but has a

broadside pinout configuration to facilitate PC board layout and

allow easy interface with microprocesors.

It is an 8-bit, edge triggered register coupled to eight 3-State output

buffers. The two sections of the device are controlled independently

by the clock (CP) and Output Enable (OE

The register is fully edge-triggered. The state of each D input, one

setup time before the Low-to-High clock transition is transferred to

the corresponding flip-flop’s Q output.

The 3-State output buffers are designed to drive heavily loaded

3-State buses, MOS memories, or MOS microprocessors. The

active Low Output Enable (OE

independently of the latch operation. When OE

or transparent data appears at the outputs. When OE

outputs are in high impedance “off” state, which means they will

neither drive nor load the bus.

TYPE

74F573 5.0ns 35mA

TYPE TYPICAL f

74F574 180MHz 50mA

PROPAGATION DELAY

) controls all eight 3-State buffers

TYPICAL

MAX

) control gates.

is Low, the latched

is High, the

TYPICAL SUPPL Y

CURRENT

(TOTAL)

TYPICAL SUPPL Y

CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

V

DESCRIPTION

20-Pin Plastic DIP N74F573N, N74F574N SOT146-1

20-Pin Plastic SOL N74F573D, N74F574D SOT163-1

20-Pin Plastic SSOP N74F573DB SOT339-1

= 5V ±10%,

CC

T

= 0°C to +70°C

amb

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

D0 - D7 Data inputs 1.0/1.0 20µA/0.6mA

E (74F573) Latch Enable input (active falling edge) 1.0/1.0 20µA/0.6mA

OE Output Enable input (active Low) 1.0/1.0 20µA/0.6mA

CP (74F574) Clock Pulse input (active rising edge) 1.0/1.0 20µA/0.6mA

Q0 - Q7 3-State outputs 150/40 3.0mA/24mA

NOTE: One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

1989 Oct 16 853-0083 97897

2

74F (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

Philips Semiconductors Product specification

74F573/74F574Latch/flip-flop

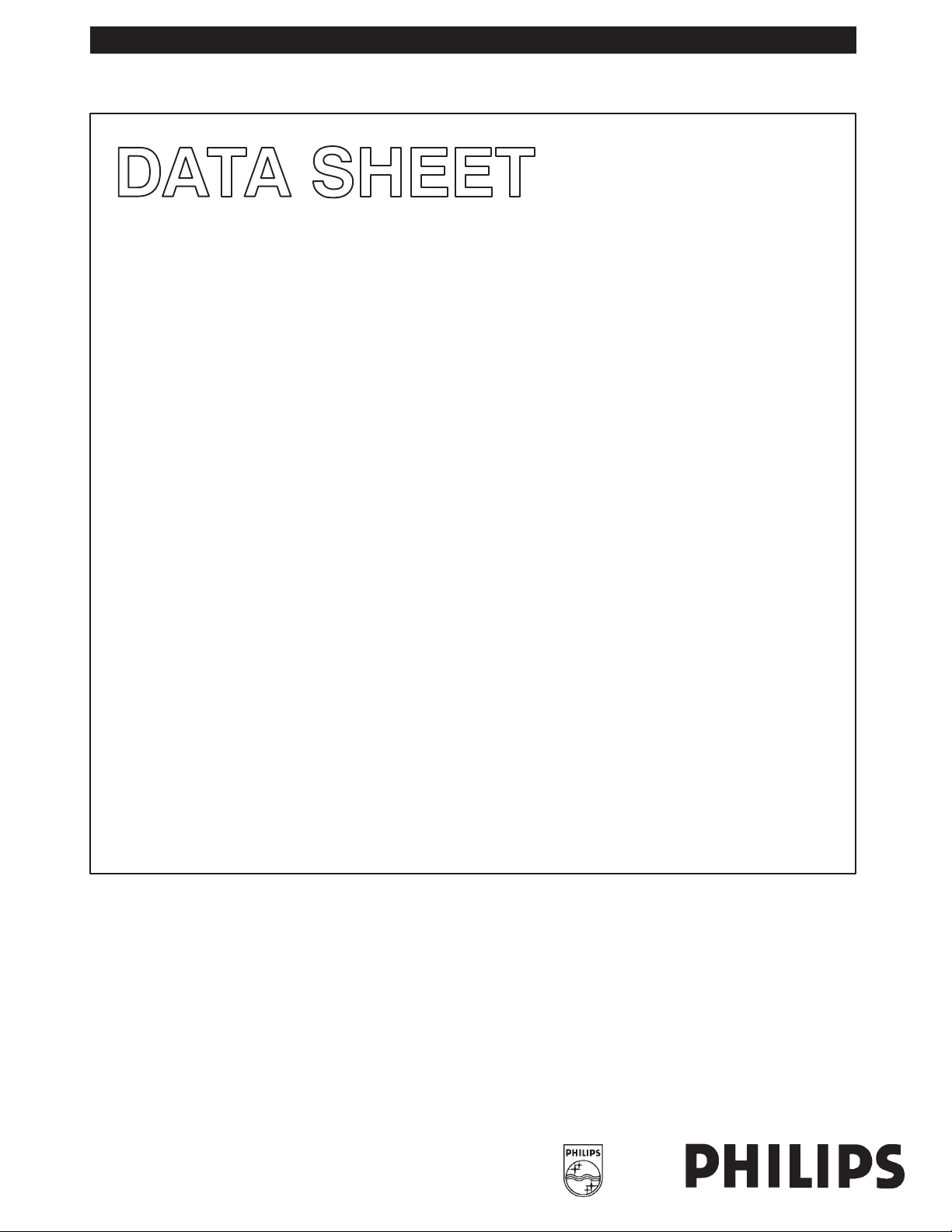

PIN CONFIGURATION – 74F573

1

OE

2

D0

3

D1

4

D2

5

D3

6

D4

7

D5

8

D6

9

D7

10 11

GND

SF01073

LOGIC SYMBOL – 74F573

345678

2

D0 D1Q1D2

11 E

1

OE

Q0

Q2 Q3D3Q4D4Q5

PIN CONFIGURATION – 74F574

20

V

CC

Q0

19

18

Q1

17

Q2

16

Q3

15

Q4

14

Q5

13

Q6

12

Q7

E

1

OE

2

D0

3

D1

4

D2

5

D3

6

D4

7

D5

8

D6

9

D7

10 11

GND

20

19

18

17

16

15

14

13

12

SF01074

V

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

CP

CC

LOGIC SYMBOL – 74F574

D5

D7

Q6D6Q7

9

11 CP

1

OE

345678

2

D0 D1Q1D2

Q0

Q2 Q3D3Q4D4Q5

D5

9

D7

Q6D6Q7

141516171819

VCC=Pin 20

GND=Pin 10

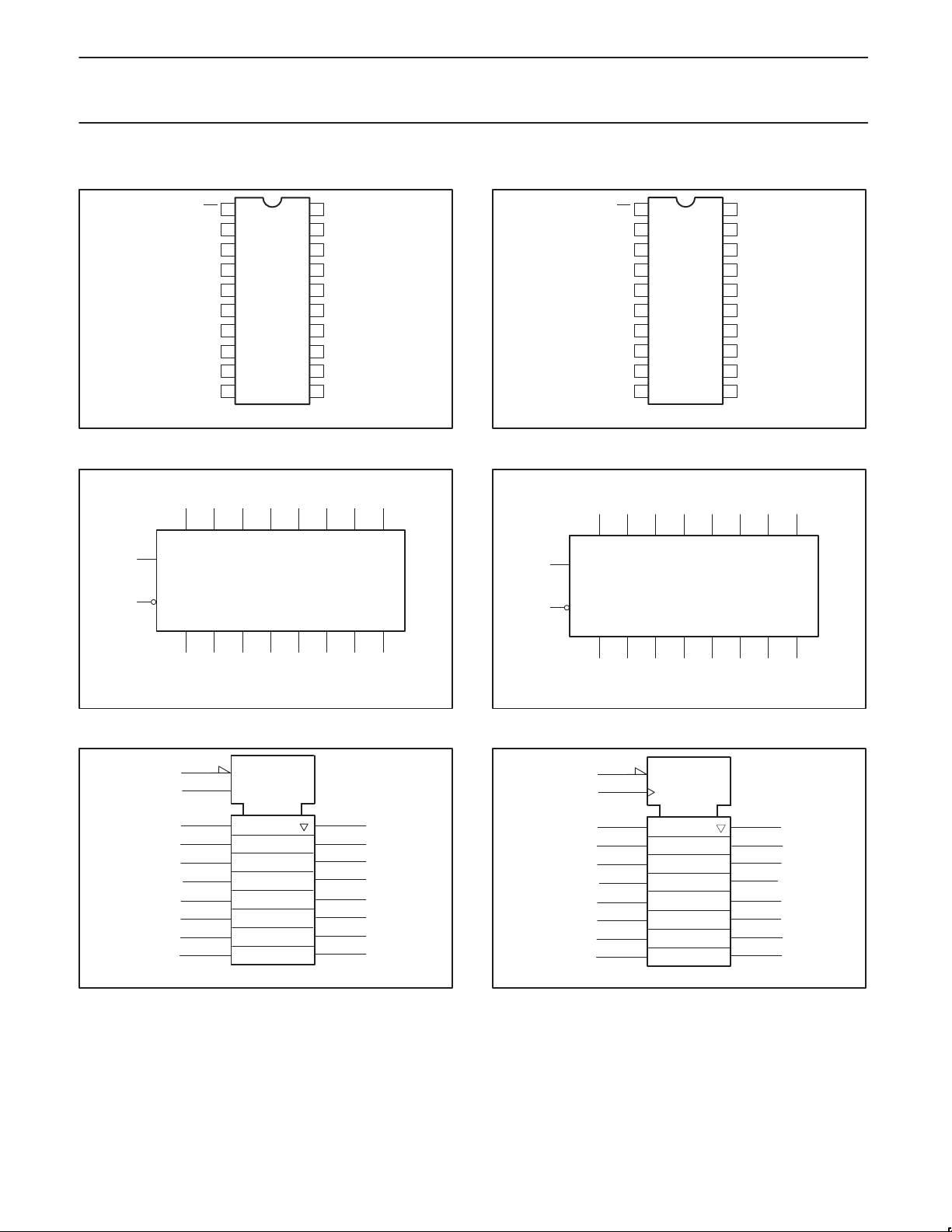

LOGIC SYMBOL (IEEE/IEC) – 74F573

1

11

2

3

4

5

6

7

8

9

EN1

EN2

2D

1

SF01077

19

18

17

16

15

14

13

12

1213

SF01075

141516171819

VCC=Pin 20

GND=Pin 10

LOGIC SYMBOL (IEEE/IEC) – 74F574

1

11

2

3

4

5

6

7

8

9

EN1

C2

2D

1

SF01078

1213

SF01076

19

18

17

16

15

14

13

12

1989 Oct 16

3

Philips Semiconductors Product specification

OPERATING MODES

74F573/74F574Latch/flip-flop

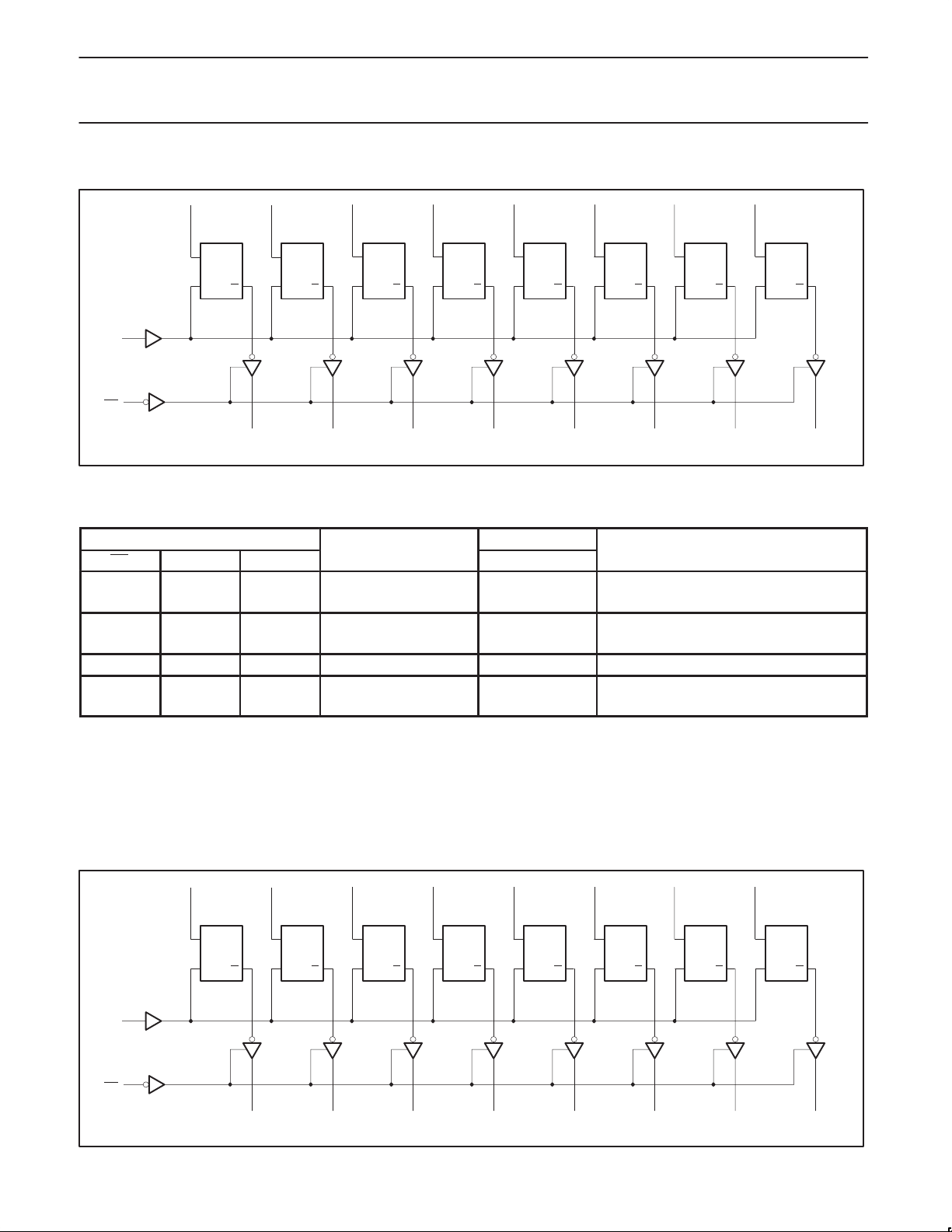

LOGIC DIAGRAM – 74F573

D0 D1 D2 D3 D4 D5 D6 D7

23456789

EDQ EDQ EQDEDQ EDQ EDQ EDQ EDQ

11

E

1

OE

VCC=Pin 20

GND=Pin 10

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

1213141516171819

SF01079

FUNCTION TABLE – 74F573

INPUTS

OE E Dn

L

L

L

L

H

H

H

↓

↓

L

l

h

INTERNAL

REGISTER

L

H

L

H

L L X NC NC Hold

H

H

L

H

X

Dn

NC

Dn

H = High voltage level

h = High voltage level one setup time prior to the High-to-Low E transition

L = Low voltage level

l = Low voltage level one setup time prior to the High-to-Low E transition

NC= No change

X = Don’t care

Z = High impedance “off” state

↓ = High-to-Low E transition

OUTPUTS

Q0 – Q7

L

H

L

H

Z

Z

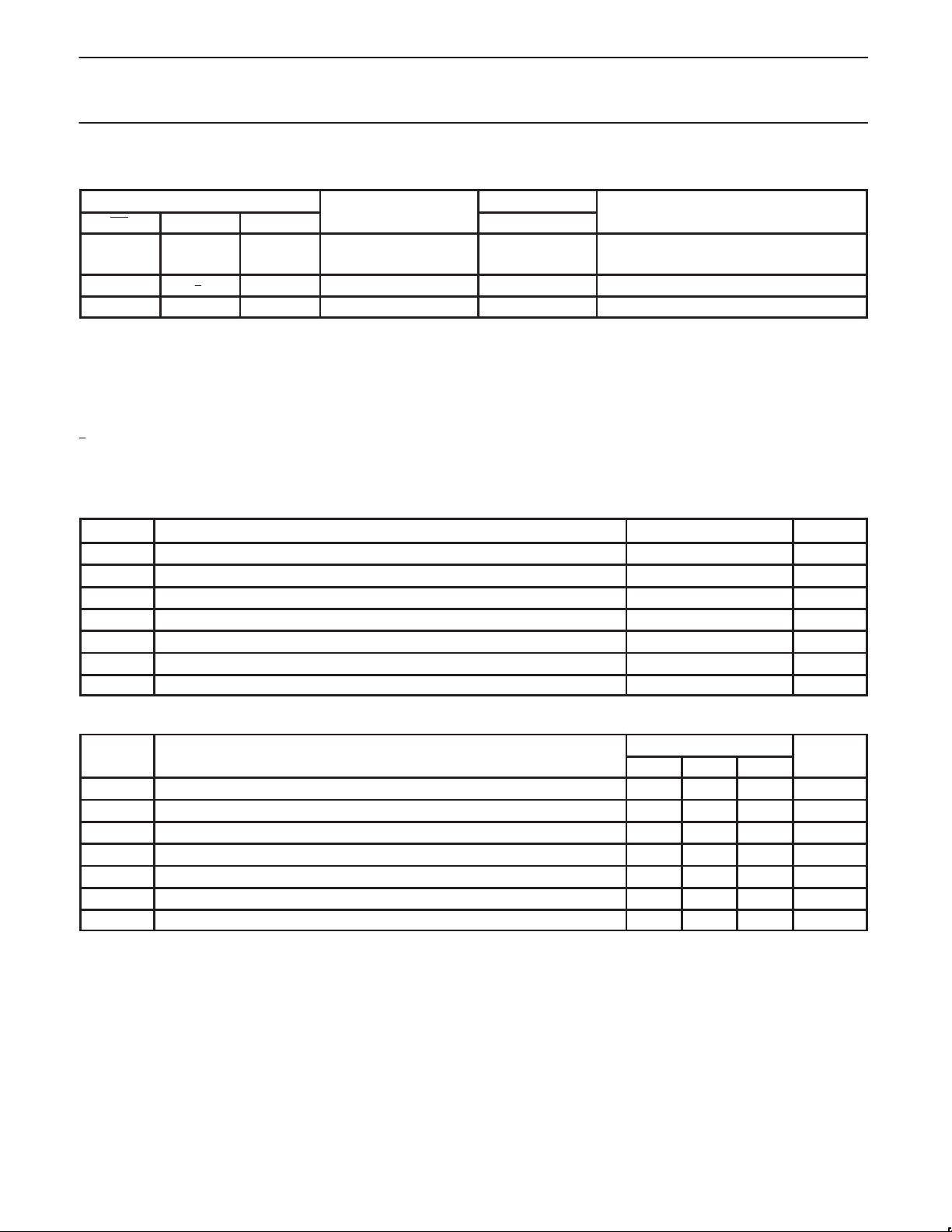

LOGIC DIAGRAM – 74F574

D0 D1 D2 D3 D4 D5 D6 D7

23456789

D

Load and read register

Latch and read register

Disable outputs

11

CP

1

OE

VCC=Pin 20

GND=Pin 10

1989 Oct 16

CPDQ CPDQ CP Q

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

CPDQ CPDQ CPDQ CPDQ CPDQ

4

1213141516171819

SF01080

Philips Semiconductors Product specification

OPERATING MODES

SYMBOL

PARAMETER

UNIT

74F573/74F574Latch/flip-flop

FUNCTION TABLE – 74F574

INPUTS

OE CP Dn

L

L

↑

↑

l

h

INTERNAL

REGISTER

L

H

L ↑ X NC NC Hold

H ↑ Dn Dn Z Disable outputs

H = High voltage level

h = High voltage level one setup time prior to the Low-to-High clock transition

L = Low voltage level

l = Low voltage level one setup time prior to the Low-to-High clock transition

NC= No change

X = Don’t care

Z = High impedance “off” state

↑ = Low-to-High clock transition

= Not a Low-to-High clock transition

↑

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limits set forth in this table may impair the useful life of the device.

Unless otherwise noted these limits are over the operating free-air temperature range.)

SYMBOL

V

CC

V

IN

I

IN

V

OUT

I

OUT

T

amb

T

stg

Supply voltage –0.5 to +7.0 V

Input voltage –0.5 to +7.0 V

Input current –30 to +5.0 mA

Voltage applied to output in High output state –0.5 to +V

Current applied to output in Low output state 48 mA

Operating free-air temperature range 0 to +70 °C

Storage temperature –65 to +150 °C

PARAMETER RATING UNIT

OUTPUTS

Q0 – Q7

L

H

Load and read register

CC

V

RECOMMENDED OPERATING CONDITIONS

V

V

V

I

I

I

T

CC

IH

IL

IK

OH

OL

amb

Supply voltage 4.5 5.0 5.5 V

High-level input voltage 2.0 V

Low-level input voltage 0.8 V

Input clamp current –18 mA

High-level output current –3 mA

Low-level output current 24 mA

Operating free-air temperature range 0 70 °C

LIMITS

MIN NOM MAX

1989 Oct 16

5

Loading...

Loading...