Philips N74F521D, N74F521N Datasheet

INTEGRATED CIRCUITS

74F521

8-bit identity comparator

Product specification

IC15 Data Handbook

1990 May 15

Philips Semiconductors Product specification

74F5218-bit identity comparator

FEA TURES

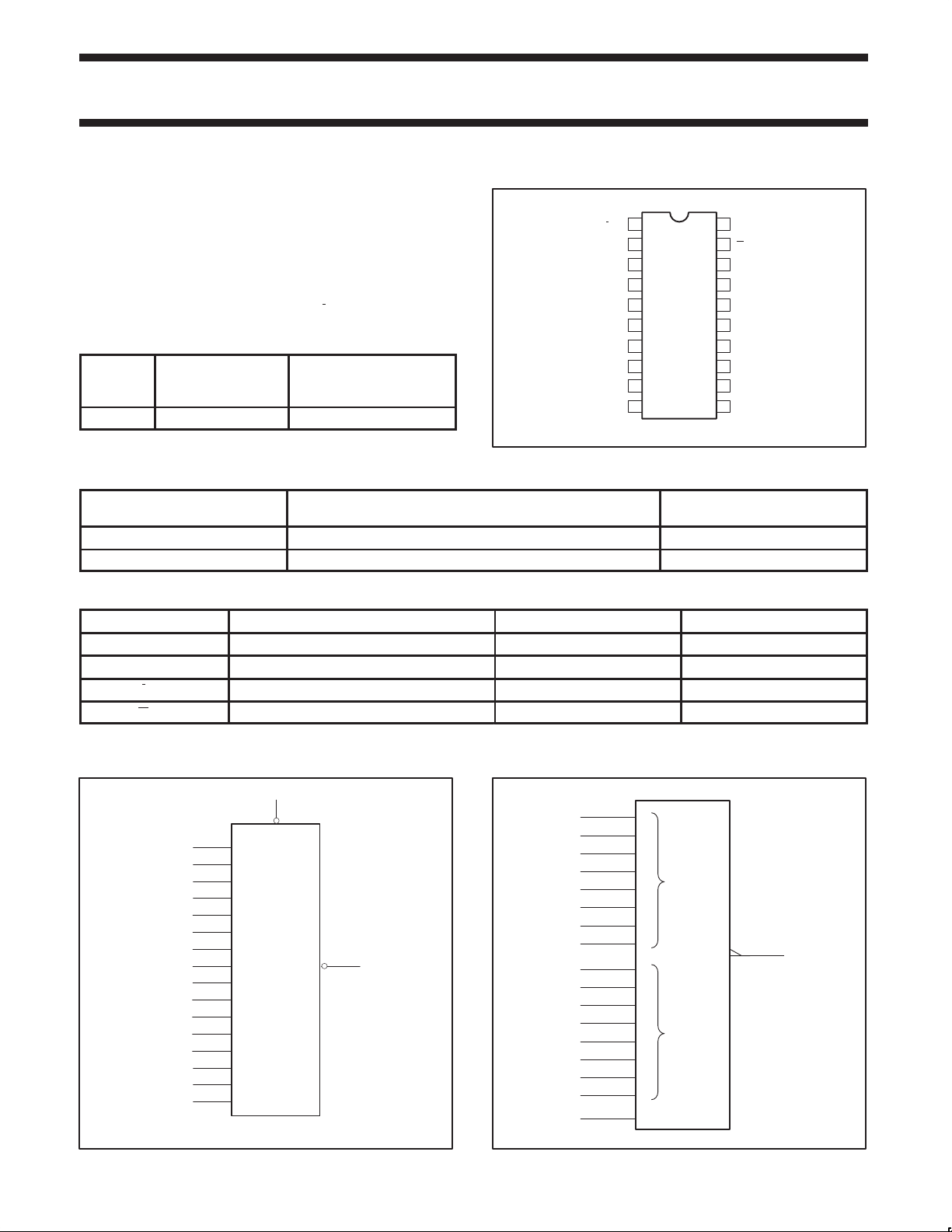

PIN CONFIGURATION

•Compares two 8-bit words in 6.5ns typical

•Expandable to any word length

DESCRIPTION

The 74F521 is an expandable 8-bit comparator. It compares two

words of up to 8 bits each and provides a Low output when the two

words match bit for bit. The expansion input I

active-Low enable input.

TYPICAL

TYPE

PROPAGATION

DELA Y

74F521 7.0ns 24mA

ORDERING INFORMA TION

DESCRIPTION

20-pin plastic DIP N74F521N SOT146-1

20-pin plastic SOL N74F521D SOT163-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION 74F (U.L.) HIGH/LOW LOAD VALUE HIGH/LOW

A0 – A7 Word A inputs 1.0/1.0 20µA/0.6mA

B0 – B7 Word B inputs 1.0/1.0 20µA/0.6mA

I

A=B

Q

A=B

NOTE: One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

Expansion or Enable input (active Low) 1.0/1.0 20µA/0.6mA

Identity output (active Low) 50/33 1.0mA/20mA

also serves as an

A=B

TYPICAL

SUPPLY CURRENT

(TOTAL)

COMMERCIAL RANGE

VCC = 5V ±10%, T

= 0°C to +70°C

amb

I

GND

1

A=B

2

A0

3

B0

4

A1

5

B1

6

A2

7

B2

8

A3

9

B3

10 11

20

19

18

17

16

15

14

13

12

SF00273

PKG DWG #

V

CC

Q

A=B

B7

A7

B6

A6

B5

A5

B4

A4

LOGIC SYMBOL

1

I

A=B

2

3

4

5

6

7

8

9

11

12

13

14

15

16

17

18

VCC = Pin 20

GND = Pin 10

May 15, 1990 853–0372 99601

A0

B0

A1

B1

A2

B2

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

Q

A=B

19

SF00274

IEC/IEEE SYMBOL

2

2

4

6

8

11

13

15

17

3

5

7

9

12

14

15

18

1

0

3

0

7

EN

COMP

A

B

A=B

19

SF00275

Philips Semiconductors Product specification

74F5218-bit identity comparator

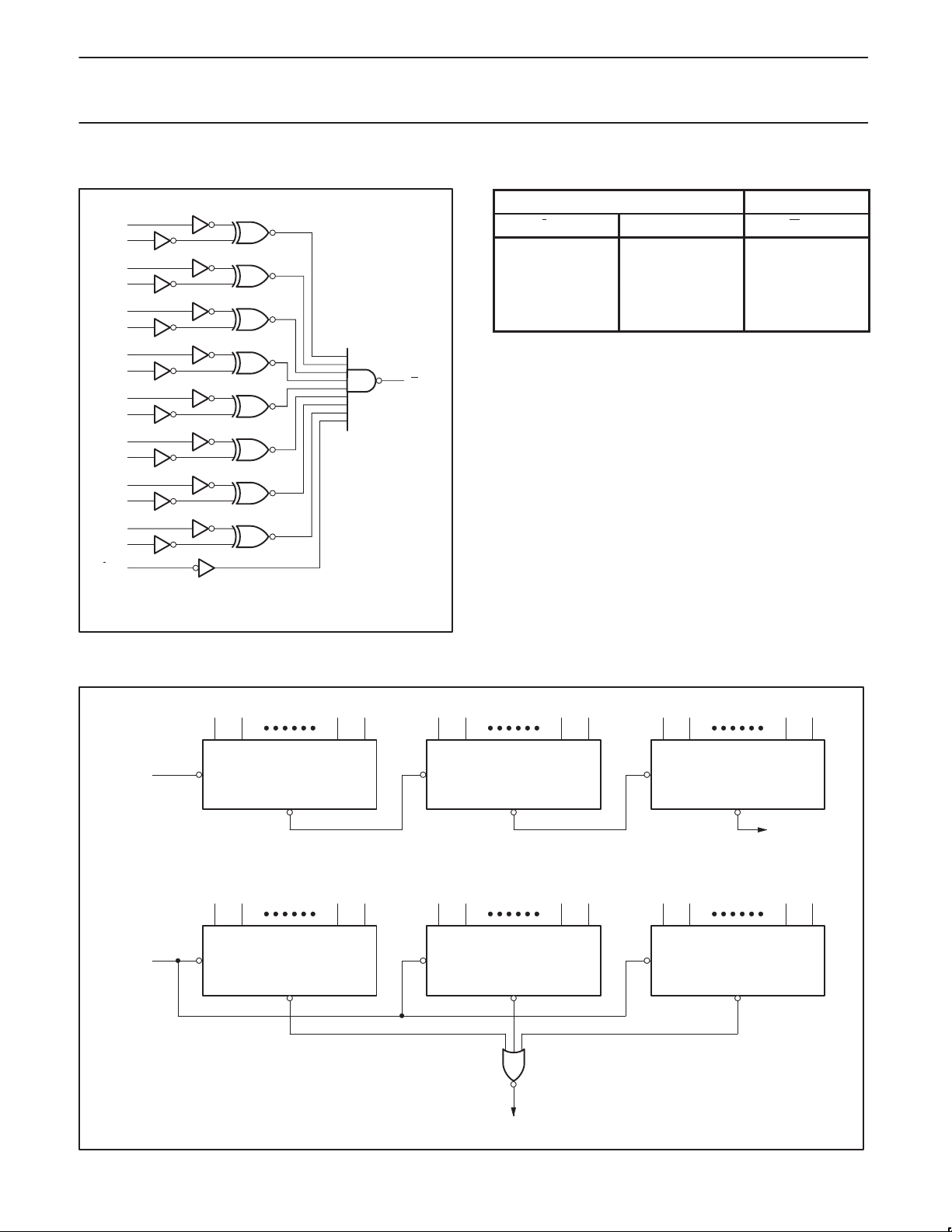

LOGIC DIAGRAM

2

A0

3

B0

4

A1

5

B1

6

A2

7

B2

8

A3

9

B3

11

A4

12

B4

13

A5

14

B5

15

A6

16

B6

17

A7

18

B7

1

I

A=B

VCC = Pin 20

GND = Pin 10

19

Q

SF00276

A=B

FUNCTION TABLE

INPUTS OUTPUT

I

A=B

L A=B* L

L A≠B H

H A=B* H

H A≠B H

H = High voltage level

L = Low voltage level

X = Don’t care

* A0=B0, A1=B1, A2=B2, etc.

A, B Q

A=B

APPLICATIONS

ENABLE

LOW

ENABLE

LOW

A0 B0 A7 B7

I

A=B

Q

A=B

A0 B0 A7 B7

I

A=B

Q

A=B

A8 B8 A15 B15

I

A=B

Q

A=B

RIPPLE EXPANSION

A8 B8 A15 B15

I

A=B

Q

A=B

A16 B16 A23 B23

I

A=B

Q

A=B

A16 B16 A23 B23

I

A=B

Q

A=B

May 15, 1990

PARALLEL EXPANSION

3

SF00277

Loading...

Loading...