Philips N74F456N, N74F456D Datasheet

74F455*, 74F456

Buffers/drivers

Product specification

Supersedes data of 1990 Nov 26

IC15 Data Handbook

1999 Jan 08

INTEGRATED CIRCUITS

* Discontinued part. Please see the Discontinued Product List.

Philips Semiconductors Product specification

74F455,* 74F456Buffers/Drivers

74F455 Octal Buffer/Driver with Parity, Inverting (3-State)

74F456 Octal Buffer/Driver with Parity, Non-Inverting (3-State)

2

1999 Jan 08 853–0371 20616

* Discontinued part. Please see the Discontinued Products List.

FEA TURES

•High impedance NPN base inputs for reduced loading

(40µA in High and Low states)

•74F456 combines 74F244 and 74F280A functions in one package

•74F456 is a center pin version of the 74F656A

•74F456 Non-Inverting

•3-State outputs sink 64mA and source 15mA

•24-pin plastic Slim DIP (300 mil) package

•Broadside pinout simplifies PC board layout

DESCRIPTION

The 74F455 and 74F456 are octal buffers and line drivers with parity

generation/checking designed to be employed as memory address

drivers, clock drivers and bus-oriented transmitters/receivers. These

parts include parity generator/checker to improve PC board density.

TYPE

TYPICAL

PROPAGATION

DELA Y

TYPICAL SUPPL Y CURRENT

(TOT AL)

74F455 6.5ns 64mA

74F456 7.5ns 64mA

ORDERING INFORMATION

DESCRIPTION

COMMERCIAL

RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

PKG DWG #

24-pin plastic Slim

DIP (300mil)

N74456N SOT222-1

24-pin plastic SOL N74456D SOT137-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

D0–D7 Data inputs 2.0/0.066 40µA/40µA

PI Parity input 1.0/0.033 20µA/20µA

OE0, OE1 Output Enable inputs (active Low) 1.0/0.033 20µA/20µA

ΣE, ΣO Parity outputs 750/106.7 15mA/64mA

Q0–Q7 Data outputs (75F455) 750/106.7 15mA/64mA

Q0–Q7 Data outputs (75F456) 750/106.7 15mA/64mA

NOTE: One (1.0) FAST Unit Load (U.L.) is defined as 20µA in the High state and 0.6mA in the Low state.

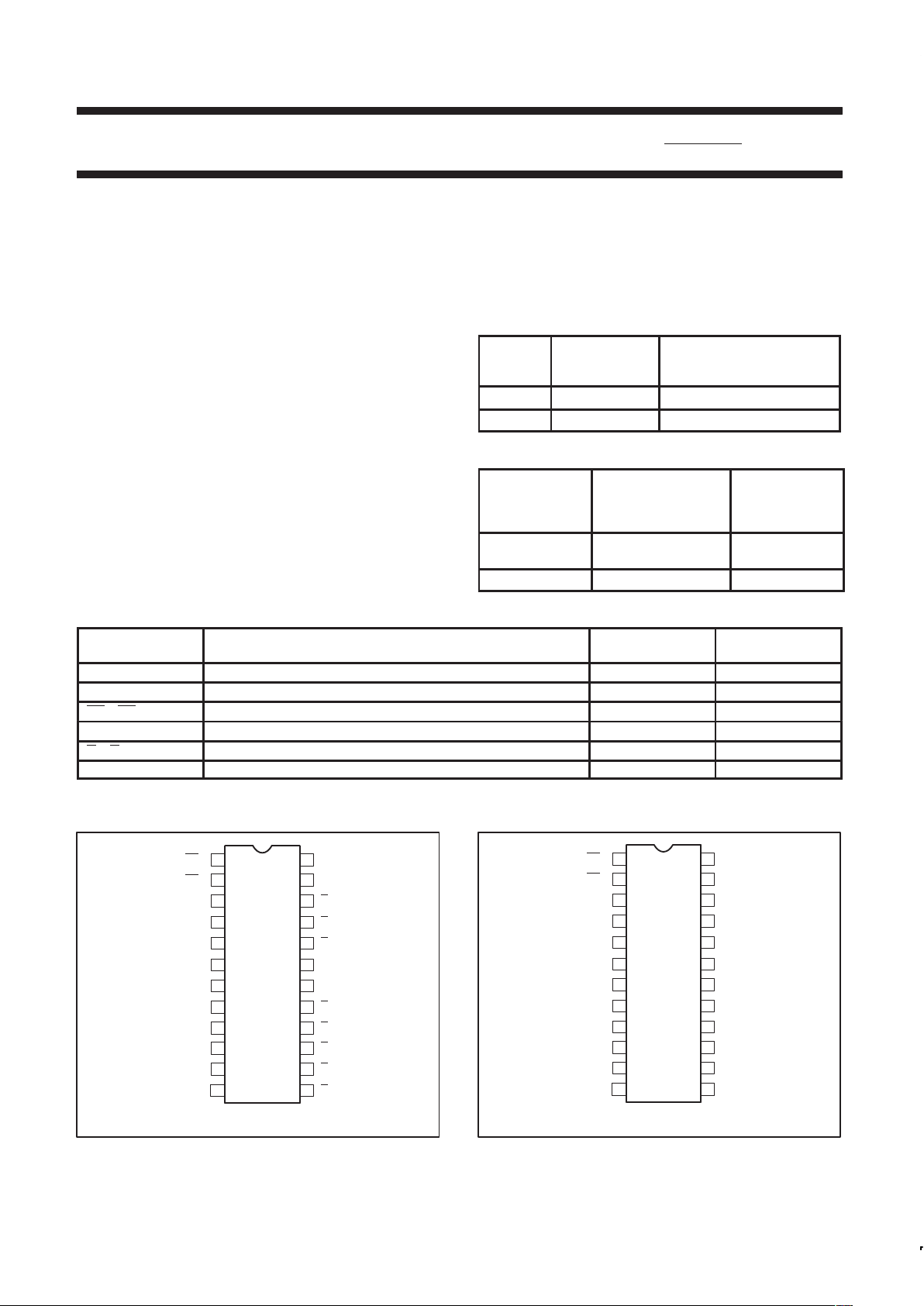

PIN CONFIGURATION – 74F455

24

23

22

21

20

19

18

17

16

15

14

1312

10

11

9

8

7

6

5

4

3

2

1

OE

0

OE

1

PI

D0

D1

D2

D3

D4

D5

D6

D7 Q

7

Q

6

Q5

Q

4

Q3

Q

2

Q

1

Q

0

ΣE

ΣO

GND

GND

V

CC

SF00969

PIN CONFIGURATION – 74F456

24

23

22

21

20

19

18

17

16

15

14

1312

10

11

9

8

7

6

5

4

3

2

1

OE

0

OE

1

PI

D0

D1

D2

D3

D4

D5

D6

D7 Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

ΣE

ΣO

GND

GND

V

CC

SF00958

Philips Semiconductors Product specification

74F455,* 74F456Buffers/Drivers

1999 Jan 08

3

* Discontinued part. Please see the Discontinued Products List.

LOGIC SYMBOL – 74F455

D0 D1 D2 D3 D4 D5 D6 D7

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

OE0

OE1

PI

ΣE

ΣO

45689101112

23

24

1

2

3

22 21 20 17 16 15 14 13

SF00959

VCC= Pin 7

GND = Pin 18, 19

LOGIC SYMBOL (IEEE/IEC) – 74F455

SF00961

4

6

8

9

3,5,6,7,8

9,10,11,12

1

2

2K

21

20

17

Z6

5

22

10

11

12

15

14

13

16

4

24

23

3

Z5

Z8

Z7

Z9

Z11

Z10

Z12

1

EN4

P3

3,5,6,7,8

9,10,11,12

[EVEN]

[ODD]

LOGIC SYMBOL – 74F456

D0 D1 D2 D3 D4 D5 D6 D7

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

OE0

OE1

PI

ΣE

ΣO

45689101112

23

24

1

2

3

22 21 20 17 16 15 14 13

SF00960

VCC= Pin 7

GND = Pin 18, 19

LOGIC SYMBOL (IEEE/IEC) – 74F456

SF00962

4

6

8

9

3,5,6,7,8

9,10,11,12

1

2

2K

21

20

17

Z6

5

22

10

11

12

15

14

13

16

4

24

23

3

Z5

Z8

Z7

Z9

Z11

Z10

Z12

1

EN4

P3

3,5,6,7,8

9,10,11,12

[EVEN]

[ODD]

FUNCTION T ABLE

INPUTS

OUTPUTS

74F455 74F456

OE0 OE1 Dn Qn Qn

L L L H L

L L H L H

H X X Z Z

X H X Z Z

H = High voltage level

L = Low voltage level

Z = High impedance “off” state

X = Don’t care

FUNCTION TABLE for PARITY OUTPUTS

INPUTS OUTPUTS

Number of inputs, High (PI, D0 - D7) ΣE ΣO

Even - 0, 2, 4, 6, 8 H L

Odd - 1, 3, 5, 7, 9 L H

Any OEn = High Z Z

H = High voltage level

L = Low voltage level

Z = High impedance “off” state

X = Don’t care

Philips Semiconductors Product specification

74F455,* 74F456Buffers/Drivers

1999 Jan 08

4

* Discontinued part. Please see the Discontinued Products List.

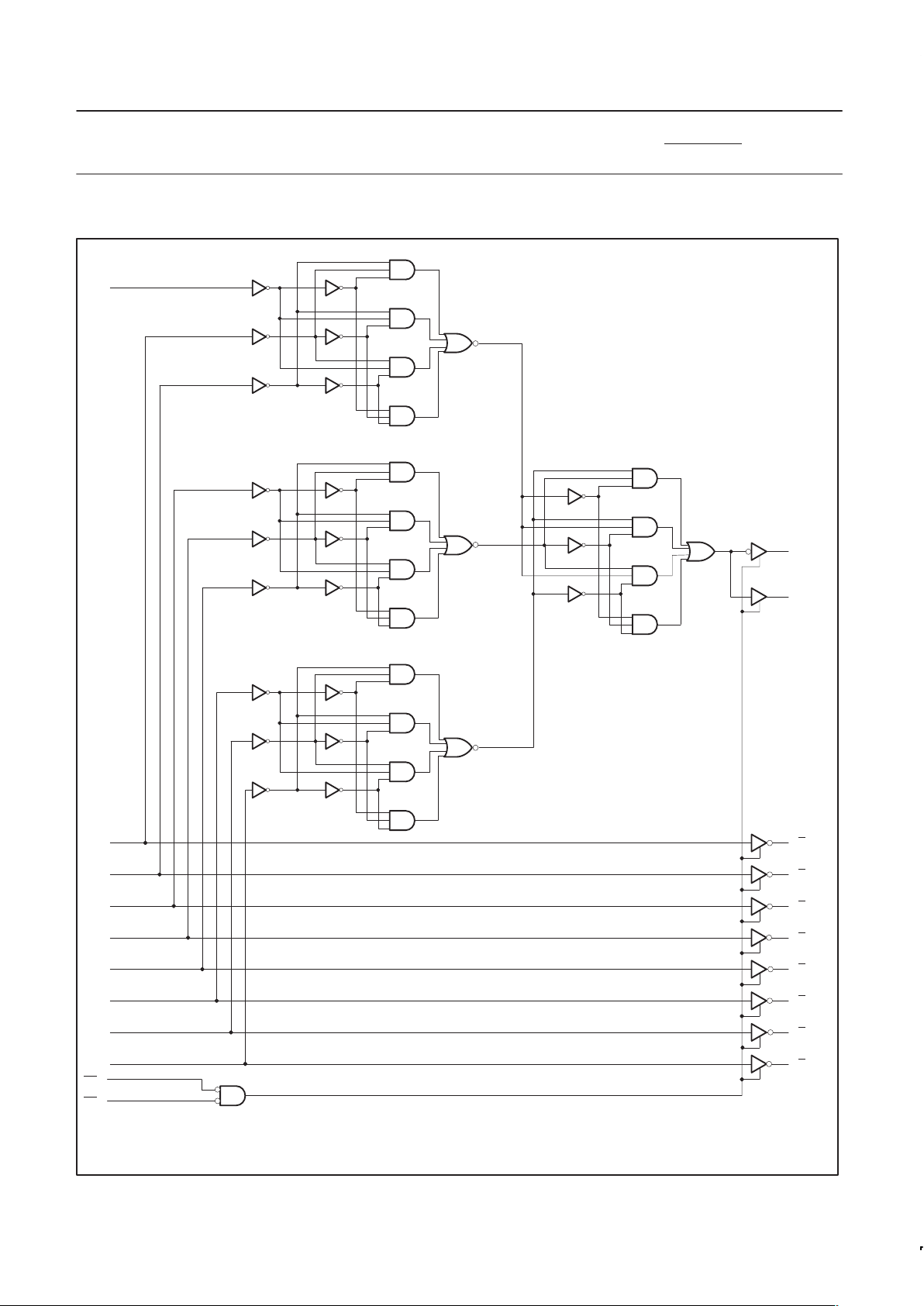

LOGIC DIAGRAM for 74F455

3

4

5

6

8

9

10

11

12

1

2

22

21

20

17

16

15

14

13

23

24

Q

0

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

ΣE

ΣO

D0

D1

D2

D3

D4

D5

D6

D7

OE

0

OE

1

PI

SF00963

VCC= Pin 7

GND = Pin 18, 19

Loading...

Loading...