Philips N74F379AN, N74F379AD Datasheet

INTEGRATED CIRCUITS

74F379A

Quad register

Product specification

IC15 Data Handbook

1996 Mar 12

Philips Semiconductors Product specification

74F379AQuad register

FEA TURES

• Edge–triggered D–type inputs

• Buffered positive edge–triggered clock

• Buffered common enable input

DESCRIPTION

The 74F379A is a 4–bit register with buffered common

enable (E

features the common enable rather than common master

reset.

). This device is similar to the 74F175A but

• True and complementary outputs

• Offers light loading PNP inputs (I

TYPE TYPICAL f

74F379A 200MHz 29mA

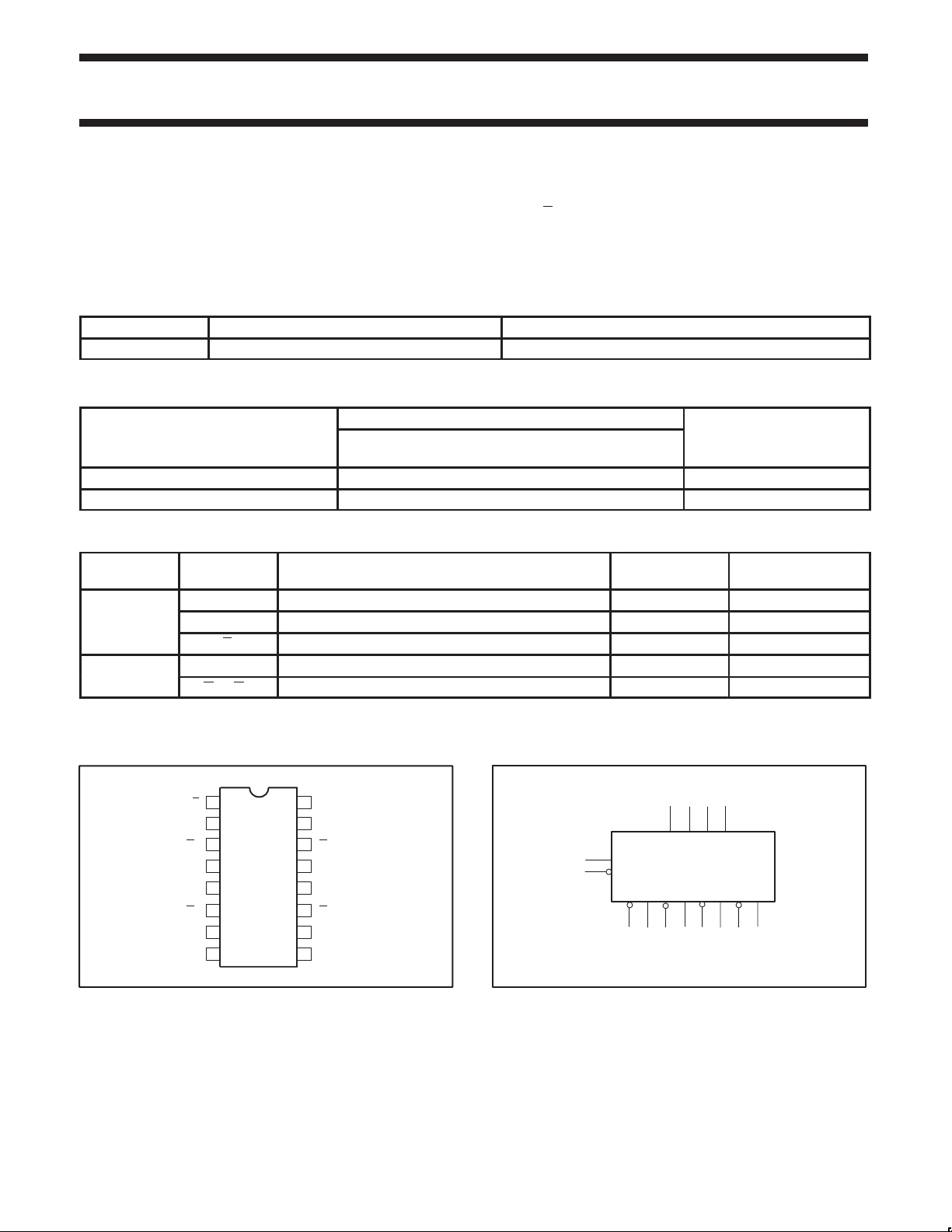

ORDERING INFORMATION

DESCRIPTION COMMERCIAL RANGE

16–pin plastic DIP N74F379AN SOT38–4

16–pin plastic SO N74F379AD SOT109–1

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

TYPE PINS DESCRIPTION 74F (U.L.) HIGH/

D0 – D3 Data inputs 1.0/0.033 20µA/20µA

74F379A CP Clock pulse input (active rising edge) 1.0/0.033 20µA/20µA

E Enable input (active low) 1.0/0.033 20µA/20µA

Q0 – Q3 T rue outputs 50/33 1.0mA/20mA

Q0 – Q3 Complementary outputs 50/33 15mA/20mA

Note to input and output loading and fan out table

1. One (1.0) FAST unit load is defined as: 20µA in the high state and 0.6mA in the low state.

= –20µA)

IL

max

V

= 5V ±10%, T

CC

ORDER CODE

= 0°C to +70°C

amb

TYPICAL SUPPLY CURRENT (TOTAL)

PKG, DWG. #

LOAD VALUE

LOW

HIGH/LOW

PIN CONFIGURATION

1

E

2

Q0

0

3

Q

D0

4

D1

5

1

Q

6

Q1

GND

1996 Mar 12 853-0027 16555

16

V

15

Q3

14

Q

D3

13

D2

12

Q

11

Q2

107

CP

98

SF00354

CC

3

2

LOGIC SYMBOL

VCC = Pin 16

GND = Pin 8

2

9

CP

E

1

Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3

3 2 6 7 11 10 14 15

4 5 12 13

D0 D1 D2 D3

SF00355

Philips Semiconductors Product specification

74F379AQuad register

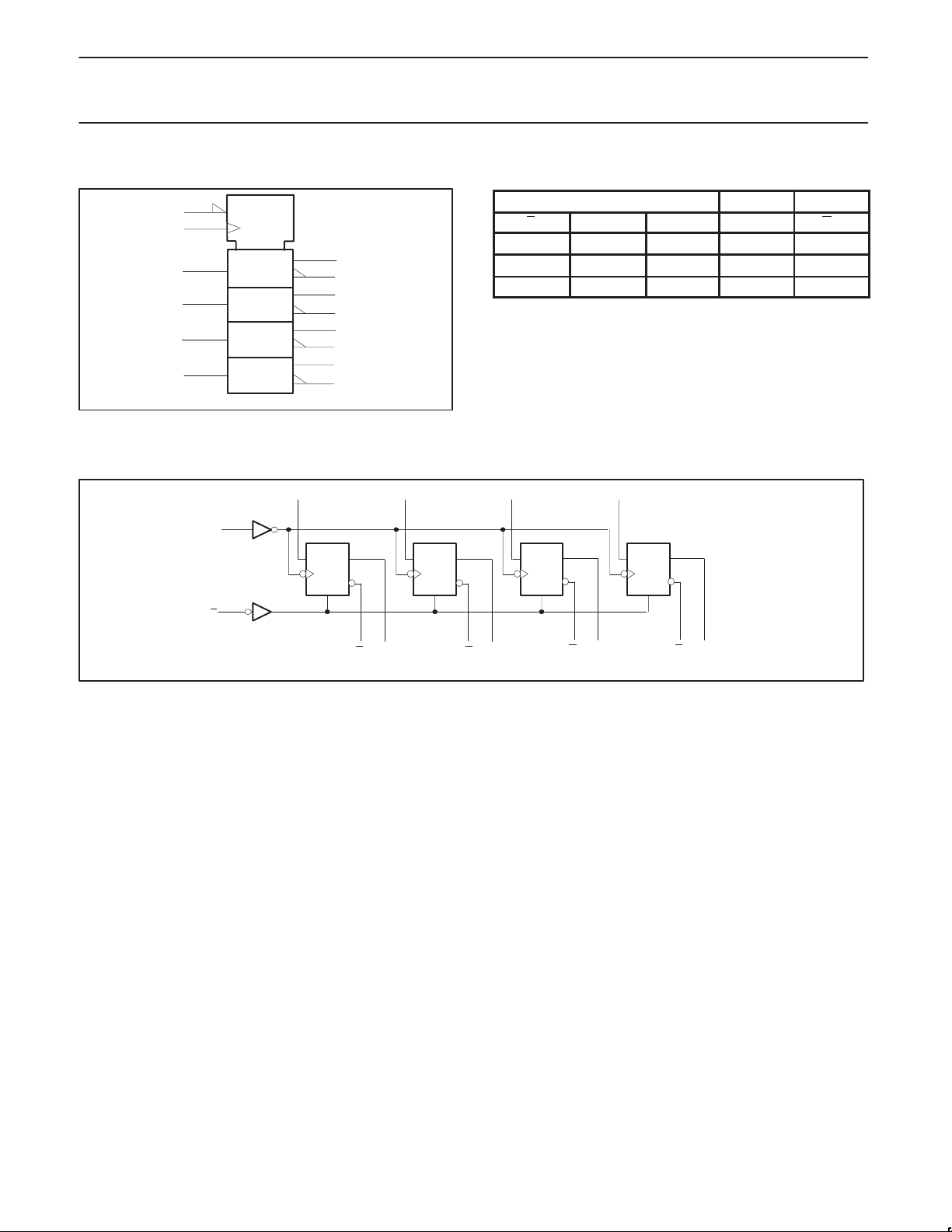

IEC/IEEE SYMBOL

1

9

4

5

12

13

LOGIC DIAGRAM

VCC = Pin 16

GND = Pin 8

CP

FUNCTION TABLE

G1

1C2

2

2D

3

7

6

10

11

15

14

SF00356

E CP Dn Qn Qn

H ↑ X NC NC

L ↑ h H L

L ↑ l L H

Notes to function table

H = High–voltage level

h = High state must be present one setup time

before the low–to–high clock transition

L = Low–voltage level

l = Low state must be present one setup time

before the low–to–high clock transition

NC= No change

X = Don’t care

↑ = Low–to–high clock transition

D0

9

1

E

4

DQ

CP

E

D1

5

DQ

CP

E

32 67

Q

0Q0

D2

12

DQ

CP

Q1Q1

INPUTS OUTPUTS OUTPUT

D3

13

DQ

CP

E

11 10

Q2Q2

E

Q

14 15

Q3Q3

SF00357

1996 Mar 12

3

Loading...

Loading...