Philips N74F280AN, N74F280BN, N74F280BD, N74F280AD Datasheet

74F280B

9-bit odd/even parity generator/checker

Product specification

IC15 Data Handbook

1996 Mar 12

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74F280B9-bit odd/even parity generator/checker

2

1996 Mar 12 853-0363 16555

FEA TURES

•High-impedance NPN base inputs for reduced loading

(20µA in Low and High states)

•Buffered inputs — one normalized load

•Word length easily expanded by cascading

•Industrial temperature range available (–40°C to +85°C)

DESCRIPTION

The 74F280B is a 9-bit Parity Generator or Checker commonly used

to detect errors in high speed data transmission or data retrieval

systems. Both Even (∑

E

) and Odd (∑O) parity outputs are available

for generating or checking even or odd parity on up to 9 bits.

The Even (∑

E

) parity output is High when an even number of Data

inputs (I

0

- I8) are High. The Odd (∑O) parity output is High when an

odd number of Data inputs are High.

Expansion to larger word sizes is accomplished by tying the Even

(∑

E

) outputs of up to nine parallel devices to the data inputs of the

final stage. This expansion scheme allows an 81-bit data word to be

checked in less than 20ns.

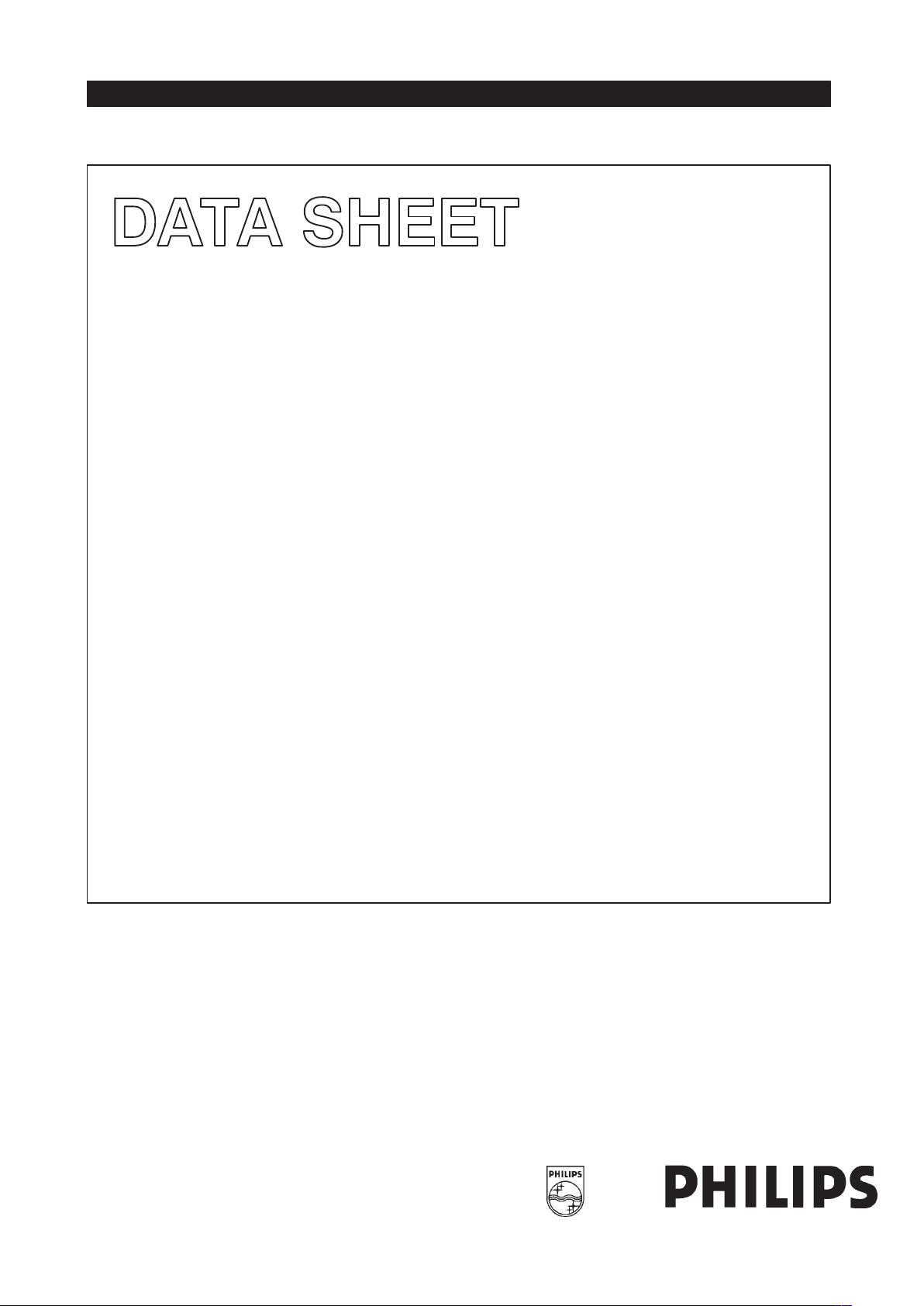

PIN CONFIGURATION

14

13

12

11

10

9

87

6

5

4

3

2

1

V

CC

I

5

I

4

I

3

I

2

I

1

I

0

I

6

I

7

I

8

Σ

E

GND

NC

Σ

O

SF00849

TYPE

TYPICAL

PROPAGATION

DELAY

TYPICAL

SUPPLY CURRENT

(TOTAL)

74F280B 5.5ns 26mA

ORDERING INFORMATION

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

INDUSTRIAL RANGE

V

CC

= 5V ±10%,

T

amb

= –40°C to +85°C

PKG. DWG. #

14-pin plastic DIP N74F280BN I74F280BN SOT27-1

14-pin plastic SO N74F280BD I74F280BD SOT108-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

I0 - I

8

Data inputs 1.0/0.033 20µA/20µA

∑E, ∑

O

Parity outputs 50/33 1.0mA/20mA

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

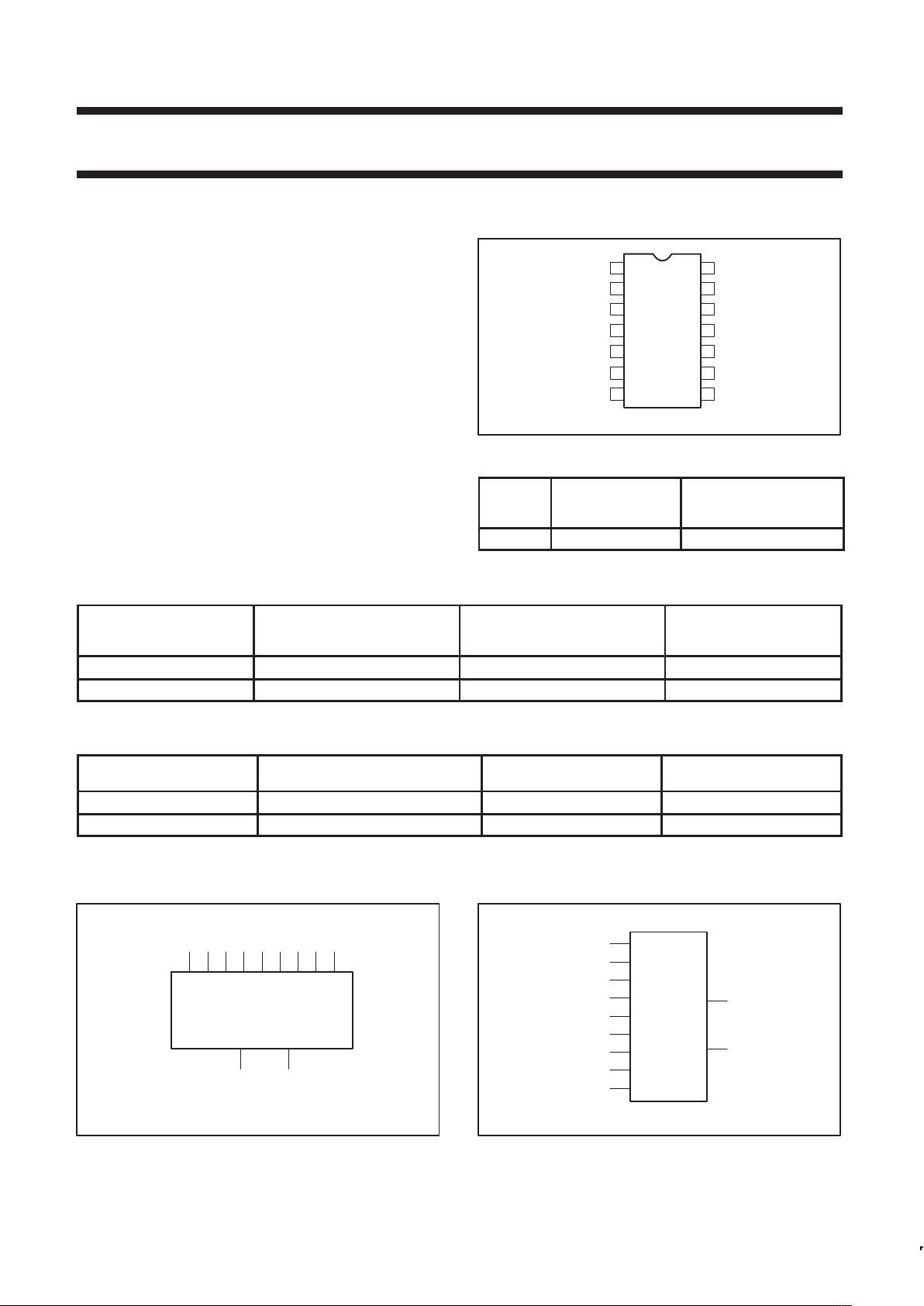

LOGIC SYMBOL

8 9 10 11 12 13 1 2 4

56

Σ

O

Σ

E

I0I1I2I3I4I5I6I7I

8

SF00845

IEC/IEEE SYMBOL

8

9

10

11

12

13

1

2

4

5

6

Σ

O

Σ

E

VCC=Pin 14

GND=Pin 7

2K

SF00846

Philips Semiconductors Product specification

74F280B9-bit odd/even parity generator/checker

1996 Mar 12

3

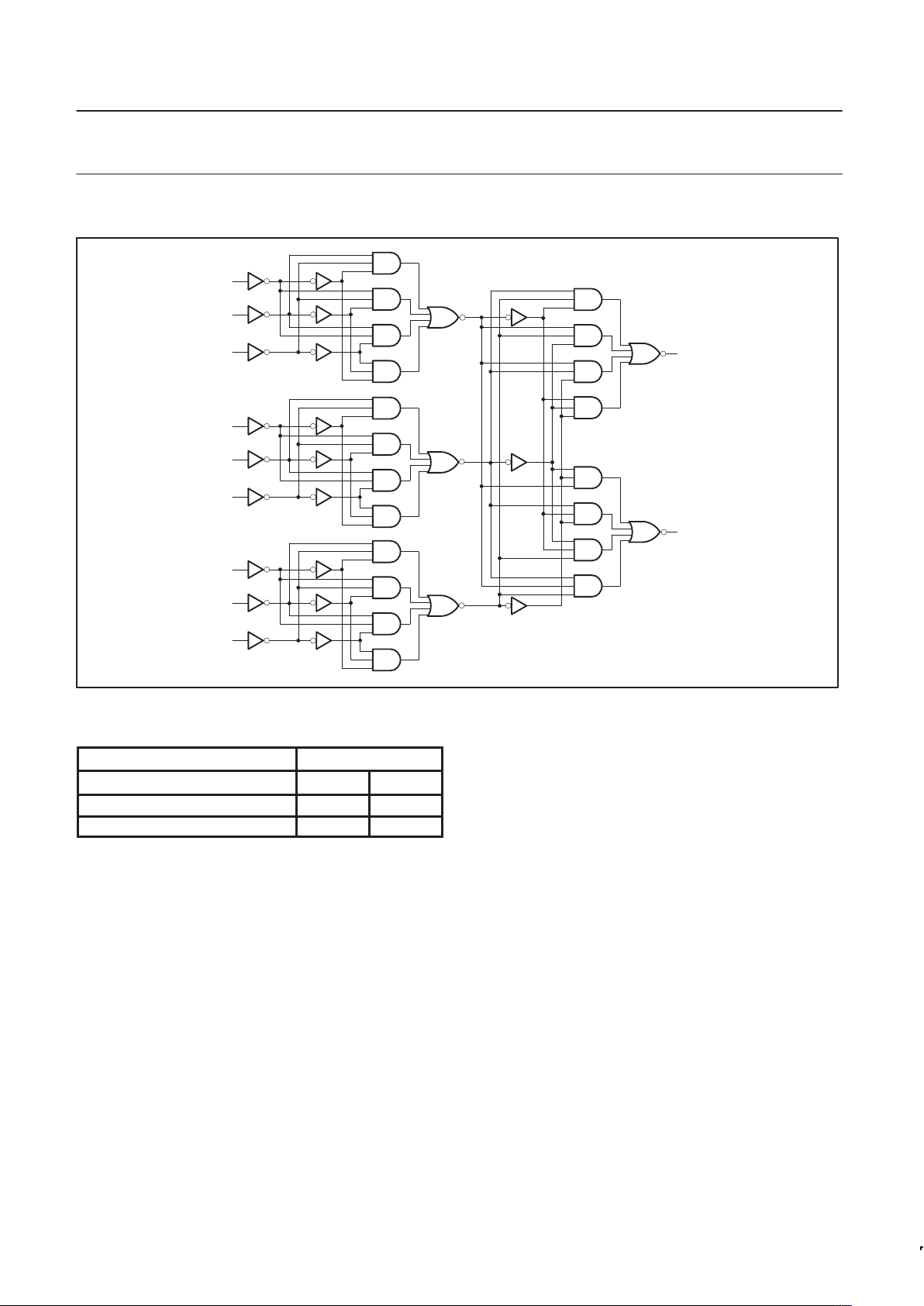

LOGIC DIAGRAM

Σ

E

Σ

O

5

6

8

9

10

11

12

13

1

2

4

I

0

I

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

SF00847

VCC=Pin 14

GND=Pin 7

FUNCTION TABLE

INPUTS OUTPUTS

Number of High Data Inputs (I0 - I8)

∑

E

∑

O

Even — 0, 2, 4, 6, 8 H L

Odd — 1, 3, 5, 7, 9 L H

H = High voltage level

L = Low voltage level

Loading...

Loading...