Philips N74F269D, N74F269N, N74F269DB Datasheet

INTEGRATED CIRCUITS

74F269

8-bit bidirectional binary counter

Product specification 1996 Jan 05

IC15 Data Handbook

Philips Semiconductors Product specification

74F2698–bit bidirectional binary counter

FEA TURES

•Synchronous counting and loading

•Built-in look-ahead carry capability

•Count frequency 115MHz typ

•Supply current 95mA typ

DESCRIPTION

The 74F269 is a fully synchronous 8-stage Up/Down Counter

featuring a preset capability for programmable operation, carry

look-ahead for easy cascading and a U/D

direction of counting. All state changes, whether in counting or

parallel loading, are initiated by the rising edge of the clock.

TYPE

TYPICAL f

MAX

74F269 115MHz 95mA

input to control the

TYPICAL

SUPPLY CURRENT

(TOTAL)

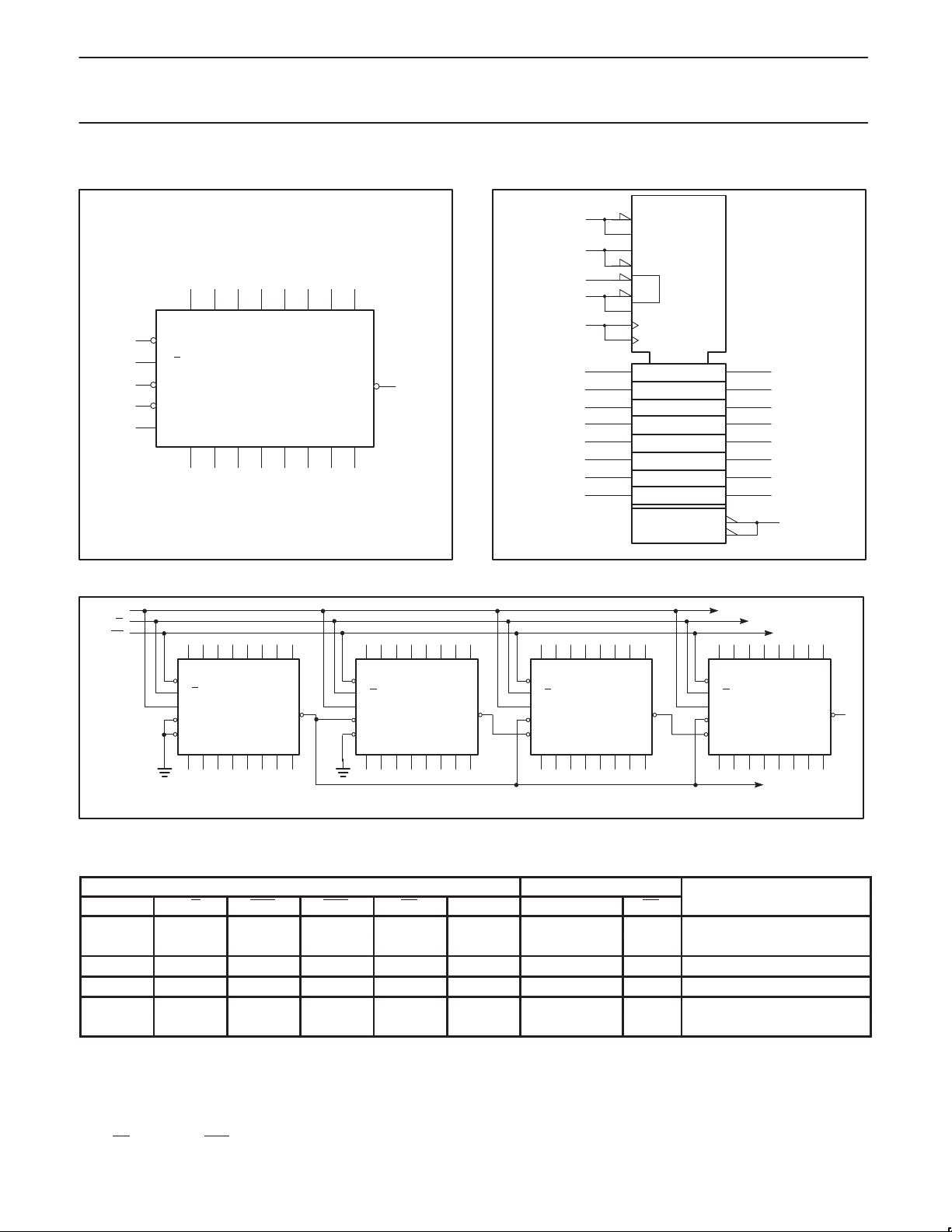

PIN CONFIGURATION

1U/D

2

Q0

3

Q1

4

Q2

5

Q3

6

Q4

7

GND

8

Q5

9

Q6

10

Q7

11

CP

CEP CET

24

PE

23

P0

22

P1

21

P2

20

P3

19

V

18

P4

17

P5

16

P6

15

P7

TC

14

1312

SF00834

ORDERING INFORMA TION

DESCRIPTION

24-Pin Plastic Slim DIP (300mil) N74F269N SOT222-1

24-Pin Plastic SOL N74F269D SOT137-1

24-Pin Plastic SSOP type II N74F269DB SOT340-1

COMMERCIAL RANGE

VCC = 5V ±10%, T

= 0°C to +70°C

amb

CC

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

P0 - P7 Parallel Data inputs 1.0/1.0 20µA/0.6mA

PE Parallel Enable input (active Low) 1.0/1.0 20µA/0.6mA

U/D Up/Down count control input 1.0/1.0 20µA/0.6mA

CEP Count Enable Parallel input (active Low) 1.0/1.0 20µA/0.6mA

CET Count Enable Trickle input (active Low) 1.0/1.0 20µA/0.6mA

CP Clock input 1.0/1.0 20µA/0.6mA

TC Terminal Count output (active Low) 50/33 1.0mA/20mA

Q0 - Q7 Flip-flop outputs 50/33 1.0mA/20mA

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

LOAD VALUE

HIGH/LOW

1996 Jan 05 853–0056 16186

2

Philips Semiconductors Product specification

OPERATING MODE

Parallel load

Hold (do nothing)

74F2698–bit bidirectional binary counter

LOGIC SYMBOL

23 22 21 20 18 17 16 15

P0 P1 P2 P3 P4 P5 P6 P7

24

PE

1

U/D

12

CEP

13

CET

11

CP

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

=Pin 19

V

CC

GND=Pin 7

APPLICATION

CP

U/D

PE

TC

234568910

SF00835

LOGIC SYMBOL (IEEE/IEC)

24

1

12

13

11

23

14

22

21

20

18

17

16

15

CTR DIV 256

M1[LOAD]

M2[COUNT]

M3[UP]

M4[DOWN]

&

G5

EN6

2, 3, 5, 6 +/C7

2, 4, 5, 6–

[1]

1, 7D

[2]

[4]

[8]

[16]

[32]

[64]

[128]

3, 5, 6 CT=256

4, 5, 8 CT=0

2

3

4

5

6

8

9

10

14

SF00836

P0 P1 P2 P3 P4 P5 P6

PE

U/D

CP

CEP

CET

Q0Q1 Q2 Q3 Q4 Q5 Q6 Q7

P7

TC

P0 P1 P2 P3 P4 P5 P6 P7

PE

U/D

CP

CEP

CET

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

TC

P0 P1 P2 P3 P4 P5 P6 P7

PE

U/D

CP

CEP

CET

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

TC

Figure 1. Synchronous Multistage Counting Scheme

MODE SELECT FUNCTION TABLE

INPUTS OUTPUTS

CP U/D CEP CET PE P

↑

↑

↑

↑

↑

↑

X X X l l L (a)

X X X l h H (a)

h l l h X Count Up (a) Count Up

l l l h X Count Down (a) Count Down

X h l h X q

X X h h X q

n

H = High voltage level

h = High voltage level one setup prior to the Low-to-High clock transition

L = Low voltage level

l = Low voltage level one setup time prior to the Low-to-High clock transition

q = Lower case letters indicate the state of the referenced output prior to the Low-to-High clock transition

X = Don’t care

↑ = Low-to-High clock transition

(a)= TC

is Low when CET is Low and the counter is at Terminal Count. Terminal Count Up is with all Qn outputs High and Terminal Count

Down is with all Qn outputs Low.

Q

n

n

n

TC

(a)

H

P0 P1 P2 P3 P4 P5 P6 P7

PE

U/D

CP

CEP

CET

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

Most significant 8-bit counterLeast significant 8-bit counter

TC

SF00851

1996 Jan 05

3

Philips Semiconductors Product specification

74F2698–bit bidirectional binary counter

LOGIC DIAGRAM

2

23

P0

P1

P2

P3

P4

DETAIL A

22

DETAIL A

21

DETAIL A

20

DETAIL A

18

DETAIL A

Q0

3

Q1

4

Q2

5

Q3

6

Q4

8

17

P5

P6

P7

PE

CP

U/D

CEP

CET

Pn

DETAIL A

16

DETAIL A

15

DETAIL A

24

11

1

12

13

TOGGLE

DETAIL A

Q

D

QCP

Q5

9

Q6

10

Q7

14

TC

V

=Pin 19

CC

GND=Pin 7

1996 Jan 05

PE CP

SF00837

4

Philips Semiconductors Product specification

SYMBOL

PARAMETER

UNIT

NO TAG

VOHHigh-level output voltage

V

VOLLow-level output voltage

V

ICCSupply current (total)

CC

74F2698–bit bidirectional binary counter

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limits set forth in this table may impair the useful life of the device.

Unless otherwise noted these limits are over the operating free-air temperature range.)

SYMBOL

V

V

I

IN

V

I

OUT

T

T

CC

IN

OUT

amb

stg

Supply voltage –0.5 to +7.0 V

Input voltage –0.5 to +7.0 V

Input current –30 to +5 mA

Voltage applied to output in High output state –0.5 to V

Current applied to output in Low output state 40 mA

Operating free-air temperature range 0 to +70 °C

Storage temperature –65 to +150 °C

RECOMMENDED OPERATING CONDITIONS

V

V

V

I

I

I

T

CC

IH

IL

IK

OH

OL

amb

Supply voltage 4.5 5.0 5.5 V

High-level input voltage 2.0 V

Low-level input voltage 0.8 V

Input clamp current –18 mA

High-level output current –1 mA

Low-level output current 20 mA

Operating free-air temperature range 0 70 °C

PARAMETER RATING UNIT

CC

V

LIMITS

MIN NOM MAX

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL PARAMETER TEST CONDITIONS

V

IK

I

I

I

IH

I

IL

I

OS

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at V

3. Not more than one output should be shorted at a time. For testing I

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a High output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, I

1996 Jan 05

LIMITS

UNIT

p

p

VCC = MIN, VIL = MAX ±10%V

VIH = MIN, IOH = MAX ±5%V

VCC = MIN, VIL = MAX ±10%V

VIH = MIN, IOL = MAX ±5%V

Input clamp voltage VCC = MIN, II = I

MIN

CC

CC

CC

CC

IK

2.5

2.7 3.4

TYP

NO TAG

MAX

0.30 0.50

0.30 0.50

–0.73 –1.2 V

Input current at maximum input voltage VCC = MAX, VI = 7.0V 100 µA

High-level input current VCC = MAX, VI = 2.7V 20 µA

Low-level input current VCC = MAX, VI = 0.5V –0.6 mA

Short-circuit output current

pp

= 5V, T

CC

NO TAG

= 25°C.

amb

tests should be performed last.

OS

VCC = MAX –60 –150 mA

I

CCH

VCC =

MAX

I

CCL

PE=CET=CEP=U/D=GND,

Pn=4.5V, CP=↑

PE=CET=CEP=U/D=GND,

Pn=GND, CP=↑

, the use of high-speed test apparatus and/or sample-and-hold

OS

93 120 mA

98 125 mA

5

Loading...

Loading...