Philips N74F02N, N74F02D Datasheet

INTEGRATED CIRCUITS

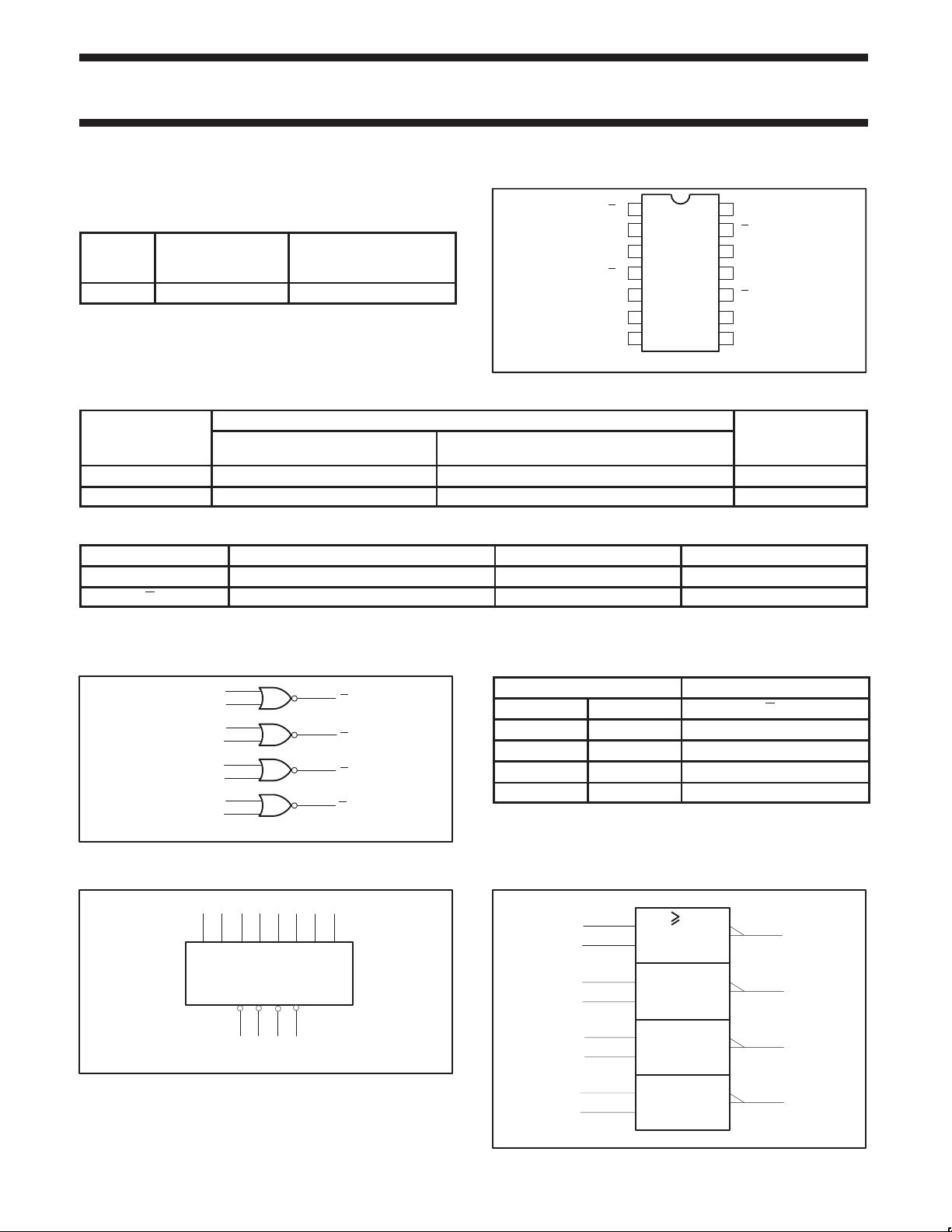

74F02

Quad 2-input NOR gate

Product specification

IC15 Data Handbook

1990 Oct 04

Philips Semiconductors Product specification

74F02Quad 2-input NOR gate

FEA TURE

•Industrial temperature range available (–40°C to +85°C)

TYPE

74F02 3.4ns 4.4mA

TYPICAL

PROPAGATION

DELAY

TYPICAL SUPPL Y

CURRENT

(TOTAL)

PIN CONFIGURATION

1

0

Q

2

D0a

3

D0b

4

1

Q

D1a

5

D1b

6

GND

14

V

Q

13

12

D3b

D3a

11

Q2

10

9

D2a

87

D2b

SF00007

CC

3

ORDERING INFORMA TION

ORDER CODE

DESCRIPTION

COMMERCIAL RANGE

VCC = 5V ±10%, T

= 0°C to +70°C

amb

VCC = 5V ±10%, T

INDUSTRIAL RANGE

= –40°C to +85°C

amb

PKG DWG #

14-pin plastic DIP N74F02N I74F02N SOT27-1

14-pin plastic SO N74F02D I74F02D SOT108-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION 74F (U.L.) HIGH/LOW LOAD VALUE HIGH/LOW

Dna, Dnb Data inputs 1.0/1.0 20µA/0.6mA

Qn Data output 50/33 1.0mA/20mA

NOTE:

One (1.0) FAST unit load is defined as: 20µA in the high state and 0.6mA in the low state.

LOGIC DIAGRAM

VCC = Pin 14

GND = Pin 7

LOGIC SYMBOL

VCC = Pin 14

GND = Pin 7

2

D0a

3

D0b

5

D1a

6

D1b

8

D2a

9

D2b

11

D3a

12

D3b

2356891112

D0a D0bD1a D2a D2b D3a D3bD1b

Q0 Q1 Q2 Q3

1 4 10 13

1

4

10

13

SF00008

SF00009

FUNCTION TABLE

Q

0

Q1

INPUTS OUTPUT

Dna Dnb Qn

L L H

L H L

Q2

Q

3

H L L

H H L

NOTES:

1 H = High voltage level

2 L = Low voltage level

IEC/IEEE SYMBOL

2

3

5

6

8

9

11

12

1

1

4

10

13

SF00010

1990 Oct 04 853-0326 00622

2

Philips Semiconductors Product specification

74F02Quad 2-input NOR gate

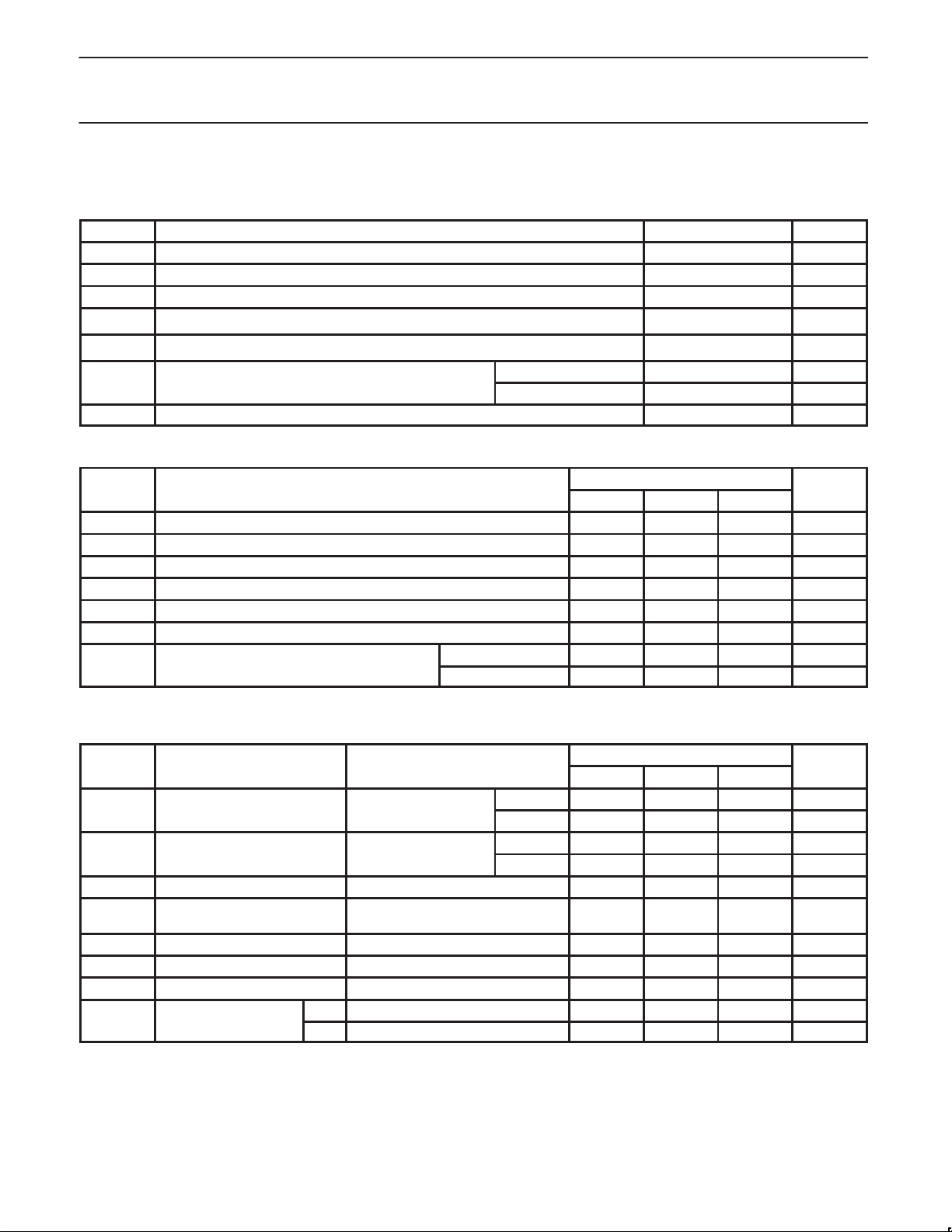

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limit set forth in this table may impair the useful life of the device.

Unless otherwise noted these limits are over the operating free air temperature range.)

SYMBOL

V

V

I

IN

V

I

OUT

T

T

CC

IN

OUT

amb

stg

Supply voltage –0.5 to +7.0 V

Input voltage –0.5 to +7.0 V

Input current –30 to +5 mA

Voltage applied to output in high output state –0.5 to V

Current applied to output in low output state 40 mA

Operating free air temperature range Commercial range 0 to +70 °C

Storage temperature range –65 to +150 °C

RECOMMENDED OPERATING CONDITIONS

SYMBOL PARAMETER LIMITS UNIT

V

V

V

I

I

I

T

CC

IH

IL

Ik

OH

OL

amb

Supply voltage 4.5 5.0 5.5 V

High-level input voltage 2.0 V

Low-level input voltage 0.8 V

Input clamp current –18 mA

High-level output current –1 mA

Low-level output current 20 mA

Operating free air temperature range Commercial range 0 +70 °C

PARAMETER RATING UNIT

CC

V

Industrial range –40 to +85 °C

MIN NOM MAX

Industrial range –40 +85 °C

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

V

OH

High-level output voltage VCC = MIN, VIL = MAX ±10%V

PARAMETER TEST CONDITIONS

VIH = MIN, IOH = MAX ±5%V

V

OL

V

IK

I

I

I

IH

I

IL

I

OS

I

CC

Low-level output voltage VCC = MIN, VIL = MAX ±10%V

VIH = MIN, I

Input clamp voltage VCC = MIN, II = I

Input current at maximum input

VCC = MAX, VI = 7.0V 100 µA

= MAX ±5%V

Ol

IK

voltage

High-level input current VCC = MAX, VI = 2.7V 20 µA

Low-level input current VCC = MAX, VI = 0.5V -0.6 mA

4

3

VCC = MAX -60 -150 mA

I

CCHVCC

I

CCLVCC

= MAX 3.0 5.6 mA

= MAX 7.0 13.0 mA

Short-circuit output current

Supply current (total)

NOTES:

1 For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2 All typical values are at V

3 Not more than one output should be shorted at a time. For testing I

= 5V, T

CC

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

amb

= 25°C.

OS

of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, I

is measured with outputs open.

4I

CC

tests should be performed last.

OS

1

MIN TYP

CC

CC

CC

CC

2.5 V

2.7 3.4 V

LIMITS UNIT

2

MAX

0.30 0.50 V

0.30 0.50 V

-0.73 -1.2 V

, the use of high-speed test apparatus and/or sample-and-hold

1990 Oct 04

3

Philips Semiconductors Product specification

TEST

CONDITION

74F02Quad 2-input NOR gate

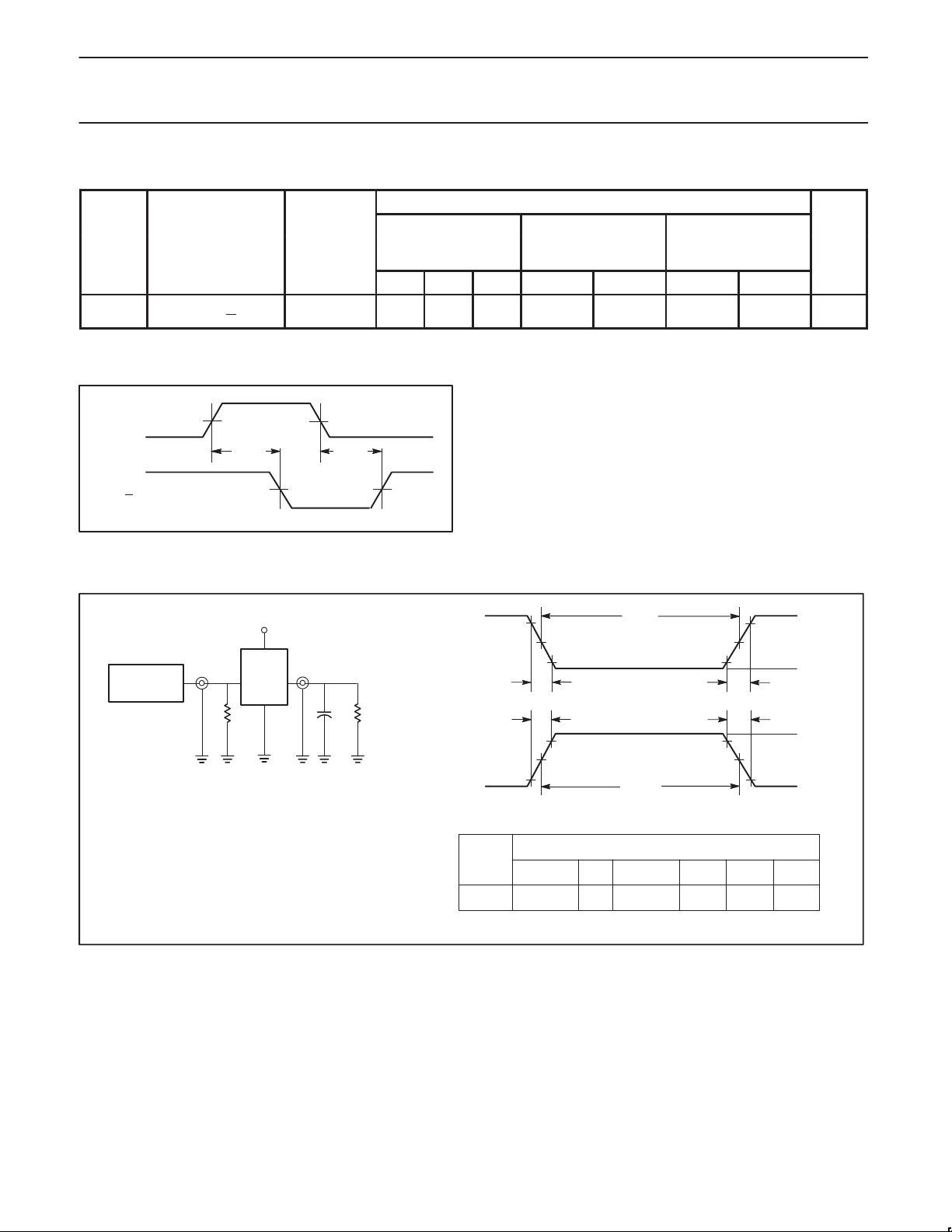

AC ELECTRICAL CHARACTERISTICS

LIMITS

VCC = +5.0V VCC = +5.0V ± 10% VCC = +5.0V ± 10%

SYMBOL PARAMETER

t

PLH

t

PHL

Propagation delay

Dna, Dnb to Qn

AC WAVEFORMS

For all waveforms, VM = 1.5V.

Waveform 1

T

= +25°C T

amb

= 0°C to +70°C T

amb

= –40°C to +85°C UNIT

amb

CL = 50pF, RL = 500Ω CL = 50pF, RL = 500Ω CL = 50pF, RL = 500Ω

MIN TYP MAX MIN MAX MIN MAX

2.5

2.0

4.4

3.2

5.5

4.3

2.5

2.0

6.5

5.3

2.5

1.5

7.0

6.0

ns

Dna, Dnb

Qn

V

M

t

PHL

V

M

t

PLH

V

M

V

Waveform 1. Propagation delay for inverting outputs

TEST CIRCUIT AND WAVEFORM

V

CC

V

PULSE

GENERATOR

IN

R

T

Test Circuit for Totem-Pole Outputs

DEFINITIONS:

R

= Load resistor;

L

see AC ELECTRICAL CHARACTERISTICS for value.

= Load capacitance includes jig and probe capacitance;

C

L

see AC ELECTRICAL CHARACTERISTICS for value.

R

= Termination resistance should be equal to Z

T

pulse generators.

D.U.T.

V

OUT

C

L

M

SF00005

t

NEGATIVE

PULSE

R

L

POSITIVE

PULSE

90%

10%

V

M

10%

t

THL (tf

t

TLH (tr

90%

V

M

w

V

M

10%

)

)

t

w

t

TLH (tr

t

THL (tf

)

)

90%

V

M

90%

10%

AMP (V)

0V

AMP (V)

0V

Input Pulse Definition

INPUT PULSE REQUIREMENTS

V

amplitude

3.0V

M

1.5V

rep. rate

1MHz 500ns

t

w

t

TLHtTHL

2.5ns 2.5ns

OUT

of

family

74F

1990 Oct 04

SF00006

4

Loading...

Loading...