Philips N74ALS138D, N74ALS138N Datasheet

74ALS138

1-of-8 decoder/demultiplexer

Product specification 1996 Jul 03

INTEGRATED CIRCUITS

IC05 Data Handbook

Philips Semiconductors Product specification

74ALS1381-of-8 decoder/demultiplexer

2

1996 Jul 03 853–1848 17016

FEA TURES

•Demultiplexing capability

•Multiple input enable for easy expansion

•Ideal for memory chip select decoding

DESCRIPTION

The 74ALS138 decoder accepts three binary weighted inputs (A0,

A1, A2) and when enabled, provides eight mutually exclusive,

active-Low outputs (Q

0 – Q7). The device features three Enable

inputs; two active-Low (E

0, E1) and one active-High (E2). Every

output will be High unless E

0 and E1 are Low and E2 is High. This

multiple enable function allows easy parallel expansion of the device

to 1-of-32 (5 lines to 32 lines) decoder with just four 74ALS138s and

one inverter. The device can be used as an eight output

demultiplexer by using one of the active-Low Enable inputs as the

data input and the remaining Enable inputs as strobes. Enable

inputs not used must be permanently tied to their appropriate

active-High or active-Low state.

TYPE

TYPICAL

PROPAGATION DELAY

TYPICAL

SUPPLY CURRENT

(TOTAL)

74ALS138 12.0ns 4.0mA

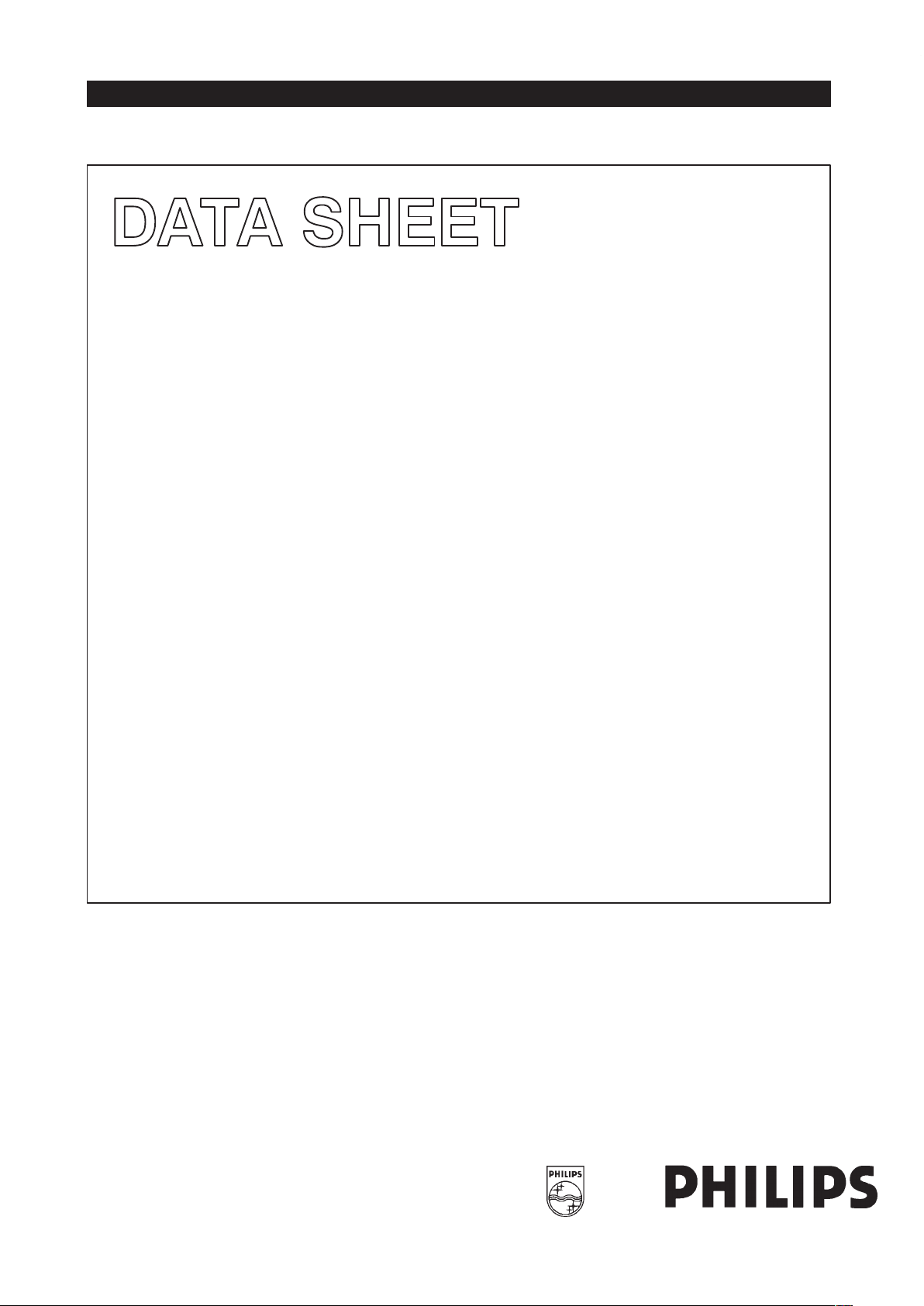

PIN CONFIGURATION

16

15

14

13

12

11

107

6

5

4

3

2

1

Q

7

V

CC

Q3

Q4

Q5

Q

2

Q

0

Q

1

A0

A1

E2

A2

E

0

E

1

98GND Q6

SF00174

ORDERING INFORMA TION

ORDER CODE

DESCRIPTION COMMERCIAL RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

DRAWING

NUMBER

16-pin plastic DIP 74ALS138N SOT38-4

16-pin plastic SO 74ALS138D SOT109-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74ALS (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

A0 – A2 Address inputs 1.0/1.0 20µA/0.1mA

E0, E1 Enable inputs (active-Low) 1.0/1.0 20µA/0.1mA

E2 Enable input (active-High) 1.0/1.0 20µA/0.1mA

Q0 – Q7 Data outputs (active-Low) 50/33 1.0mA/20mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

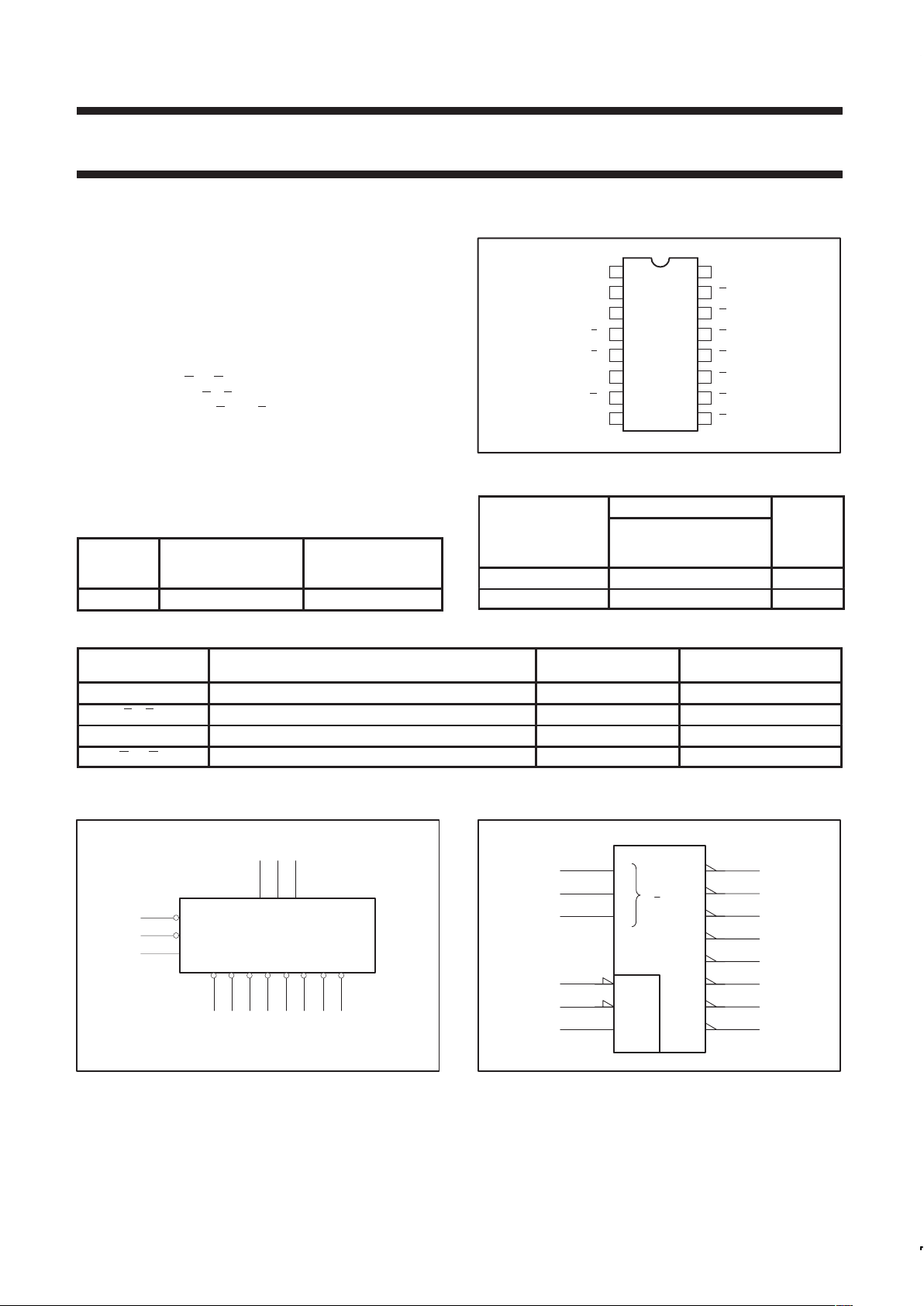

LOGIC SYMBOL

A1 A2A0

Q2 Q3 Q4 Q5

13 12 11 10

123

VCC = Pin 16

GND = Pin 8

SF00175

Q114Q0

15

Q69Q7

7

4

5

6

E0

E1

E2

IEC/IEEE SYMBOL

SC00047

DX

1

2

4

5

6

15

14

13

12

11

10

9

7

0

0

1

2

G

0

7

3

3

2

&

Philips Semiconductors Product specification

74ALS1381-of-8 decoder/demultiplexer

1996 Jul 03

3

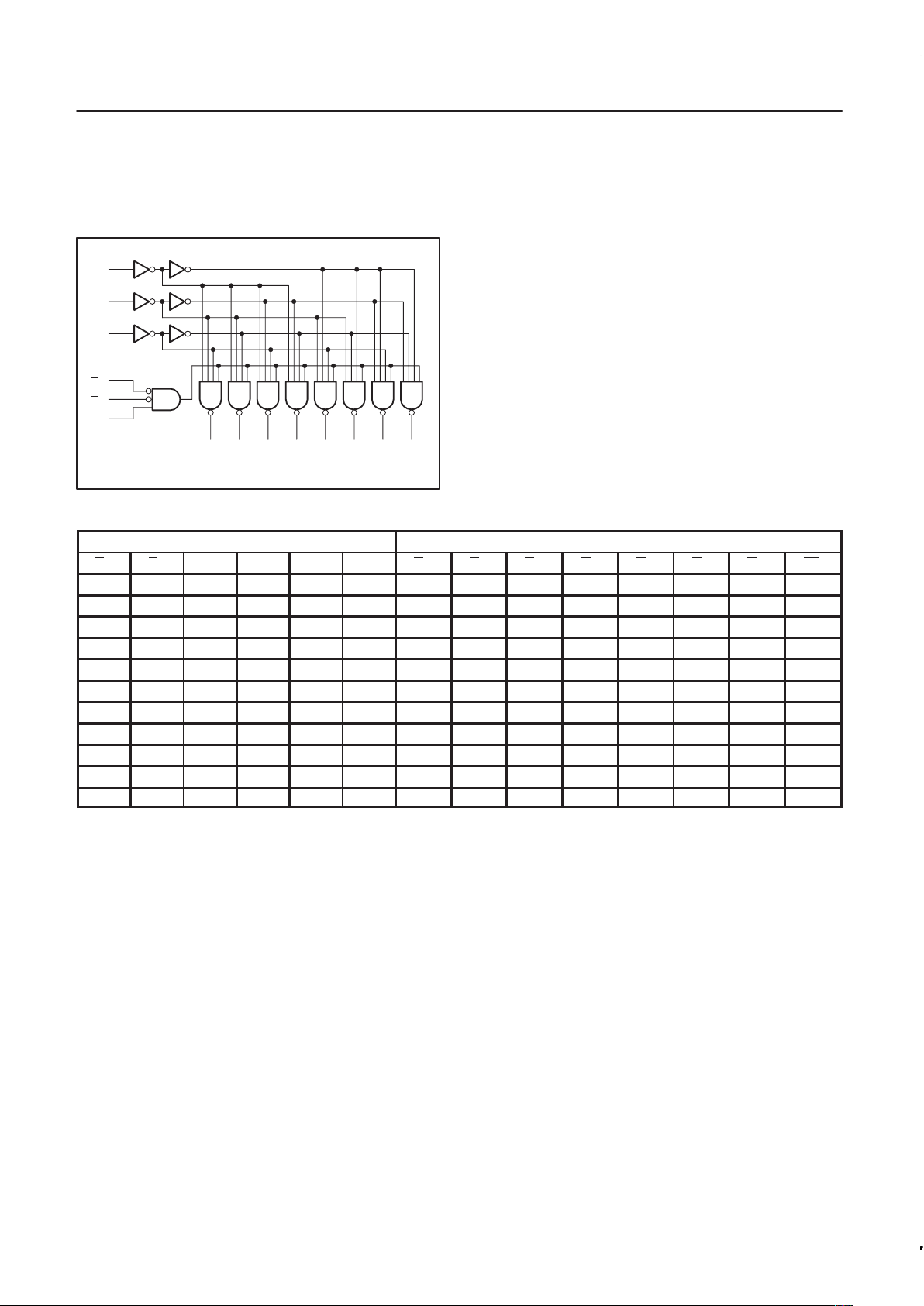

LOGIC DIAGRAM

15 14 13 12 11 10 9 7

Q

0Q1Q2Q3Q4Q5Q6Q7

3

2

1

4

5

6

A2

A1

A0

E

0

E

1

E2

V

CC

= Pin 16

GND = Pin 8

SF00177

FUNCTION TABLE

INPUTS OUTPUTS

E0 E1 E2 A0 A1 A2 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

H X X X X X H H H H H H H H

X H X X X X H H H H H H H H

X X L X X X H H H H H H H H

L L H L L L L H H H H H H H

L L H H L L H L H H H H H H

L L H L H L H H L H H H H H

L L H H H L H H H L H H H H

L L H L L H H H H H L H H H

L L H H L H H H H H H L H H

L L H L H H H H H H H H L H

L L H H H H H H H H H H H L

H = High voltage level

L = Low voltage level

X = Don’t care

Loading...

Loading...