Page 1

Colour Television Chassis

MP1.1U

AA

Contents Page

1 Specification 2

2 Precautions and Notices 13

3 Operation 14

4 Trouble shooting chart 20

5 White-Balance Adjustment 25

6 DDC program and test 26

7 Flash Update 28

8 Software Platform Reference TV Application 31

9 Block diagram & Explain 33

10 Waveform of Signal 37

11 Check and Measure 44

12 Mechanical of Cabinet 47

13 PCB Layout 62

14 Circuit Diagrams 65

15 Spare Parts List 32MF130A/37 88

16 Spare Parts List 32MF230A/37 88

17 Revision List 89

©

Copyright 2005 Philips Consumer Electronics B.V. Eindhoven, The Netherlands.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

Published by JH 567 TV Service Printed in the Netherlands Subject to modification EN 3122 785 15691

Page 2

1、 SPECIFICATION 42MF130A/37

1-1 General Specification

NOTE:

*This model complies with the specifications listed below.

*Designs and specifications are subject to change without notice.

*This model may not be compatible with features and/or specifications that may be added in the future.

Item Specification

Screen size 107cm(42 inch) plasma display panel

Panel Spec

Component

INPUT

DVI INPUT

VGA INPUT

Video INPUT

Video Output

Aspect

Display pixels 852(H) x 480 (V)

V iewing Angle 160°

Number of color 1670 million colors

Contrast Ration 3000:1 (in dark room)

Peak brightness(with filter) 400 cd/m

Y 1V(p-p), 75 ohm

Rear(2 Group)

Pr/Cr 0.7 V (p-p), 75 ohm

Pb/Cb 0.7 V (p-p), 75 ohm

AUDIO 150 mV (rms)

Rear(1 Group) DVI-D

Rear(1 Group) D-SUB 15Pin

S-Video

Side(1 Group)

Rear(1 Group)

Video

Audio

Rear(1 Group)

VIDEO

AUDIO

16:9

2

Suggested resolutions:

1080i, 480p, 480i, 720p

HDCP compliant

E-EDID compliant

Suggested scan rates:

1080i/60Hz, 1080p/60Hz, 720p/60Hz

E-EDID compliant

Suggested scan rates:

x 480/60Hz, 800 x 600/60Hz, 1024 x 768/60Hz

640

Y : 1 V(p-p), 75 ohm, negative sync.

C : 0.286 V(p-p) (burst signal), 75 ohm

1 V(p-p), 75 ohm, negative sync.

150 mV(rms)

1 V(p-p), 75 ohm, negative sync

150 mV(rms)

Channel Coverage:

VHF: 2 through 13

Television

System

NTSC standard

ATSC standard (8VSB)

UHF: 14 through 69

Cable TV: Mid band (A-8 through A-1, A through I)

Super band (J through W)

Hyper band (AA through ZZ, AAA, BBB)

Ultra band (65 through 94, 100 through 125)

Audio Power

Internal Speaker 5 W + 5 W

Power input sources 100 -240V, 50/60 Hz

Power

Dimension

Power consumption

Width x Height x Depth

350 W (on average) / 1W in standby mode

(power cord plugged in and power OFF)

Without Stand: 1038 x 660 x 82 (mm)

Include Stand: 1038 x 726.5 x 270 (mm)

Without Stand 35.5 kg

Net weight

With Stand 43 kg

Accessory

Choose Part

1pcs power cord, 1pcs remote control, (with two *AAA*sized alkaline batteries)

Wall Mounting Bracket

NOTE: This TV does not provide ATSC TV/S-VIDEO/HD/VGA/DVI Output.

2

Page 3

1、 SPECIFICATION 42MF230A/37

1-1 General Specification

NOTE:

*This model complies with the specifications listed below.

*Designs and specifications are subject to change without notice.

*This model may not be compatible with features and/or specifications that may be added in the future.

Item Specification

Screen size 107cm(42 inch) plasma display panel

Panel Spec

Component

INPUT

DVI INPUT

VGA INPUT

Video INPUT

Video Output

Aspect

Display pixels 1024(H) x 768 (V)

V iewing Angle 160°

Number of color 1670 million colors

Contrast Ration 3000:1 (in dark room)

Max. brightness 1000 cd/m

Y 1V(p-p), 75 ohm

Rear(2 Group)

Pr/Cr 0.7 V (p-p), 75 ohm

Pb/Cb 0.7 V (p-p), 75 ohm

AUDIO 150 mV (rms)

Rear(1 Group) DVI-D

Rear(1 Group) D-SUB 15Pin

S-Video

Side(1 Group)

Rear(1 Group)

Video

Audio

Rear(1 Group)

VIDEO

AUDIO

16:9

2

Suggested resolutions:

1080i, 480p, 480i, 720p

HDCP compliant

E-EDID compliant

Suggested scan rates:

1080i/60Hz, 480p/60Hz, 720p/60Hz

E-EDID compliant

Suggested scan rates:

x 480/60Hz, 800 x 600/60Hz, 1024 x 768/60Hz

640

Y : 1 V(p-p), 75 ohm, negative sync.

C : 0.286 V(p-p) (burst signal), 75 ohm

1 V(p-p), 75 ohm, negative sync.

150 mV(rms)

1 V(p-p), 75 ohm, negative sync

150 mV(rms)

Channel Coverage:

VHF: 2 through 13

Television

System

NTSC standard

ATSC standard (8VSB)

UHF: 14 through 69

Cable TV: Mid band (A-8 through A-1, A through I)

Super band (J through W)

Hyper band (AA through ZZ, AAA, BBB)

Ultra band (65 through 94, 100 through 125)

Audio Power

Internal Speaker 5 W + 5 W

Power input sources 100 -240V, 50/60 Hz

Power

Dimension

Power consumption

Width x Height x Depth

450 W (on average) / 1W in standby mode

(power cord plugged in and power OFF)

Without Stand: 1038 x 660 x 82 (mm)

Include Stand: 1038 x 726.5 x 270 (mm)

Without Stand 35.5 kg

Net weight

With Stand 43 kg

Accessory

Choose Part

1pcs power cord, 1pcs remote control, (with two *AAA*sized alkaline batteries)

Wall Mounting Bracket

NOTE: This TV does not provide ATSC TV/S-VIDEO/HD/VGA/DVI Output.

3

Page 4

1-2 Feature Summary 42MF130A/37

The following is the specification summary for the display:

107 cm (42”) 16:9 PLASMA DISPLAY PANEL

Resolutions: 852 (H) X 480 (V) pixels, (1 pixel = 1 R, G, B cells)

1.095 mm (H) X 1.110mm(V) pixel pitch.

Viewing Angle: 160° Vertically and Horizontally

Typical Maximum Contrast Ratio: 3000:1

Typical Maximum Brightness (with filter): 400 cd/m

2

ATSC receiver, MPEG-2 decoder

NTSC receiver, Video decoder

Closed Caption / V-chip

Composite, S-Video, and component video receiver

DVI digital video interface

D-SUB analog video with rate 50Hz to 85 Hz vertical refresh rate and 31KHz to

80KHz horizontal frequency

MIPS controller

Field upgradeable firmware

Universal Power Supply designed for worldwide application

Operating power consumption less than 350 W

Standby power consumption less than 1 W

UL, FCC, certification

Dimension: width – 1038mm, height – 660mm, depth – 82mm, weight – 35 Kg

4

Page 5

1-2 Feature Summary 42MF230A/37

The following is the specification summary for the display:

z 107 cm (42”) 16:9 PLASMA DISPLAY PANEL

z Resolutions: 1024 (H) X 768(V) pixels, (1 pixel = 1 R, G, B cells)

z 0.912 mm (H) X 0.693mm(V) pixel pitch.

z Viewing Angle: 160° Vertically and Horizontally

z Typical Maximum Contrast Ratio: 3000:1

z Typical Maximum Brightness: 1000 cd/m2

z ATSC receiver, MPEG-2 decoder

z NTSC receiver, Video decoder

z Closed Caption / V-chip

z Composite, S-Video, and component video receiver

z DVI digital video interface

z D-SUB analog video with rate 50Hz to 85 Hz vertical refresh rate and 31KHz to

80KHz horizontal frequency

z MIPS controller

z Field upgradable firmware

z Universal Power Supply designed for worldwide application

z Operating power consumption less than 450 W

z Standby power consumption less than 1 W

z UL, FCC, certification

z Main Dimension: width 1038mm, height 640mm, depth 110mm, weight 43 Kg

5

Page 6

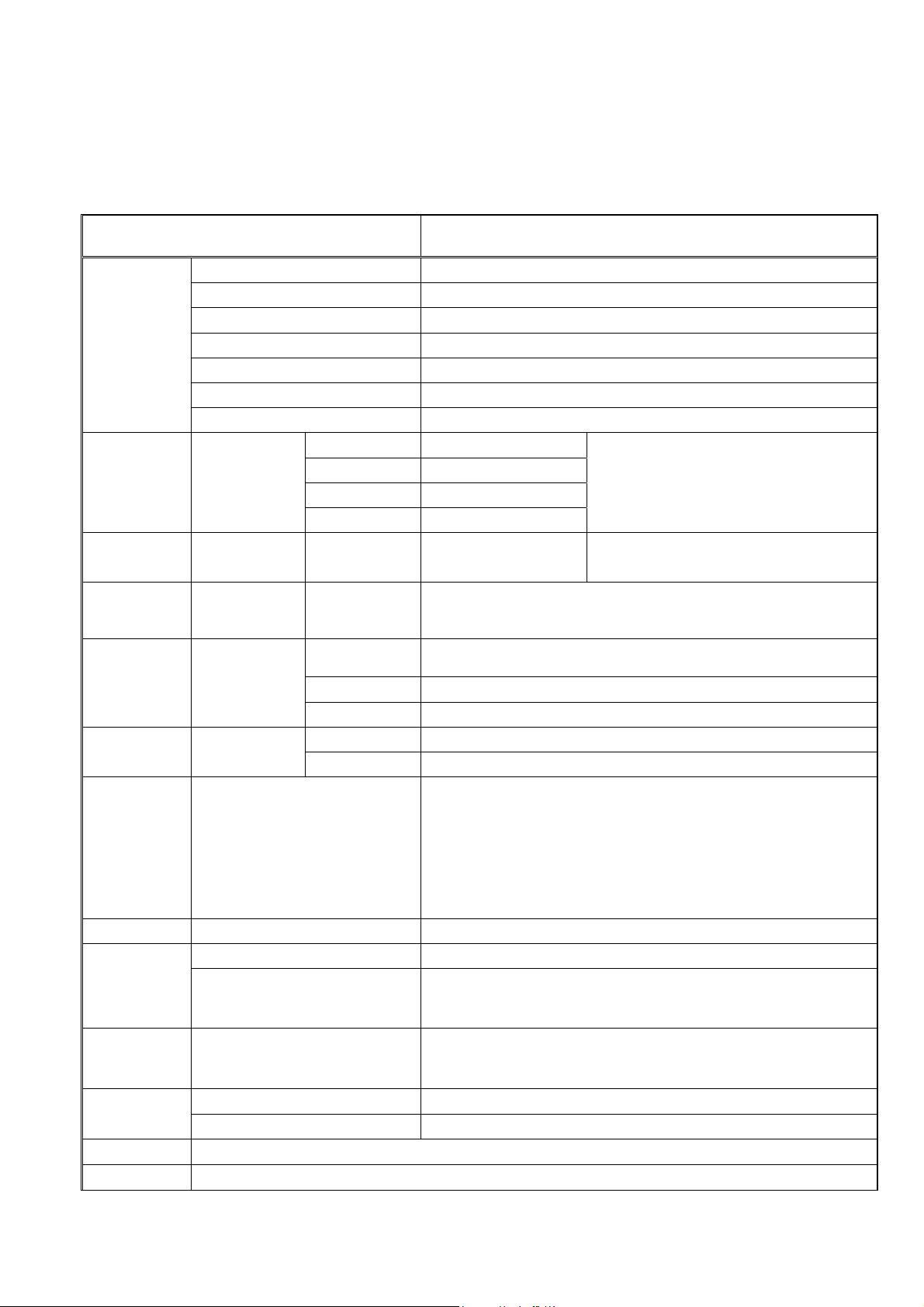

1-3 External interface

Most of these interfaces are located at the back-panel. There’s also a group of connectors located

on the side of this device for easier access. The following figures depict these A/V connectors.

Side A/V Connectors

S-Video Video L R Earphone

AV2 Input

RS-232

ANT

ATSC/NTSC

1-3-1 Video/Audio Inputs

The following sections specify the video/audio inputs for 42MFx30A/37

1-3-1-1 TV A ntenna Interface

①. TV Antenna Connector

42MFx30A/37 shall provide a F-type cable connector with 75 ohms termination on its back

panel for reception of radio frequency signals.

②. TV Systems

42MFx30A/37 shall be capable of receiving the following broadcasting systems in the North

America region.

• Analog terrestrial and cable broadcasting in NTSC system and “M” sound system.

DVI L/ R

DVI Input

Back Panel A/V Connectors

AV3 Component Input

Y Pb/Cb Pr/Cr R L

VGA L/ R

PC Input

Y Pb/Cb Pr/Cr R L

AV4 Component Input

AV Output

Video R L

S-Video Video R L

AV1 I np u t

• All 18 formats specified for ATSC digital broadcasting

• Clear QAM digital cable broadcasting

③. TV Channel Coverage

The RF tuner shall be capable of covering 55.25 to 859.25 MHz and tuning to the following

6

Page 7

channels:

• VHF: channel 2 through 13

• UHF: channel 14 through 69

• Mid band cable: A1 through A8, A through I

• Super band cable: J through W

• Hyper band cable: AA through ZZ, AAA, BBB

• Ultra band cable: channel 65 through 94, 100 through 125

④. Closed Caption

42MFx30A/37 shall support closed caption and text mode for both video and TV system.

These supports shall include channel ½ and field ½ selectable features.

⑤. V -Chip

42MFx30A/37 shall support MPAA grade for movie and TV Parental Guideline for TV. This

support shall include changeable password.

1-3-1-2 AV1

A standard definition (SD) analog video/audio source designated as AV1 shall be located on its

back panel. It comprises the following electrical connections. Only one of the two video inputs

shall be connected.

①. S-Video Input

42MFx30A/37 shall provide a 4-pin mini-DIN connector for connection to an external

S-Video source.

②. CVBS Video Input

42MFx30A/37 shall provide a RCA type receptacle for connection to an external CVBS

source.

③. Audio Inputs

42MFx30A/37 shall provide two RCA type receptacles for the stereo audio signal associated

with AV1 input.

1-3-1-3 AV2

A standard definition analog video/audio source designated as AV2 shall be located at the side

of 42MFx30A/37. It comprises the following electrical connections. Only one of the two video

inputs shall be connected.

①. S-Video Input

42MFx30A/37 shall provide a 4-pin mini-DIN connector for connection to an external

S-Video source.

②. CVBS Video Input

42MFx30A/37 shall provide a RCA type receptacle for connection to an external CVBS

source.

③. Audio Inputs

42MFx30A/37 shall provide two RCA type receptacles for the stereo audio signal associated

with AV2 input.

1-3-1-4 AV3

A YPbPr/YcbCr type component video interface designated as AV3 shall be located on its back

panel. It comprises the following electrical connections.

①. Video Inputs

42MFx30A/37 shall provide three RCA type receptacles for connection to an external

component video source.

②. Audio Inputs

42MFx30A/37 shall provide two RCA type receptacles for the stereo audio signal associated

7

Page 8

with Component1 input.

1-3-1-5 AV4

A YPbPr/YcbCr type component video interface designated as AV4 shall be located on its back

panel. It comprises the following electrical connections.

①. Video Inputs

42MFx30A/37 shall provide three RCA type receptacles for connection to an external

component video source.

②. Audio Inputs

42MFx30A/37 shall provide two RCA type receptacles for the stereo audio signal associated

with Component2 input.

1-3-1-6 PC Input

42MFx30A/37 accommodates a VGA type computer connection as specified below.

①. Video Input connector

42MF130A/37 shall provide a 15-pin D-Sub connector on its back panel for connection to a

VGA type video source. The VGA signal input on the display shall be capable of receiving

RGB analog video, H and V syncs, and DDC. The table below specifies pin-outs of this

connector.

Analog Connector Pin-outs

PIN

1 RV Red Video

2 GV Green Video

3 BV Blue Video

4 NC None

5 GND Ground (DDC Return)

6 RG Red GND

7 GG Green GND

8 BG Blue GND

9 +5 V +5 V (from the PC)

10 SG Sync Ground

11 NC None

12 SDA DDC Data

13 HS Horizontal Sync

14 VS Vertical Sync

15 SCL DDC Clock

②. Audio Inputs

42MFx30A/37 shall provide a 3.5 mm jack for the stereo audio signal associated with VGA

input.

③. Input Formats

42MFx30A/37 shall support the following input format on its VGA input.

Mode Resolution Total

VGA 640x480@60Hz 800 x 525 31.469 N 59.940 N 25.175

SVGA 800x600@60Hz 1056 x 628 37.879 P 60.317 P 40.000

XGA 1024x768@60Hz 1344x806 48.363 N 60.004 N 65.000

MNEMONIC

SIGNAL

1

6

11 15

Horizontal Vertical

Nominal

Frequency

(KHz)

8

Sync

Polarity

Nominal

Freq.

(Hz)

Sync

Polarity

5

10

Nominal

Pixel

Clock

(MHz)

Page 9

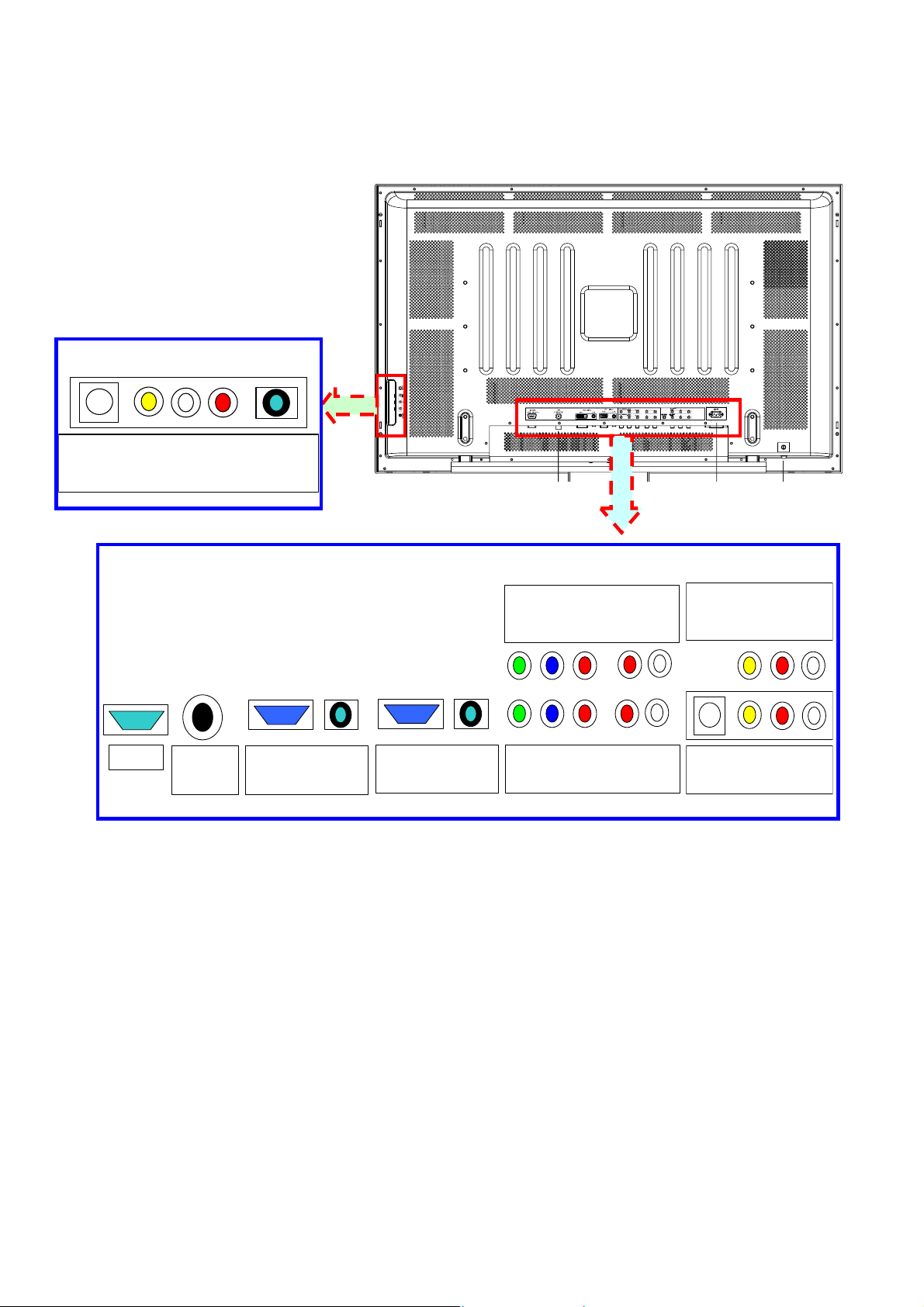

1-3-1-7 DVI

42MFx30A/37 shall accommodate a DVI type digital video source as specified in this section.

①①. Video Inputs

42MFx30A/37 shall provide a 24 contact DVI-D receptacle on its back panel for receiving

TMDS digital video. The table below specifies pin assignments for the DVI-D connector.

DVI-D Digital connector pin assignments

PIN MNEMONIC SIGNAL

1 TX 2 - TMDS Data 2 -

2 TX 2 + TMDS Data 2 +

3 SHLD 2 / 4 TMDS Data 2 / 4 Shield

4 TX 4 - TMDS Data 4 -

5 TX 4 + TMDS Data 4 +

6 DDC Clk DDC Clock

7 DDC Data DDC Data

8 N/C No Connect

9 TX 1 - TMDS Data 1 -

10 TX 1 + TMDS Data 1 +

11 SHLD 1 / 3 TMDS Data 1 / 3 Shield

12 TX 3 - TMDS Data 3 -

13 TX 3 + TMDS Data 3 +

14 +5V +5V Power (from the PC)

15 GND Ground (Return for +5V)

16 HPD Hot Plug Detect

17 TX 0 - TMDS Data 0 -

18 TX 0 + TMDS Data 0 +

19 SHLD 0 / 5 TMDS Data 0 / 5 Shield

20 TX 5 - TMDS Data 5 -

21 TX 5 + TMDS Data 5 +

22 TX CLK SHLD TMDS Clock Shield

23 TX CLK + TMDS Clock +

24 TX CLK - TMDS Clock -

②②. Audio Inputs

42MFx30A/37 shall provide a 3.5 mm jack for the stereo audio signal associated with DVI

.

input

③③. HDCP support

HDCP must be supported on the DVI input. Refer to the High-bandwidth Digital Content

Protection System specification version 1.1 for details.

9

Page 10

④④. Input Formats

42MF130A/37 shall support the following input format on its DVI input.

minal

No

minal

Mode Resolution Total

VGA 640x480@60Hz 800 x 525 31.469 59.940 25.175

SVGA 800x600@60Hz 1056 x 628 37.879 60.317 40.000

XGA 1024x768@60Hz 1344x806 48.363 60.004 65.000

720P 1280×720P 74.25 60

HFreq

(KHz)

uency

No

Vertical

equency

Fr

(KHz)

minal Pixel

No

ck Frequency

Clo

(MHz)

42MF230A/37 shall support the following input format on its DVI input.

Nominal

Mode Resolution Total

VGA 640x480@60Hz 800 x 525 31.469 59.940 25.175

SVGA 800x600@60Hz 1056 x 628 37.879 60.317 40.000

XGA 1024x768@60Hz 1344x806 48.363 60.004 65.000

720P 1280×720P 45.00 60 74.25

1080i 1920×1080i 33.75 60 74.25

480p 720×480p 31.54 60 27.00

HFrequ

ency

(KHz)

Nominal

Vertical

equency

Fr

(KHz)

Nominal Pixel

ck Frequency

Clo

(MHz)

10

Page 11

1-3-2 Audio/Video Outputs

1-3-2-1 Composite Video Output

42MFx30A/37 shall provide a RCA type receptacle on its back panel for composite video output.

1-3-2-2 Analog Audio Output

42MFx30A/37 shall provide two RCA type receptacles for external connection to a stereo

amplifier.

1-3-2-3 Head Phone

42MFx30A/37 shall provide a 3.5 mm jack at side of 42MFx30A/37 for external connection of a

stereo headphone.

1-3-3 Power Interface

1-3-3-1 Power Connector

42MFx30A/37 shall support an IEC C-13/C-14 (Standard) type male power receptacle for

connection to AC power source.

1-3-3-2 Power Input Range

The operating range shall be from 100 to 265 VAC sinusoidal for 42MF130A and 100 to 240VAC

sinusoidal for 42MF230A. Input power frequency range shall be from 50 to 60 Hz over the

specified input voltage range.

1-3-3-3 Power Consumption

①①. Operating Power

Power consumption for the display over the specified voltage and frequency ranges shall be

les

s than 350 W for the assemblies with speakers for 42MF130A and less than 450 W

for 42MF230A.

②②. Standby Power

42MFx30A/37 power also below than one watt in the standby mode.

1-3-4 Service Interface

42MFx30A/37 shall provide a 9-pin D-sub connector on its back panel for firmware upgrading

purpose. This interface shall conform to RS-232 standard with the following pin-outs.

Pin Function

1 NC

2 TXD transmitted data

3 RXD received data

4 Shorted with pin 6

5 FG frame ground

6 Shorted with pin 4

7 Shorted with pin 8

8 Shorted with pin 7

9 NC

The method of firmware upgrading please see “Flash update process” chapter.

1-4 User interface

1-4-1 Power Indicator

42MFx30A/37 shall make use of an LED type indicator located on the front of the display. The

LED color shall indicate the power states as given in the following table.

LED colors

Mode H-Sync V-Sync Video Pw-cons. Indicator

Power-On On On Active

Standby Off Off Off

350W/ Blue LED

<

450W

<

1W Red LED

<

11

Page 12

1-4-2 Remote Control Receiver

42MFx30A/37 shall provide an infra-red (IR) optical detector on its front panel for use as the

receiver for remote controller signal. The IR communication protocol shall conform to RC-5

standard. The minimum IR reception angles shall be +/- 30 degrees horizontally and vertically.

The required operating distance of the remote control shall be 7 m.

1-4-3 On-Screen Display

42MFx30A/37 shall provide an On Screen Display (OSD) system for customer setup. The

following table gives the structure of the OSD menus.

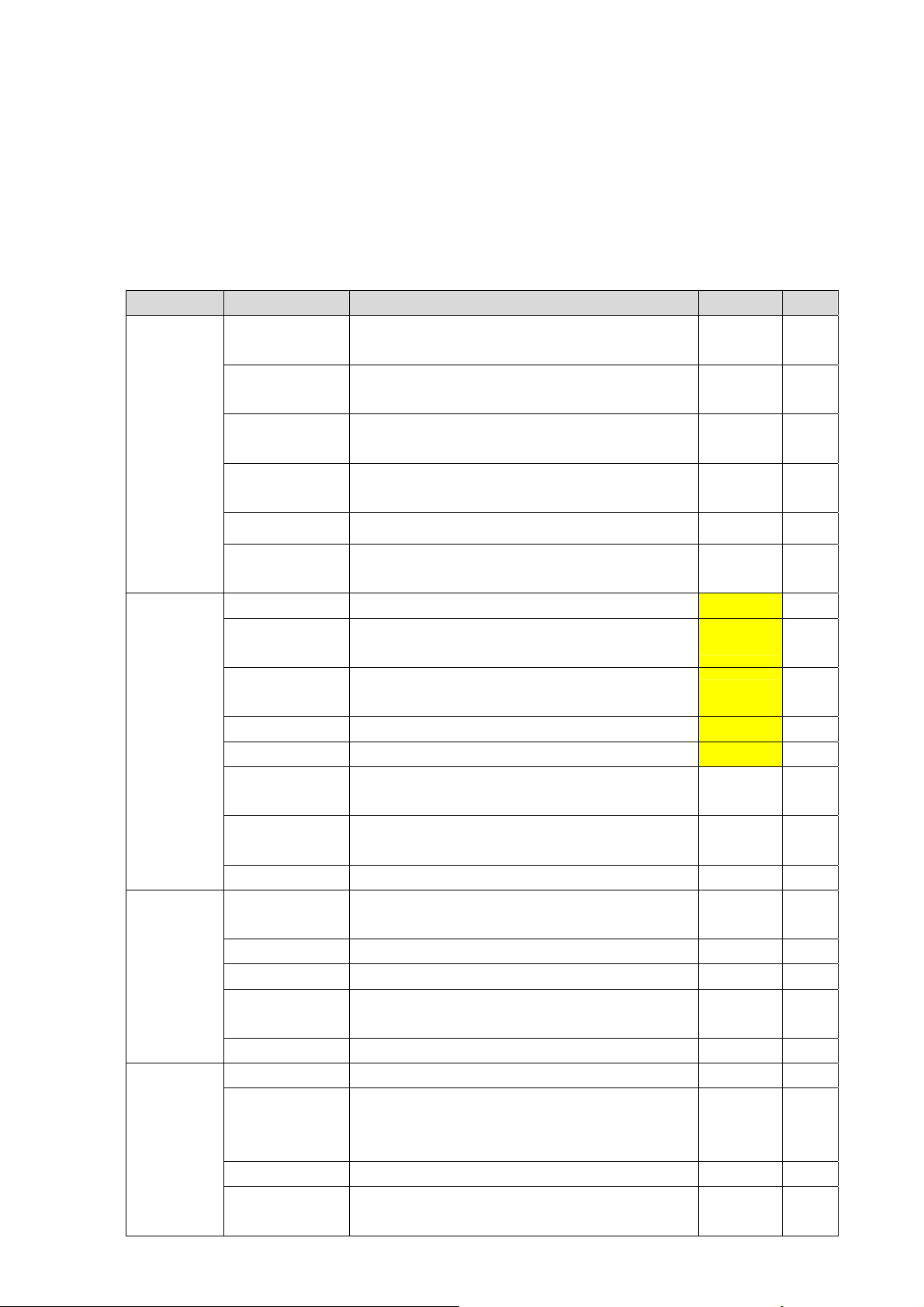

Main menu Sub menu Function Default Reset

SETUP

Tuning Band

Signal Strength

Auto

Channel Search

Manual

Channel Set

To select between Terrestrial and Cable

System

To display the signal strength in order to aid

the antenna adjustment

To scan all TV channels and store them in

memory

Air —

— —

— —

To enable or disable channels — —

VIDEO

AUDIO

FEATURE

Channel Label To rename a channel — —

Manu

Language

To select the language for OSD among

English, Spanish, and French

English —

CONTRAST To adjust the contrast value between 0 and 63 50 Yes

BRIGHTNESS

SHARPNESS

To adjust the brightness value between 0 and

63

To adjust the sharpness value between 0 and

63

50 Yes

50 Yes

COLOR To adjust the color value between 0 and 63 50 Yes

TINT To adjust the tint value between 0 and 63 50 Yes

COLOR

Temperature

Aspect Ratio

To adjust the color temperature and white

balance.

To select aspect ratio among Nor mal, Zoom,

Wide, and Cinema

Yes

Normal Yes

Settings To restore all video settings to factory default — —

Audio

Language

To select audio language among English,

Spanish, and French

English Yes

BASS Sets the bass value between 0 and 63 31 Yes

TREBLE Sets the treble value between 0 and 63 31 Yes

BALANCE

Sets the left/right balance value between 0

and 63

31 Yes

Restore Default To restore all audio settings to factory default — —

Time Set To set current time — —

To set the timer period to turn off the TV.

Sleep Timer

Selectable values are OFF, 30, 60, and 90

OFF —

minutes

Password Set To set or change Parental Control password TBD —

Parental

Control

To select V CHIP settings Un-locked —

12

Page 13

1-5 External Mounting Requirements

42MFx30A/37 shall be designed so that the display enclosure can be easily removed from the

base for external mounting applications. When the base is removed, there shall be no additional

non-removable parts that are visible from the front of the display

1-6

Environmental Requirements

1-6-1 Temperature Ranges

Operating

Temperature (Independent of altitude) 42MF130A.................... 5°C to 35°C

42MF230A.................... 0°C to 40°C

Non-Operating Temperature (Independent of altitude)

42MF130A.................... -20°C to 60°C

42MF230A.................... -10°C to 85°C

1-6-2 Humidity

Operating (non-condensing)

.......................................................

Non-Operating (38.7°C maximum wet bulb temperature

42MF130A.................... 20% to 80%

42MF230A.................... 10% to 85%

42MF130A.................... 5% to 80%

42MF230A.................... 5% to 85%

1-6-3 Altitude

Operating

Non-Operating

................................................................................

......................................................................

42MF130A......... 0 to 6,562 ft. (0 to 2,000 m)

42MF230A......... 0 to 6,562 ft. (0 to 3,000 m)

42MF130A......... 0 to 9843 ft. (0 to 3,000 m)

42MF230A......... 0 to 9843 ft. (0 to 3,000 m)

1-6-4 Vibration and Shock

All testing shall be done in each of three mutually perpendicular axes, referenced to the position

of the system as it is in front of the user (i.e., front-to-back, side-to-side, and top-to-bottom).

2、、Precautions and Notices::

2-1

Precaution of assembly

(1)Please do not press or scratch PDP panel surface with anything hard.

(2)Please wipe out PDP panel surface with absorbent cotton or soft cloth in case of it being soiled

(3)Please wipe out drops of adhesive like saliva and water in PDP panel surface immediately. They might

mage to cause panel surface variation and color change

da

(4)Do not apply any strong mechanical shock to the PDP panel

2-2

Precaution of Operation::

(1)Please be sure to unplug the power cord before remove the back-cover. (make sure the power is turn-off)

(2)Please do not change variable resistance settings in PDP MODULE; They are adjusted to the most

suitable value. If they are changed, it might happen LUMINANCE does not satisfy.

(3)Please consider that PDP MODULE takes longer time to become stable of radiation characteristic in

mperature than in room temperature.

low te

(4)Please pay attention to displaying the same pattern for very long-time. Image might stick on PDP.

13

Page 14

3、Operation

m

y

r

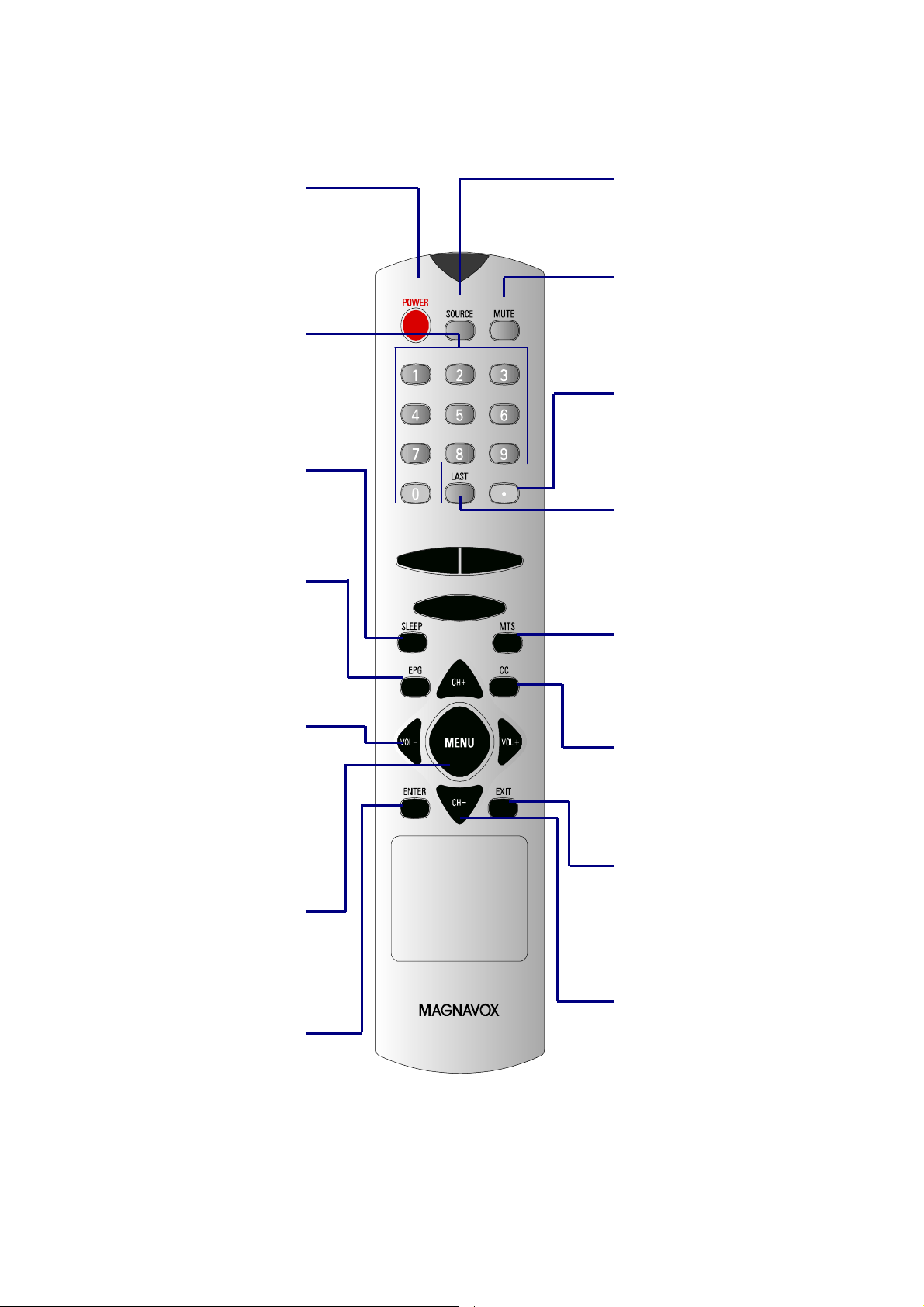

3-1 Operation of Remote Control Transmitter

42MFx30A/37 shall provide an IR remote controller as accessory.

To switch TV set between

power on and standby modes.

To enter TV channel number.

To Adjust sleep timer options.

To enter or exit Electronic

“VOL- ()/ VOL+()”

To decrease or increase the

sound volume. Also to navigate

left or right the Menu.

To enter Menu mode.

To enter sub Menu or sub

“POWER”

“0~9 number”

“SLEEP”

“EPG”

Program Guide.

“MENU”

“ENTER”

item.

14

“SOURCE”

To select input source.

“MUTE”

To mute the audio output.

“•(dot)”

To enter sub channel number.

“LAST”

To switch to the previousl

viewed channel.

“MTS”

To select audio progra

options.

“CC”

To select close caption options

(CC1, CC2 ...)

“Exit”

To exit Menu or other OSD.

“CH+ ( )/ CH – ()”

To select the next higher o

lower channel. Also to navigate

up or down the Menu.

Page 15

3-2 Front panel controls

⑦

⑥

⑤

④

③

②

①

②

- CH + - VOL +

IR: Remote Control Sensor.

Power switch: Press to power on or power off the TV set..

③ ● LED: Power Indicator.

MENU MODE

④ MODE Mode: Press to select input signal modes or use as Enter in Menu operation.

⑤ MENU Menu: Press to enter Menu or exit Menu.

⑥ -VOL+

Left: Press to decrease the sound volume level or move Left in Menu operation.

Right: Press to increase the sound volume level or move Right in Menu operation.

Down: Press to select the next lower Program number or move Down in Menu

⑦ -CH+

operation.

Up: Press to select the next higher Program number or move up in Menu

operation.

15

Page 16

3-3 OSD MENU Description

r

d

u

h

3-3-1 Main MENU

1. Press “MENU” key on remote control o

front panel controls to bring up Main Menu.

2. Press “ ” or “ ” to move the cursor up

and down the sub menu list.

3. Press “ ” or “” to select sub menu item.

4. Press "Enter" to enter sub-item then use

“ ” or “ ” to adjust.

3-3-2 SETUP MENU

1. Tuning Band: Select TV signal source

between Air and Cable. Select “Cable” if you

are connecting to a cable box and select

“Air” if you are directly connecting to the

antenna.

2.

DTV Signal: Display signal strength to aid

antenna adjustment.

3.

Auto Ch Search: Automatically scan an

store all TV channels.

Manual Ch Set: Enter channel setup table.

4.

5. Channel Labels: Display and edit channel

names.

6. Menu Language: Select language for men

(English Español).

DTV signal menu indicates signal strengt

in real-time.

Auto channel scan menu displays channel

number being scanned.

Manual Channel Set Menu

Displays

all the channel numbers that are

found.

Tune either to ATSC or NTSC channels.

Add or delete Channel number.

Channel Labels Menu allows user labeling.

16

Page 17

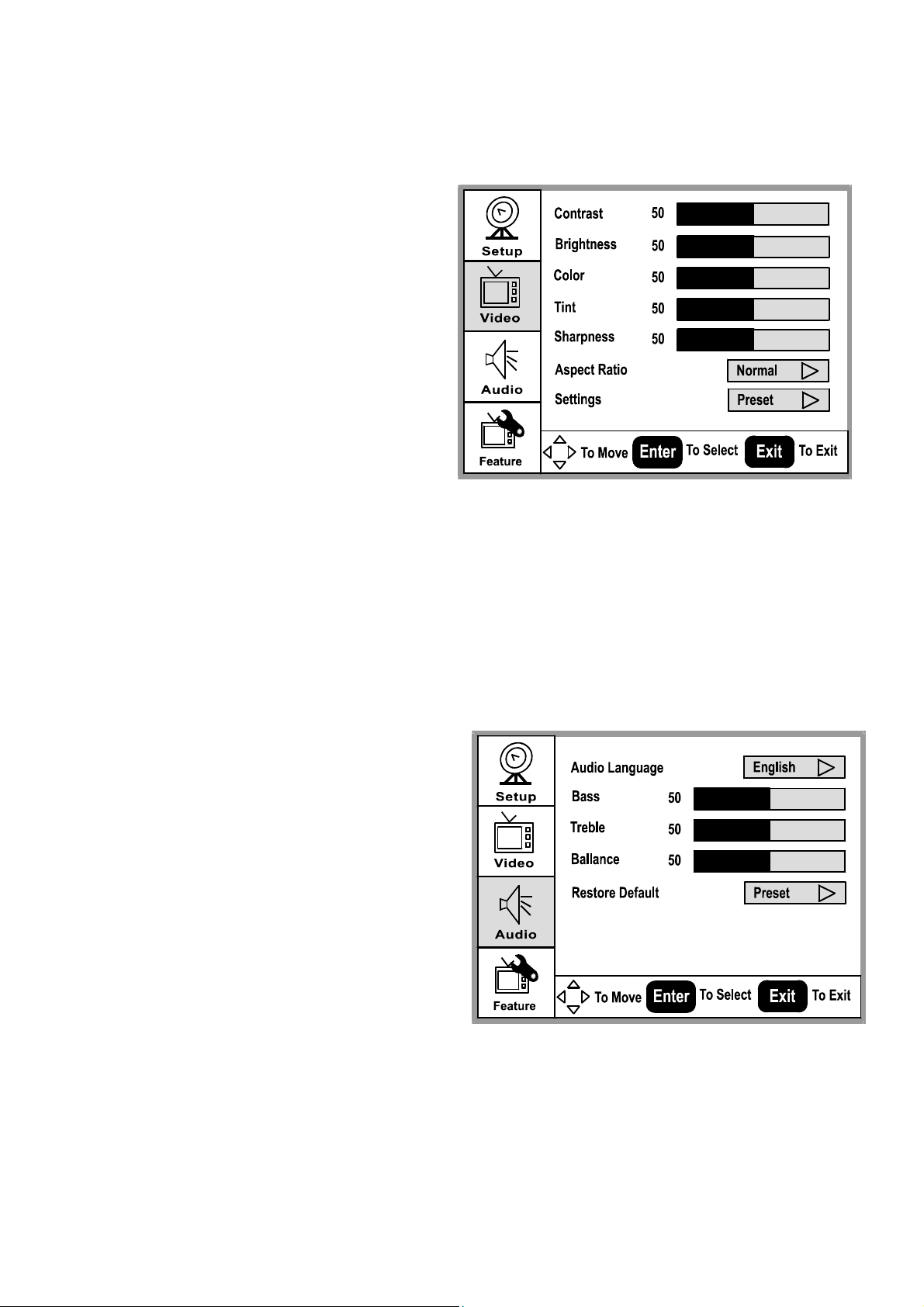

3-3-3 Video MENU

d

f

d

1. Press “” or “” to move the cursor up

or down the sub-item list.

2. Press "Enter" to enter the highlighte

sub-item menu.

3. Press “

” or “ ” to adjust the value o

the sub-item.

4. Press "Enter" again to exit the sub-item.

Contrast: Contrast adjustment, 0~100.

Brightness: Brightness adjustment, 0~100.

Color: Color chroma adjustment, 0~100.

Tint: Tint adjustment, 0~100.

Aspect Ratio: Aspect Ratio selection.

Normal

ZoomWide Cinema.

Settings: Restore default setting.

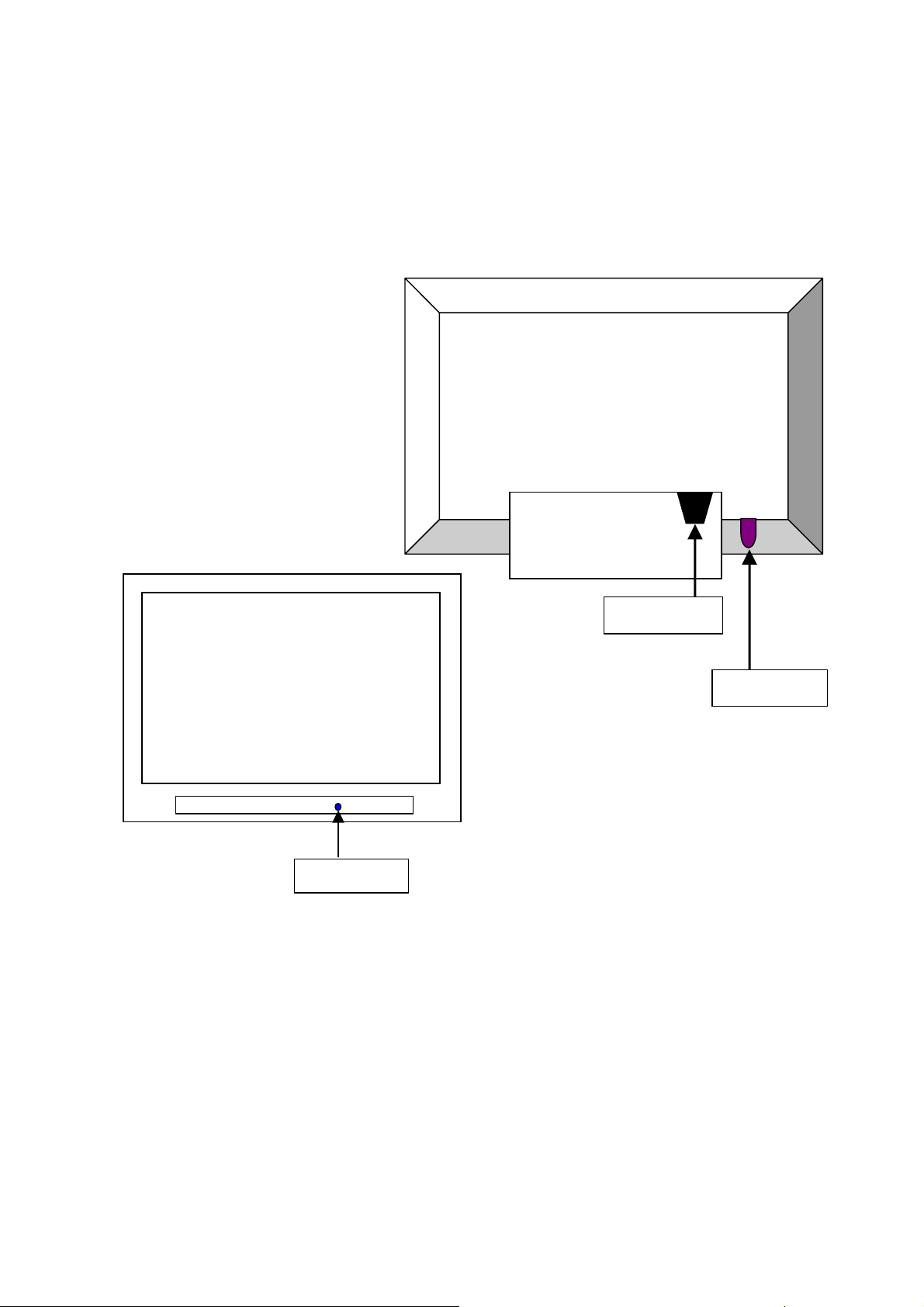

3-3-4 Audio MENU

1. Press “” or “” to move the cursor up

or down the sub-item list.

2. Press "Enter" to enter the highlighte

sub-item menu.

3. Press “

” or “” to adjust the value of

the sub-item.

4. Press "Enter" again to exit the sub-item.

Audio Language:

EnglishEspañolFrançais.

Bass: Bass adjustment, 0 ~ 100.

Treble: Treble adjustment, 0 ~ 100.

Balance: Balance adjustment, 0 ~ 100.

Restore Default: Restore Audio Language,

Treble, Base, and Balance setting to default.

17

Page 18

3-3-5 Featuree MENU

d

f

p

1. Press “” or “” to move the cursor up

or down the sub-item list.

2. Press "Enter" to enter the highlighte

sub-item menu.

3. Press “” or “” to adjust the value o

the sub-item.

4. Press "Enter" again to exit the sub-item.

Sleep Timer: Select minutes into standby

Off

30

60

90

.

Password Set: Enter and change Parental

Control Password.

Parental Control: Setup TV and Movie

rating controls.

Parental Control Menu: Controls

viewing of rated TV and Movie

rograms.

Note: Need password to change

settings. Default passwd = : 0000

3-3-6 Closed Captions

1. Press “CC” key on remote control to select closed captions mode.

NTSC TV: Off CC1 CC2 …

ATSC TV: Off CS1 CS2 …

2. Select desired closed caption mode.

NTSC TV

CC1

ATSC TV

18

CS1

Page 19

f

3-3-7 EPG

Press the “EPG” key on the remote control

to display the Electronic Program Guide

(EPG). A message window will be

displayed on screen.

3-3-8 TV channel arrangement

Each digital channel may comprise o

several sub-channels.

To select a digital channel using the remote

control:

1. Enter main channel number.

2. Press the “•” key.

3. Enter the sub-channel number.

EPG Message Window

Ch 5.4

19

Page 20

4、Trouble shooting chart

If replace “IMAGE BOARD”, Please re-do “DDC-content” program & “WHITE-BALANCE” & Flash

Update.

4-1 PANEL Trouble shooting

Please reference th e “PANEL Service Manual”.

4-2 Turn PDP on and Check:

Put the power switch after inserting the cable.

If PDP under the normal working, display of LED is blue. Then, the screen show is nor dark. If the color of

LED is red under standby state, you should press the “power” bottom of remote control or you should press

the front standby key. Then, turn PDP TV on.

If it is nothing about OSD or display on screen, service PDP.

The procedure and maintain the step meet as follows:

LED Light

20

Power Cable

Power Switch

Page 21

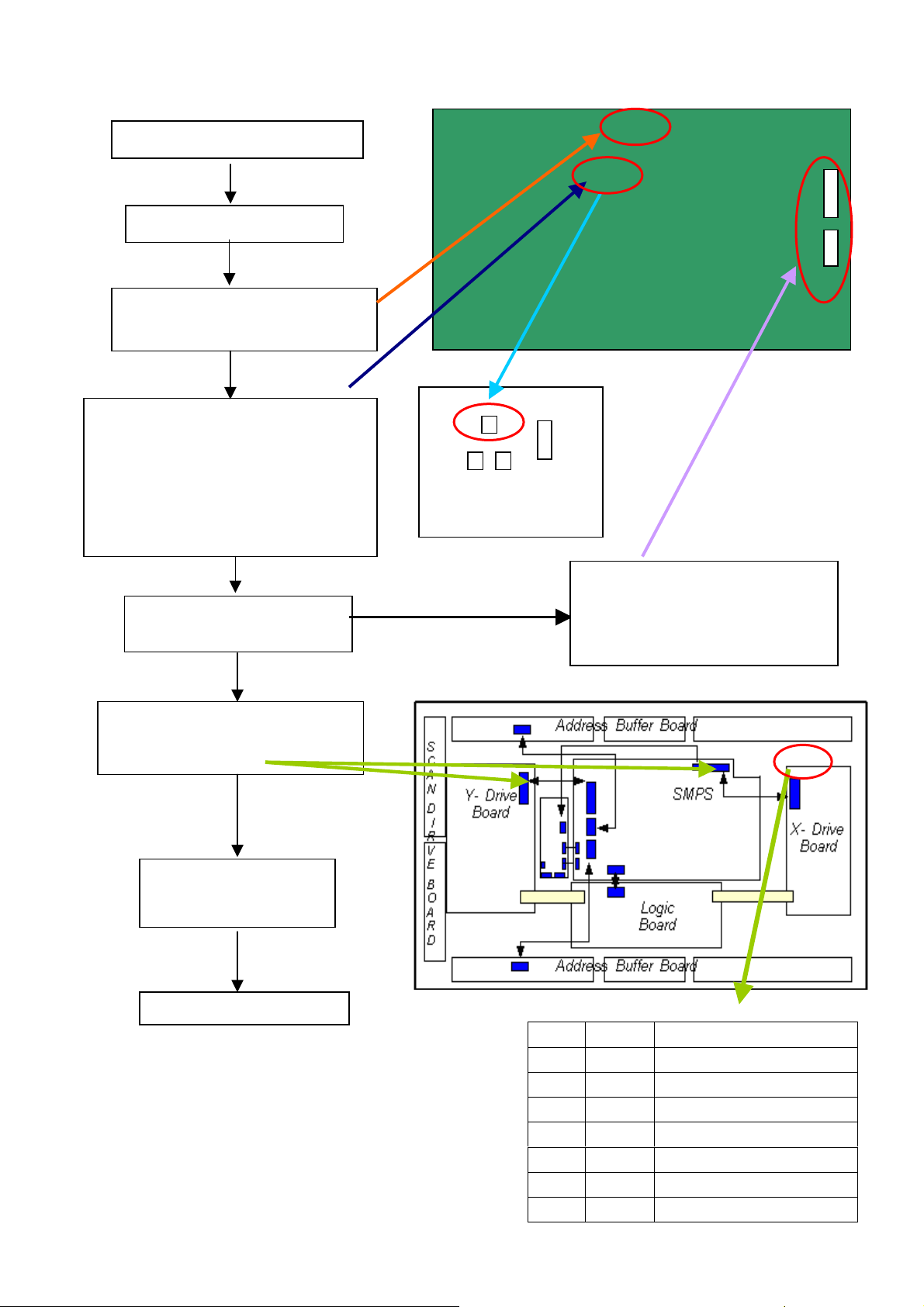

4-2-2 Solution process of whole PDP:

r

p

d

Screen is nothing under power on

Check AC input of PDC

Check PowerSTB5V(U516 3PIN)

Voltage: 5V

Check the REL-SW state of power IO

interface,

High Voltage:Turn on

Low Voltage:Standby

Test Point: C pole of Q5

High Voltage:5V(4.2---5.3V)

Low Voltage:0V

If REL-SW is ok,check othe

ower.

Check device circuit and logic circuit,

Vs, Vset, Vsc, Ve etc.

Arrow shows test point.

If there was anything

unmoral, test voltage an

repair it.

Process of repair as follow

U516

Q5

Image board

R128

CN703

CN704

Q5

Check the voltage of CN703:

PIN5 -- 12 V

PIN8 -- 3.3 V

PIN9 -- 3.3 V

--

Fig1: Voltage sheet

Name Voltage Reference

VS 170V Voltage for driving sustain

VA 70V Voltage for driving address

VE 155V Voltage for driving X-bias

VSET 160V Voltage for driving reset

Vscan -65V Voltage for driving scan

VCC 15V Voltage for driving FET

D3V3 3.3V Voltage for driving logic

21

Page 22

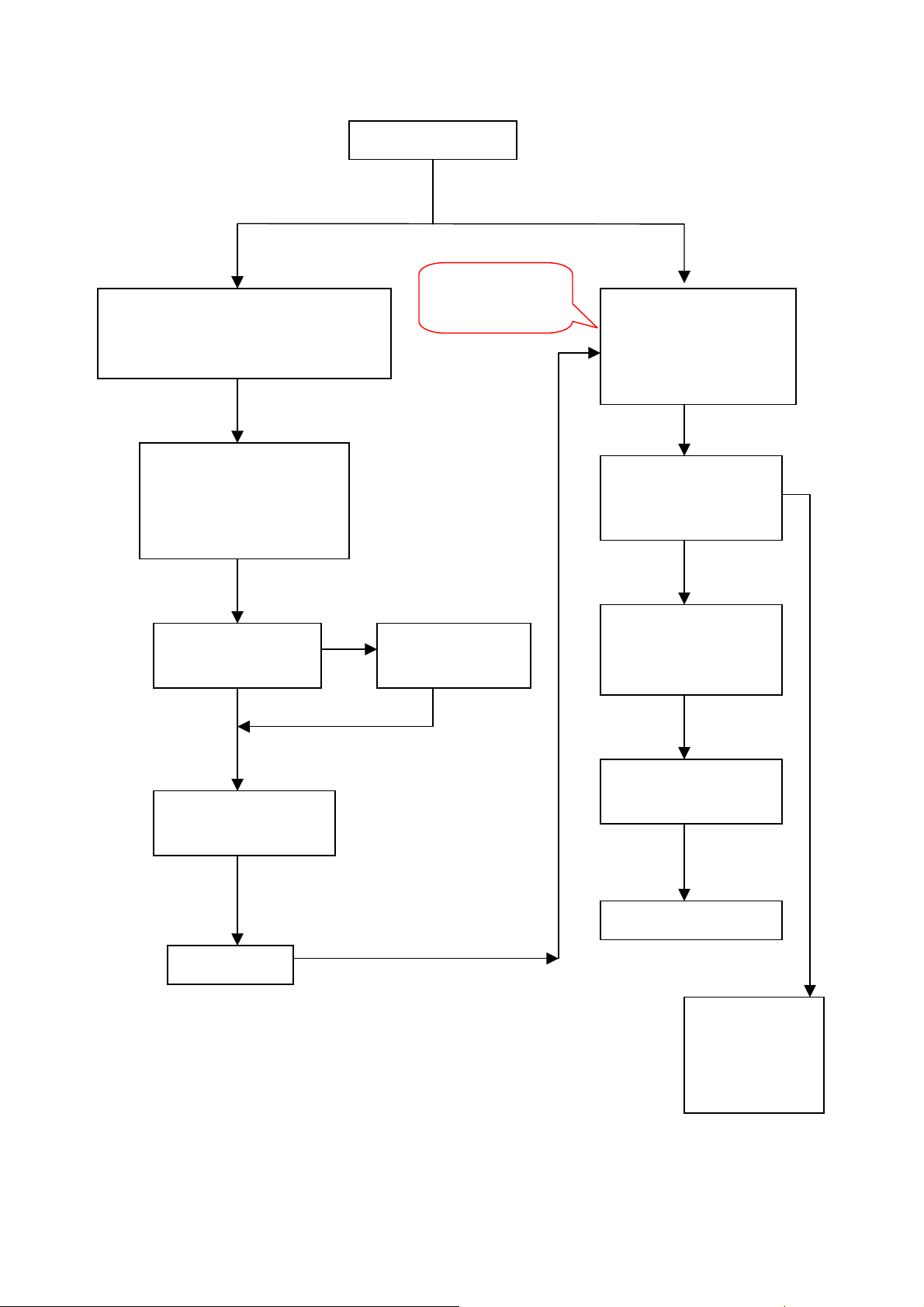

4-2-3 STB POWER Solution process

N

V

N

r

NG N

NG N

V

POWER un-moral

o input of +5VSB,or output is unmoral

Test point:CN903 PIN2

Voltage:5V(4.9-5.1)

Do these process

under the state is

+5VSB

out, or output is unmoral

Test point:CN902

Voltage: AC INPUT±1V

G

Test AC Input of CON901

ok or not?

Voltage:AC 100 V ~ 120

/200 V ~ 240 V

PS-ON ok or not?

Test point:CN903 PIN4

Voltage:DC5V(High)

Test voltage of C905

is DC300V or not?

OK

Check FUSE F901,

BD901ok or not?

Vccp ok?

Test pads of C909

Voltage:DC13V-25

Check IC901 and D901

ok or not?

OK

Q901, Q902, Q903, Q904,

M902 ok or not?

OK

AC POWER-OUT OK

+5VSB OK

Note:Must distinguish connect Grand point of Power primary and secondary level.

22

o input of AC Powe

G

OK

OK

OK

Check circuit of

IMAGE BOARD,

and check PS-ON

OK or not?

Page 23

4-2-4 Solution processes for DC Power

k

r

Check the junction that CN703 to

CN704 or CN701 to CN702 ok

or not?

Test input voltage:

L701 -- 12 V

L703 -- 6 V

L721 -- 3.3 V (Samsung PANEL)

OK

Test voltage as follow:

L705--8V

L706--5V

L704--5V

L718--2.5V

L719--1.2V

OK

4-2-5 Solution processes for SCALER

Check power supply , input

and output signal of U1

(ZR391055) and U2

(DS90C2501)ok or not?.

Check input and output signal of

U8,and TX0-/TX0+ signal etc. o

or not?

OK

OK

NG

23

NG

NG

Is there any short or

cold solder?

Is there any short o

cold solder?

Replace U8

Page 24

4-2-6 Solution processes VIDEO

N

r

r

r

N

N

N

o display under Video, S-video,

YCbCr and YPbPr mode

Check the state of powe

switch ,and DC power.

1.Test input signal of U14

under VIDEO and

S-VIDEO mode

2. Test input signal of U1

at C18/C19/C20 under

YCbCr mode

OK

Check U1

Check circuit of U6

(PW1231) ok or not?

OK

Check circuit of U20

(SCALAR)and LVDS

OK

OK

OK

G

G

G

Is there any short or disconnection,

and signal is wrong.

(The signal of standard color ba

will be very clea

Is there any short or disconnection, CLK

and SYNC signal to U1circuit?

Is there any short or disconnection, CLK

and SYNC signal to U6 circuit?

)

U6

X5

24

Page 25

5、White-Balance Adjustment

5-1 Equipments list

Chroma7100 1set

VG828 video signal generator 1set

Chroma-2326 1set

5-2 Preparation and Adjustment process

1、Preparation:

Connect rear Video port of PDP with AV port of VG-828.

Connect component port of PDP with YPbPr port of VG-828

Connect VGA port of PDP with corresponding port of Chrom2326

Turn power of PDP and test instrument on.

Before open lens, Press O-CAL of Chrom-7100 and revise lens.

2、Adjustment process

AV Adjustment

1). Change to Video mode, you can press “SOURCE” of remote. Press “Vol - ”, adjust volume

until Min. Then press number key “6543”and enter factory Menu.

2). Press “SOURCE” and change to Video Rear mode

3). When setting of VG-828 is TIM946/PAT922, 32 Gray steps. Then, see the color of picture

is deflection or not. And the Gray steps distinguish 28 steps from 32steps or not.

①. If dark of Gray is deflection, press “CH+/-”and adjust:

1.White.BRoCVBS (vMin=0,vMax=100,vDef=50) →50,

2.White.BBoCVBS (vMin=0,vMax=100,vDef=50) →50,

3.White.BGoCVBS (vMin=0,vMax=100,vDef=50) →50,

②. If sharpness of Gray is deflection, press “CH+/-”and adjust:

4.White.BRgCVBS (vMin=0,vMax=100,vDef=50) →50,

5.White.BBgCVBS (vMin=0,vMax=100,vDef=50) →50,

4). When the Gray is ok, change input signal to white picture at P936, Use colored analysis

instrument Chroma7100 measure colors temperature value of picture at present (whether

Chroma7100 is it given to picture center to pop one's head), On pressing the remote

controller such as the specification of going beyond "program + /- "key choose following

the projects adjust:

4.White.BRgCVBS (vMin=0,vMax=100,vDef=50) →50,

5.White.BBgCVBS (vMin=0,vMax=100,vDef=50) →50,

5). When adjustment about white is ok, changes signal to P822 that Gray steps picture. The

Gray picture has no deflection color, and the Gray steps distinguish 28 steps from 32steps

Note: The white balance is adjusted in the course, will influence each other to adjust in the

adjustment of gray steps and white picture, and need to change repeatedly.

Please notice that can't enter the mode of the factory in every station homework after adjusting

and finishing, so as not to miss movements and revise the white balance data again.

25

Page 26

VGA Adjustment

Setting of Chroma2326 as follows:

Gray picture: TIM4/PAT48

White picture: TIM4/PAT105

Change to VGA mode, press “CH+/-”and adjust following items. Method same as AV mode:

6. White.BRoVga (vMin=0,vMax=100,vDef=50) →50,

7. White.BBoVga (vMin=0,vMax=100,vDef=50) →50,

8. White.BGoVga (vMin=0,vMax=100,vDef=50) →50,

9. White.BRgVga (vMin=0,vMax=100,vDef=50) →50,

10. White.BBgVga (vMin=0,vMax=100,vDef=50) →50,

Note: Press “Source” and change mode that Video Rear to VGA, then adjustment items of

white balance same as Video Rear First, press “CH+/-” and adjust under the VGA mode.

(White.BBgCVBS(vMin=0,vMax=100,vDef=50)→50 CVBS change to VGA)

COMPONENT Adjustment:

1). VG828 setting as follow:

Gray picture:TIM954/PAT922

White picture:TIM954/PAT936

2). Change to COMPONENT1 mode,press “CH+/-”and adjust following items. Method same

as AV mode:

1. White.BRoVga (vMin=0,vMax=100,vDef=50) →50,

2. White.BBoVga (vMin=0,vMax=100,vDef=50) →50,

3. White.BGoVga (vMin=0,vMax=100,vDef=50) →50,

4. White.BRgVga (vMin=0,vMax=100,vDef=50) →50,

5. White.BBgVga (vMin=0,vMax=100,vDef=50) →50,

Adjustment stand of white Balance: x=299±15,y=315±15

6、DDC program and test

6-1 Equipments list and prepare

DDC tester 1PCS

PC 1set

D-SUB cable 1PCS

DVI cable 1PCS

Barcode reader 1set

Prepare before test:

1. Turn on the power of your PC and programmer, then make good connection of them.

2. Connect the D-SUB wire and DVI wire to the DDC program equipment and the PDP monitor.

6-2 Program and test process

1. Choose different DDC menu according to different customer , do use PAGE DOWN/PAGE UP to go to the

submenu and parent menu until find the right model. Press enter to access the program interface. There will

be shown RGB on the screen. Then switch to RGB program on the DDC connector。Press any key to access

RGB program interface ,then there will be “input serial no.:” prompt on the screen.

26

Page 27

2. Use Bar Readers to read the serial no to the program,then make sure the serial no you have read is the same as

on the barcode. Then set the PDP to blue screen mode, press enter to start.

3. Watch the information of the program, it means programmed OK when the following interface come out.

please CHECK Manufacturer Name、V endor Assigned Code、Model Name、Serial Number:

****[?????????****](same as Barcode)、Week of Manufacture:**、Year of Manufacture:****、Checksum:

**(same as the last byte of data table, reference to the note of RGB programming picture)and so on.

4. Press Enter to access RGB DDC test interface,follow the DDC test picture,CHECK Manufacturer Name、

V endor A ssigned Code、Model Name、Serial Number:****[?????????****](same as Barcode)、Week of

Manufacture:**、Year of Manufacture ****、Video Input:Analog、Checksum:**(same as the last byte

of data table, reference to the note of RGB programming picture)and so on.

5. Press any key to access DVI program interface, there will be “DVI” shown on the screen. Switch the of

switch on the DDC connector, press any key to access DVI program interface, there will be “input serial

no.:” promote.

6. Use Bar Readers to read the serial no to the program,then make sure the serial no you have read is the same

as on the barcode. Then set the PDP to blue screen mode, press enter to start.

7. Watch the information of the program, it means programmed OK when the following interface come out.

please CHECK Manufacturer Name、V endor Assigned Code、Model Name、Serial Number:

****[?????????****](same as Barcode)、Week of Manufacture:**、Year of Manufacture:****、Checksum:

**(same as the last byte of data table, reference to the note of DVI programming picture)and so on.

8. Press Enter to access DVI DDC test interface,follow the DDC test picture,CHECK Manufacturer Name、

V endor A ssigned Code、Model Name、Serial Number:****[?????????****](same as Barcode)、Week of

Manufacture:**、Year of Manufacture ****、Video Input:Analog、Checksum:**(same as the last byte

of data table, reference to the note of DVI programming picture)and so on。If the recording is failure, check

the connection of equipment and record again from the step4.If all of these work does not take work ,please

ask IE department for help.

9. Notice :the “?” and “*” symbol will be changed according to the year of manufacture ,and so on.

27

Page 28

7、、Flash Update

7-1 The list of Instrument

1、Prepare 1 piece of RS232 cable(The Pin connection see the Figure-1,If difference, please re-connect the

e)and 1 set of PC.

cabl

2、 Connect the RS232 cable with PC and PDP(See the Figure-2).

PC

PC

To

To

To PC

To PC

Pin (Female)

9 Pin (Female)

Signal Pin

Signal Pin

1

1

1

RXD 2

RXD 2

RXD 2

3

3

3

TXD

TXD

TXD

DTR 4

DTR 4

DTR 4

GND 5

GND 5

GND 5

DSR 6

DSR 6

DSR 6

RTS 7

RTS 7

RTS 7

CTS 8

CTS 8

CTS 8

9

9

9

Figure-1 Figure-2

7-2 The operation explaining Flash Update

Note: Operation Under the situation of PDP working normally.

The iDev is a Windows utility that installs hex files into the FLASH ROM of the target Image Processor

em. iDev is a Windows-based application.

syst

Downloading is done through an RS-232 connection, which is bidirectional and serial.

Step 1: Open the file iDev (You should

To Philips PDP

To Philips PDP

Philips PDP

Philips PDP

To

To

9 Pin (Female)

9 Pin (Female)

Signal Pin

Signal Pin

1

1

2 RXD Received Data

2 RXD Received Data

3 TXD Transmitted Data

3 TXD Transmitted Data

4 DTR Data Terminal Ready

4 DTR Data Terminal Ready

5 GND Signal Ground

5 GND Signal Ground

6 DSR Data Set Ready

6 DSR Data Set Ready

7 RTS Request To Send

7 RTS Request To Send

8 CTS Clear To Send

8 CTS Clear To Send

9

9

PC

PDP

RS232 Connector

RS232 Cable

28

Page 29

Step 2: Choose the director of the file to flash

Note: Connect the computer’s serial port (usually COM1) to the serial port of the ZORAN evaluation board

using a null modem cable, and select speed.

Step 3: Flash only the file required

29

Page 30

Step 5: Press reset or cycle the power from the Evaluation Board and click “down”

Step 6: View hex file flashing progress, after the files have been downloaded, Click “Close” to exit

30

Page 31

8、Software Platform Reference TV Application

8-1 Introduction

This document describes Phobos’s reference TV application, supporting the basic control functionalities

required to watch television. The reference application is designed to assist Phobos customers in implementing

a DTV system, using the Generation9-Elite IC and its APIs. This reference application is intended to support

U.S. based terrestrial analog/digital broadcasting(NTSC/ATSC), and includes Electronic Program Guide

(EPG), closed captioning, and parental control, as well as basic TV controls and underlying A/V decoding. The

reference TV application layer lies on top of Phobos’s Cougar API middleware that provides the

Transport/Audio/Video/graphics driver functionalities as a chip-independent set of APIs.

8-1-1 Supported Functions

The supported application functions are:

• Power control

• Source selection

• Channel change (up/down, recall and direct digit key input)

• Volume and mute control

• Closed caption selection

• Electronic program guide

• Menus: audio, video, setup, feature

8-2 The Phobos Reference TV Application

This chapter describes basic TV controls such as channel changing, source selection, and mute/volume control.

These basic functionalities are made available through the combination of GUI and standardized TV APIs. The

application also utilizes the results of PSIP parsing and decoding of EIA708/608 data. These are used to

support closed captioning and parental control, both of which are required on television sets sold within the

U.S.

In addition to Tuner, AV Input and Channel Map APIs, the reference application uses a set of Control

Array APIs to control the hardware blocks. These provide a standardized way to control the various hardware

blocks in the TV chassis.

8-2-1 Power Control

The current reference application does not support standby power control as part of this

implementation. Instead, pressing the power button on the remote and front panel controls the display and

audio outputs only. A power-on configures the system based on Control Array values stored in non-volatile

memory.

8-2-2 Source Selection

The Reference platform has analog/digital base band inputs as well as transport input through ATSC digital

channel. The TV/Input button cycles through the input sources:

1. RF

2. Front Composite (shared with S-video)

3. Rear Composite (shared with S-video)

4. YPbPr Component 1

5. YPbPr Component 2

6. VGA

7. HDMI input

The displayed banner for changing source is the same as the channel banner, except for displaying source

number and name.

31

Page 32

8-2-3 Channel Change

There are three ways to select a channel in the reference TV application: channel up/down, digital, and last

buttons in remote controller.

• Pressing the channel up or down key tunes to the next highest or lowest channel in the selected channel

map; a channel in a different channel group (analog or digital) is tuned at the limits of the available scan.

The channel map is established through the Auto Program menu, which automatically removes any no

signal channels. After channel scanning, the channels are grouped as digital channels and analog

channels.

• For digital channels, the channels are sorted on the virtual channel number. Further manual editing of the

channel list can be done through the Manual Channel Set menu. If no channels are enabled in the

selected channel map after initial power on, then the channel up/down keys select the channel number

next to the current channel, and determine the analog or digital channel based on the availability of

signal.

• Channels can be directly accessed by pressing the digit keys on the remote controller. The channel

selected is tuned immediately if the OK key is pressed, or will be tuned automatically after two seconds

of inactivity following the last entered digit. If the entered digit keys starts with a zero (“0”), the channel

number will be tuned to the second digit (for instance, the digits 03, entered in sequence, will tune

immediately to channel 3). Any channel may be selected by this method, regardless of its presence or

absence in the current channel map.

• Pressing the Last key in the remote control tunes the channel selected prior to the currently tuned

channel. For ATSC channels, it selects the sub-program number as well as the channel number.

The above channel-change operations are implemented via the Tuner and Channel Map APIs.

After tuning, the application displays the information of the currently-tuned channel. This includes:

1. Channel number [Ch 9-1]

2. Channel Label [for instance, KQED]

3. Current Time [for instance, 12:30 PM]

4. Rating information [for instance, TV-PG]

The virtual channel number will be displayed if the current channel is digital. The chann el la bel is extracted

from input signal if there is no label setting for the current channel. The channel label can be explicitly set with

Channel Labels menu, which will use TLChMapSetChannelName to store the label.

8-2-4 Volume and Mute Control

Pressing the volume Up or Down button changes the current volume in the Control Array and applies this

change to the hardware block. The range of control is determined by the Control Array; the current

implementation has a range from 0 to 63. Pressing either of the volume keys clears the mute audio mode of

operation, if previously set. If no button is pressed for five seconds after pressing the last volume Up or Down

button, the volume display will be automatically removed.

The reference application supports audio mute or un-mute by pressing the Mute key. When mute is enabled,

the audio is muted, displaying an icon on upper right side. The mute condition is cleared when the TV is

powered off.

Pressing the Mute key invokes the mute icon on the right corner of screen.

8-2-5 Closed Caption Selection

This section describes how to enable Closed Caption (CC) on the Phobos TV application. When the TV

is switched ON, captions are disabled by default. The user switches captions ON using the [SUBTITLE] key

on the remote. Each time the [SUBTITLE] key is pressed, a new language/CC option, is displayed near

the bottom center of the display. The sequence of options available are listed below

(depending upon the stream type — ATSC/NTSC).

For ATSC, English – Spanish – French – Off For NTSC, CC1 – CC2 – CC3 – CC4 – Off The displayed CC

option can be set either by the user pressing the [OK] key on remote, or else it is set automatically after two

32

Page 33

seconds.

8-2-6 Navigating a Menu

Pressing the Menu button displays the most-recently-used menu. The main menu is presented in two areas: a

group of icons, and a list of sub-menus based on the selected icon. After launching the menu, the Left/Right

buttons are used to select one of the two areas. The icons and sub-menus can then be navigated through the

Up/Down arrow keys, which moves the highlighted item up or down, depending on the key pressed. This

display gives the user a method of selecting among the various sub-menus available, in order to co nfig ure the

system.

The action wraps from first to last when an up arrow is received and the first list item is highlighted, and from

the last to the first when a down arrow is received and the last list item is highlighted. If no key is pressed for

one minute after pressing the last navigation or OK buttons, the volume display will be automatically

removed.

9、Block diagram & Explain

9-1 PDP b

J6 to Panel

Front AV PCB

lock diagram and functions

CN5008 to CN8003

CN4001 to CN8086

Panel

CN009 to J11

CN004 to J30

POWER PCB

CN8001 to CN902

CN904 to CN703

CN903 to CN704 & J603

CN706 to CN903

Image Board PCB

Power Down Control PCB

J42 to P210

Key Board PCB

Function of Board:

1) IMAGE Board : Control all input signals, Decode the video signal, De-interlace, and

send digital signals (LVDS signal) sent from image Board and display

2) PDC Board: Power Down Control Board

3) SIDE AV Board: The input signal interface

4) Power Board: Supply Power for Panel and Image Board

5) KEY Board: POWER, Signal Source, MENU, CH+, CH - / VOL +, VOL -

6) Power ON /OFF: Turn power on/off

33

Page 34

Part apt to decrease:

1) BEZEL, REAR COVER& GLASS FILTER

2)

Panel

3) Terminal Board’s RCA plug

9-2 Image board block diagram and signal introduce/process

9-2-1 Image board block diagram

34

Page 35

X

ATSC/NTS

C

V

TV

PDP Module

PDP Module

MPEG

l

Signa

Process

SCALER

Process

Analog

AV

Process

ideo / Audio block

ATSC/NTSC TV (Tuner)

Signal

Logic

(Memory Con

Y Con.)

X-

SMPS

Power

supply

Audio Process

Scan

Drive

PPDDPPPPaanneel

DATA Drive

Speaker

l

Scan

Drive

Y

9-2-2

Signal introduce/process

Panel

SDI-42HD

35

Page 36

ATSC+NTSC TV RF signal are separated into 2 way output when enter into Tuner. One is NTSC

(Analog signal) that output video signal by mixing, amplifying, demodulating. Video signal are

separated into Y/C signal throughTEA6415C, and transferred into ITU601 through ADV7401, then

send into Video-audio process chip Generation9. Tuner output SIF audio signal to MSP3450G to

process, amplify, then put in D-type amplifier TA2024.

The other ATSC (Digital signal, ATSC channel bandwidth is 6MHZ) via Tuner transferred into

TS-strea

m through 44MHZ intermediate frequency amplify, ASW filter, QAM\OFDM demodulate,

then enter into Generation-9 to MPEG decode, video part revert into video signal through coding,

and transferred into double-field TTL signal by this chip process. Then put into Scaler and LVDS

drive chip DS90C2501, through coding output 5 pair LVDS signal to drive PDP panel module.

Digital audio signal from Generation-9 revert into Audio signal to MSP3450G through PCM

decoding.

Program information in TS-stream be parsed and stored, user could know related program

information through OSD query menu. For multi-program TS-stream, user could appoint to see

some program in this stream through program guide EPG.

, S-video, YPBPR, DVI, D-Sub and each Audio signal through two group of 74HC4052

AV

switch with ATSC audio signal together put into MSP3450G, through alt, woof, balance, volume,

SRS, BEE process, then amplify by D power amplifier TA2024,output to loud-speaker.

36

Page 37

9-2-2 Input signal introduce

1. VIDEO: transmit bright & chroma signal , it is general ,its picture quality is equal to the general VCD.

S-VIDEO transmit the bright and the chroma single, and can reduce/control the cross-interfere , it is better

than the Video.

2. RGB&D-SUB(Pc interface ): general RGB simulative input interface .

3. YCbCr(NTSC/PAL): is composed of one bright and two chromatism signals U/V. due to the eye is more

sensitive for bright than chroma , RGB via the formulae Y=0.39R+0.50G+0.11B to transform into one bright

d two chromatism signals U(R-Y), V(B-Y).

an

4. VIDEO、、S-VIDEO、、YCBCR: the frequency 15.6KHZ 50(PAL)/60HZ(NTSC), interleaved simulative signal.

5. YPbPr: non-interlaced signal, belong to DTV scope, support 480P,720P,1080i format, current is NTSC.

6. DVI:digital Visual Interface, has 29pin(DVI-I)and 25pin (DVI-D), now many top grade display card own it.

10、、Waveform of signal

10-1 Waveform of input signal

YCbCr:

(Instrument outputs

Timing946 Pattern946 color bar picture

the sub board signal,,Instrument::VG828/ TG19CC/Oscillograph)

Y Luminance Signal R Red Signal

B Blue Signal

YCbCr: Timing 949 Pattern936 Full White Picture

37

Page 38

Y Luminance Signal

YCbCr:Timing 949 Pattern921 Gray Picture

Y Luminance Signal

YPbPr:Timing955 Pattern946Color Bar Picture

Y Luminance Signal R Red Signal

B Blue Signal

38

Page 39

YPbPr:Timing953 Pattern921 Gray Picture

Y Luminance Signal

YPbPr:Timing954 Pattern936 Full white picture

Y Luminance Signal

Video: Timing946 Pattern946 Color Picture Video: Timing949 Pattern936 Full White Picture

Video: Timing949 Pattern921 Gray Steps Picture

39

Page 40

S-video: Timing946 Patern946 color bar picture S-video: Timing949 Pattern936 Full white picture

S-video: Timing949 Pattern921 gray steps picture

10-2 Signal waveform in the image board

Video: Timing946 Pattern946 color bar picture

U14(Y/C separate)In (pin3 C136)/(pin20 C142)

40

Page 41

U14(Y/C separate)Out pin18/17 R119/R120

Video: Timing 949 Pattern936 white picture

U7 decoder output 8bit digital signal:

S-Video: Timing 946 Pattern946 color bar picture

U14 pin8, pin10

S-Video: Timing 949 Pattern946color bar picture

U7 8bit digital signal output:

41

Page 42

YCbCr: Timing946 Pattern946 Full white picture

Y signal—L55 R signal—L53

B signal—L54:

YCbCr:Timing 949、946 Pattern921、936、946 gray scale, color bar, white picture

U7 decoder output 8bit digital signal waveform

YPbPr: Timing 955 PATTERN946 color bar picture

Y signal—L55 R signal—L53

42

Page 43

B signal—L54

43

Page 44

11、Check and Measure

11-1 Image board

Test the power of each chip with the universal meter, to ground impedance and earth

situation.

11-1-1 Power Check and Measure

J603

Supply with getting red arrow point three interface J603, CN703 and CN704 that identification

come out for power, image of board with the interface among having picture, it corresponding

power make detection method separately among following several picture.: (Only for

SUMWUNG POWER)

①. In the following the first picture it is successively 1 to 6 pin of J603 from left to right:

Among them, 1pin and 2pin connect 12V voltage; 3pin, 4pin and 5pin are digital earth;

The second picture it is 1 to 5 pin of CN704 from left to right: Among them,2pin and

4pin of CN704 connect digital earth, 1pin of CN704 connect D6V voltage, 3pin of

CN704 connect D12V voltage ,The following picture shows:

CN703

CN704

44

Page 45

In the following picture it is

2

them

, The second pin connects STB5V,3pin 、6pin 、7pin and 10pin are grounded digitally,

5in connect D12V voltage, 8pin and 9pin connect D3.3V voltage,11pin connect D6V

voltage .The following picture shows:

11-1-2 Voltage value of IC necessary

Voltage Corresponding IC position and pin

U706 Pin3;

U704 Pin3;

U710 Pin3;

3.3V

U2 Pin38;

U9 Pin13;

U13 Pin3;

U10 Pin91;

CN703 Pin2;

E708;

STB5V

R301;

R635;

R68

L722,L713;

5V

L706,C718,E717;

CN706(PDC Board)

Pin2;

U709 Pin3;

6V

U702 Pin3;

U711 Pin3;

J603 Pin1,Pin2;

U701 Pin3;

R322;

12V

L702,E711;

CN703 Pin5;

L701;

successively 1 to 11 pin of CN703 from left to right. Among

D40 Pin5;

D41 Pin5;

U68 Pin3;

U30 Pin3, Pin1;

J32 Pin7;

U48 Pin26;

U52 Pin20

TP9;

R126,R128;

L216,L217;

R301,R635,R638

CN703 Pin10;

L703;

C702

TP8;

U601

Pin29,Pin30,Pin33;

C700;

U602 Pin8;

U12 Pin2,Pin4;

C695

45

Page 46

11-2 SIDE AV Board

The picture below is AV SIDE board, The interface pointed out in order to provides the power

for Audio board. The enlarged interface picture show in its connection.

CN004

Shown order connect power(it depends on to be 1 pin to 10 pin from left to right) according to

the picture:

11-3 PDC Board

The following picture show PDC Board, among them getting red difference label about

connection with PDC Board and main board, power board and switch of board.

CN901: Connect with P9Z1 of Power Switch Board;

CN902: Connect with CN8001 of Power Board;

CN903: Connect with CN706 of Imager Board.

CN903

CN901

CN902

The following picture shows the pin connection of CN903:

46

Page 47

12、Mechanical Introduction

12-1 PDP Internal view

47

Page 48

12、Mechanical of cabinet front disassembly 42MF130A

48

Page 49

12-2 Mechanical of cabinet front disassembly 42MF230A

49

Page 50

12-3 Disassembly and assembly

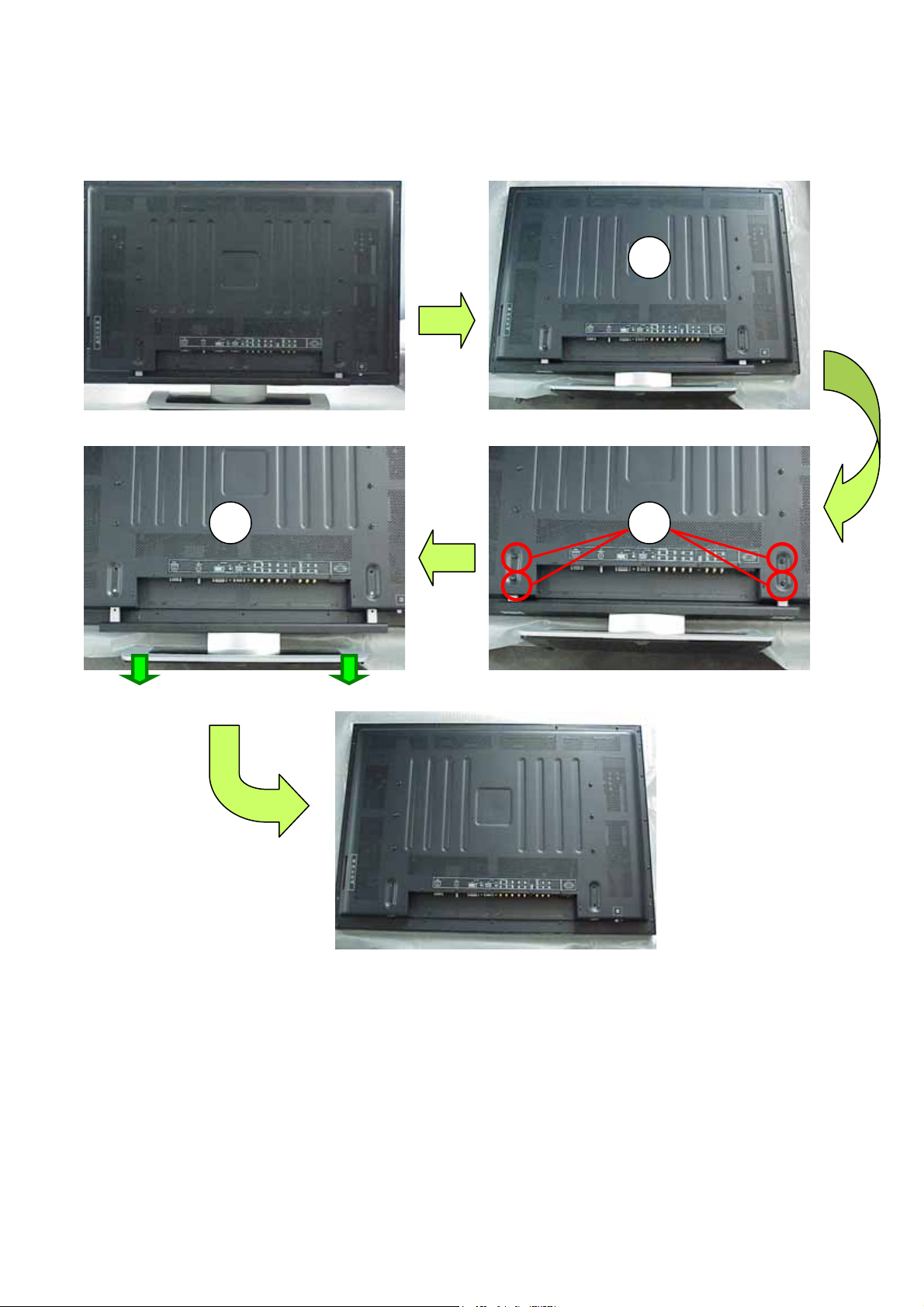

12-3-1 PDP stand removal

1) Unplug the AC power and all signal cables.

2) Place the PDP upside down on a tabletop (use a protection sheet or EPE bag), Take care, that this

is flat and free from obstacles like screws, to prevent damaging the fragile PDP glass filter (1).

3) Remove the four black colored screws around the stand holder (2).

4) Remove the Base assembly from PDP as the direction arrowhead showed (3).

3 2

50

1

Page 51

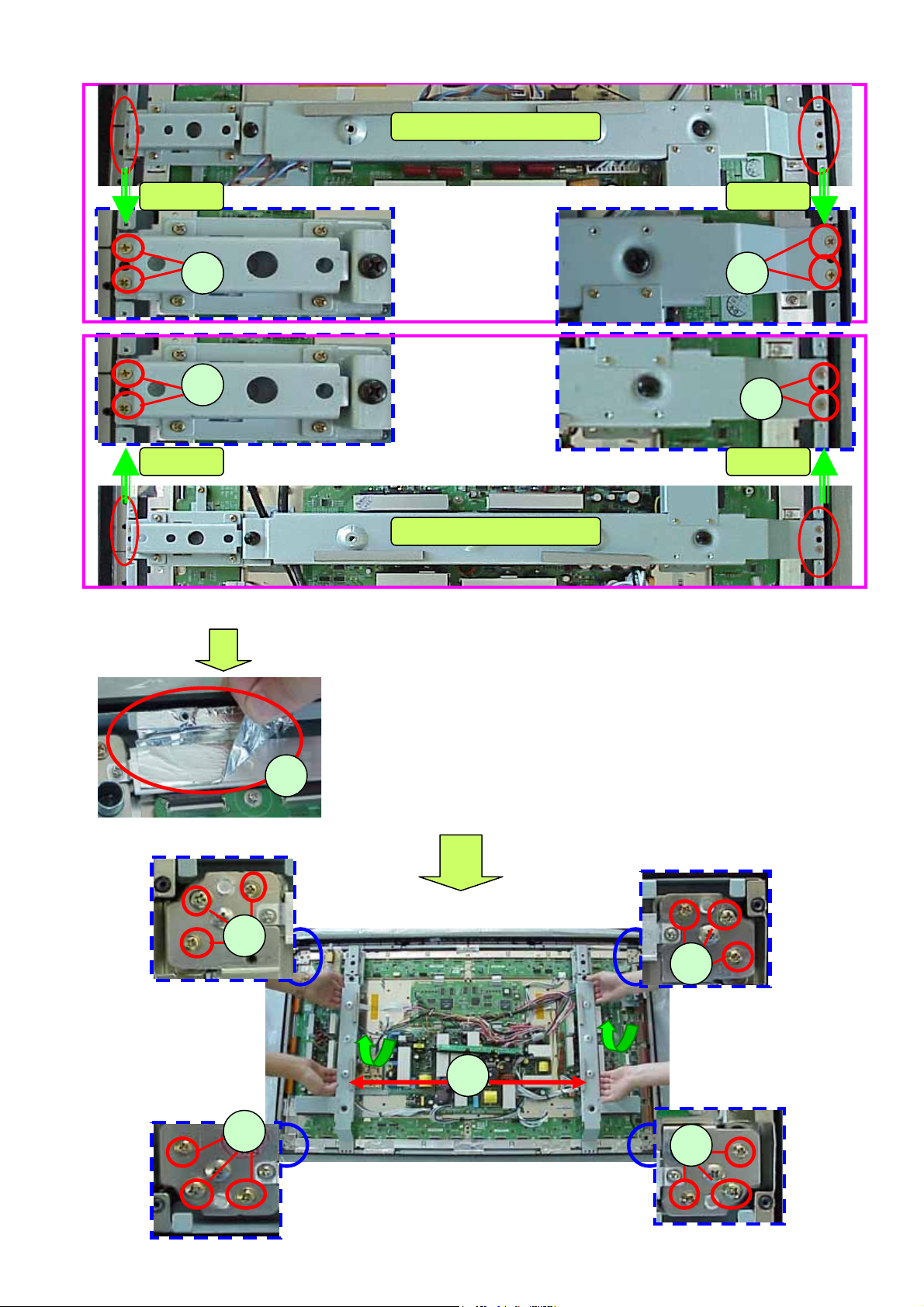

12-3-2 Back Cover Removal

5) Remove the six big black colored screws in the panel holder as the red-circle showed (1).

6) Remove the seven black colored screws around the terminals as the green-pane showed (2).

7) Remove the eighteen black colored screws around the back cover as the blue-pane showed (3).

5) Carefully prize up the back cover from

the left of the PDP (5).

z Don’t remove the cover in this st

ep, otherwise, the power button

should be damaged.

6) Carefully remove the Back Cover from the

top of the PDP, and store in a safe place.

5 4

3

1

2

Push

4) Push in the power button before remove the

back cover(4) (to prevent damaging the

power button).

7) Done.

Notes: Must be press down the power button before remove the back cover, if don’t do this it

well be avert broken switch at the remove the back cover.

51

Page 52

3

12-3-3 Rear Low Cover removal

1) Remove the three black screws in Rear low cover (1).

2) Carefully use a allen screwdriver to remove the six silver colored allen screws M3*6mm (2).

3) Remove the five black screws (3).

5 4

ZOOM-1 ZOOM-1

2

6

1

4) Remove the one silver screws and remove the

GND cable (4).

5) Disconnect the AC cable from AC FILTER

Board (5).

6)Remove the Rear Low Cover as the

direction arrowhead showed (6).

7)Done.

52

Page 53

12-3-4 Main Board(MGPC) removal

1) Disconnect the all connectors(J42,CN706,J14,J603,CN703,CN704,J11,J30 and J6 form M

GPC(main board). See the above figure.

2) Remove the six silver screws from MGPC(main board)(1).

3) Remove the MGPC board from PCB plate. 4) Done.

1

PCB Plate

J6

1

53

Page 54

12-3-5 PCB Plate Removal

1 2

4

3

1) Remove the two Cable Clips from the PCB Plate(1)(2).

2) Remove the six sliver screws(3).

3) Cut the cable tie(4), Note, please carefully cut it, don’t make the cable damage.

4) Remove the PCB Plate

54

Page 55

12-3-6 Key Board Remove

1) Remove the four silver screws(1).

2) Pull the Bezel downside(2), then push and take out the KEY board

assembly(3).

3) Remove the five silver screws to disassemble the key board from Key button.

Pull

Push and take it out

3

2

55

Page 56

12-3-7 Side AV Board Removal

1) Remove the two silver screws (1).

2) Remove the side cover from Side AV board(2)

3

3) Disconnect the CN004 and CN009 from Side AV board.

4) Remove the four silver screws (3).

2

CN004

1

CN009

3

56

Page 57

12-3-8 PDC(power down control)Board Removal

Panel

stand

Panel Holder

ZOOM 1

1 2

1) Remove the four sliver screws (1) and remove the panel stand from panel holder as

the direction arrowed showed.

2) Remove the four silver flat screws (2).

3) Remove the two black screws (3)

4) Remove the two silver screws (4)

5) Remove the panel holder from PDP.

CN903

5

CN901

CN902

ZOOM 2

2

3

4

6) Disconnect CN901,CN902 and CN903 from PDC

board.

7) Remove the four sliver screws (5), and remove

the PDC board.

57

Page 58

12-3-9 Panel Module Removal

1) Remove the eight silver flat screws around the two panel holder (1).

ZOOM 1 ZOOM 2

1 1

1

ZOOM 3 ZOOM 4

2) Remove all the aluminum foil around the panel (2), after assemble

the new panel, must re-affix the aluminum foil, if it’s broken

must change a new one, otherwise, the EMI can be affected.

3) Remove the twelve silver screw around the PANEL corner (3).

2

4) Two people hold the panel holder 1 and 2 respectively, then uplift

the panel module and move it out form the front cover(Bezel),

and store in a safe place.

3

3

Panel Holder-1

Panel Holder-2

4

1

3

3

58

Page 59

12-4 Block Wiring diagram

12-4-1 PDP boards block wiring diagram

Internal speaker

Internal speaker

Internal speaker

Internal speaker

Internal speaker

Left

Left

Left

Left

Left

Sub-PSU

Sub-PSU

Sub-PSU

Sub-PSUSub-PSU

PANEL Module

PANEL Module

PANEL Module

PANEL Module

Main PSU

Main PSU

Main PSU

Main PSUMain PSUMain PSUMain PSU

CN706

CN706

CN706

J42

J42

J42

J42

CN706

J14 J603

J14 J603

J14 J603

J14 J603

J6

J6

J6

J6

Power

Power

Power

Power

input

input

input

input

PDC B/d

PDC B/d

PDC B/d

PDC B/d

AC output

AC output

AC output

AC output

Internal speaker

Internal speaker

Internal speaker

Internal speaker

Internal speaker

Right

Right

Right

Right

Right

CN902CN903

CN902CN903

CN902CN903

CN902CN903

CN901

CN901

CN901

CN901

Power filter B/d

Power filter B/d

Power filter B/d

Power filter B/d

CN004

CN004

CN004

CN004

CN009

CN009

CN009

CN009

Side AV B/d

Side AV B/d

Side AV B/d

Side AV B/d

Image board

Image board

Image board

Image board

Image board

Image board

Image board

Image board

Image board

Image board

Key board

Key board

Key board

Key boardKey board

CN703

CN703

CN703

CN703

CN704

CN704

CN704

CN704

J11

J11

J11

J11

J30

J30

J30

J30

Socket

Socket

Socket

Socket

59

AC in

AC in

AC in

AC in

AC input

AC input

AC input

AC input

output

output

output

output

input

input

input

input

AC switch B/d

AC switch B/d

AC switch B/d

AC switch B/d

Page 60

No. Pin Connection Name Pin function

J42 Connector(13 Pins):

Pin 1= GND Pin 2= +5VSB

Pin 3= IR Pin 4= ENTER

J42 to Key board

1

MGPC key control signal

output

Pin 5= LED-B Pin 6=LED-A

Pin 7=KEY6 Pin 8=CH+

Pin 9= CH- Pin 10=VOL+

Pin 11=VOL- Pin 12=MENU

Pin 13=TV video

CN706 Connector(4 Pins):

Pin 1,3= GND Pin 2=+5VSB

Pin 4=REL-SW

CN903 Connector(4 Pins):

Pin 1,3= GND Pin 2=+5VSB

CN706 to CN903

2

PDC board DC output, and

MGPC standby PDC power

control output

Pin 4=PS-ON

J14 to speaker MGPC audio signal output

3

J14 Connector (2 Pins+2 Pins):

LO+/COMLO- and RO+/COMRO-

J603 Connector(6 Pins):

J603 to Sub-PSU

4

MGPC audio circuit power

input

Pin 1,2=+12V Audio

Pin 3,4,6=GND

Pin 5 = NC

CN703 Connector(11 Pins):

Pin 1=NC Pin 2=STB5V

Pin 4=Relay-SW Pin 5=D12V

Pin 8,9=D3.3V Pin 11=D6V

CN703 to Sub-PSU

5

MGPC power input and

relay control output

Pin 3,6,7,10 =GND

CN704 Connector(5 Pins):

CN704 to Sub-PSU MGPC power input

6

Pin 1=D6V Pin 3=D12V

Pin 2,4=GND Pin 5=NC

J11 Connector(5 Pins):

J11 to CN004 To Earphone output

7

Pin 1,3=GND Pin 2=EAR-L

Pin 4 = EAR-R Pin 5=Phone-on

J30 Connector(10 Pins):

Pin 1,3,5,9=GND Pin 2=CVBS IN-2

J30 to CN009 Side AV signal input

8

Pin 4=FRONT-Y Pin 6=FRONT-C

Pin 7=FRONT-AV-SEL

Pin 8=SM-L Pin 10=SM-R

J6 LVDS connector(31 Pins):

Pin 1,8,9=NC

Pin 2,4,6,11,14,15,18,19,

J6 to Panel Logic

9

b/d

MGPC LVDS signal output

22,23,26,27,30,31=GND

Pin 12=TXE3p Pin 13=TXE3m

Pin 16=TXECp Pin 17=TXECm

Pin 20=TXE2p Pin 21=TXE2m

Pin 24=TXE1p Pin 25=TXE1m

Pin 28=TXE0p Pin 29=TXE0m

60

Page 61

61

Page 62

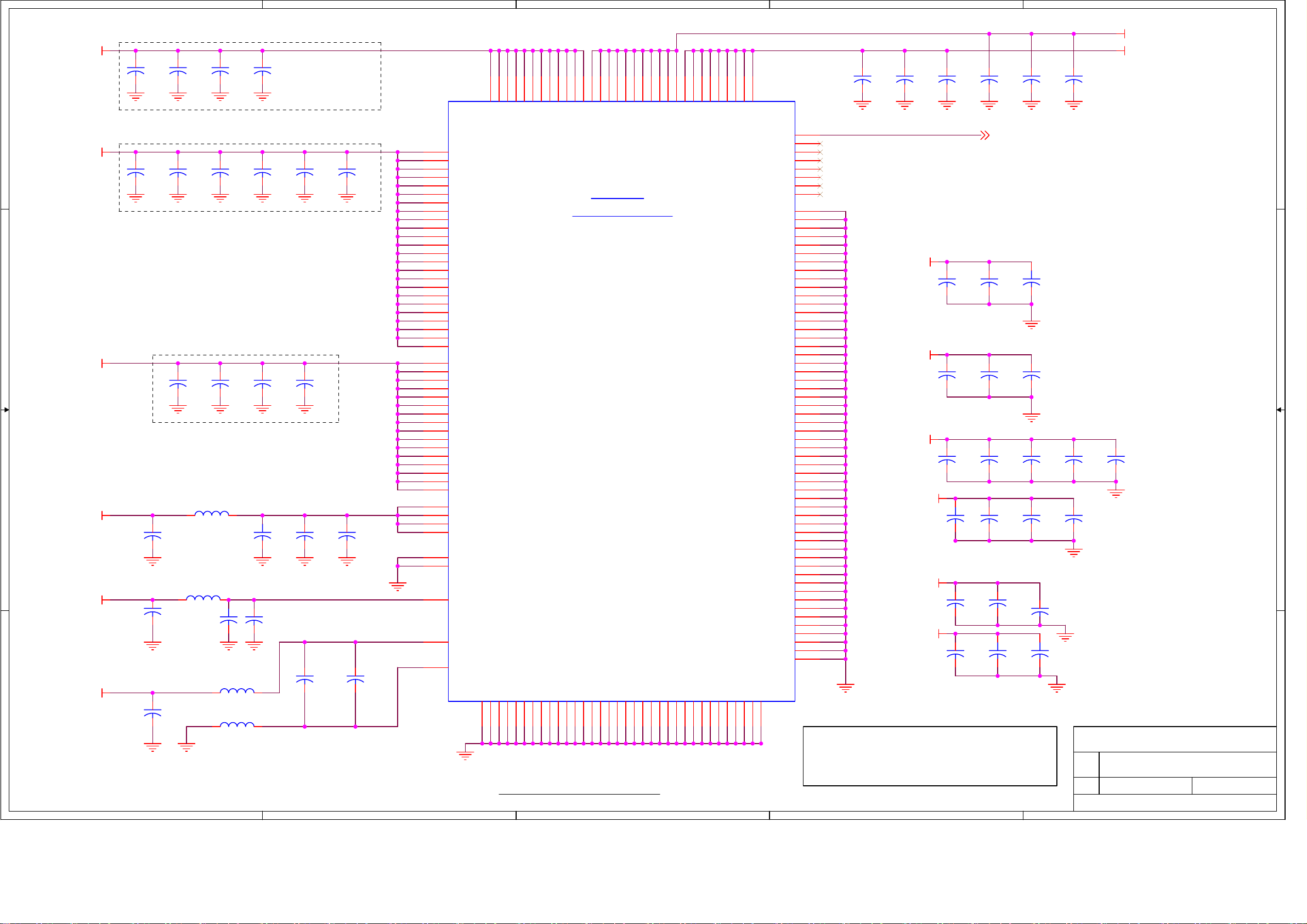

13、PCB LAYOUT

13-1 Image board PCB LAYOUT

62

Page 63

13-2 Audio board PCB LAYOUT

63

Page 64

13-3 Tuner board PCB LAYOUT

13-4 Key board PCB LAYOUT

64

Page 65

DEL

B

A

N

E

n

o

itarepO daeR

-

o

tu

A nO

-rewo

P

TU

O -

3R

.)YLNO

M

6

5

2 gnu

sm

aS rof

(

e

lu

doM

VTD s

no

i

tpO g

niffu

tS

x

e

dnI tee

h

S

t

ee

hS elti

T

- 1

0

e

g

a

P

F

/

I

suB

l

acoL - 20 eg

a

P

F

/I

0

M

AR

D

S

RD

D

- 3

0 e

g

a

P

rotalu

domeD

/

re

nuT - 40

eg

aP

n

I o

id

uA

/ o

ed

iV - 50

eg

aP

F/I

I

MDH

-

60

eg

a

P

st

up

n

I oed

i

V

go

la

n

A -

70

e

gaP

F/I

t

ro

psnarT/redoceD - 80 egaP

e

cafretnI oe

d

i

V - 01 e

g

a

P

e

ca

f

r

e

tn

I

o

i

duA

- 11

e

ga

P

t

e

s

eR

/

O

X

CV /

O

I

S

- 21 e

g

aP

k

c

o

l

B

sOI

P

G

/

de

su

n

U

-

31 egaP

s

r

otc

e

n

n

o

C

GATJ/yt

i

l

i

t

U -

41

e

gaP

1

d

n

G

dna

re

wo

P

-

51

eg

aP

2 d

n

G

dna

r

e

w

o

P - 61

eg

a

P

.gni

t

tes t

luafeD -

*

:eto

N

3

dn

G

dna re

woP -

71

eg

a

P

4

dn

G

dn

a

r

e

wo

P -

81

ega

P

5

d

n

G

d

na

re

wo

P

-

91

eg

aP

noitceleSec

iveD tooB

=

]42,

3

2,2

2[J

kcolc ICP LANR

E

TXE htiw

eciv

ed atad tib-8 B

L mo

rf toob = 111

kcolc I

CP LA

NR

E

TXE htiw ec

ive

d

atad ti

b

-

6

1 BL

mor

f t

o

o

b = 01

1

ecived

z

HK

004

sserdda tib-61

C2

I mor

f

toob = 1

01

ecived

z

HK

001

sserdda t

ib-61 C2I morf

toob

= 001

)z

H

M

72( kcolc IC

P

l

anretni hti

w

eciv

e

d ata

d t

i

b-8 BL

m

o

rf toob = 110

)

z

H

M 72(

kcol

c IC

P lanret

ni htiw ecived ata

d tib-61

BL m

o

rf

t

oob = 010

k

col

c

z

HM 1 ,eci

v

ed atad ti

b-8 /s

s

e

rdda tib

-

42 I

PS morf toob = 100

k

colc zHM 1 ,eciv

ed atad ti

b-8 /sserdda tib

-61 I

PS morf toob = 000

s

noitp

O

r

ep

muJ dra

o

B ytil

itU

)A

)

B

edom GATJE - FFO

- 7

2

J

edom G

ATJ

-

NO

- 72J

)

2

*

.yln

o

dr

a

o

b

D&R r

o

F-

N

I - 8

1P

T-

1P

T

.

ver dra

o

b lani

f roF

-

TU

O

-

81PT-

1P

T

)1

1

SC -

hs

alFatart

S

42U

,0S

C

- hs

alF 32U -

-

3-

2 -

02

J ,NO -

61J

0

S

C - hsalFatartS 42U ,.

c

s

iD S

C - hsalF 32U -- 2-1 - 02J ,FF

O - 61J

)

3

.deretla eb ton

nac stnetnoc y

romem hsalFatartS

42U

- ,

NO - 7

1J

,ed

o

m

61x

ni

ecived hsalFatartS - FFO

- 81J

)

5

.ed

om 8x ni ecived

hsalF

atartS -NO - 81J

)

4

el

ba

T

s

OI

P

G

-

02

eg

a

P

SD

V

L

/ emi

rP

oe

d

i

V -

90

e

g

aP

*

.

IP

S morf

p

u-t

o

o

b la

mr

oN

TUO

-

8R

,N

I -

7R

)

C

.hsa

lf DN

AN morf

pu-tooB NI - 8R ,T

U

O

-7R

)

D

*

TUO - 82

5R ,5

2

5R

.putes

slevel

t

hgilkcaB DCL - N

I - 825

R

,525

R

*

sCAD

9G

rot ferV lanr

o

t

xE

-

-

TUO - 685R

,

485R

,N

I

- 58

5R

,38

5R,94

D

*

s

CA

D 9

G r

ot f

er

V

lanrotnI -- N

I

- 68

5R

,48

5R ,TUO - 58

5R,38

5R,94D

)E

D

ELBA

SID

n

oitare

pO daeR

-ot

uA

nO-rew

oP

TUO

-

3R

*

.)

Y

LNO M652

g

nu

sma

S r

of

(

.elb

ane drac yti

litU 232SR

,N

I - 34

3R ,243R

)

F

.e

lb

a

ne

rotcennoc kniL-G ,TUO - 3

43R ,2

43

R

)de

tats e

s

i

wrehto

ss

elnu

(

:

setoN

.1

.2

.3

.4

%

5

er

a

dna s

m

h

o

ni d

e

t

s

i

l

e

r

a

srot

s

i

s

e

r

l

l

A

)

r

otca

f

m

rof

3

0

6

0

( m

l

iF

lat

eM

,

61

/

1

,

)rotcaf

mrof 306

0(

R7

X

,c

imar

ec

,V

52 ,%

0

1 er

a dn

a

,s

dar

a

f