Page 1

ISP1582

Hi-Speed Universal Serial Bus peripheral controller

Rev. 03 — 25 August 2004 Preliminary data

1. General description

The ISP1582 is a cost-optimized and feature-optimized Hi-Speed Universal Serial

Bus (USB) peripheral controller. It fully complies with

Specification Rev. 2.0

full-speed (12 Mbit/s).

The ISP1582 provides high-speed USB communication capacity to systems based

on microcontrollers or microprocessors. It communicates with a microcontroller or

microprocessor of a system through a high-speed general-purpose parallel interface.

The ISP1582 supports automatic detection of Hi-Speed USB system operation.

Original USB fall-back mode allows thedevice to remain operational under full-speed

conditions. It is designed as a generic USB peripheral controller so that it can fit into

all existing device classes, such as imaging class, mass storage devices,

communication devices, printing devices and human interface devices.

Universal Serial Bus

, supporting data transfer at high-speed (480 Mbit/s) and

The internal generic Direct Memory Access (DMA) block allows easy integration into

data streaming applications.

The modular approach to implementing a USB peripheral controller allows the

designer to select the optimum system microcontroller from the wide variety available.

The ability to reuse existing architecture and firmware investments shortens the

development time, eliminates risk and reduces cost. The result is fast and efficient

development of the most cost-effective USB peripheral solution.

The ISP1582 is ideally suited for many types of peripherals, such as: printers,

scanners, digital still cameras, USB-to-Ethernet links, cable and DSL modems. The

low power consumption during suspend mode allows easy design of equipment that

is compliant to the ACPI™, OnNow™ and USB power management requirements.

The ISP1582 also incorporates features such as SoftConnect™, a reduced

frequency crystal oscillator,andintegrated termination resistors. These features allow

significant cost savings in system design and easy implementation of advanced USB

functionality into PC peripherals.

Page 2

Philips Semiconductors

2. Features

■ Complies fully with:

■ Supports data transfer at high-speed (480 Mbit/s) and full-speed (12 Mbit/s)

■ High performance USB peripheral controller with integrated Serial Interface

■ Automatic Hi-Speed USB mode detection and Original USB fall-back mode

■ Supports sharing mode

■ Supports V

■ High-speed DMA interface

■ Fully autonomous and multiconfiguration DMA operation

■ 7 IN endpoints, 7 OUT endpoints and a fixed control IN/OUT endpoint

■ Integrated physical 8 kbytes of multiconfiguration FIFO memory

■ Endpoints with double buffering to increase throughput and ease real-time data

■ Bus-independent interface with most microcontrollers and microprocessors

■ 12 MHz crystal oscillator with integrated PLL for low EMI

■ Software-controlled connection to the USB bus (SoftConnect™)

■ Low-power consumption in operation and power-down modes; suitable for use in

■ Supports Session Request Protocol (SRP) that complies with

■ Internal power-on and low-voltage reset circuits; also supports software reset

■ Operation over the extended USB bus voltage range (DP, DM and V

■ 5 V tolerant I/O pads at 3.3 V

■ Operating temperature range from −40 °C to +85 °C

■ Available in HVQFN56 halogen-free and lead-free package.

ISP1582

Hi-Speed USB peripheral controller

◆

Universal Serial Bus Specification Rev. 2.0

◆ Most Device Class specifications

◆ ACPI™, OnNow™ and USB power management requirements.

Engine (SIE), Parallel Interface Engine (PIE), FIFO memory and data transceiver

sensing

BUS

transfer

bus-powered USB devices

On-The-Go

Supplement to the USB Specification Rev. 1.0a

)

BUS

3. Applications

■ Personal digital assistant

■ Digital video camera

■ Digital still camera

■ 3G mobile phone

■ MP3 player

■ Communication device, for example: router and modem

■ Printer

■ Scanner.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 2 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 3

Philips Semiconductors

4. Abbreviations

DMA — Direct Memory Access

EMI — ElectroMagnetic Interference

FS — Full-speed

GDMA — Generic DMA

HS — High-speed

MMU — Memory Management Unit

NRZI — Non-Return-to-Zero Inverted

OTG — On-The-Go

PDA — Personal Digital Assistant

PID — Packet IDentifier

PIE — Parallel Interface Engine

PIO — Parallel Input/Output

PLL — Phase-Locked Loop

SE0 — Single-Ended zero

SIE — Serial Interface Engine

SRP — Session Request Protocol

USB — Universal Serial Bus.

ISP1582

Hi-Speed USB peripheral controller

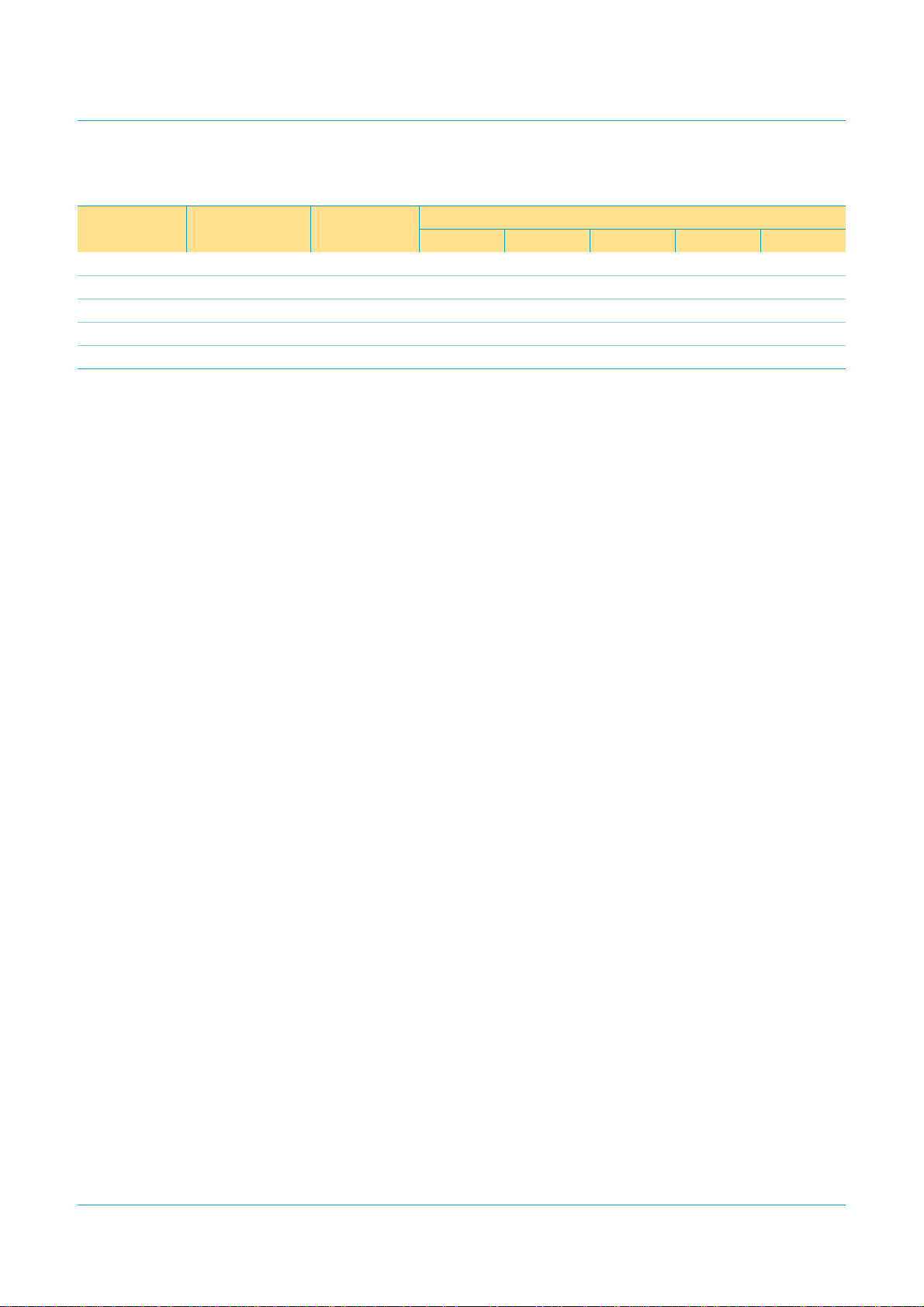

5. Ordering information

Table 1: Ordering information

Type

number

ISP1582BS HVQFN56 plastic thermal enhanced very thin quad flat package;

Package

Name Description Version

SOT684-1

no leads; 56 terminals; body 8 × 8 × 0.85 mm

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 3 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 4

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 4 of 66

xxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx x xxxxxxxxxxxxxx xxxxxxxxxx xxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxx

xxxxx xxxxxx xx xxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxx xxxxxxx xxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxx xxxxxxxxxxxxxx xxxxxx xx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxx xxxxx x x

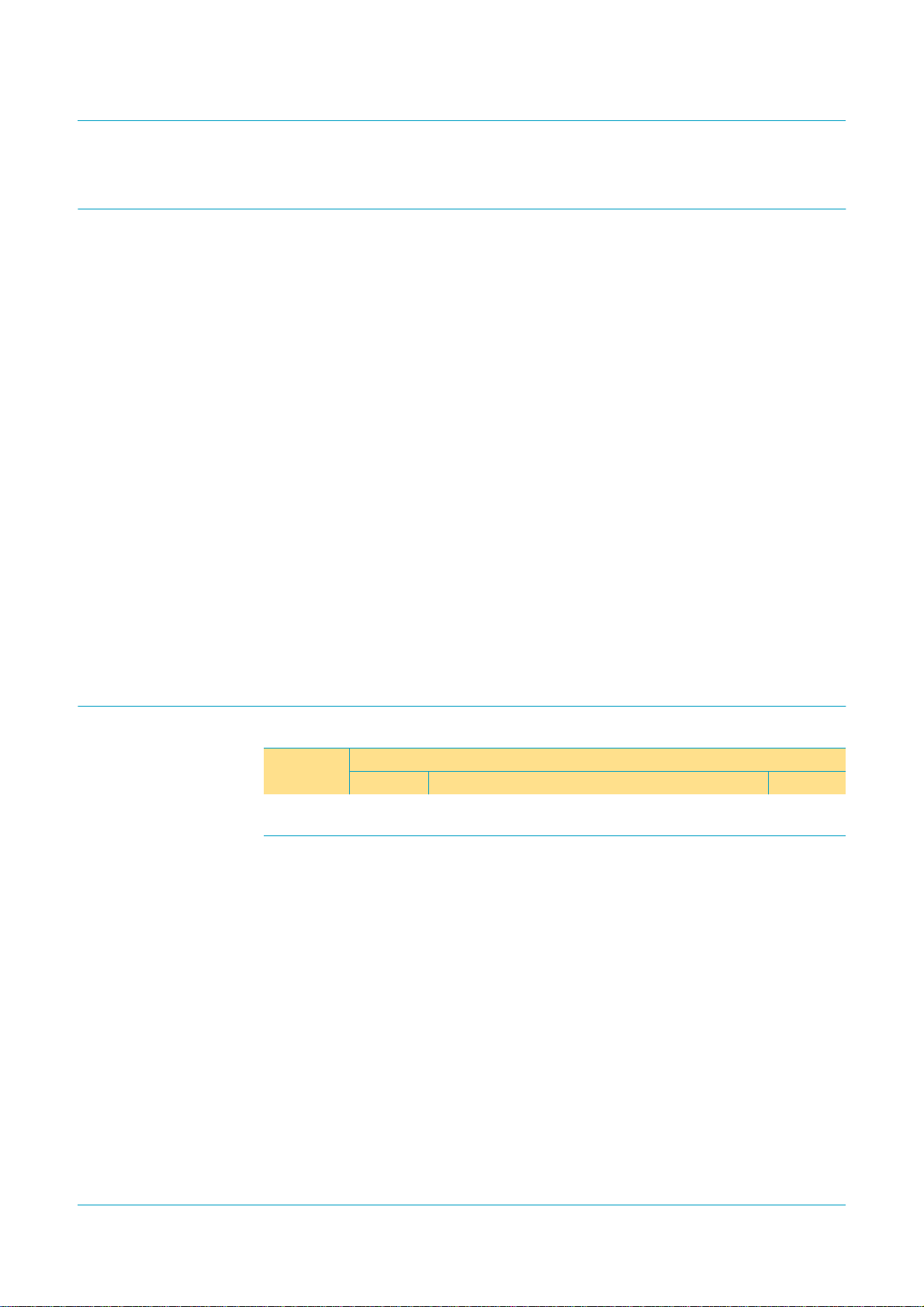

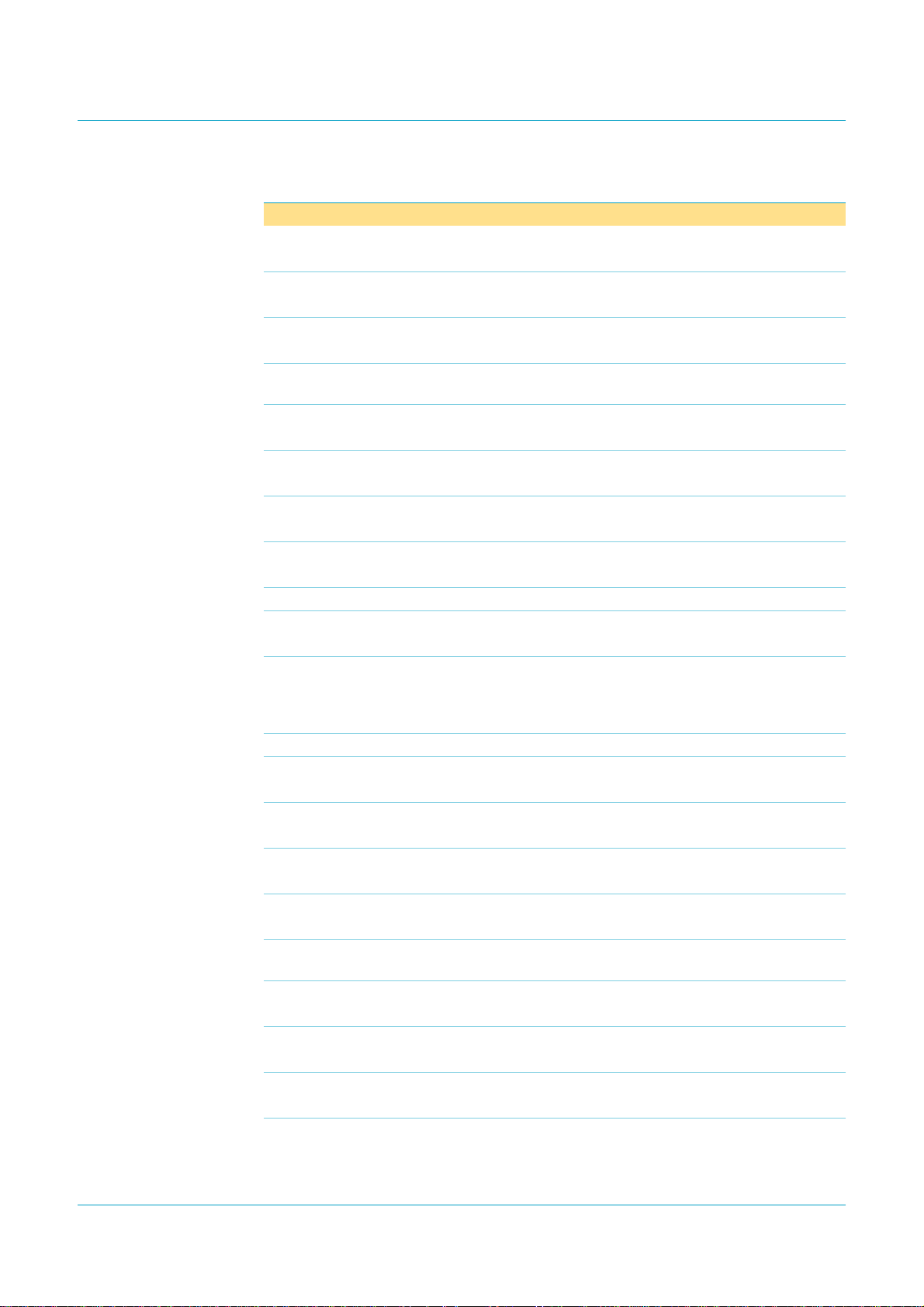

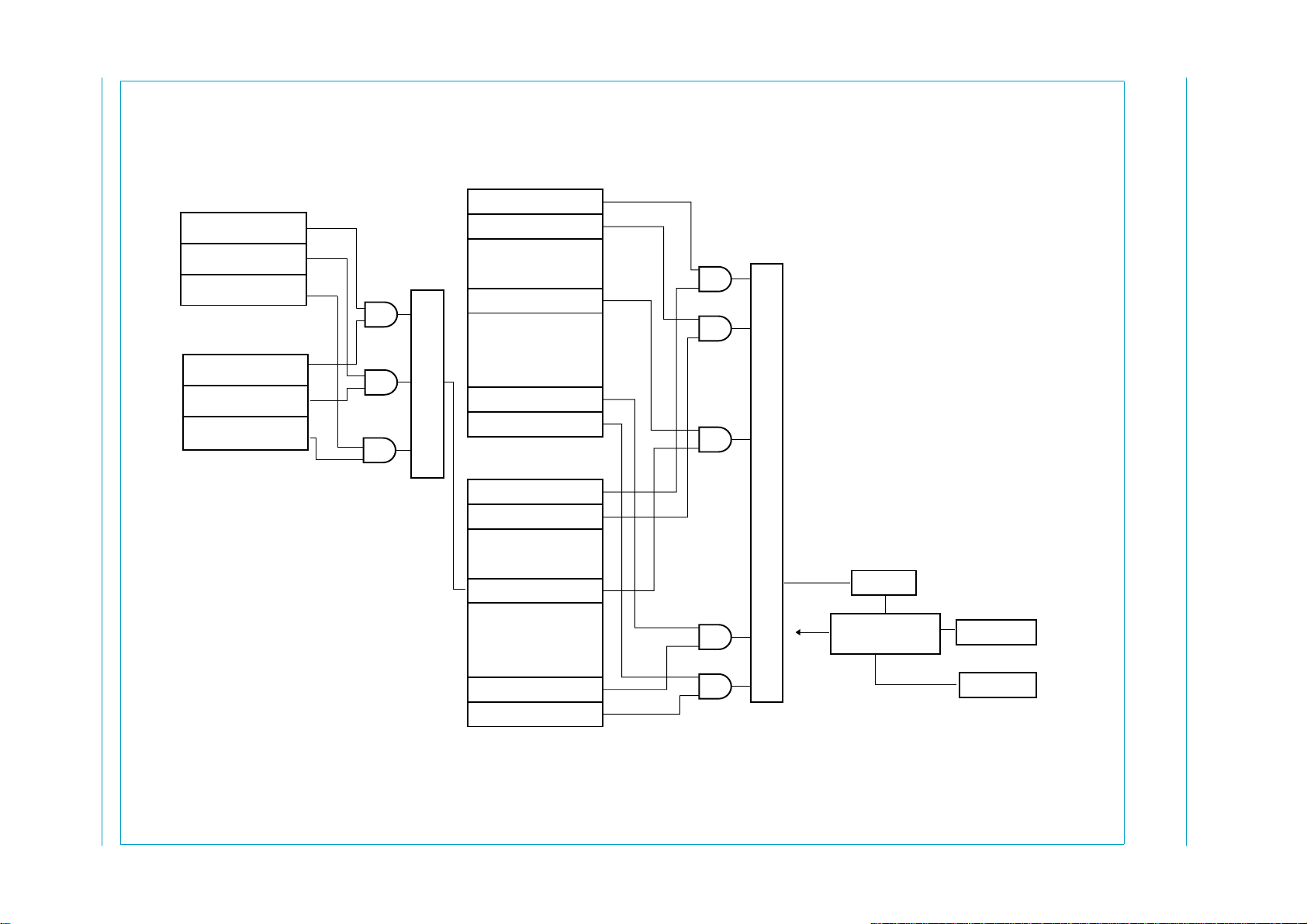

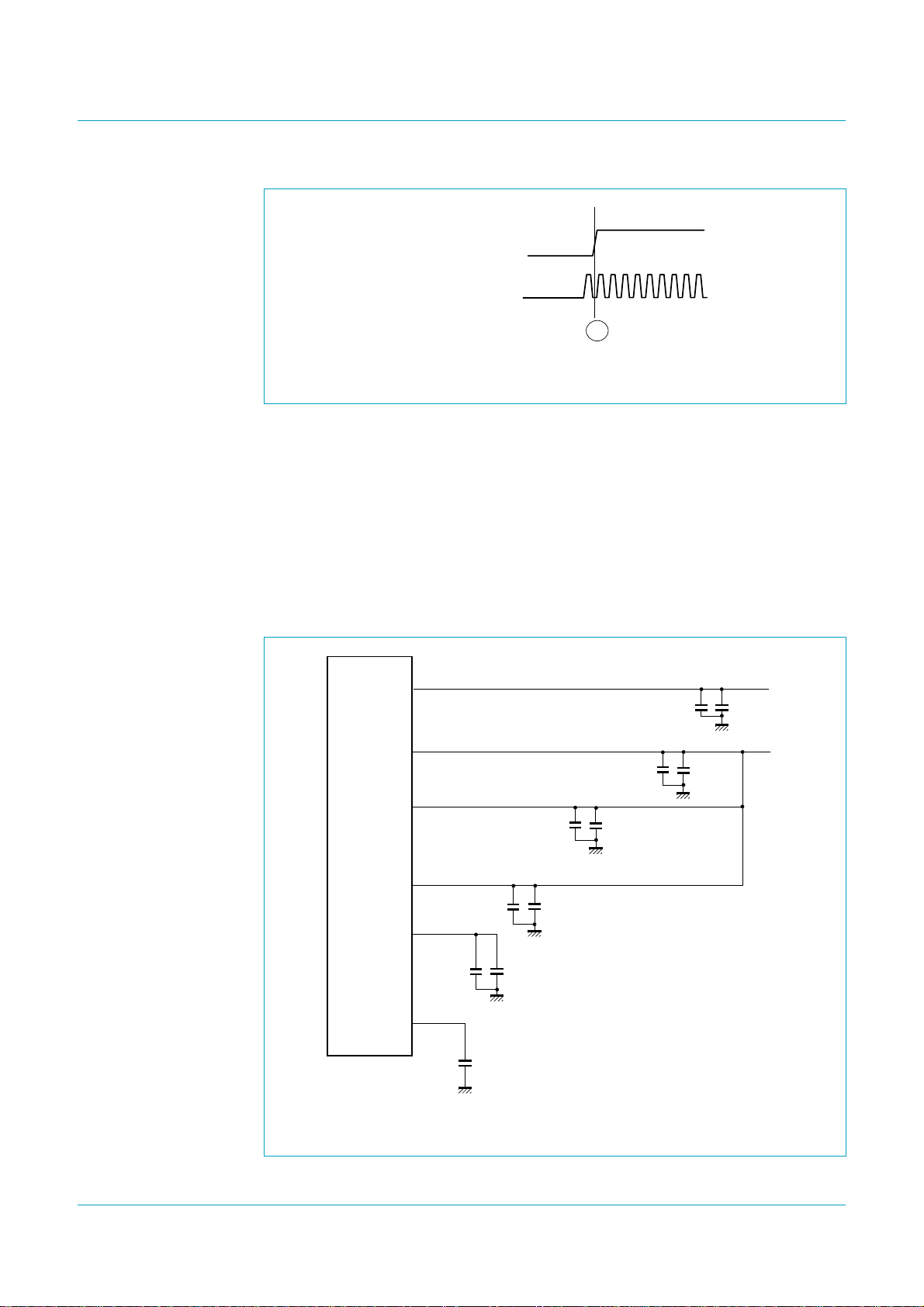

6. Block diagram

Philips Semiconductors

3.3 V

1.5

kΩ

RREF

12.0

kΩ

RESET_N

V

CC

RPU

2

6

7

53, 54

3.3 V

to/from USB

HI-SPEED USB

TRANSCEIVER

POWER-ON

RESET

analog supply

VOLT AGE

REGULATORS

13, 26,

29, 41

12 MHz

DMDP

43495251

V

BUS

XTAL2XTAL1

ISP1582

SoftConnect

MEMORY

MANAGEMENT

UNIT

INTEGRATED

RAM

(8 KBYTES)

I/O pad

supply

21, 34, 4828, 50

V

CC(I/O)

1, 5

V

CC(1V8)

internal

reset

digital

supply

PHILIPS

SIE/PIE

SYSTEM

CONTROLLER

SUSPEND WAKEUPAGNDDGND

5556

DMA

HANDLER

DMA

REGISTERS

MICRO-

CONTROLLER

HANDLER

OTG SRP

MODULE

DREQ DIOR

DACK

9101112

INTERFACE

CONTROLLER

INTERFACE

DIOW

DMA

MICRO-

30 to 33,

35 to 40,

42 to 47

18 to 20,

22 to 25,

27

15

16

17

14

004aaa199

8

EOT

16

8

DATA[15:0

A[7:0

CS_N

RD_N

WR_N

INT

]

]

Fig 1. Block diagram.

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Hi-Speed USB peripheral controller

ISP1582

Page 5

Philips Semiconductors

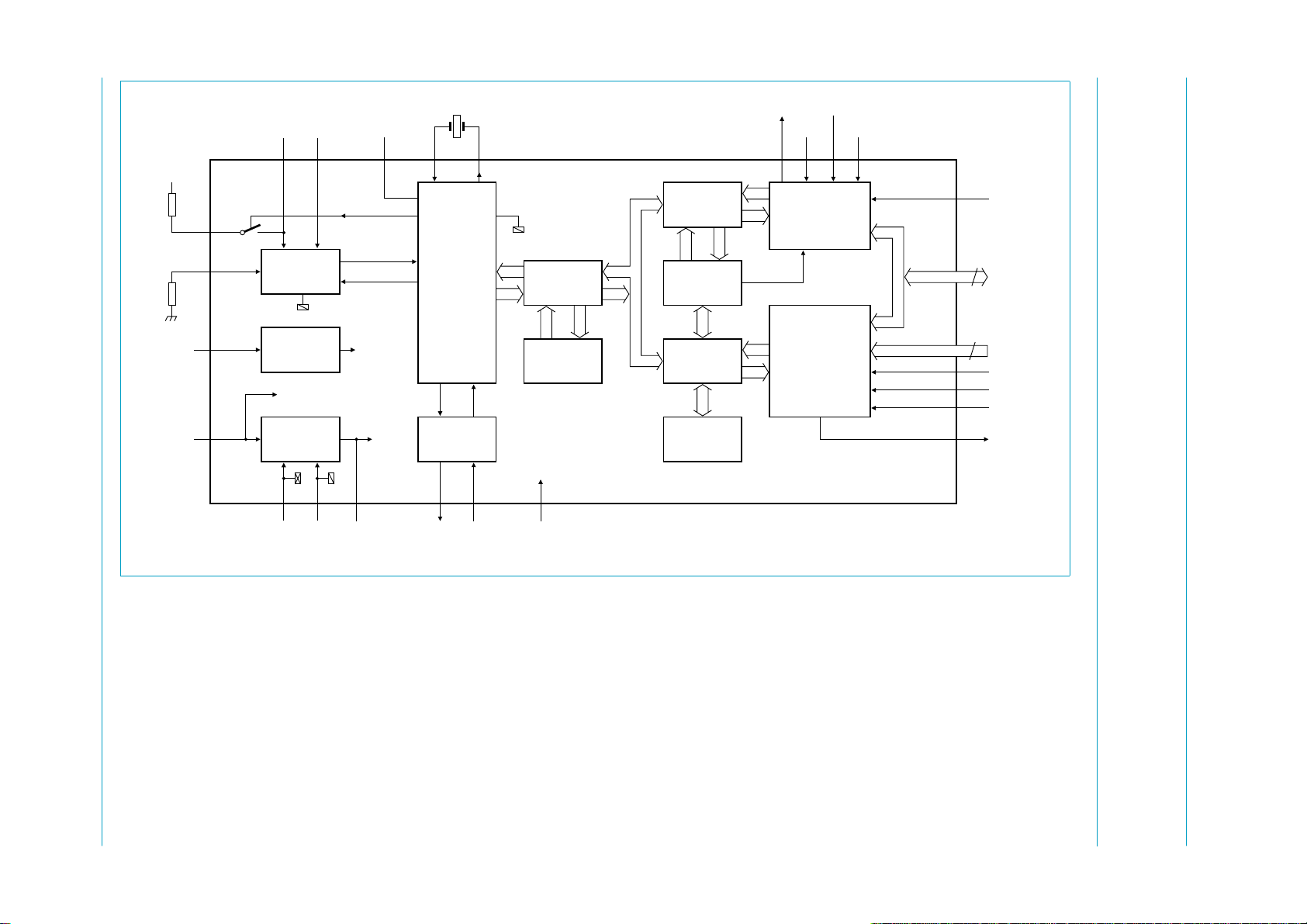

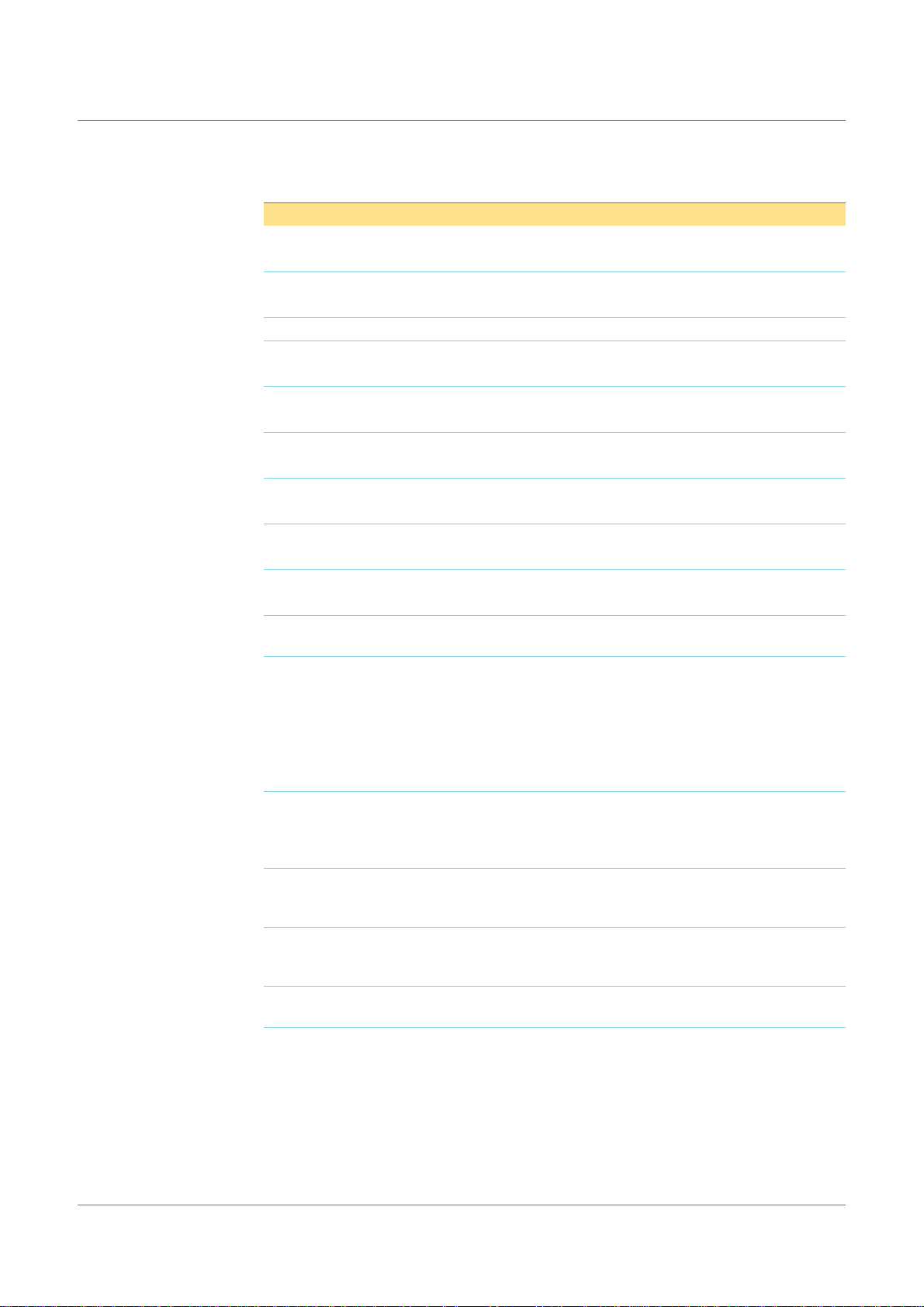

7. Pinning information

7.1 Pinning

AGND

RPU

DP

DM

AGND

RREF

RESET_N

EOT

DREQ

DACK

DIOR

DIOW

DGND

INT

Hi-Speed USB peripheral controller

BUS

CC(1V8)

CC

CC

XTAL1

V

52

ISP1582BS

19

A1

A0

XTAL2

515349

20

A2

V

WAKEUP

SUSPEND

54

55

56

1 42

2

3

4

5

6

7

8

9

10

11

12

13

14

171518

16

CS_N

RD_N

WR_N

V

V

50

21

A3

CC(I/O)

V

22

CC(I/O)

V

DATA15

474648

24

23

A5

A4

DATA14

DATA13

45

26

25

A6

DGND

DATA12

DATA11

43

44

28

27

A7

CC(1V8)

V

41

40

39

38

37

36

35

34

33

32

31

30

29

ISP1582

DATA10

DGND

DATA9

DATA8

DATA7

DATA6

DATA5

DATA4

V

CC(I/O)

DATA3

DATA2

DATA1

DATA0

DGND

004aaa536

Fig 2. Pin configuration HVQFN56 (top view).

CC(I/O)

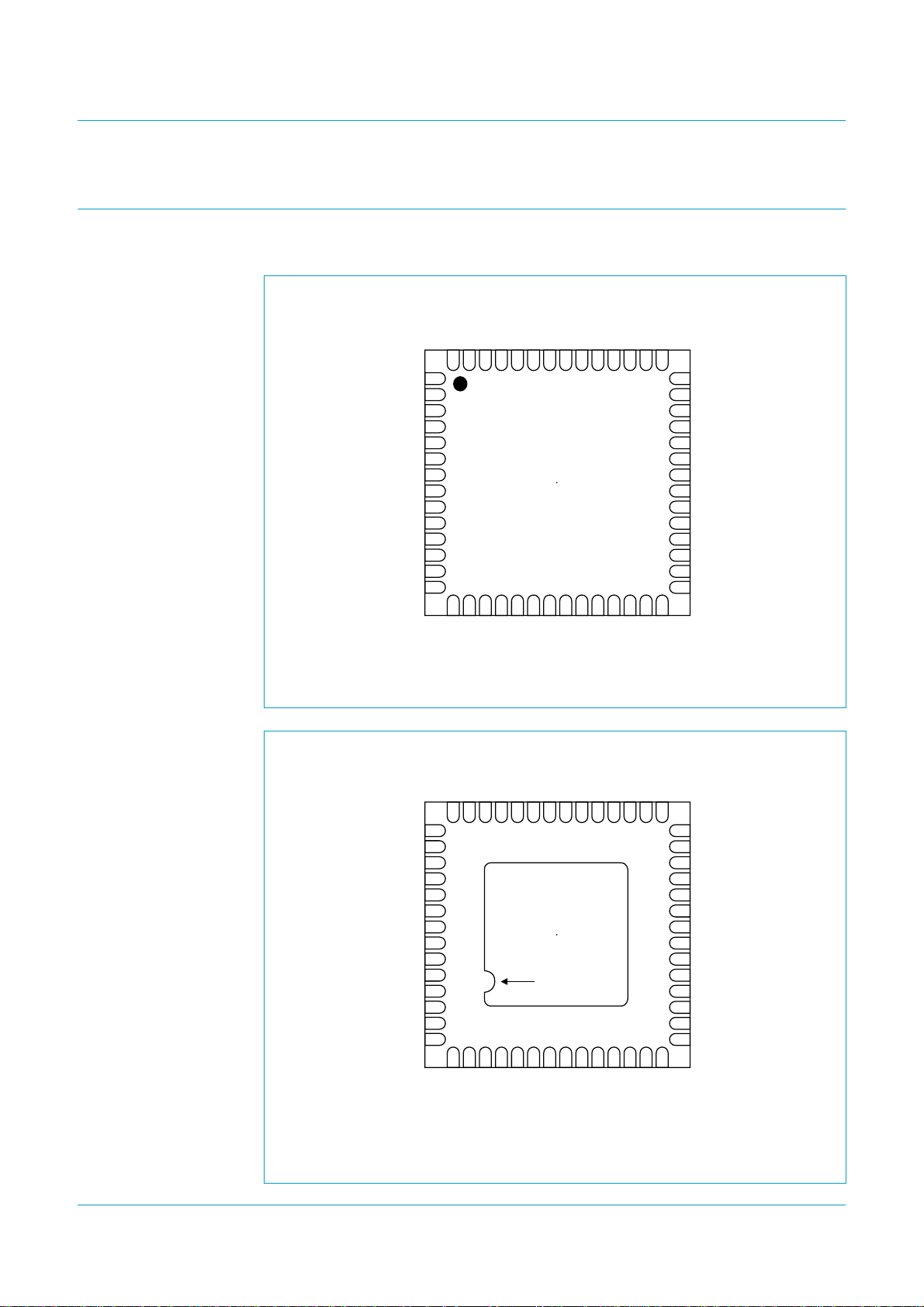

A1

A2

A0

V

201822

21

19

GND (exposed die pad)

ISP1582BS

terminal 1

50

52

51

CC

CC

V

XTAL1

XTAL2

CC(1V8)

V

INT

DGND

DIOW

DIOR

DACK

DREQ

EOT

RESET_N

RREF

AGND

DM

DP

RPU

AGND

Bottom View

CS_N

WR_N

RD_N

17

16

15

14 29

13

12

11

10

9

8

7

6

5

4

3

2

1

545653

55

V

WAKEUP

SUSPEND

A3

49

BUS

V

A5

A4

242523

47

48

CC(I/O)

DATA15

V

A6

DGND

26

45

46

DATA13

DATA14

CC(1V8)

A7

V

28

27

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

DATA11

DATA12

DGND

DATA0

DATA1

DATA2

DATA3

V

CC(I/O)

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DGND

DATA10

004aaa377

Fig 3. Pin configuration HVQFN56 (bottom view).

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 5 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 6

Philips Semiconductors

7.2 Pin description

Table 2: Pin description

Symbol

AGND 1 - analog ground

RPU 2 A connect to the external pull-up resistor for pin DP; must be

DP 3 A USB D+ line connection (analog)

DM 4 A USB D− line connection (analog)

AGND 5 - analog ground

RREF 6 A connect to the external bias resistor; must be connected to

RESET_N 7 I reset input (500 µs); a LOW levelproducesanasynchronous

EOT 8 I End-of-transfer input (programmable polarity); used in DMA

DREQ 9 O DMA request (programmable polarity) output; when not in

DACK 10 I DMA acknowledge input (programmable polarity); when not

DIOR 11 I DMA read strobe input (programmable polarity); when not in

DIOW 12 I DMA write strobe input (programmable polarity); when not in

DGND 13 - digital ground

INT 14 O interrupt output; programmable polarity (active HIGH or

CS_N 15 I chip select input

RD_N 16 I read strobe input

WR_N 17 I write strobe input

[1]

Pin Type

ISP1582

Hi-Speed USB peripheral controller

[2]

Description

connected to 3.3 V via a 1.5 kΩ resistor

ground via a 12.0 kΩ±1 % resistor

reset; connect to V

circuit)

TTL; 5 V tolerant

slavemodeonly; when not in use, connect this pin to V

through a 10 kΩ resistor

input pad; TTL; 5 V tolerant

use, connect this pin to ground through a 10 kΩ resistor; see

Table 54 and Table 55

TTL; 4 ns slew-rate control

in use, connect this pin to V

see Table 54 and Table 55

TTL; 5 V tolerant

use, connect this pin to V

Table 54 and Table 55

TTL; 5 V tolerant

use, connect this pin to V

Table 54 and Table 55

TTL; 5 V tolerant

LOW) and signaling (edge or level triggered)

CMOS output; 8 mA drive

input pad; TTL; 5 V tolerant

input pad; TTL; 5 V tolerant

input pad; TTL; 5 V tolerant

for the power-on reset (internal POR

CC

through a 10 kΩ resistor;

CC(I/O)

through a 10 kΩ resistor; see

CC(I/O)

through a 10 kΩ resistor; see

CC(I/O)

CC(I/O)

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 6 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 7

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 2: Pin description

Symbol

[1]

Pin Type

…continued

[2]

Description

A0 18 I bit 0 of the address bus

input pad; TTL; 5 V tolerant

A1 19 I bit 1 of the address bus

input pad; TTL; 5 V tolerant

A2 20 I bit 2 of the address bus

input pad; TTL; 5 V tolerant

[3]

V

CC(I/O)

21 - supply voltage; used to supply voltage to the I/O pads; see

Section 8.14

A3 22 I bit 3 of the address bus

input pad; TTL; 5 V tolerant

A4 23 I bit 4 of the address bus

input pad; TTL; 5 V tolerant

A5 24 I bit 5 of the address bus

input pad; TTL; 5 V tolerant

A6 25 I bit 6 of the address bus

input pad; TTL; 5 V tolerant

DGND 26 - digital ground

A7 27 I bit 7 of the address bus

input pad; TTL; 5 V tolerant

[3]

V

CC(1V8)

28 - regulator output voltage (1.8 V ± 0.15 V); tapped out voltage

from the internal regulator; this regulated voltage cannot

drive external devices; decouple this pin using a 0.1 µF

capacitor; see Section 8.14

DGND 29 - digital ground

DATA0 30 I/O bit0 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA1 31 I/O bit1 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA2 32 I/O bit2 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA3 33 I/O bit3 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

[3]

V

CC(I/O)

34 - supply voltage; used to supply voltage to the I/O pads; see

Section 8.14

DATA4 35 I/O bit4 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA5 36 I/O bit5 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA6 37 I/O bit6 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA7 38 I/O bit7 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 7 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 8

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 2: Pin description

Symbol

[1]

Pin Type

…continued

[2]

Description

DATA8 39 I/O bit8 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA9 40 I/O bit9 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DGND 41 - digital ground

DATA10 42 I/O bit10 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA11 43 I/O bit11 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA12 44 I/O bit12 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA13 45 I/O bit13 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA14 46 I/O bit14 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

DATA15 47 I/O bit15 of bidirectional data bus

bidirectional pad; 4 ns slew-rate control; TTL; 5 V tolerant

[3]

V

CC(I/O)

48 - supply voltage; used to supply voltage to the I/O pads; see

Section 8.14

V

BUS

49 A USB bus power pin sensing input; used to detect whether

the host is connected or not; it is an output for V

in OTG mode; when V

is not detected, pin RPU is

BUS

BUS

pulsing

internally disconnected from pin DP in approximately 4 ns;

connect a 1 µF electrolytic capacitor and a 1 MΩ pull-down

resistor to ground; see Section 8.12

5 V tolerant

[3]

V

CC(1V8)

50 - regulator output voltage (1.8 V ± 0.15 V); tapped out voltage

from the internal regulator; this regulated voltage can drive

external devices up to 1 mA; decouple this pin using 4.7 µF

and 0.1 µF capacitors; see Section 8.14

XTAL2 51 O crystal oscillator output (12 MHz); connect a fundamental

parallel-resonant crystal; leave this pin open-circuit when

using an external clock source on pin XTAL1; see Table 83

XTAL1 52 I crystal oscillator input (12 MHz); connect a fundamental

parallel-resonant crystal or an external clock source (leaving

pin XTAL2 unconnected); see Table 83

[3]

V

CC

53 - supply voltage (3.3 V ± 0.3 V); this pin supplies the internal

voltage regulator and the analog circuit; see Section 8.14

[3]

V

CC

54 - supply voltage (3.3 V ± 0.3 V); this pin supplies the internal

voltage regulator and the analog circuit; see Section 8.14

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 8 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 9

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 2: Pin description

Symbol

[1]

Pin Type

…continued

[2]

Description

WAKEUP 55 I wake-up input; when this pin is at the HIGH level, the chip is

prevented from getting into the suspend state and the chip

wakes up from the suspend state; when not in use, connect

this pin to ground through a 10 kΩ resistor

input pad; TTL; 5 V tolerant

SUSPEND 56 O suspend state indicator output; used as a power switch

control output for powered-off application or as a resume

signal to the CPU for powered-on application

CMOS output; 8 mA drive

GND exposed

die pad

[1] Symbol names ending with underscore N (for example, NAME_N) represent active LOW signals.

[2] All outputs and I/O pins can source 4 mA.

[3] Add a decoupling capacitor (0.1 µF) to all the supply pins. For better EMI results, add a 0.01 µF

capacitor in parallel to the 0.1 µF.

- ground supply; down bonded to the exposed die pad

(heatsink); to be connected to DGND during PCB layout

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 9 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 10

Philips Semiconductors

8. Functional description

The ISP1582 is a high-speed USB peripheral controller. It implements the Hi-Speed

USB or the Original USB physical layer and the packet protocol layer. It maintains up

to 16 USB endpoints concurrently (control IN and control OUT, 7 IN and 7 OUT

configurable) along with endpoint EP0 setup, which accesses the setup buffer. The

USB Chapter 9 protocol handling is executed by means of external firmware.

For high-bandwidth data transfer, the integrated DMA handler can be invoked to

transfer data to or from external memory or devices. The DMA interface can be

configured by writing to the proper DMA registers (see Section 9.4).

The ISP1582 supports Hi-Speed USB and Original USB signaling. The USB

signaling speed is automatically detected.

The ISP1582 has 8 kbytes of internal FIFO memory, which is shared among the

enabled USB endpoints.

There are 7 IN endpoints, 7 OUT endpoints and 2 control endpoints that are a fixed

64 bytes long. Any of the 7 IN and 7 OUT endpoints can be separately enabled or

disabled. The endpoint type (interrupt, isochronous or bulk) and packet size of these

endpoints can be individually configured depending on the requirements of the

application. Optional double buffering increases the data throughput of these data

endpoints.

ISP1582

Hi-Speed USB peripheral controller

The ISP1582 requires 3.3 V power supply. It has 5 V tolerant I/O pads when

operating at V

transceiver.

The ISP1582 operates on a 12 MHz crystal oscillator. An integrated 40× PLL clock

multiplier generates the internal sampling clock of 480 MHz.

= 3.3 V and an internal 1.8 V regulator for powering the analog

CC(I/O)

8.1 DMA interface, DMA handler and DMA registers

The DMA block can be subdivided into two blocks: the DMA handler and the DMA

interface.

The firmware writes to the DMA command register to start a DMA transfer (see

Table 47). The command opcode determines whether a generic DMA or PIO transfer

will start. The handler interfaces to the same FIFO (internal RAM) as used by the

USB core. On receiving the DMA command, the DMA handler directs the data from

the endpoint FIFO to the external DMA device or from the external DMA device to the

endpoint FIFO.

The DMA interface configures the timing and the DMA handshake. Data can be

transferred using either the DIOR and DIOW strobes or by the DACK and DREQ

handshakes. The DMA configurations are set up by writing to the DMA Configuration

register (see Table 52 and Table 53).

For a generic DMA interface, Generic DMA (GDMA) slave mode can be used.

Remark: The DMA endpoint buffer length must be a multiple of 4 bytes.

For details on DMA registers, see Section 9.4.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 10 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 11

Philips Semiconductors

8.2 Hi-Speed USB transceiver

The analog transceiver directly interfaces to the USB cable through integrated

termination resistors. The high-speed transceiver requires an external resistor

(12.0 kΩ±1 %) between pin RREF and ground to ensure an accurate current mirror

that generates the Hi-Speed USB current drive. A full-speed transceiver is integrated

as well. This makes the ISP1582 compliant to Hi-Speed USB and Original USB,

supporting both the high-speed and full-speed physical layers. After automatic speed

detection, the Philips Serial Interface Engine (SIE) sets the transceiver to use either

high-speed or full-speed signaling.

8.3 MMU and integrated RAM

The Memory Management Unit (MMU) and the integrated RAM provide the

conversion between the USB speed (full-speed: 12 Mbit/s, high-speed: 480 Mbit/s)

and the microcontroller handler or the DMA handler. The data from the USB bus is

stored in the integrated RAM, which is cleared only when the microcontroller has read

or written all data from or to the corresponding endpoint buffer or when the DMA

handler has read or written all data from or to the endpoint buffer. The OUT endpoint

buffer can also be cleared forcibly by setting bit CLBUF in the Control Function

register. A total of 8 kbytes RAM is available for buffering.

ISP1582

Hi-Speed USB peripheral controller

8.4 Microcontroller interface and microcontroller handler

The microcontroller handler allows the external microcontroller or microprocessor to

access the register set in the Philips SIE as well as the DMA handler. The

initialization of the DMA configuration is done through the microcontroller handler.

8.5 OTG SRP module

The OTG supplement defines a Session Request Protocol (SRP), which allows a

B-device to request the A-device to turn on V

allows the A-device, which may be battery-powered, to conserve power by turning off

V

when there is no bus activity while still providing a means for the B-device to

BUS

initiate bus activity.

Any A-device, including a PC or laptop, can respond to SRP. Any B-device, including

a standard USB peripheral, can initiate SRP.

The ISP1582 is a device that can initiate SRP.

and start a session. This protocol

BUS

8.6 Philips high-speed transceiver

8.6.1 Philips Parallel Interface Engine (PIE)

In the high-speed (HS) transceiver, the Philips PIE interface uses a 16-bit parallel

bidirectional data interface. The functions of the HS module also include bit-stuffing or

destuffing and Non-Return-to-Zero Inverted (NRZI) encoding or decoding logic.

8.6.2 Peripheral circuit

To maintain a constant current driver for HS transmit circuits and to bias other analog

circuits, an internal band gap reference circuit and an RREF resistor form the

reference current. This circuit requires an external precision resistor (12.0 kΩ±1%)

connected to the analog ground.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 11 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 12

Philips Semiconductors

8.6.3 HS detection

The ISP1582 handles more than one electrical state—full-speed (FS) or high-speed

(HS)—under the USB specification. When the USB cable is connected from the

peripheral to the host controller, the ISP1582 defaults to the FS state until it sees a

bus reset from the host controller.

During the bus reset, the peripheral initiates an HS chirp to detect whether the host

controller supports Hi-Speed USB or Original USB. Chirping must be done with the

pull-up resistor connected and the internal termination resistors disabled. If the HS

handshake shows that there is an HS host connected, then the ISP1582 switches to

the HS state.

In the HS state, the ISP1582 should observe the bus for periodic activity. If the bus

remains inactive for 3 ms, the peripheral switches to the FS state to check for a

Single-Ended Zero (SE0) condition on the USB bus. If an SE0 condition is detected

for the designated time (100 µs to 875 µs; refer to section 7.1.7.6 of the USB

specification Rev. 2.0), the ISP1582 switches to the HS chirp state to perform an HS

detection handshake. Otherwise, the ISP1582 remains in the FS state adhering to the

bus-suspend specification.

ISP1582

Hi-Speed USB peripheral controller

8.7 Philips Serial Interface Engine (SIE)

The Philips SIE implements the full USB protocol layer. It is completely hardwired for

speed and needs no firmware intervention. The functions of this block include:

synchronization pattern recognition, parallel or serial conversion, bit (de)stuffing,

CRC checking or generation, Packet IDentifier (PID) verification or generation,

address recognition, handshake evaluation or generation.

8.8 SoftConnect

The connection to the USB is established by pulling pin DP (for full-speed devices)

HIGH through a 1.5 kΩ pull-up resistor. In the ISP1582, an external 1.5 kΩ pull-up

resistor must be connected between pin RPU and 3.3 V. Pin RPU connects the

pull-up resistor to pin DP, when bit SOFTCT in the Mode register is set (see Table 20

and Table 21). After a hardware reset, the pull-up resistor is disconnected by default

(bit SOFTCT = 0). The USB bus reset does not change the value of bit SOFTCT.

When the V

the back-drive voltage.

is not present, the SOFTCT bit must be set to logic 0 to comply with

BUS

8.9 System controller

The system controller implements the USB power-down capabilities of the ISP1582.

Registers are protected against data corruption during wake-up following a resume

(from the suspend state) by locking the write access until an unlock code has been

written in the Unlock Device register (see Table 73 and Table 74).

8.10 Output pins status

Table 3 illustrates the behavior of output pins when V

various operating conditions.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 12 of 66

is supplied with VCC in

CC(I/O)

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 13

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 3: ISP1582 pin status

V

CC

0V V

0V V

0V−> 3.3 V V

3.3 V V

3.3 V V

[1] X: Don’t care.

[2] Dead: The USB cable is plugged-out and V

[3] Plug-out: The USB cable is not present but V

[4] Plug-in: The USB cable is being plugged-in and V

V

CC(I/O)

CC

CC

CC

CC

CC

[1]

State Pin

[2]

dead

plug-out

plug-in

[3]

[4]

reset LOW HIGH LOW high-Z high-Z

normal HIGH HIGH LOW high-Z high-Z

CC(I/O)

CC(I/O)

8.11 Interrupt

8.11.1 Interrupt output pin

The Interrupt Configuration register of the ISP1582 controls the behavior of the INT

output pin. The polarity and signaling mode of pin INT can be programmed by setting

bits INTPOL and INTLVL of the Interrupt Configuration register (R/W: 10h); see

Table 24. Bit GLINTENA of the Mode register (R/W: OCh) is used to enable pin INT.

Default settings after reset are active LOW and level mode. When pulse mode is

selected, a pulse of 60 ns is generated when the OR-ed combination of all interrupt

bits changes from logic 0 to logic 1.

RESET_N INT_N SUSPEND DREQ DATA[15:0]

XXXXX

X LOW HIGH high-Z input

X LOW HIGH high-Z high-Z

is not available.

is available.

is available.

CC(I/O)

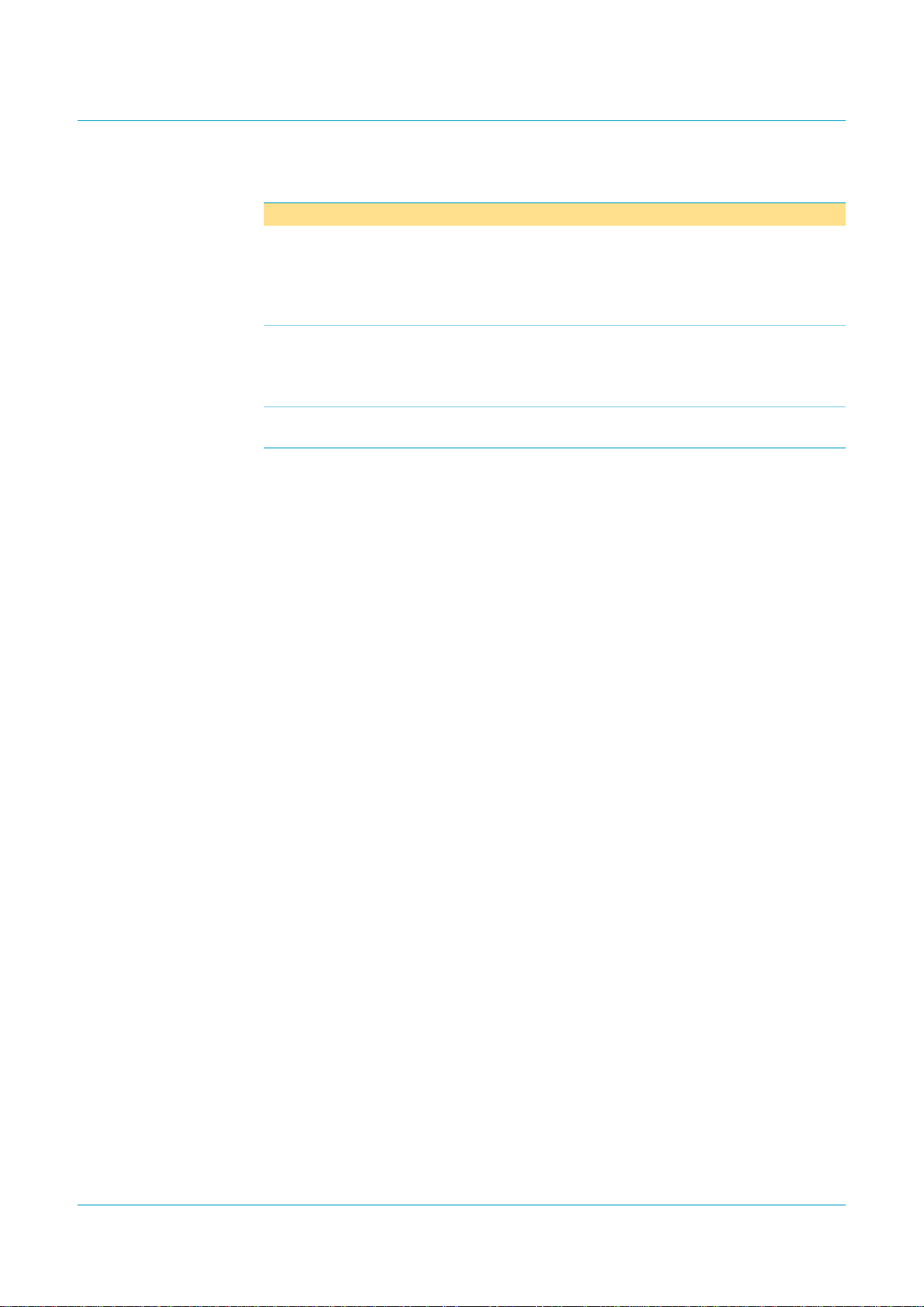

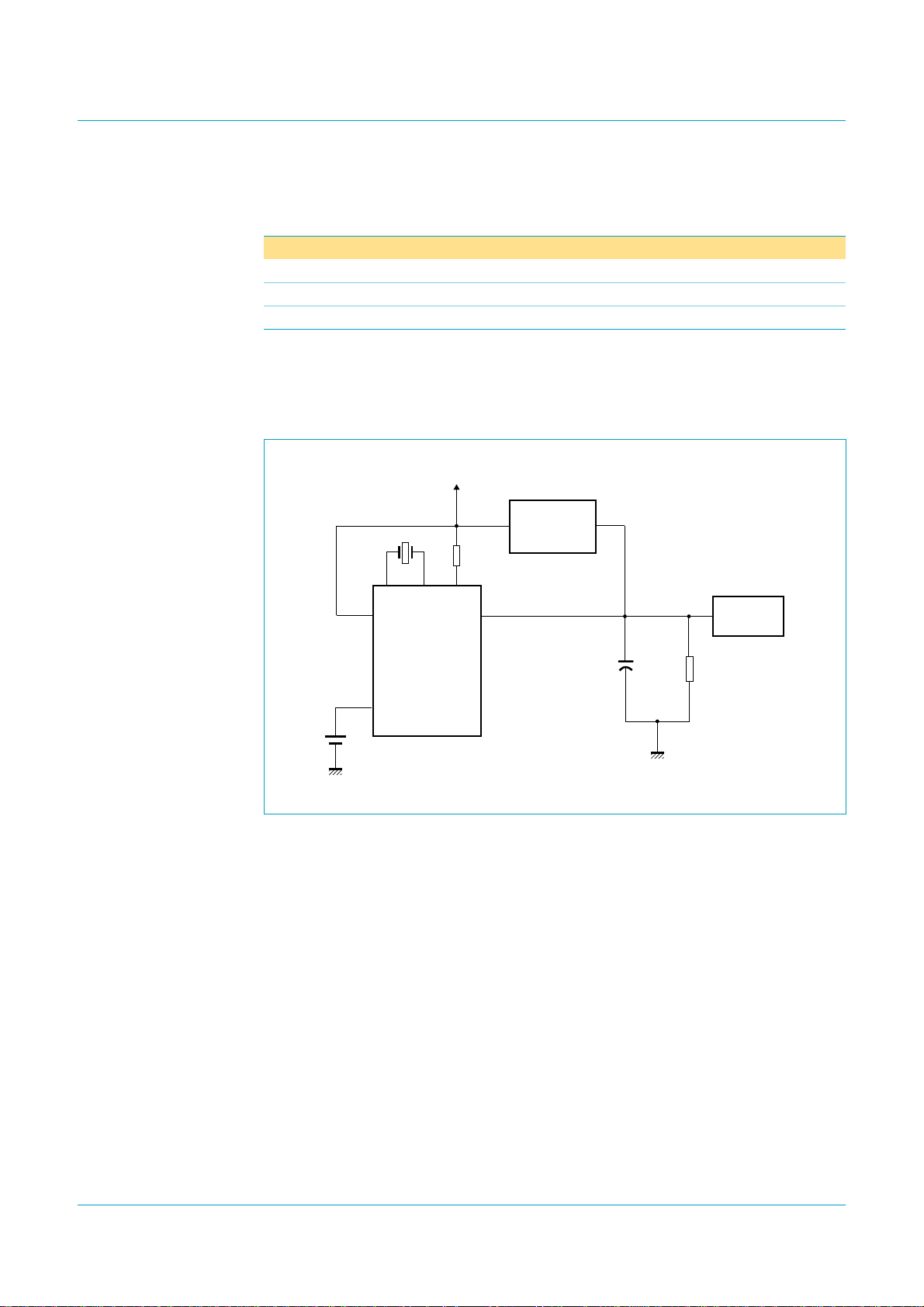

Figure 4 shows the relationship between the interrupt events and pin INT.

Each of the indicated USB and DMA events is logged in a status bit of the Interrupt

register and the DMA Interrupt Reason register, respectively. Corresponding bits in

the Interrupt Enable register and the DMA Interrupt Enable register determine

whether or not an event will generate an interrupt.

Interrupts can be masked globally by means of bit GLINTENA of the Mode register;

see Table 21.

Field CDBGMOD[1:0] of the Interrupt Configuration register controls the generation

of the INT signals for the control pipe. Field DDBGMODIN[1:0] of the Interrupt

Configuration register controls the generation of the INT signals for the IN pipe. Field

DDBGMODOUT[1:0] of the Interrupt Configuration register controls the generation of

the INT signals for the OUT pipe; see Table 25.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 13 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 14

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 14 of 66

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx

xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

Philips Semiconductors

DMA Interrupt Reason

register

EXT_EOT

INT_EOT

DMA_XFER_OK

IE_EXT_EOT

OR

IE_INT_EOT

IE_DMA_XFER_OK

DMA Interrupt Enable

register

Interrupt Enable register

IEBRESET

IESOF

IEDMA

IEP7RX

IEP7TX

Interrupt register

BRESET

SOF

OR

..........

LE

DMA

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

....................

INT

LATCH

PULSE/LEVEL

GENERATOR

Interrupt Configuration

register

INTPOL

Hi-Speed USB peripheral controller

Fig 4. Interrupt logic.

EP7RX

EP7TX

GLINTENA

Mode register

004aaa275

ISP1582

Page 15

Philips Semiconductors

8.11.2 Interrupt control

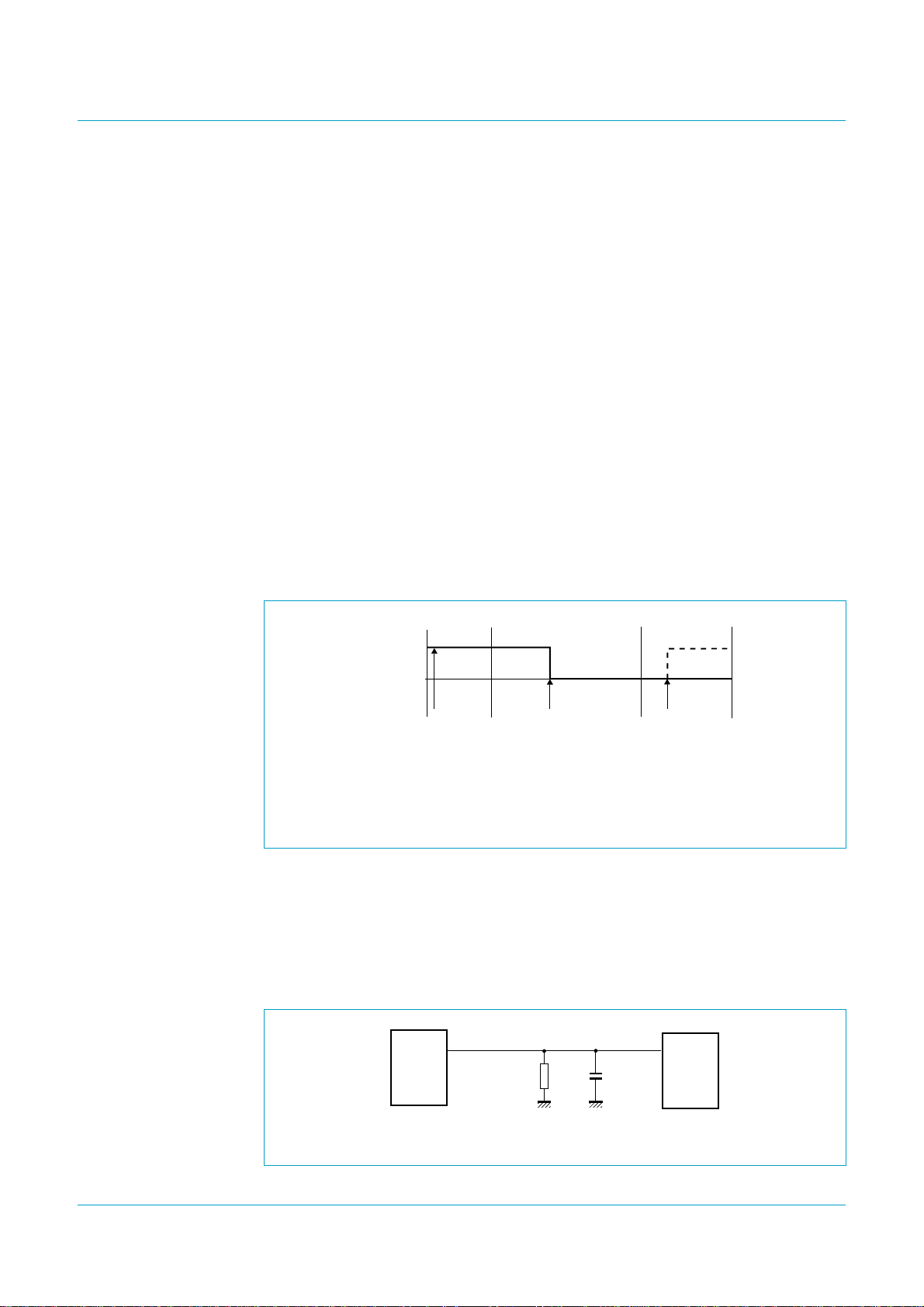

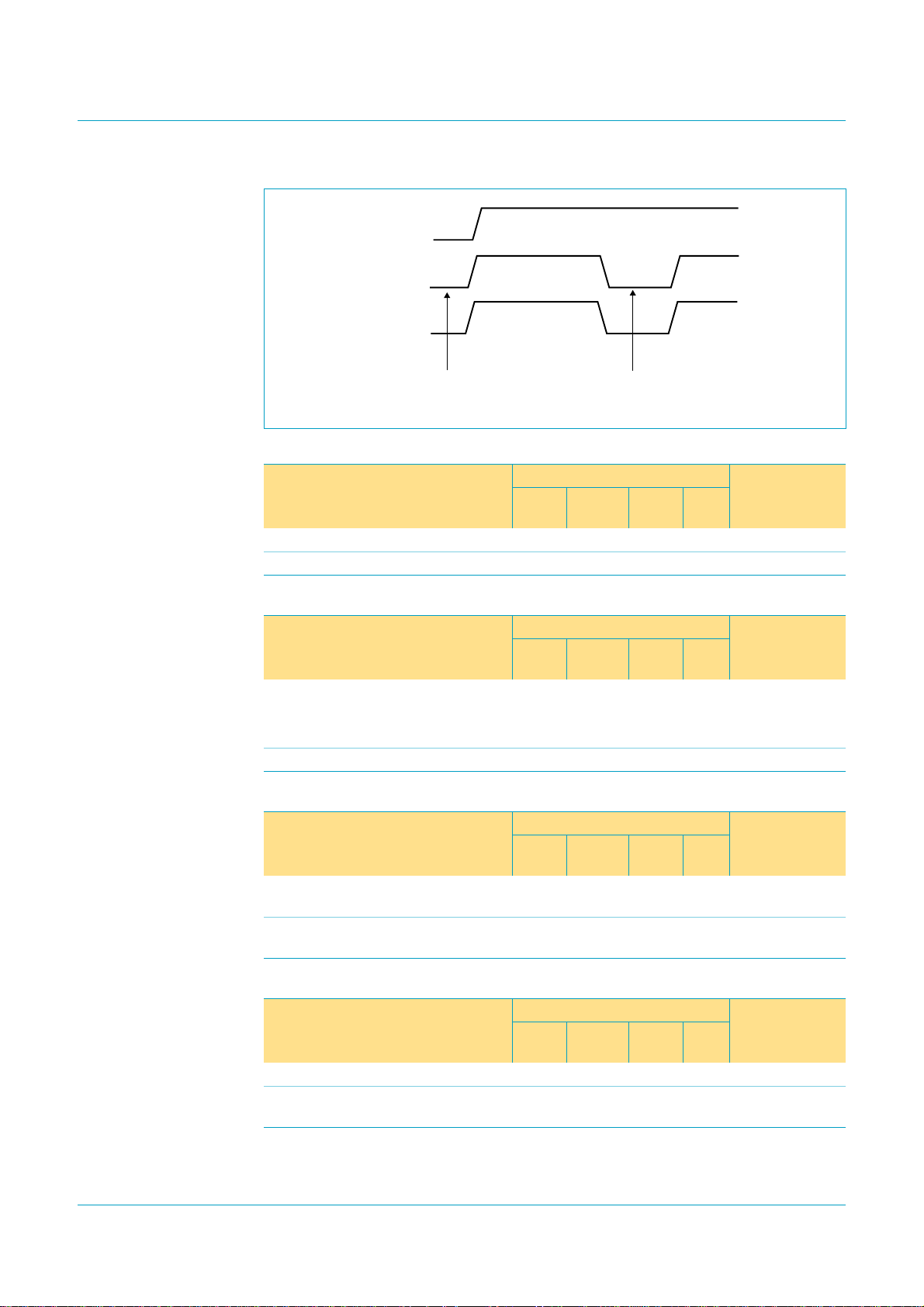

Bit GLINTENA in the Mode register is a global enable/disable bit. The behavior of this

bit is given in Figure 5.

Event A: When an interrupt event occurs (for example, SOF interrupt) with

bit GLINTENA set to logic 0, an interrupt will not be generated at pin INT. It will,

however, be registered in the corresponding Interrupt register bit.

Event B: When bit GLINTENA is set to logic 1, pin INT is asserted because bit SOF in

the Interrupt register is already set.

Event C: If the firmware sets bit GLINTENA to logic 0, pin INT will still be asserted.

The bold dashed line shows the desired behavior of pin INT.

Deassertion of pin INT can be achieved either by clearing all the Interrupt register or

the DMA Interrupt Reason register, depending on the event.

Remark: When clearing an interrupt event, perform write to all the bytes of the

register.

For more information on interrupt control, see Section 9.2.2, Section 9.2.5 and

Section 9.5.1.

ISP1582

Hi-Speed USB peripheral controller

8.12 V

Pin V

with bit CLKAON set to logic 0 (clock off option).

To detect whether the host is connected or not, that is V

and a 1 µF electrolytic capacitor must be added to damp the overshoot upon plug-in.

A

INT pin

GLINTENA = 0

(during this time,

an interrupt event

occurs. For example,

SOF asserted.)

Pin INT: HIGH = deassert; LOW = assert (individual interrupts are enabled).

GLINTENA = 1

B

SOF asserted

Fig 5. Behavior of bit GLINTENA.

sensing

BUS

is one of the ways to wake up the clock when the ISP1582 is suspended

BUS

BUS

49

ISP1582

1 MΩ

+

1 µF

C

GLINTENA = 0

SOF asserted

004aaa394

sensing, a 1 MΩ resistor

USB

Connector

004aaa440

Fig 6. Resistor and electrolytic capacitor needed for V

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 15 of 66

sensing.

BUS

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 16

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

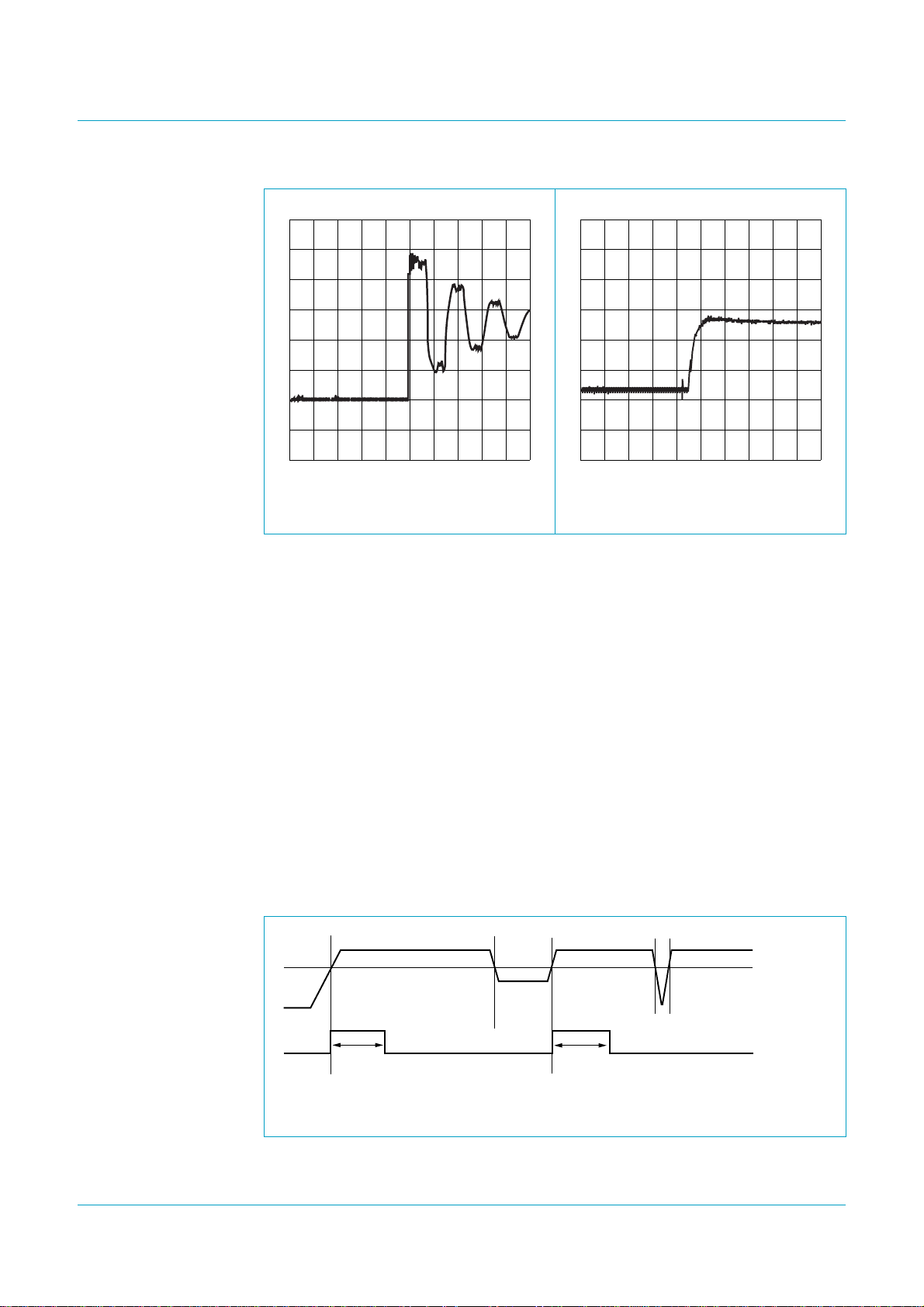

004aaa441 004aaa442

Fig 7. Oscilloscope reading: no resistor

and capacitor in the network.

8.13 Power-on reset

The ISP1582 requires a minimum pulse width of 500 µs.

Pin RESET_N can be either connected to VCC (using the internal POR circuit) or

externally controlled (by the microcontroller, ASIC, and so on). When VCC is directly

connected to pin RESET_N, the internal pulse width t

The power-on reset function can be explained by viewing the dips at t2-t3 and t4-t5

on the V

CC(POR)

t0 — The internal POR starts with a HIGH level.

t1 — The detector will see the passing of the trip level and a delay element will add

another t

PORP

t2-t3 — The internal POR pulse will be generated whenever V

V

for more than 11 µs.

trip

t4-t5 — The dip is too short (< 11 µs) and the internal POR pulse will not react and

will remain LOW.

curve (Figure 9).

before it drops to LOW.

Fig 8. Oscilloscope reading: with

resistor and capacitor in the

network.

will be typically 200 ns.

PORP

CC(POR)

drops below

V

BAT(POR)

V

trip

t0 t1

t

PORP

(1) PORP = power-on reset pulse.

t2

t3

t

PORP

t4

t5

(1)

PORP

004aaa389

Fig 9. POR timing.

Figure 10 shows the availability of the clock with respect to the external POR.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 16 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 17

Philips Semiconductors

Fig 10. Clock with respect to the external POR.

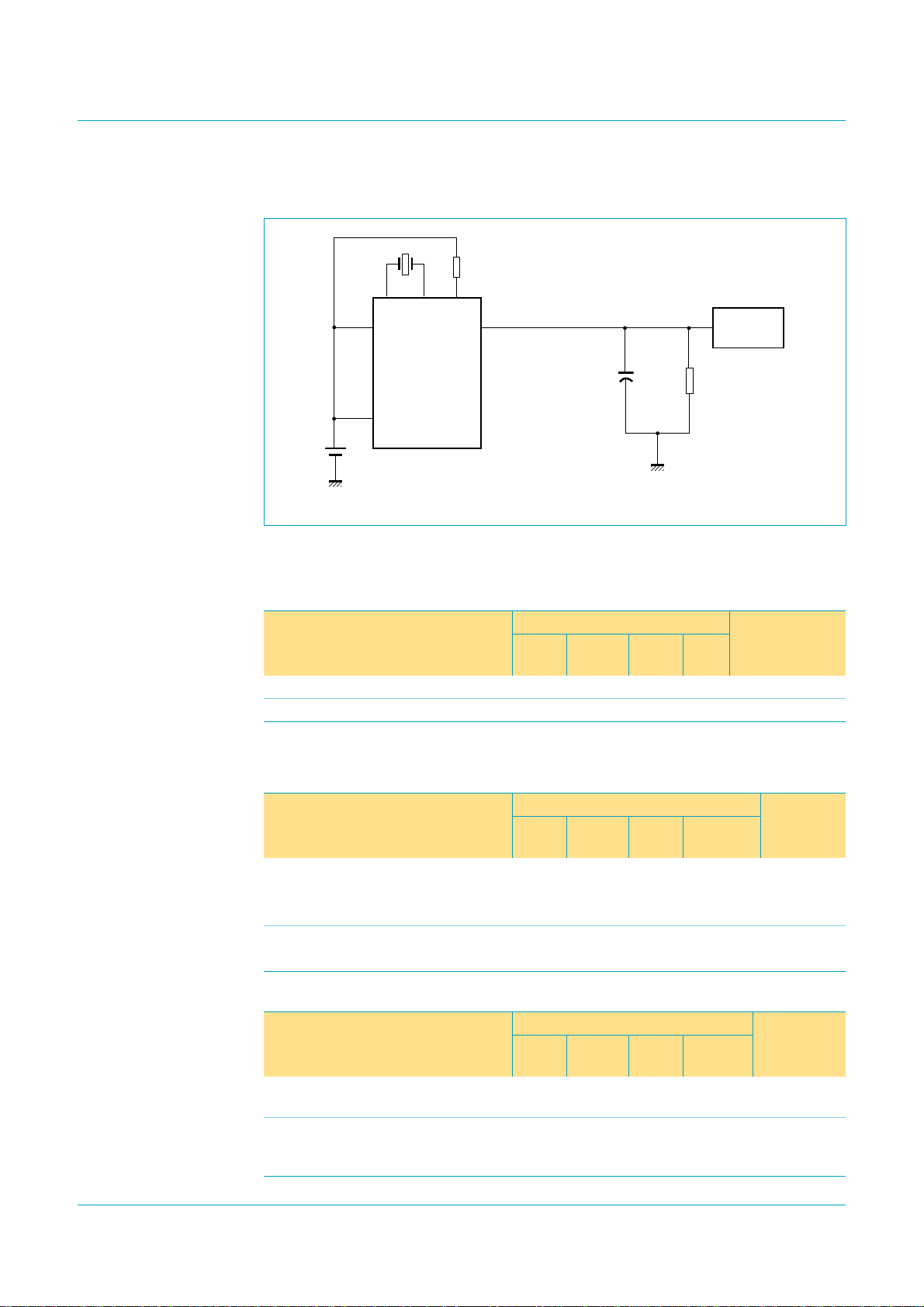

8.14 Power supply

The ISP1582 can be powered by 3.3 V ± 0.3 V, and 3.3 V at the interface. For

connection details, see Figure 11.

If the ISP1582 is powered by VCC= 3.3 V, an integrated 3.3 V-to-1.8 V voltage

regulator provides a 1.8 V supply voltage for the internal logic.

ISP1582

Hi-Speed USB peripheral controller

POR

EXTERNAL CLOCK

004aaa365

A

Stable external clock is to be available at A.

In sharing mode (that is, when VCC is not present and V

is present), all the I/O

CC(I/O)

pins are in three-state, the interrupt pin is connected to ground, and the suspend pin

is connected to V

ISP1582

CC(I/O)

53, 54

48

34

21

50

28

. See Table 3.

V

CC

V

CC(I/O)

V

CC(I/O)

V

CC(I/O)

V

V

0.01 µF 0.1 µF

CC(1V8)

+

(1)

4.7 µF

CC(1V8)

0.1 µF

0.01 µF

0.01 µF

0.1 µF

0.01 µF

0.1 µF

3.3 V ± 0.3 V

0.1 µF

V

CC

004aaa203

(1) It is mandatory to use a 4.7 µF electrolytic capacitor on V

0.1 µF

CC(1V8)

.

Fig 11. ISP1582 with 3.3 V supply.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 17 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 18

Philips Semiconductors

Table 4 shows power modes in which the ISP1582 can be operated.

Table 4: Power modes

V

CC

V

BUS

self-powered self-powered self-powered

V

BUS

[1] Power supply to the IC (VCC) is 3.3 V. Therefore, if the application is bus-powered, a 3.3 V regulator

[2] V

8.14.1 Power-sharing mode

[1]

[1]

needs to be used.

CC(I/O)=VCC

. If the application is bus-powered, a voltage regulator needs to be used.

V

CC(I/O)

[2]

V

BUS

self-powered power-sharing (hybrid)

To GPIO of processor

for sensing V

BUS

1.5 kΩ

5 V-to-3.3 V

VOLTAGE

REGULATOR

ISP1582

Hi-Speed USB peripheral controller

Power mode

bus-powered

RPU

V

CC

V

CC(I/O)

+

−

ISP1582

V

BUS

004aaa457

1 µF

+

−

V

BUS

USB

1 MΩ

Fig 12. Power-sharing mode.

As can be seen in Figure 12, in power-sharing mode, VCCis supplied by the output of

the 5 V-to-3.3 V voltage regulator. The input to the regulator is from V

BUS

. V

CC(I/O)

is

supplied through the power source of the system. When the USB cable is plugged in,

the ISP1582 goes through the power-on reset cycle. In this mode, OTG is disabled.

The processor will experience continuous interrupt because the default status of the

interrupt pin when operating in sharing mode with the V

overcomethis,implement external V

sensing circuitry.The output from the voltage

BUS

not present is LOW. To

BUS

regulator can be connected to pin GPIO of the processor to qualify the interrupt from

the ISP1582.

Remark: When the core power is removed, the ISP1582 must be reset using the

RESET_N pin. The reset pulse width must be 2 ms.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 18 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 19

Philips Semiconductors

V

CC(I/O)

ISP1582

Hi-Speed USB peripheral controller

V

CC

INT

power off

power off

004aaa469

Fig 13. Interrupt pin status during power off in power-sharing mode.

Table 5: Operation truth table for SoftConnect

ISP1582 operation Power supply Bit SOFTCT in

V

CC

V

CC(I/O)

RPU

V

Mode register

BUS

(3.3 V)

Normal bus operation 3.3 V 3.3 V 3.3 V 5 V enabled

Core power is lost 0 V 3.3 V 0 V 0 V not applicable

Table 6: Operation truth table for clock off during suspend

ISP1582 operation Power supply Clockoffduring

V

CC

V

CC(I/O)

RPU

V

BUS

suspend

(3.3 V)

Clock will wake up:

3.3 V 3.3 V 3.3 V 5 V enabled

After resume and

After a bus reset

Core power is lost 0 V 3.3 V 0 V 0 V not applicable

Table 7: Operation truth table for back voltage compliance

ISP1582 operation Power supply Bit SOFTCT in

V

CC

V

CC(I/O)

RPU

V

Mode register

BUS

(3.3 V)

Back voltage is not measured in this

3.3 V 3.3 V 3.3 V 5 V enabled

mode

Back voltage is not an issue because

0 V 3.3 V 0 V 0 V not applicable

core power is lost

Table 8: Operation truth table for OTG

ISP1582 operation Power supply OTG register

V

CC

V

CC(I/O)

RPU

V

BUS

(3.3 V)

SRP is not applicable 3.3 V 3.3 V 3.3 V 5 V not applicable

is

OTG is not possible because V

BUS

0 V 3.3 V 0 V 0 V not applicable

not present and so core power is lost

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 19 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 20

Philips Semiconductors

8.14.2 Self-powered mode

ISP1582

Hi-Speed USB peripheral controller

1.5 kΩ

RPU

V

CC

V

CC(I/O)

+

−

ISP1582

V

BUS

004aaa460

1 µF

V

BUS

+

−

USB

1 MΩ

Fig 14. Self-powered mode.

In self-powered mode, VCC and V

are supplied by the system. Bit SOFTCT in

CC(I/O)

the Mode register must be always logic 1. See Figure 14.

Table 9: Operation truth table for SoftConnect

ISP1582 operation Power supply Bit SOFTCT in

V

CC

V

CC(I/O)

RPU

(3.3 V)

Normal bus operation 3.3 V 3.3 V 3.3 V 5 V enabled

No pull-up on DP 3.3 V 3.3 V 3.3 V 0 V

[1] When the USB cable is removed, SoftConnect is disabled.

V

Mode register

BUS

[1]

disabled

Table 10: Operation truth table for clock off during suspend

ISP1582 operation Power supply Clock off

during

suspend

Clock will wake up:

V

CC

V

CC(I/O)

RPU

V

BUS

(3.3 V)

3.3 V 3.3 V 3.3 V 5 V enabled

After resume and

After a bus reset

Clock will wake up:

After detecting the presence of V

3.3 V 3.3 V 3.3 V 0 V => 5 V enabled

BUS

Table 11: Operation truth table for back voltage compliance

ISP1582 operation Power supply Bit SOFTCT

in Mode

register

Back voltage is not measured in this

V

CC

V

CC(I/O)

RPU

V

BUS

(3.3 V)

3.3 V 3.3 V 3.3 V 5 V enabled

mode

Back voltage is not an issue because

3.3 V 3.3 V 3.3 V 0 V disabled

pull-up on DP will not be present when

V

is not present

BUS

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 20 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 21

Philips Semiconductors

Table 12: Operation truth table for OTG

ISP1582 operation Power supply OTG

SRP is not applicable 3.3 V 3.3 V 3.3 V 5 V not

SRP is possible 3.3 V 3.3 V 3.3 V 0 V operational

8.14.3 Bus-powered mode

ISP1582

Hi-Speed USB peripheral controller

V

CC

V

CC(I/O)

RPU

V

BUS

(3.3 V)

5 V-to-3.3 V

VOLTAGE

REGULATOR

V

V

CC

V

BUS

BUS

register

applicable

USB

1 µF

+

−

1 MΩ

1.5 kΩ

V

CC(I/O)

RPU

ISP1582

004aaa462

Fig 15. Bus-powered mode.

In bus-powered mode (see Figure 15), VCCand V

the 5 V-to-3.3 V voltage regulator. The input to the regulator is from V

are supplied by the output of

CC(I/O)

BUS

. On

plugging in of the USB cable, the ISP1582 goes through the power-on reset cycle. In

this mode, OTG is disabled.

Table 13: Operation truth table for SoftConnect

ISP1582 operation Power supply Bit SOFTCT in

V

CC

V

CC(I/O)

RPU

(3.3 V)

Normal bus operation 3.3 V 3.3 V 3.3 V 5 V enabled

Power loss 0 V 0 V 0 V 0 V not applicable

Table 14: Operation truth table for clock off during suspend

ISP1582 operation Power supply Clockoffduring

V

CC

V

CC(I/O)

RPU

(3.3 V)

Clock will wake up:

3.3 V 3.3 V 3.3 V 5 V enabled

After resume and

After a bus reset

Power loss 0 V 0 V 0 V 0 V not applicable

V

V

Mode register

BUS

suspend

BUS

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 21 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 22

Philips Semiconductors

Table 15: Operation truth table for back voltage compliance

ISP1582 operation Power supply Bit SOFTCT in

Back voltage is not measured in this

mode

Power loss 0 V 0 V 0 V 0 V not applicable

Table 16: Operation truth table for OTG

ISP1582 operation Power supply OTG register

SRP is not applicable 3.3 V 3.3 V 3.3 V 5 V not applicable

Power loss 0 V 0 V 0 V 0 V not applicable

ISP1582

Hi-Speed USB peripheral controller

V

CC

V

CC(I/O)

RPU

(3.3 V)

3.3 V 3.3 V 3.3 V 5 V enabled

V

CC

V

CC(I/O)

RPU

(3.3 V)

V

V

Mode register

BUS

BUS

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 22 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 23

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

9. Register description

Table 17: Register overview

Name Destination Address Description Size

(bytes)

Initialization registers

Address device 00h USB device address and enabling 1 Section 9.2.1

Mode device 0Ch power-down options, global interrupt

enable, SoftConnect

Interrupt Configuration device 10h interrupt sources, trigger mode, output

polarity

OTG device 12h OTG implementation 1 Section 9.2.4

Interrupt Enable device 14h interrupt source enabling 4 Section 9.2.5

Data flow registers

Endpoint Index endpoints 2Ch endpoint selection, data flow direction 1 Section 9.3.1

Control Function endpoint 28h endpoint buffer management 1 Section 9.3.2

Data Port endpoint 20h data access to endpoint FIFO 2 Section 9.3.3

Buffer Length endpoint 1Ch packet size counter 2 Section 9.3.4

Buffer Status endpoint 1Eh buffer status for each endpoint 1 Section 9.3.5

Endpoint MaxPacketSize endpoint 04h maximum packet size 2 Section 9.3.6

Endpoint Type endpoint 08h selects endpoint type: control,

isochronous, bulk or interrupt

DMA registers

DMA Command DMA controller 30h controls all DMA transfers 1 Section 9.4.1

DMA Transfer Counter DMA controller 34h sets byte count for DMA transfer 4 Section 9.4.2

DMA Configuration DMA controller 38h sets GDMA configuration (counter

enable, burst length, data strobing, bus

width)

DMA Hardware DMA controller 3Ch endian type, master or slave selection,

signal polarity for DACK, DREQ, DIOW,

DIOR

DMA Interrupt Reason DMA controller 50h shows reason (source) for DMA interrupt 2 Section 9.4.5

DMA Interrupt Enable DMA controller 54h enables DMA interrupt sources 2 Section 9.4.6

DMA Endpoint DMA controller 58h selects endpoint FIFO,data flow direction 1 Section 9.4.7

1 Section 9.2.2

1 Section 9.2.3

2 Section 9.3.7

1 Section 9.4.3

1 Section 9.4.4

Reference

on page 24

on page 25

on page 27

on page 28

on page 30

on page 31

on page 33

on page 33

on page 34

on page 35

on page 36

on page 37

on page 39

on page 40

on page 41

on page 42

on page 43

on page 45

on page 45

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 23 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 24

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 17: Register overview

Name Destination Address Description Size

DMA Burst Counter DMA controller 64h DMA burst counter 2 Section 9.4.8

General registers

Interrupt device 18h shows interrupt sources 4 Section 9.5.1

Chip ID device 70h product ID code and hardware version 3 Section 9.5.2

Frame Number device 74h last successfully received

Scratch device 78h allows save or restore of firmware status

Unlock Device device 7Ch reenables register access after suspend 2 Section 9.5.5

Test Mode PHY 84h direct setting of DP and DM states,

…continued

Start-Of-Frame: lower byte (byte 0) is

accessed first

during suspend

internal transceiver test (PHY)

Reference

(bytes)

on page 46

on page 46

on page 48

2 Section 9.5.3

on page 49

2 Section 9.5.4

on page 49

on page 50

1 Section 9.5.6

on page 51

9.1 Register access

Register access depends on the bus width used. The ISP1582 uses a 16-bit bus

access. For single-byte registers, the upper byte (MSByte) must be ignored.

Endpoint specific registers are indexed via the Endpoint Index register. The target

endpoint must be selected before accessing the following registers:

• Buffer Length

• Buffer Status

• Control Function

• Data Port

• Endpoint MaxPacketSize

• Endpoint Type.

Remark: All reserved bits are not implemented. The bus and bus reset values are not

defined. Therefore, writing to these reserved bits will have no effect.

9.2 Initialization registers

9.2.1 Address register (address: 00h)

This register sets the USB assigned address and enables the USB device. Table 18

shows the Address register bit allocation.

Bits DEVADDR will be cleared whenever a bus reset, a power-on reset or a soft reset

occurs. Bit DEVEN will be cleared whenever a power-on reset or a soft reset occurs,

and will be set after a bus reset.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 24 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 25

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

In response to the standard USB request SET_ADDRESS, the firmware must write

the (enabled) device address to the Address register, followed by sending an empty

packet to the host. The new device address is activated when the device receives

acknowledgment from the host.

Table 18: Address register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol DEVEN DEVADDR[6:0]

Reset 00000000

Bus reset 10000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 19: Address register: bit description

Bit Symbol Description

7 DEVEN Logic 1 enables the device.

6 to 0 DEVADDR[6:0] This field specifies the USB device address.

9.2.2 Mode register (address: 0Ch)

This register consists of 2 bytes (bit allocation: see Table 20).

The Mode register controls resume, suspend and wake-up behavior, interrupt activity,

soft reset, clock signals and SoftConnect operation.

Table 20: Mode register: bit allocation

Bit 15 14 13 12 11 10 9 8

Symbol reserved DMA

CLKON

Reset ------0-

Bus reset ------0-

Access RRRRRRR/WR

Bit 7 6 5 4 3 2 1 0

Symbol CLKAON SNDRSU GOSUSP SFRESET GLINTENA WKUPCS PWRON SOFTCT

Reset 00000000

Bus reset 0000unchanged 0 0 unchanged

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 21: Mode register: bit description

Bit Symbol Description

15 to 10 - reserved

9 DMACLKON 1 — Supply clock to the DMA circuit.

0 — Power save mode; the DMA circuit will stop completely to save

power.

8 VBUSSTAT This bit reflects the V

pin status.

BUS

VBUSSTAT

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 25 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 26

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 21: Mode register: bit description

Bit Symbol Description

7 CLKAON Clock Always On: Logic 1 indicates that the internal clocks are

always running when in the suspend state. Logic 0 switches off the

internal oscillator and PLL when the device goes into suspend

mode. The device will consume less power if this bit is set to logic 0.

The clock is stopped after a delay of approximately 2 ms, following

which bit GOSUSP is set.

6 SNDRSU Send Resume: Writing logic 1, followed by logic 0 will generate an

upstream resume signal of 10 ms duration, after a 5 ms delay.

5 GOSUSP Go Suspend: Writing logic 1, followed by logic 0 will activate

suspend mode.

4 SFRESET Soft Reset: Writing logic 1, followed by logic 0 will enable a

software-initiated reset to the ISP1582. A soft reset is similar to a

hardware-initiated reset (via pin RESET_N).

3 GLINTENA Global Interrupt Enable: Logic 1 enables all interrupts. Individual

interrupts can be masked by clearing the corresponding bits in the

Interrupt Enable register.

When this bit is not set, an unmasked interrupt will not generate an

interrupt trigger on the interrupt pin. If global interrupt, however, is

enabled while there is any pending unmasked interrupt, an interrupt

signal will be immediately generated on the interrupt pin. (If the

interrupt is set to pulse mode, the interrupt events that were

generated before the global interrupt is enabled may be dropped).

2 WKUPCS Wake up on Chip Select: Logic 1 enables wake-up from suspend

mode through a valid register read on the ISP1582. (A read will

invokethe chip clock to restart. If you write to the register before the

clock gets stable, it may cause malfunctioning).

1 PWRON Pin SUSPEND output control.

…continued

0 — Pin SUSPEND is HIGH when the ISP1582 is in the suspend

state. Otherwise, pin SUSPEND is LOW.

1 — When the device is woken up from the suspend state, there will

be a 1 ms active HIGH pulse on pin SUSPEND. Pin SUSPEND will

remain LOW in all other states.

0 SOFTCT SoftConnect: Logic 1 enables the connection of the 1.5 kΩ pull-up

resistor on pin RPU to the DP line. Bus reset value: unchanged.

When SoftConnect and V

are not present (except in OTG), the USB bus activities

BUS

are not qualified. Therefore, the chip will follow the suspend command to enter

suspend mode (the clock is controlled by bit CLKAON).

When V

is off, the 1.5 kΩ pull-up resister is disconnected from pin DP in

BUS

approximately 4 ns via bit SOFTCT in the Mode register and a suspend interrupt is

set with some latency (debounce and disqualify USB traffic).

When bit SOFTCT is set to logic 0, no interrupt is generated. The firmware can issue

a suspend command, followed by the resetting of bit SOFTCT to suspend the chip.

If OTG is logic 1, the pull-up resistor on pin DP depends on D+ line (V

BUS

sensing

status). Bit DP operates as normal, so the firmware must mask suspend and wake-up

interrupt events. When SRP is completed, the device should clear OTG.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 26 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 27

Philips Semiconductors

If OTG is logic 0, the status of the pull-up resistor on DP is referred to in Table 22.

Table 22: Status of the chip

V

BUS

On pull-up resistor on DP pull-up resistor on DP is removed;

Off pull-up resistor on DP is removed;

9.2.3 Interrupt Configuration register (address: 10h)

This 1-byte register determines the behavior and polarity of the INT output. The bit

allocation is shown in Table 23. When the USB SIE receives or generates an ACK,

NAK or STALL, it will generate interrupts depending on three Debug mode fields.

CDBGMOD[1:0] — Interrupts for the control endpoint 0

DDBGMODIN[1:0] — Interrupts for the DATA IN endpoints 1 to 7

DDBGMODOUT[1:0] — Interrupts for the DATA OUT endpoints 1 to 7.

Hi-Speed USB peripheral controller

SoftConnect = on SoftConnect = off

suspend interrupt is immediately set,

regardless of the D+ and D− signals

pull-up resistor on DP is removed;

suspend interrupt is immediately set,

regardless of the D+ and D− signals

suspend interrupt is immediately set,

regardless of the D+ and D− signals

ISP1582

The Debug mode settings for CDBGMOD, DDBGMODIN and DDBGMODOUT allow

you to individually configure when the ISP1582 sends an interrupt to the external

microprocessor. Table 25 lists the available combinations.

Bit INTPOL controls the signal polarity of the INT output: active HIGH or LOW, rising

or falling edge. For level-triggering, bit INTLVL must be made logic 0. By setting

INTLVL to logic 1, an interrupt will generate a pulse of 60 ns (edge-triggering).

Table 23: Interrupt Configuration register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol CDBGMOD[1:0] DDBGMODIN[1:0] DDBGMODOUT[1:0] INTLVL INTPOL

Reset 11111100

Bus reset 111111unchanged unchanged

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 24: Interrupt Configuration register: bit description

Bit Symbol Description

7 to 6 CDBGMOD[1:0] Control 0 Debug Mode: For values, see Table 25

5 to 4 DDBGMODIN[1:0] Data Debug Mode IN: For values, see Table 25

3 to 2 DDBGMODOUT[1:0] Data Debug Mode OUT: For values, seeTable 25

1 INTLVL Interrupt Level: Selects signaling mode on output INT

(0 = level; 1 = pulsed). In pulsed mode, an interrupt

produces a 60 ns pulse. Bus reset value: unchanged.

0 INTPOL Interrupt Polarity: Selects signal polarity on output INT

(0 = active LOW; 1 = active HIGH). Bus reset

value: unchanged.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 27 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 28

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Table 25: Debug mode settings

Value CDBGMOD DDBGMODIN DDBGMODOUT

00h interrupt on all ACK and

NAK

interrupt on all ACK and

NAK

interrupt on all ACK, NYET

and NAK

01h interrupt on all ACK. interrupt on ACK interrupt on ACK and NYET

1Xh interrupt on all ACK and

first NAK

[1] First NAK: the first NAK on an IN or OUT token after a previous ACK response.

[1]

interrupt on all ACK and

first NAK

[1]

interrupt on all ACK, NYET

and first NAK

[1]

9.2.4 OTG register (address: 12h)

The bit allocation of the OTG register is given in Table 26.

Table 26: OTG register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol reserved DP BSESSVALID INITCOND DISCV VP OTG

Reset --0- -000

Bus reset --0- -000

Access - - R/W R/W R/W R/W R/W R/W

Table 27: OTG register: bit description

[1][2][3]

Bit Symbol Description

7 to 6 - reserved

5 DP When set, data-line pulsing is started. The default value of this bit is

logic 0. This bit must be cleared when data-line pulsing is completed.

4 BSESS VALID The device can initiate another V

data-line pulsing and V

pulsing, and before it clears this bit and

BUS

discharge sequence after

BUS

detects a session valid.

This bit is latched to logic 1 once V

exceeds the B-device session

BUS

valid threshold. Once set, it remains at logic 1. To clear this bit, write

logic 1. (The ISP1582 continuously updates this bit to logic 1 when

the B-session is valid. If the B-session is valid after it is cleared, it is

set back to logic 1 by the ISP1582).

0 — It implies that SRP has failed. Toproceed to a normal operation,

the device can restart SRP, clear bit OTG or proceed to an error

handling process.

1 — It implies that the B-session is valid. The device clears bit OTG,

goes into normal operation mode, and sets bit SOFTCT (DP pull-up)

in the Mode register. The OTG host has a maximum of 5 s before it

responds to a session request. During this period, the ISP1582 may

request to suspend. Therefore, the device firmware must wait for

sometime if it wishes to know the SRP result (success—if there is

minimum response from the host within 5 s; failure—if there is no

response from the host within 5 s).

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 28 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 29

Philips Semiconductors

Table 27: OTG register: bit description

Bit Symbol Description

3 INIT COND Write logic 1 to clear this bit. The device clears this bit, and waits for

2 DISCV Set to logic 1 to discharge V

1 VP Set to logic 1 to start V

0OTG 1 — Enables the OTG function. The V

ISP1582

Hi-Speed USB peripheral controller

[1][2][3]

…continued

more than 2 ms to check the bit status. If it reads logic 0, it means

that V

elapsed time is cleared. The device can then start a B-device SRP. If

it reads logic 1, it means that the initial condition of an SRP is

violated. So, the device should abort SRP.

The bit is set to logic 1 by the ISP1582 when initial conditions are not

met, and only writing logic 1 clears the bit. (If initial conditions are not

met after this bit has been cleared, it will be set again).

Remark: This implementation does not cover the case if an initial

SRP condition is violated when this bit is read and data-line pulsing is

started.

starting a new SRP. The discharge can take as long as 30 ms for

V

BUS

logic 0) before starting a session end detection.

16 ms and must be cleared before 26 ms.

bypassed.

0 — Normal operation. All OTG control bits will be masked. Status

bits are undefined.

remains lower than 0.8 V, and DP or DM at SE0 during the

BUS

. The device discharges V

BUS

BUS

before

to be charged less than 0.8 V. This bit must be cleared (write

pulsing. This bit must be set for more than

BUS

sensing functionality will be

BUS

[1] No interrupt is designed for OTG. The V

V

pulsing (see note 2).

BUS

[2] When OTG is in progress, the V

threshold or the OTG host has turned on the V

found during SRP, the device should complete data-line pulsing and V

B_SESSION_VALID detection.

[3] OTG implementation applies to the device with self-power capability. If the device works in sharing

mode, it should provide a switch circuit to supply power to the ISP1582 core during SRP.

BUS

interrupt, however, may assert as a side effect during the

BUS

interrupt may be set because V

supply to the device. Even if the V

BUS

is charged over V

BUS

pulsing before starting the

BUS

BUS

interrupt is

BUS

sensing

Session Request Protocol (SRP):

The ISP1582 can initiate an SRP. The B-device initiates SRP by data-line pulsing

followed by V

pulsing. The A-device can detect either data-line pulsing or V

BUS

BUS

pulsing.

The ISP1582 can initiate the B-device SRP by performing the following steps:

1. Detect initial conditions: read bit INITCOND of the OTG register.

2. Start data-line pulsing: set bit DP of the OTG register to logic 1.

3. Wait for 5 ms to 10 ms.

4. Stop data-line pulsing: set bit DP of the OTG register to logic 0.

5. Start V

pulsing: set bit VP of the OTG register to logic 1.

BUS

6. Wait for 10 ms to 20 ms.

7. Stop V

8. Discharge V

pulsing: set bit VP of the OTG register to logic 0.

BUS

for about 30 ms: optional by using bit DISCV of the OTG register.

BUS

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 29 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 30

Philips Semiconductors

9. Detect bit BSESSVALID of the OTG register for a successful SRP with bit OTG

ISP1582

Hi-Speed USB peripheral controller

disabled.

The B-device must complete both data-line pulsing and V

Remark: When disabling, OTG data-line pulsing bit DP and V

be cleared by writing logic 1.

9.2.5 Interrupt Enable register (address: 14h)

This register enables or disables individual interrupt sources. The interrupt for each

endpoint can be individually controlled via the associated bits IEPnRX or IEPnTX,

here n represents the endpoint number. All interrupts can be globally disabled

through bit GLINTENA in the Mode register (see Table 20).

An interrupt is generated when the USB SIE receives or generates an ACK or NAK

on the USB bus. The interrupt generation depends on Debug mode settings of bit

fields CDBGMOD[1:0], DDBGMODIN[1:0] and DDBGMODOUT[1:0].

All data IN transactions use the Transmit buffers (TX), which are handled by bits

DDBGMODIN. All data OUT transactions go via the Receive buffers (RX), which are

handled by bits DDBGMODOUT. Transactions on control endpoint 0 (IN, OUT and

SETUP) are handled by bits CDBGMOD.

Interrupts caused by events on the USB bus (SOF, Pseudo SOF, suspend, resume,

bus reset, setup and high-speed status) can also be individually controlled. A bus

reset disables all enabled interrupts except bit IEBRST (bus reset), which remains

unchanged.

pulsing within 100 ms.

BUS

pulsing bit VP must

BUS

The Interrupt Enable register consists of 4 bytes. The bit allocation is given in

Table 28.

Table 28: Interrupt Enable register: bit allocation

Bit 31 30 29 28 27 26 25 24

Symbol reserved IEP7TX IEP7RX

Reset ------00

Bus Reset ------00

Access - - - - - - R/W R/W

Bit 23 22 21 20 19 18 17 16

Symbol IEP6TX IEP6RX IEP5TX IEP5RX IEP4TX IEP4RX IEP3TX IEP3RX

Reset 00000000

Bus Reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 15 14 13 12 11 10 9 8

Symbol IEP2TX IEP2RX IEP1TX IEP1RX IEP0TX IEP0RX reserved IEP0SETUP

Reset 000000-0

Bus Reset 000000-0

Access R/W R/W R/W R/W R/W R/W R/W R/W

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 30 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 31

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Bit 7 6 5 4 3 2 1 0

Symbol IEVBUS IEDMA IEHS_STA IERESM IESUSP IEPSOF IESOF IEBRST

Reset 00000000

Bus Reset 0000000unchanged

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 29: Interrupt Enable register: bit description

Bit Symbol Description

31 to 26 - reserved

25 EP7TX Logic 1 enables interrupt from the indicated endpoint.

24 EP7RX Logic 1 enables interrupt from the indicated endpoint.

23 EP6TX Logic 1 enables interrupt from the indicated endpoint.

22 EP6RX Logic 1 enables interrupt from the indicated endpoint.

21 EP5TX Logic 1 enables interrupt from the indicated endpoint.

20 EP5RX Logic 1 enables interrupt from the indicated endpoint.

19 EP4TX Logic 1 enables interrupt from the indicated endpoint.

18 EP4RX Logic 1 enables interrupt from the indicated endpoint.

17 EP3TX Logic 1 enables interrupt from the indicated endpoint.

16 EP3RX Logic 1 enables interrupt from the indicated endpoint.

15 EP2TX Logic 1 enables interrupt from the indicated endpoint.

14 EP2RX Logic 1 enables interrupt from the indicated endpoint.

13 EP1TX Logic 1 enables interrupt from the indicated endpoint.

12 IEP1RX Logic 1 enables interrupt from the indicated endpoint.

11 IEP0TX Logic 1 enables interrupt from the control IN endpoint 0.

10 IEP0RX Logic 1 enables interrupt from the control OUT endpoint 0.

9 - reserved

8 IEP0SETUP Logic 1 enables interrupt for the setup data received on endpoint 0.

7 IEVBUS Logic 1 enables interrupt for V

6 IEDMA Logic 1 enables interrupt on DMA status change detection.

5 IEHS_STA Logic 1 enables interrupt on detection of a high-speed status

change.

4 IERESM Logic 1 enables interrupt on detection of a resume state.

3 IESUSP Logic 1 enables interrupt on detection of a suspend state.

2 IEPSOF Logic 1 enables interrupt on detection of a Pseudo SOF.

1 IESOF Logic 1 enables interrupt on detection of an SOF.

0 IEBRST Logic 1 enables interrupt on detection of a bus reset.

BUS

sensing.

9.3 Data flow registers

9.3.1 Endpoint Index register (address: 2Ch)

The Endpoint Index register selects a target endpoint for register access by the

microcontroller. The register consists of 1 byte, and the bit allocation is shown in

Table 30.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 31 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 32

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

The following registers are indexed:

• Buffer Length

• Buffer Status

• Control Function

• Data Port

• Endpoint MaxPacketSize

• Endpoint Type.

For example, to access the OUT data buffer of endpoint 1 using the Data Port

register, the Endpoint Index register has to be written first with 02h.

Remark: The Endpoint Index register and the DMA Endpoint Index register must not

point to the same endpoint.

Table 30: Endpoint Index register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol reserved EP0SETUP ENDPIDX[3:0] DIR

Reset - - 000000

Bus reset - - 000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 31: Endpoint Index register: bit description

Bit Symbol Description

7 to 6 - reserved

5 EP0SETUP Selects the SETUP buffer for endpoint 0.

0 — EP0 data buffer

1 — SETUP buffer.

Must be logic 0 for access to other endpoints than endpoint 0.

4 to 1 ENDPIDX[3:0] Endpoint Index: Selects the target endpoint for register access of

Buffer Length, Control Function, Data Port, Endpoint Type and

MaxPacketSize.

0 DIR Direction bit: Sets the target endpoint as IN or OUT.

0 — target endpoint refers to OUT (RX) FIFO

1 — target endpoint refers to IN (TX) FIFO.

Table 32: Addressing of endpoint 0 buffers

Buffer name EP0SETUP ENDPIDX DIR

SETUP 1 00h 0

Data OUT 0 00h 0

Data IN 0 00h 1

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 32 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 33

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

9.3.2 Control Function register (address: 28h)

The Control Function register performs the buffer management on endpoints. It

consists of 1 byte, and the bit configuration is given in Table 33. The register bits can

stall, clear or validate any enabled data endpoint. Before accessing this register, the

Endpoint Index register must be written first to specify the target endpoint.

Table 33: Control Function register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol reserved CLBUF VENDP DSEN STATUS STALL

Reset - - -00000

Bus reset - - -00000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 34: Control Function register: bit description

Bit Symbol Description

7 to 5 - reserved

4 CLBUF Clear Buffer: Logic 1 clears the RX bufferoftheindexed endpoint; the TX

buffer is not affected. The RX buffer is automatically cleared once the

endpoint is completely read. This bit is set only when it is necessary to

forcefully clear the buffer.

3 VENDP Validate Endpoint: Logic 1 validates the data in the TX FIFO of an IN

endpoint for sending on the next IN token. In general, the endpoint is

automatically validated when its FIFO byte count has reached the

endpoint MaxPacketSize. This bit is set only when it is necessary to

validate the endpoint with the FIFO byte count which is below the

Endpoint MaxPacketSize.

2 DSEN Data Stage Enable: This bit controls the response of the ISP1582 to a

control transfer. When this bit is set, the ISP1582 goes to the data stage;

otherwise, the ISP1582 will NAK the data stage transfer until the firmware

explicitly responds to the setup command.

1 STATUS Status Acknowledge: Only applicable for control IN/OUT.

This bit controls the generation of ACK or NAK during the status stage of

a SETUP transfer. It is automatically cleared when the status stage is

completed, or when a SETUP tokenis received. No interrupt signal will be

generated.

0 — Sends NAK

1 — Sends an empty packet following the IN token (host-to-peripheral) or

ACK following the OUT token (peripheral-to-host).

0 STALL Stall Endpoint: Logic 1 stalls the indexed endpoint. This bit is not

applicable for isochronous transfers.

Remark: ‘Stall’ing a data endpoint will confuse the Data Toggle bit about

the stalled endpoint because the internal logic picks up from where it is

stalled. Therefore, the Data Toggle bit must be reset by disabling and

reenabling the corresponding endpoint (by setting bit ENABLE to logic 0

or logic 1 in the Endpoint Type register) to reset the PID.

9.3.3 Data Port register (address: 20h)

This 2-byte register provides direct access for a microcontroller to the FIFO of the

indexed endpoint. The bit allocation is shown in Table 35.

9397 750 13699

Preliminary data Rev. 03 — 25 August 2004 33 of 66

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Page 34

Philips Semiconductors

ISP1582

Hi-Speed USB peripheral controller

Peripheral-to-host (IN endpoint): After each write action, an internal counter is auto

incremented by two to the next location in the TX FIFO. When all bytes have been

written (FIFO byte count = endpoint MaxPacketSize), the buffer is automatically

validated. The data packet will then be sent on the next IN token. When it is

necessary to validate the endpoint whose byte count is less than MaxPacketSize, it

can be done using the Control Function register (bit VENDP).

Host-to-peripheral (OUT endpoint): After each read action, an internal counter is

auto decremented by two to the next location in the RX FIFO. When all bytes have

been read, the buffer contents are automatically cleared. A new data packet can then

be received on the next OUT token. The buffer contents can also be cleared through

the Control Function register (bit CLBUF), when it is necessary to forcefully clear the

contents.

Remark: The buffer can be automatically validated or cleared by using the Buffer

Length register (see Table 37).

Table 35: Data Port register: bit allocation

Bit 15 14 13 12 11 10 9 8

Symbol DATAPORT[15:8]

Reset 00000000

Bus reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7 6 5 4 3 2 1 0

Symbol DATAPORT[7:0]

Reset 00000000

Bus reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 36: Data Port register: bit description

Bit Symbol Description

15 to 8 DATAPORT[15:8] data (upper byte)

7 to 0 DATAPORT[7:0] data (lower byte)

9.3.4 Buffer Length register (address: 1Ch)

This register determines the current packet size (DATACOUNT) of the indexed

endpoint FIFO. The bit allocation is given in Table 37.

The Buffer Length register is automatically loaded with the FIFO size, when the

Endpoint MaxPacketSize register is written (see Table 41). A smaller value can be