ISP1581

Universal Serial Bus 2.0 high-speed interface device

Rev. 02 — 23 October 2000 Objective specification

1. General description

The ISP1581 is a cost-optimized and feature-optimized Universal Serial Bus (USB)

interface device, which fully complies with the

Rev. 2.0

microcontroller or microprocessor. The ISP1581 communicates with the system’s

microcontroller/processor through a high-speed general-purpose parallel interface.

The ISP1581 supports automatic detection of USB 2.0 system operation. The

USB 1.1 fall-back mode allows the device to remain operational under full-speed

conditions. It is designed as a generic USB interface device so that it can fit into all

existing device classes, such as: Imaging Class, Mass Storage Devices,

Communication Devices, Printing Devices and Human Interface Devices.

Universal Serial Bus Specification

. It provideshigh-speedUSB communication capacity to systems based on a

The internal generic DMA block allows easy integration into data streaming

applications. In addition, the various configurations of the DMA block are tailored for

mass storage applications.

The modular approach to implementing a USB interface device allows the designer to

select the optimum system microcontroller from the wide variety available. The ability

to re-use existing architecture and firmware investments shortens the development

c

c

time, eliminates risk and reduces costs. The result is fast and efficient developmentof

the most cost-effective USB peripheral solution.

The ISP1581 is ideally suited for many types of peripherals, such as: printers;

scanners; magneto-optical (MO), compact disc (CD), digital video disc (DVD) and

Zip®/Jaz® drives; digital still cameras; USB-to-Ethernet links; cable and DSL

modems. The low power consumption during ‘suspend’ mode allows easy design of

equipment that is compliant to the ACPI™, OnNow™ and USB power management

requirements.

The ISP1581 also incorporates features such as SoftConnect™, a reduced

frequency crystal oscillator and integrated termination resistors. These features allow

significant cost savings in system design and easy implementation of advanced USB

functionality into PC peripherals.

Philips Semiconductors

2. Features

■ Complies fully with Universal Serial Bus Specification Rev. 2.0

■ Complies with most Device Class specifications

■ High performance USB interface device with integrated Serial Interface Engine

■ Supports automatic USB 2.0 mode detection and USB 1.1 fall-back mode

■ High speed DMA interface

■ Fully autonomous and multi-configuration DMA operation

■ Up to 14 programmable USB endpoints with 2 fixed control IN/OUT endpoints

■ Integrated physical 8 kbyte of multi-configuration FIFO memory

■ Endpoints with double buffering to increase throughput and ease real-time data

■ Bus independent interface with most microcontroller/microprocessors

■ Bus-powered capability with low power consumption and low ‘suspend’ current

■ 12 MHz crystal oscillator with integrated PLL for low EMI

■ Software controlled connection to the USB bus (SoftConnect™)

■ Complies with the ACPI™, OnNow™ and USB power management requirements

■ Internal power-on and low-voltage reset circuit, also supporting a software reset

■ Operation over the extended USB bus voltage range (4.0 to 5.5 V) with 5 V

■ Operating temperature range −40 to +85 °C

■ 12 kV in-circuit ESD protection on human accessible pins such as D+ and D−

■ Full-scan design with high fault coverage (>99%)

■ Available in LQFP64 package.

ISP1581

USB 2.0 HS interface device

(SIE), FIFO memory, data transceiver and 3.3 V voltage regulators

transfer

(16 Mbytes/s or 16 Mwords/s)

tolerant I/O pads

3. Applications

■ Personal digital assistant (PDA)

■ Mass storage device, e.g., Zip®, Jaz®, MO, CD, DVD drive

■ Digital camera

■ Communication device, e.g. router, modem

■ Printer

■ Scanner.

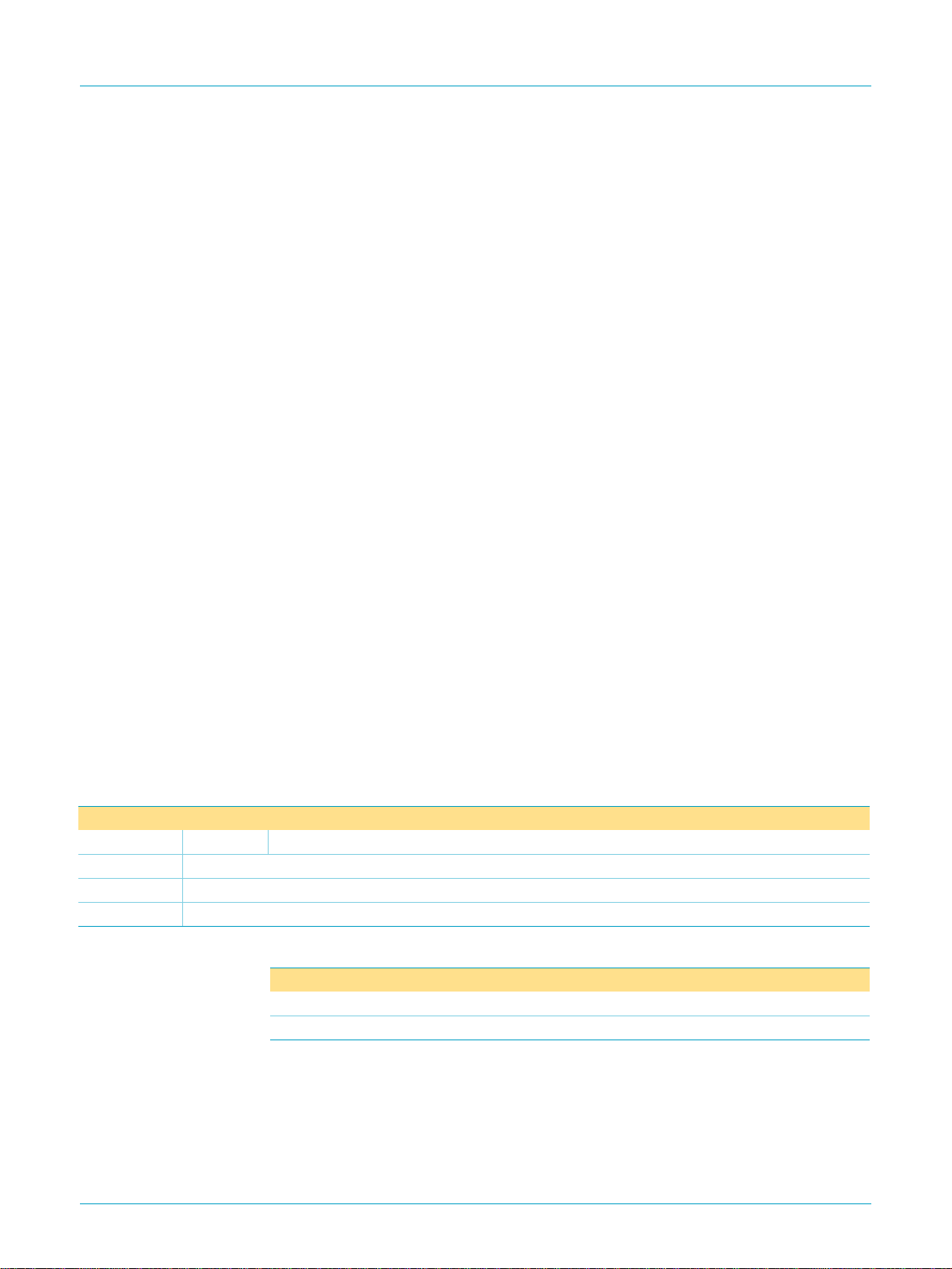

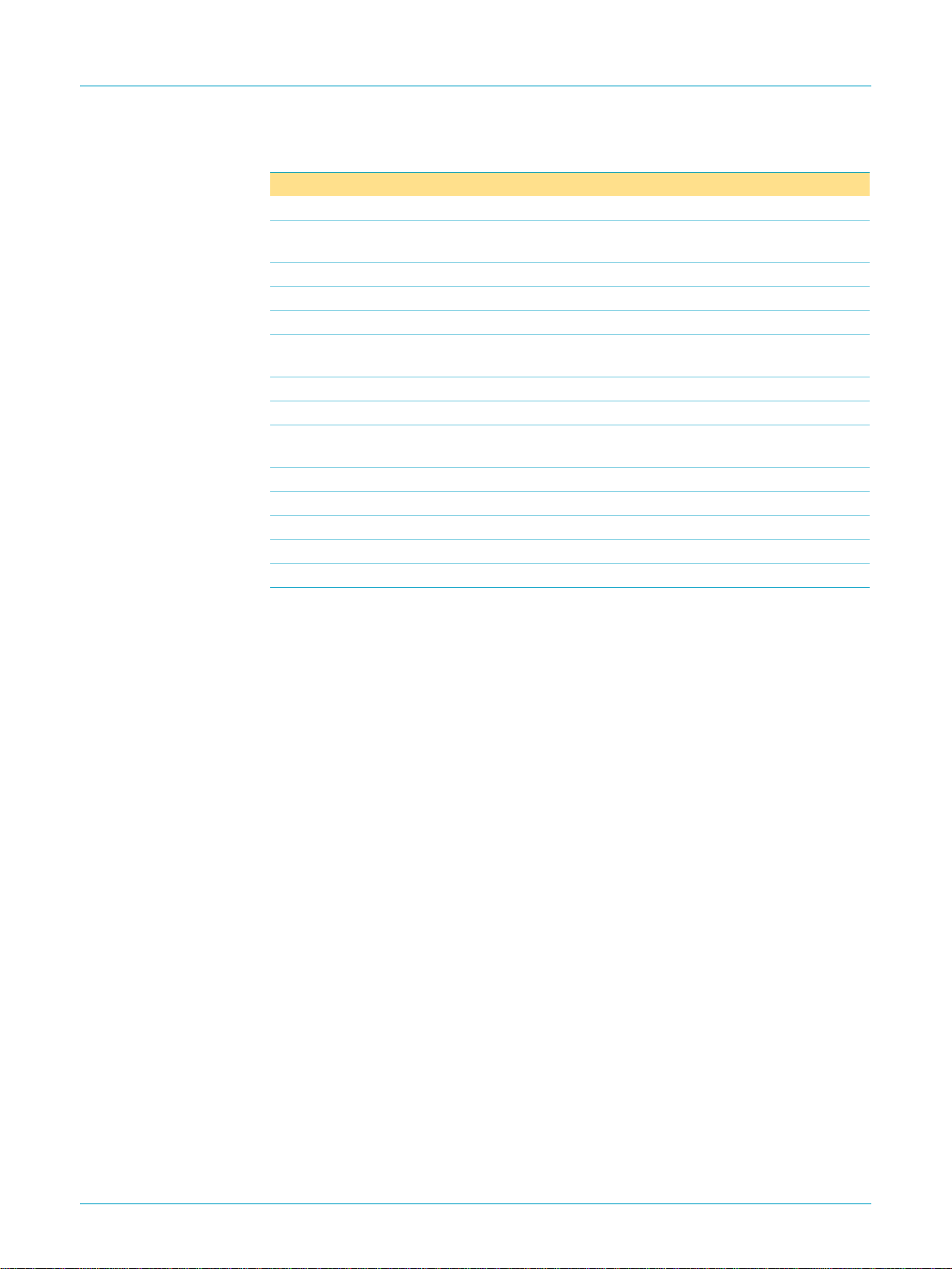

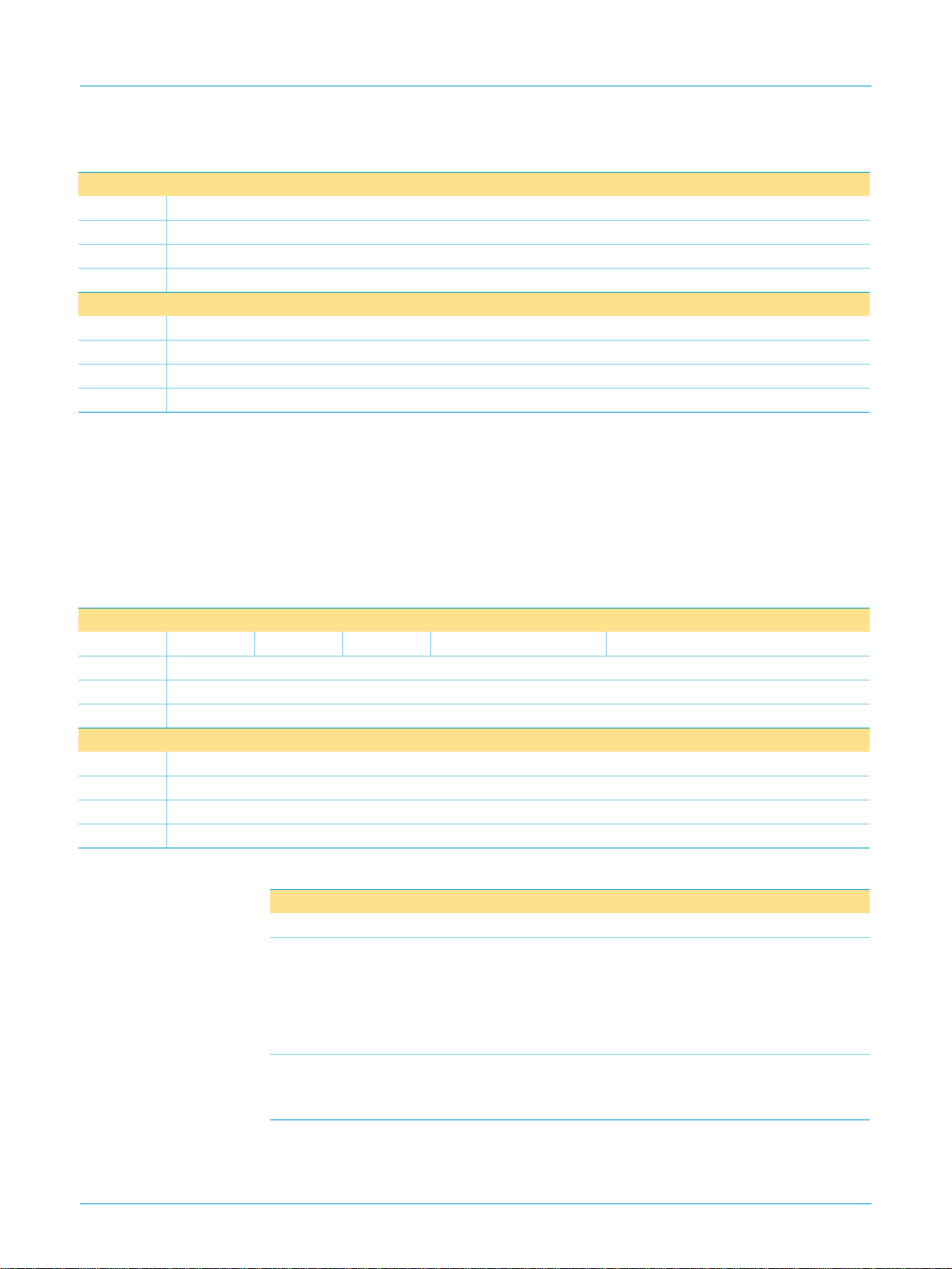

4. Ordering information

Table 1: Ordering information

Type number Package

Name Description Version

ISP1581BD LQFP64 Plastic low profile quad flat package; 64 leads; body 10 x 10 x 1.4 mm SOT314-2

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 2 of 73

© Philips Electronics N.V. 2000. All rights reserved.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 3 of 73

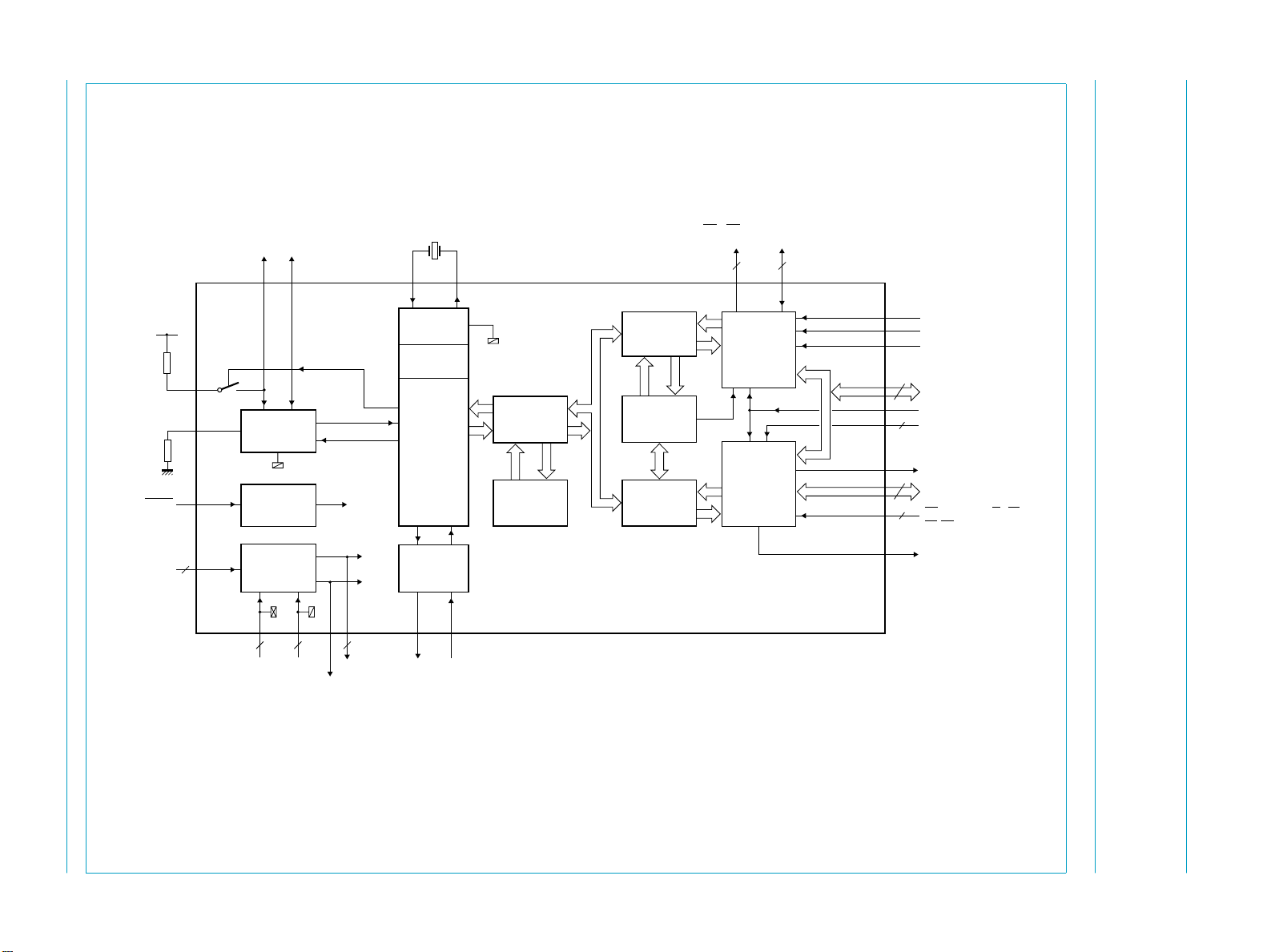

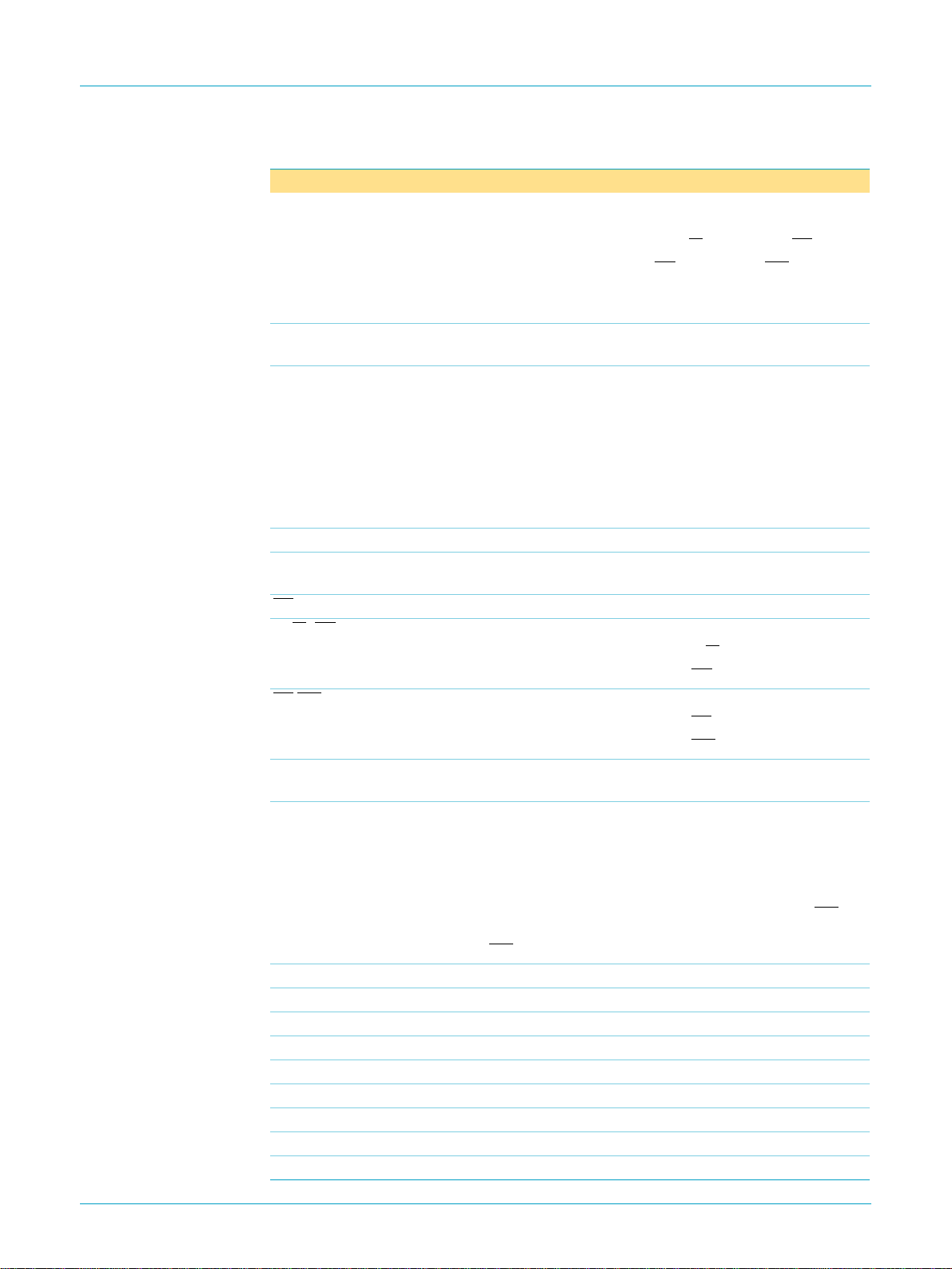

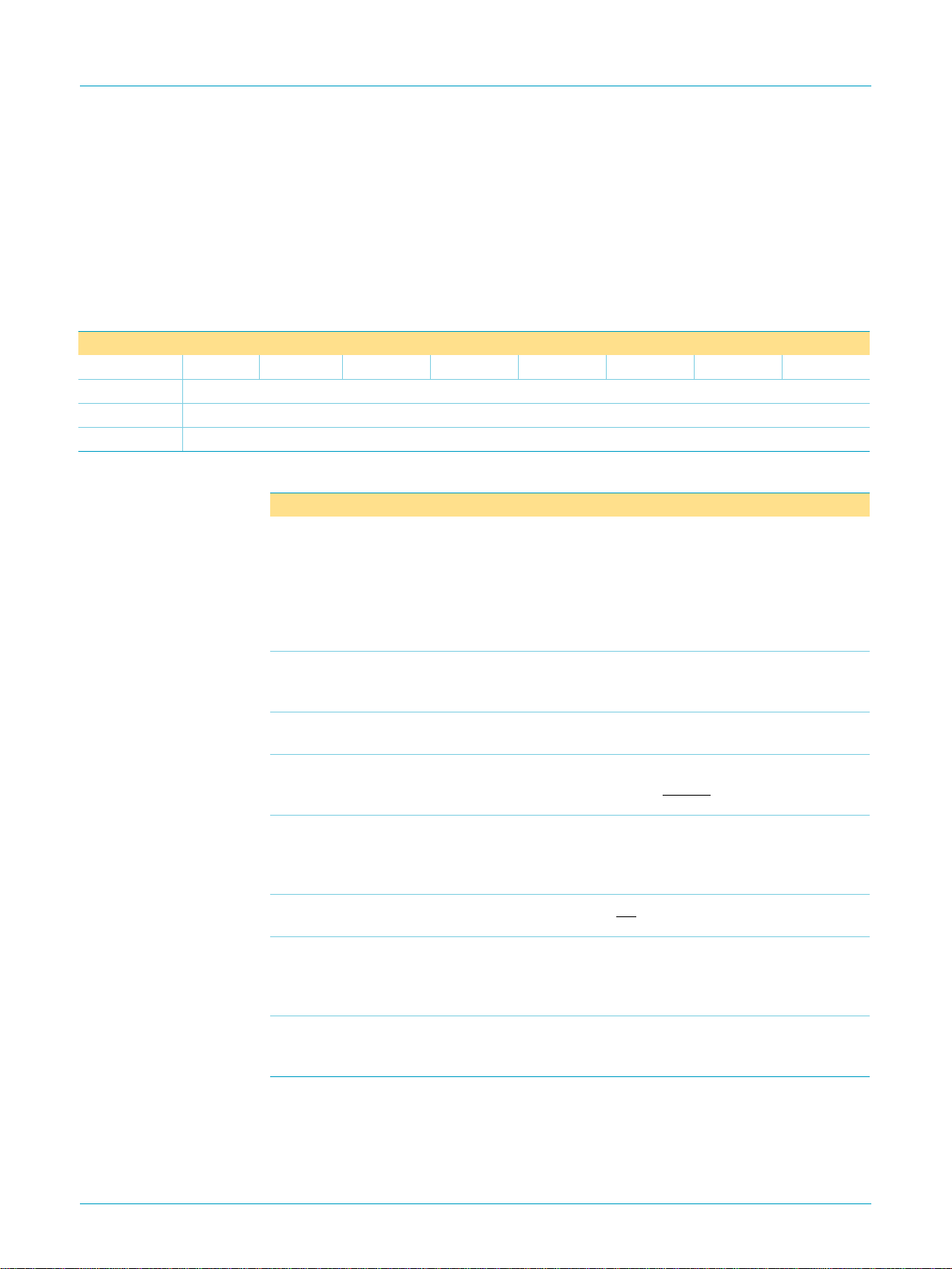

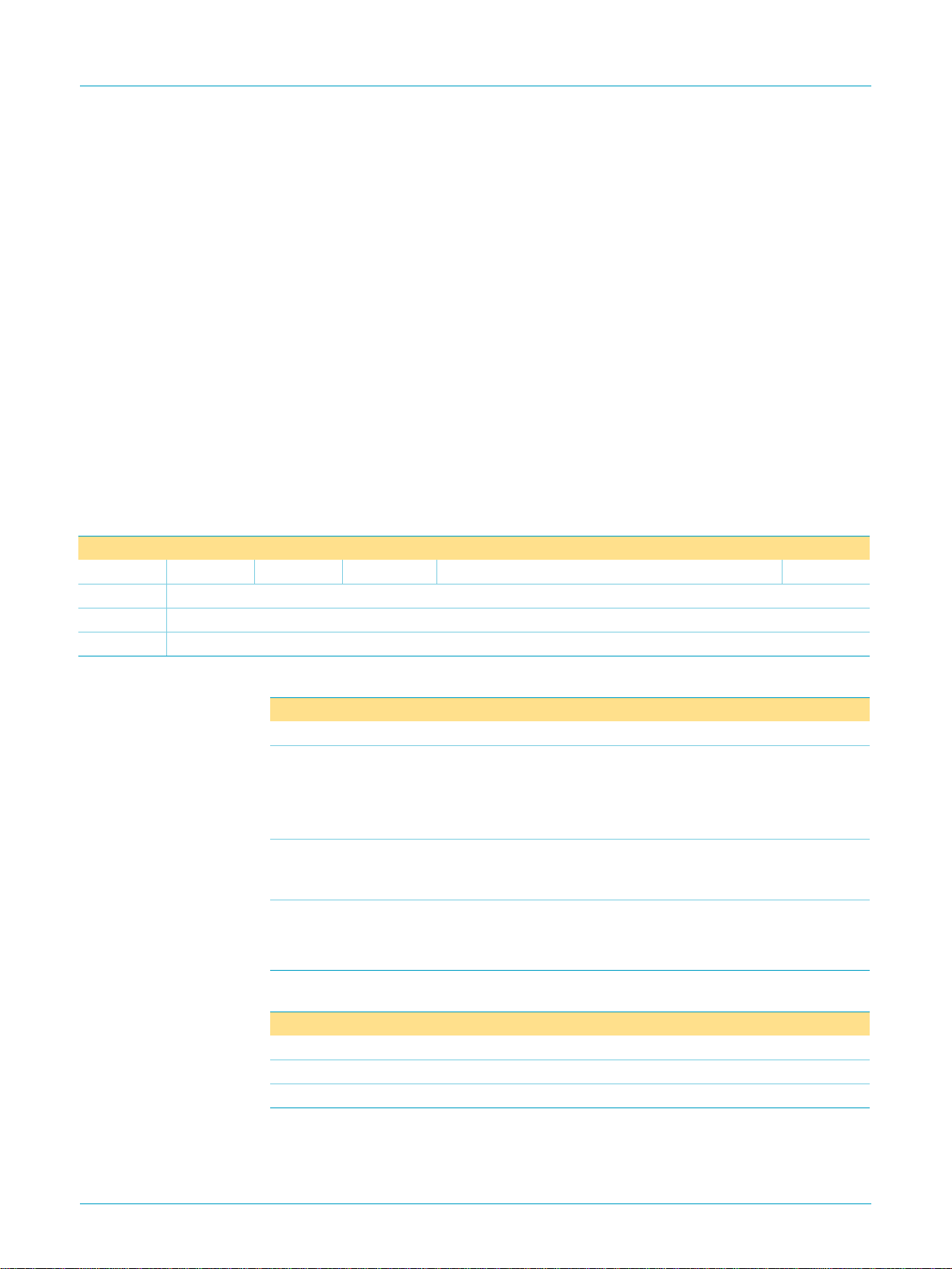

5. Block diagram

Philips Semiconductors

to/from USB

D−

D+

5

6

3.3 V

1.5

kΩ

12.2 kΩ

(±0.1%)

RESET

V

CC(5.0)

© Philips Electronics N.V. 2000. All rights reserved.

RPU

RREF

4

7

8

10

2, 37,

43, 64

5 V

1, 36, 42, 61

TRANSCEIVER

POWER-ON

VOLTAGE

REGULATORS

DGND

USB 2.0

RESET

4

SoftConnect

2 2

AGND

3.3 V

3.3 V

V

reg(3.3)

43, 23

V

CC(3.3)

internal

reset

digital

supply

analog

supply

24, 58

12 MHz

XTAL2XTAL1

60 59

40× PLL

OSCILLATOR

BIT CLOCK

RECOVERY

PHILIPS

SIE

SYSTEM

CONTROLLER

63

SUSPEND62WAKEUP

MEMORY

MANAGEMENT

UNIT

INTEGRATED

RAM

(8 KBYTE)

DMA

HANDLER

DMA

REGISTERS

MICRO-

CONTROLLER

HANDLER

ISP1581

Denotes shared pin usage

*

CS0, CS1,

DA0

*

18, 17,

19, 20, 21

, DA1*, DA2

DREQ, DACK,

DIOR, DIOW

5 4

DMA

INTERFACE

MICRO

CONTROLLER

INTERFACE

12, 13,

14, 15

40, 41,

44 to 57

20, 9

38, 39, 30 to 35

25, 29, 26, 27

MGT234

11

16

22

19

22

28

EOT

INTRQ

IORDY

16

DATA0 to DATA15

BUS_CONF

2

MODE0

READY

8

AD0 to AD7

4

CS, ALE/A0, (R/W)/RD,

DS/WR

INT

*

, MODE1

*

*

*

USB 2.0 HS interface device

The direction of pins DREQ, DACK, DIOR and DIOW is determined by bit MASTER (DMA Hardware register) and bit ATA_MODE(DMA Configuration register).

Fig 1. Block diagram.

ISP1581

Philips Semiconductors

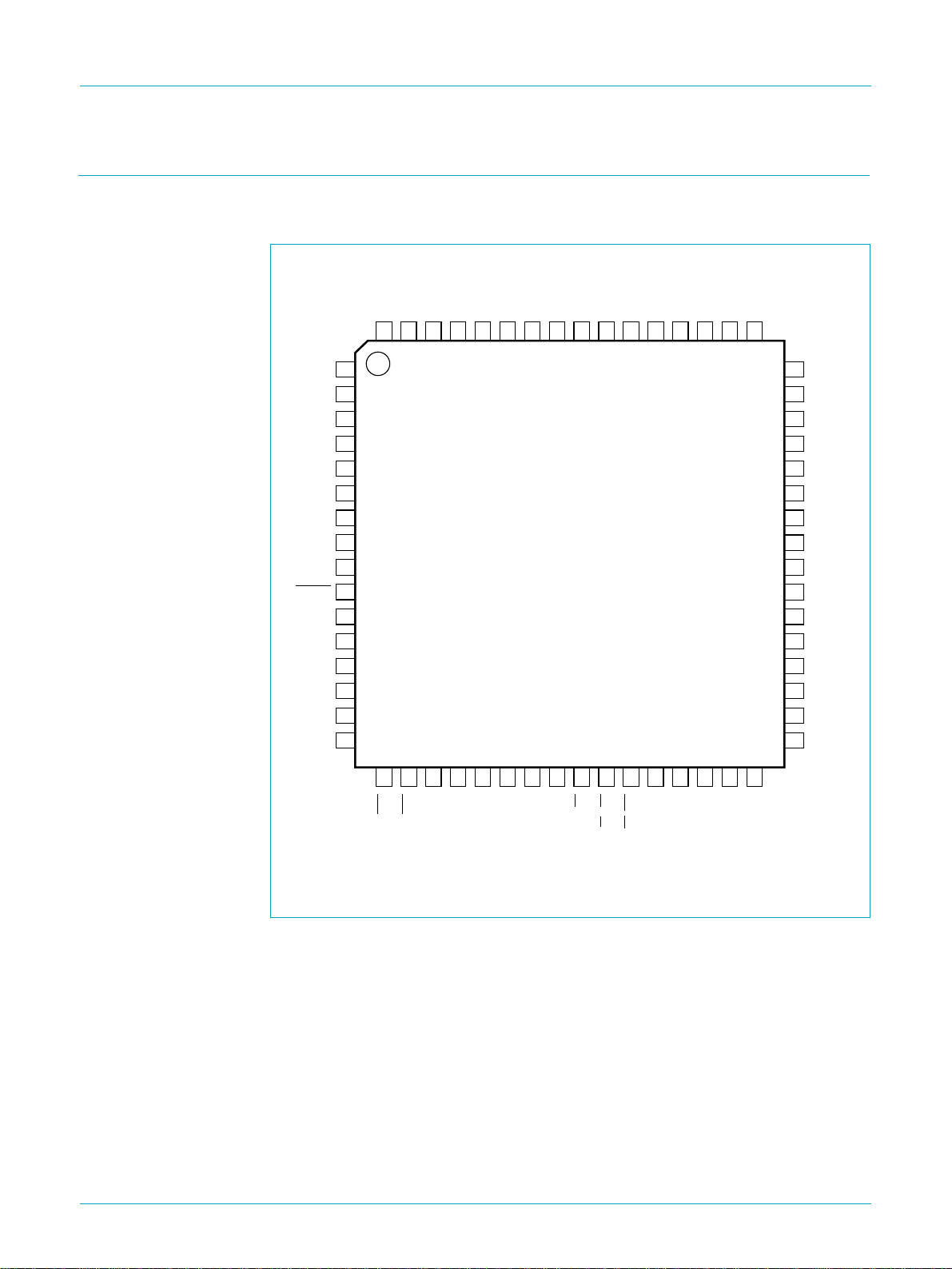

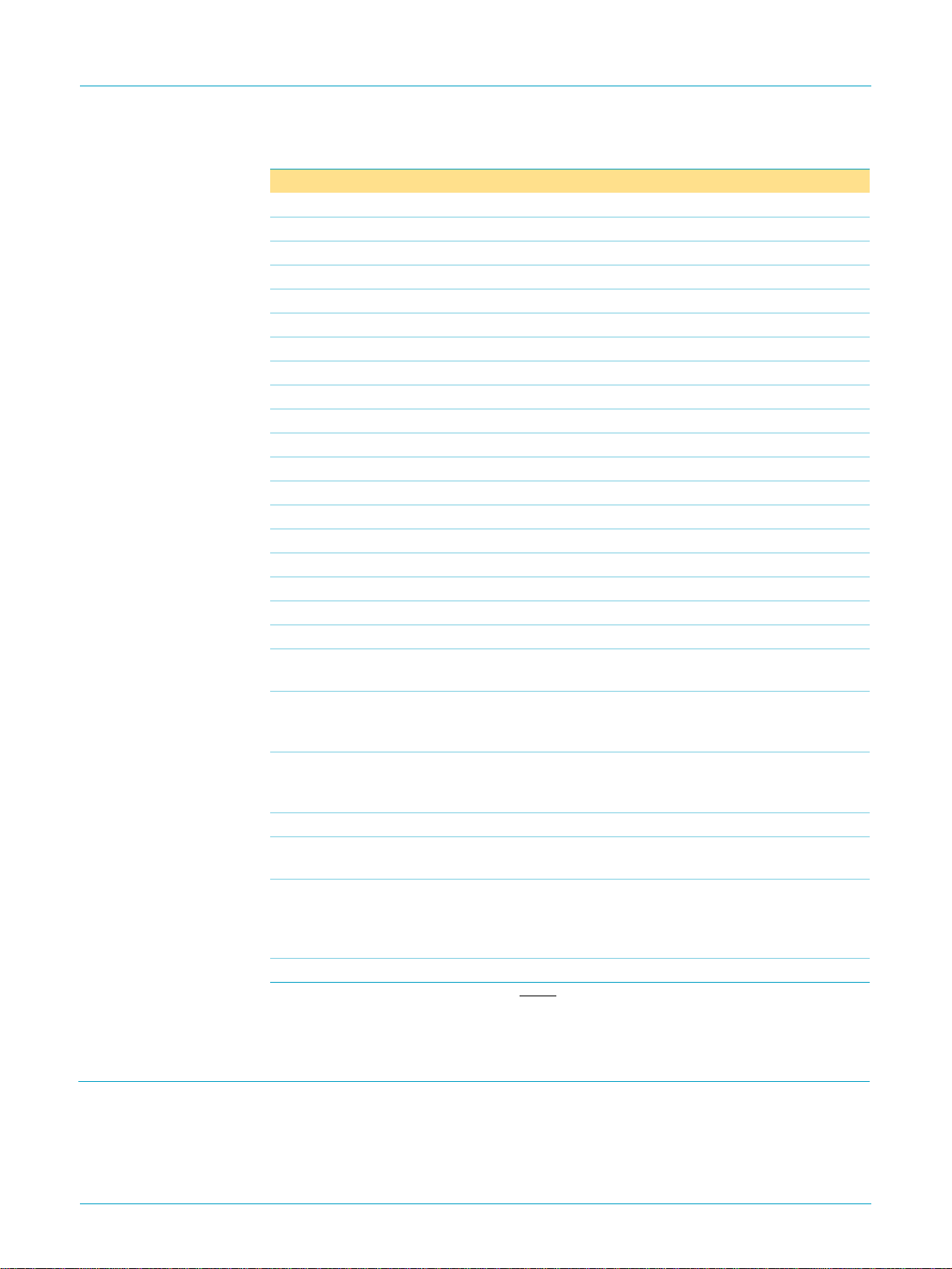

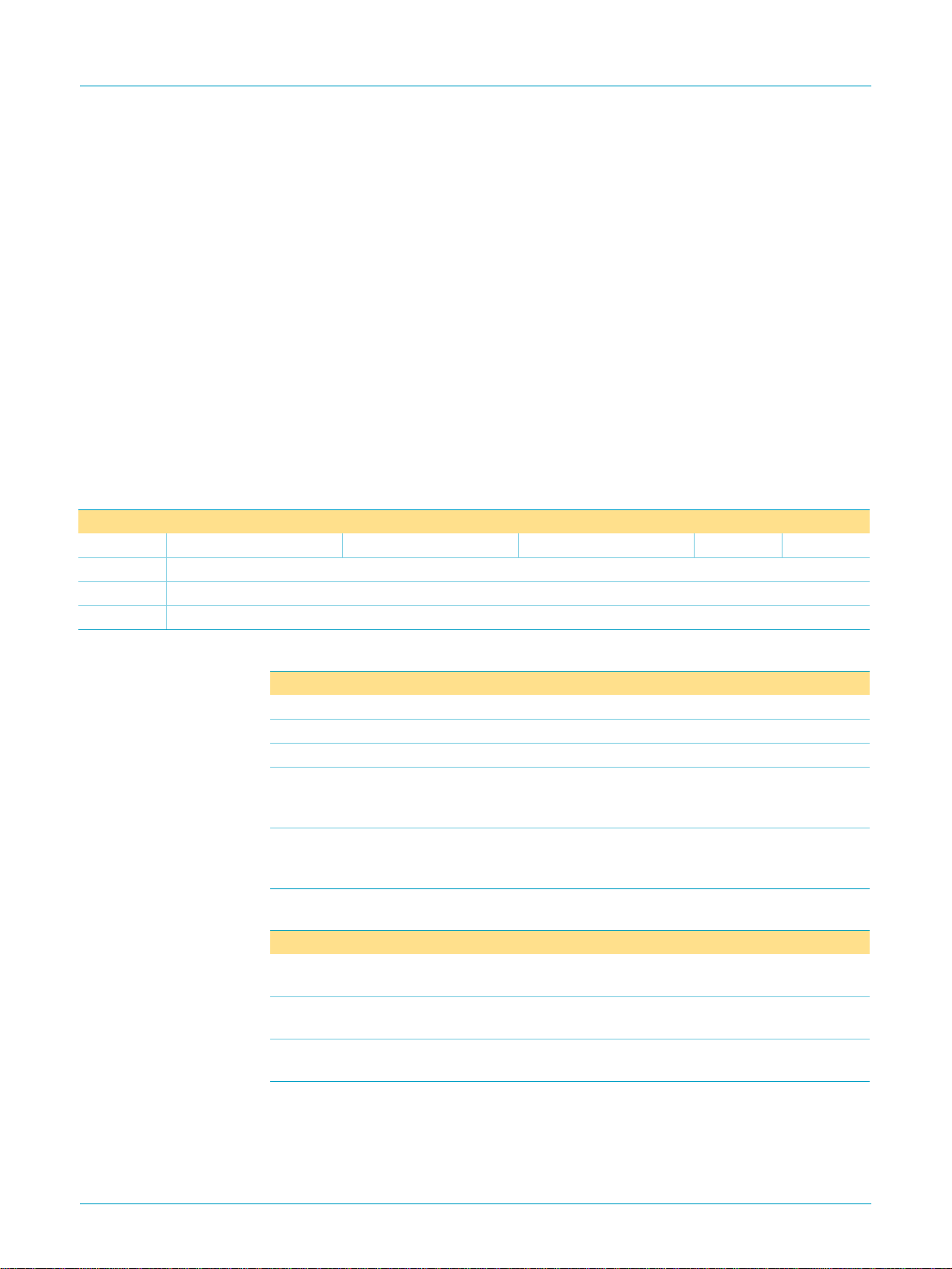

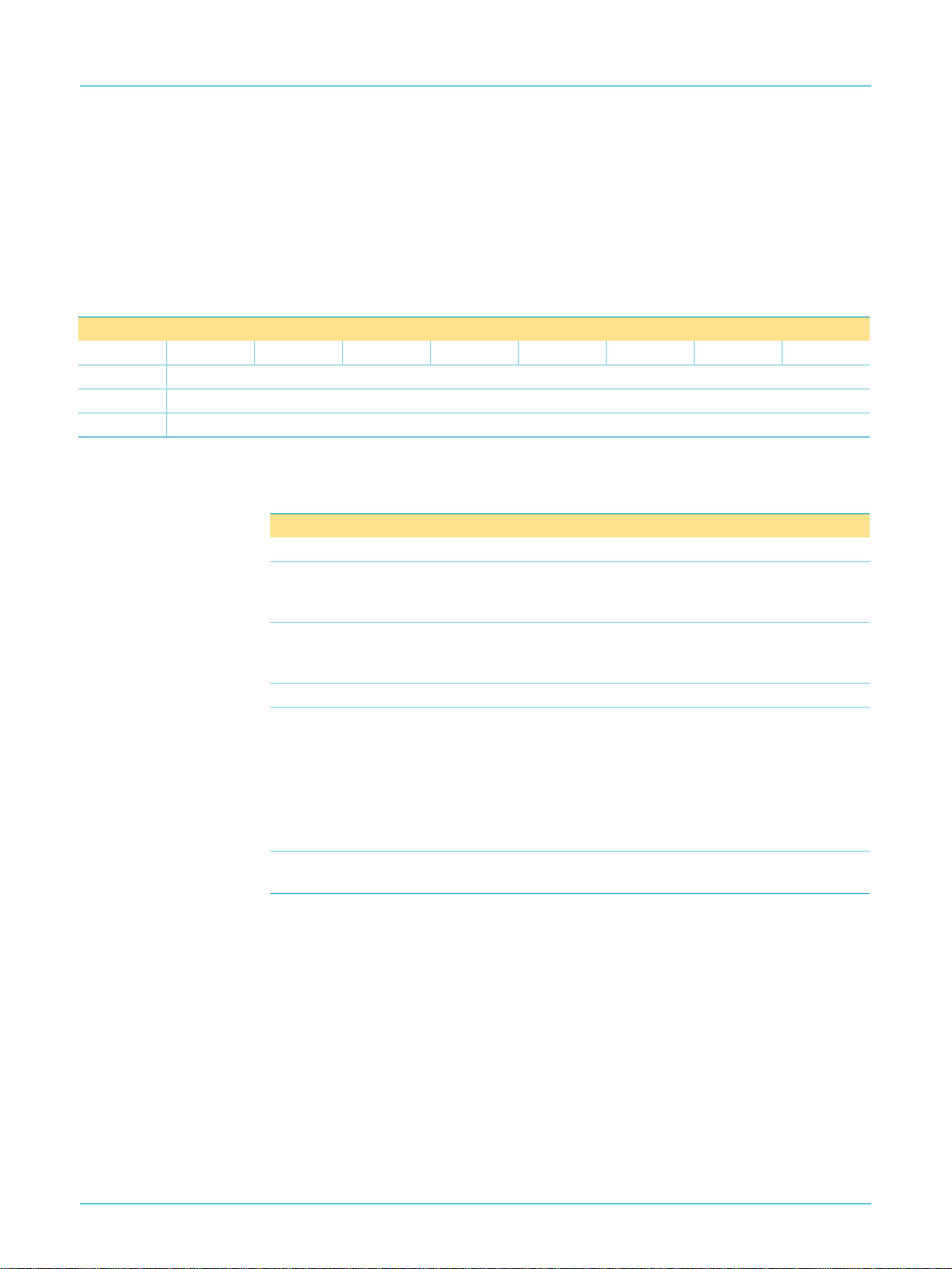

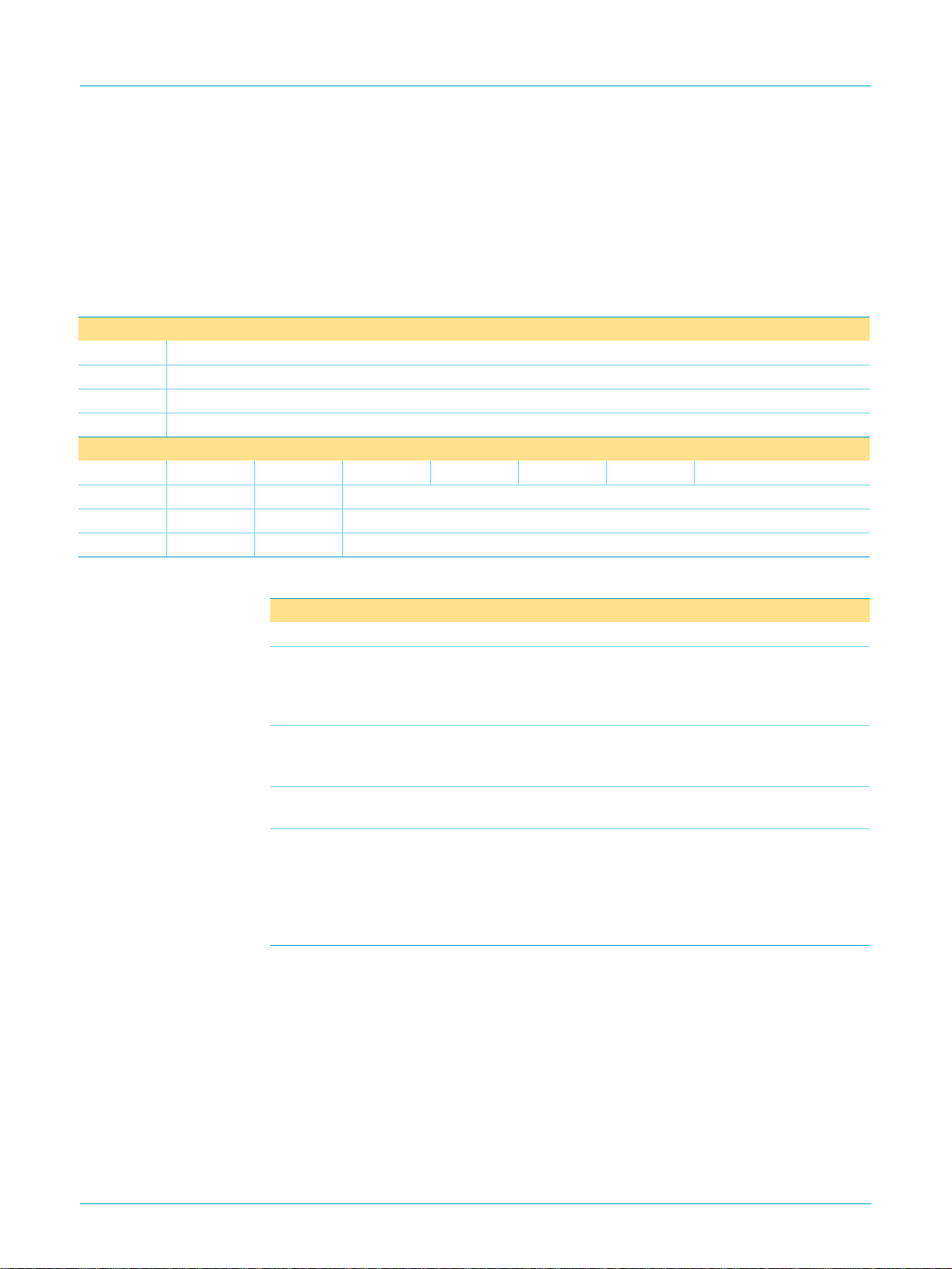

6. Pinning information

6.1 Pinning

dth

ISP1581

USB 2.0 HS interface device

CC(5.0)

V

SUSPEND

WAKEUP

DGND

XTAL1

64

63

62

61

60

1

DGND

V

CC(5.0)

V

reg(3.3)

MODE1

2

AGND

3

4

D−

5

6

D+

RPU

7

RREF

8

9

RESET

10

EOT

11

DREQ

12

DACK

13

DIOR

14

DIOW

15

INTRQ 33

16

CC(3.3)

XTAL2

V

59

58

ISP1581BD

DATA15

DATA14

57

56

DATA13

DATA12

55

54

DATA11

DATA10

53

52

DATA9

51

DATA8

50

DATA7

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

DATA6

DATA5

DATA4

DATA3

DATA2

V

CC(5.0)

DGND

DATA1

DATA0

AD7

AD6

V

CC(5.0)

DGND

AD5

AD4

AD3

17

CS1

18

CS0

19

BUS_CONF/DA0

20

MODE0/DA1

DA2

22

READY/IORDY

23

AGND

24

CC(3.3)

V

25

CS

26

27

DS/WR

(R/W)/RD

28

INT

29

ALE/A0

30

AD0

31

AD1

32

AD2 49

MBL248

21

Fig 2. Pin configuration LQFP64.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 4 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

6.2 Pin description

Table 2: Pin description for LQFP64

Symbol

DGND 1 - digital ground

V

CC(5.0)

AGND 3 - analog ground

V

reg(3.3)

D− 5 AI/O USB D− connection (analog)

D+ 6 AI/O USB D+ connection (analog)

RPU 7 AI connection for external pull-up resistor for USB D+ line;

RREF 8 AI connection for external bias resistor; must be connected to

MODE1 9 I selects function of pin ALE/A0 (in Split Bus mode only):

RESET 10 I reset input (Schmitt trigger); a LOW level produces an

EOT 11 I End Of Transfer input (programmable polarity, see

DREQ 12 I/O DMA request (programmable polarity); direction depends

DACK 13 I/O DMA acknowledge (programmable polarity); direction of

DIOR 14 I/O DMA read strobe (programmable polarity); direction

DIOW 15 I/O DMA write strobe (programmable polarity); direction

INTRQ 16 I interrupt request input from ATA/ATAPI peripheral

CS1 17 O chip select output for ATAPI device

CS0 18 O chip select output for ATAPI device

BUS_CONF/

DA0

ISP1581

USB 2.0 HS interface device

[1]

Pin Type

2 - supply voltage (3.3 or 5.0 V)

5 - regulated supply voltage (3.3 V ± 10%) from internal

19 I/O during power-up: input to select the bus configuration

[2]

Description

regulator; supplies internal analog circuits; used to connect

decoupling capacitor and 1.5 kΩ pull-up resistor on D+ line

Remark: Cannot be used to supply external devices.

must be connected to V

via a 1.5 kΩ resistor

reg(3.3)

ground via a 12.2 kΩ (± 0.1%) resistor

0 — ALE function (address latch enable)

1 — A0 function (address/data indicator).

Remark: Connect to V

asynchronous reset; connect to V

in Generic Processor mode.

CC(5.0)

for power-on reset

CC

(internal POR circuit)

Table 37); used in DMA slave mode only

on the bit MASTER in the DMA Hardware register (DMA

master: input, DMA slave: output); see Table 37

depends on bit MASTER in the DMA Hardware register

(DMA slave: input, DMA master: output); see Table 37

depends on bit MASTER in the DMA Hardware register

(DMA slave: input, DMA master: output); see Table 37

depends on bit MASTER in the DMA Hardware register

(DMA slave: input, DMA master: output); see Table 37

0 — Split Bus mode; multiplexed8-bit address/data bus on

AD[7:0], separate 8/16-bit DMA data bus on DATA[15:0]

1 — Generic Processor mode; separate 8-bit address on

AD[7:0], 16-bit DMA data bus on DATA[15:0].

normal operation: address output to select the task file

register of an ATAPI device

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 5 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

Table 2: Pin description for LQFP64

Symbol

[1]

Pin Type

[2]

…continued

Description

MODE0/DA1 20 I/O during power-up: input to select the read/write strobe

functionality in generic processor mode

0 — Motorola style: pin 26 is R/

1 — 8051 style: pin 26 is

W and pin 27 is DS

RD and pin 27 is WR

normal operation: address output to select the task file

register of an ATAPI device

DA2 21 O address output to select the task file register of an ATAPI

device

READY/

IORDY

22 I/O Generic processor mode: ready signal (READY; output)

A LOW level signals that ISP1581 is processing a previous

command or data and is not ready for the next command or

data transfer; a HIGH level signals that ISP1581 is ready

for the next microprocessor read or write.

Split Bus mode: DMA ready signal (IORDY; input); used

for accessing ATAPI peripherals (PIO and UDMA modes

only).

AGND 23 - analog ground

V

CC(3.3)

24 - supply voltage (3.3 V ± 10%); supplies internal digital

circuits

CS 25 I chip select input

W)/RD 26 I input; function is determined by input MODE0 at power-up:

(R/

MODE0 = 0 — pin functions as R/

MODE0 = 1 — pin functions as

W (Motorola style)

RD (8051 style).

DS/WR 27 I input; function is determined by input MODE0 at power-up:

MODE0 = 0 — pin functions as

MODE0 = 1 — pin functions as

DS (Motorola style)

WR (8051 style).

INT 28 O interrupt output; programmable polarity (active HIGH or

LOW) and signaling (edge or level triggered)

ALE/A0 29 I input; function determined by input MODE1 during

power-up:

MODE1 = 0 — address latch enable; a falling edge latches

the address on the multiplexed address/data bus (AD[7:0])

MODE1 = 1 — address/data selection on AD[7:0]; a logic 1

indicates that an address will be written at the next

WR

pulse; a logic 0 indicates that data will be written at the next

WR pulse; used in Split Bus mode only.

AD0 30 I/O bit 0 of multiplexed address/data

AD1 31 I/O bit 1 of multiplexed address/data

AD2 32 I/O bit 2 of multiplexed address/data

AD3 33 I/O bit 3 of multiplexed address/data

AD4 34 I/O bit 4 of multiplexed address/data

AD5 35 I/O bit 5 of multiplexed address/data

DGND 36 - digital ground

V

CC(5.0)

37 - supply voltage (3.3 or 5.0 V)

AD6 38 I/O bit 6 of multiplexed address/data

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 6 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

Table 2: Pin description for LQFP64

CC(5.0)

CC(3.3)

CC(5.0)

[1]

Pin Type

43 - supply voltage (3.3 or 5.0 V)

58 - supply voltage (3.3 V ± 10%); supplies internal digital

64 - supply voltage (3.3 or 5.0 V)

Symbol

AD7 39 I/O bit 7 of multiplexed address/data

DATA0 40 I/O bit 0 of bidirectional data

DATA1 41 I/O bit 1 of bidirectional data

DGND 42 - digital ground

V

DATA2 44 I/O bit 2 of bidirectional data

DATA3 45 I/O bit 3 of bidirectional data

DATA4 46 I/O bit 4 of bidirectional data

DATA5 47 I/O bit 5 of bidirectional data

DATA6 48 I/O bit 6 of bidirectional data

DATA7 49 I/O bit 7 of bidirectional data

DATA8 50 I/O bit 8 of bidirectional data

DATA9 51 I/O bit 9 of bidirectional data

DATA10 52 I/O bit 10 of bidirectional data

DATA11 53 I/O bit 11 of bidirectional data

DATA12 54 I/O bit 12 of bidirectional data

DATA13 55 I/O bit 13 of bidirectional data

DATA14 56 I/O bit 14 of bidirectional data

DATA15 57 I/O bit 15 of bidirectional data

V

XTAL2 59 O crystal oscillator output (12 MHz); connect a fundamental

XTAL1 60 I crystal oscillator input (12 MHz); connect a fundamental

DGND 61 - digital ground

WAKEUP 62 I wake-up input (edge triggered); a LOW-to-HIGH transition

SUSPEND 63 O ’suspend’ state indicator output (4 mA); used as a power

V

[2]

…continued

Description

circuits

parallel-resonant crystal; leavethis pin open when using an

external clock source on pin XTAL1

parallel-resonant crystal or an external clock source

(leaving pin XTAL2 unconnected)

generates a remote wake-up from ‘suspend’ state

switch control output (active LOW) for powered-off

application or as a resume signal to the CPU (active HIGH)

for powered-on application

[1] Symbol names with an overscore (e.g. NAME) represent active LOW signals.

[2] All outputs and I/O pins can source 4 mA of current.

7. Functional description

The ISP1581 is a high-speed USB device controller. It implements the USB 2.0/1.1

physical layer, the packet protocol layer and maintains up to 16 USB endpoints

concurrently (2 control, 14 configurable).

executed by means of external firmware.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 7 of 73

USB Chapter 9

protocol handling is

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

The ISP1581 has a fast general-purpose interface for communication with most types

of microcontrollers/processors. This Microcontroller Interface is configured by pins

BUS_CONF, MODE1 and MODE0 to accommodate most interface types. Two bus

configurations are available, selected via input BUS_CONF during power-up:

•

•

ISP1581

USB 2.0 HS interface device

Generic Processor mode (BUS_CONF = 1):

– AD[7:0]: 8-bit address bus (selects target register)

– DATA[15:0]: 16-bit data bus (shared by processor and DMA)

– Control signals: R/W and DS or RD and WR (selected via pin MODE0)

– DMA interface (generic slave mode only): uses lines DATA[15:0] as data bus,

DIOR and DIOW as dedicated read and write strobes.

Split Bus mode (BUS_CONF = 0):

– AD[7:0]: 8-bit local microprocessor bus (multiplexed address/data)

– DATA[15:0]: 16-bit DMA data bus

– Control signals: CS, ALE or A0 (selected via pin MODE1), R/W and DS or RD

and WR (selected via pin MODE0)

– DMA interface (master or slave mode): uses DIOR and DIOW as dedicated read

and write strobes.

For high-bandwidth data transfer, the integrated DMA handler can be invoked to

transfer data to/from external memory or devices. The DMA Interface can be

configured by writing to the proper DMA registers (see Section 9.4).

The ISP1581 supports high-speed USB 2.0 and full-speed USB 1.1 signaling.

Detection of the USB signaling speed is done automatically.

ISP1581 has 8 kbytes of internal FIFO memory, which is shared among the enabled

USB endpoints.

There are 14 configurable data endpoints and 2 control endpoints. Any of the 14 data

endpoints can be separately enabled or disabled. The endpoint type (interrupt,

isochronous or bulk) and packet size of these endpoints can be individually

configured depending on the requirements of the application. Optional double

buffering increases the data throughput of the data endpoints.

The ISP1581 requires a single supply of 3.0 V or 5.0 V, depending on the I/O voltage.

It has 5.0 V tolerant I/O pads and has an internal 3.3 V regulator for powering the

analog transceiver. It supports bus-powered operation with a ‘suspend’ current below

500 µA.

The ISP1581 operates on a 12 MHz crystal oscillator. An integrated 40× PLL clock

multiplier generates the internal sampling clock of 480 MHz.

7.1 USB 2.0 transceiver

The analog transceiver interfaces directly to the USB cable via integrated termination

resistors. The high-speed transceiver requires an external resistor (12.2 kΩ±0.1%)

between pin RREF and ground to ensure an accurate current mirror. A full-speed

transceiver is integrated as well. This makes the ISP1581 compliant with USB 2.0

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 8 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

and USB 1.1, supporting both the high-speed and full-speed physical layer. After

automatic speed detection, the Philips Serial Interface Engine sets the transceiver to

use either high-speed or full-speed signaling.

7.2 Philips Serial Interface Engine (SIE)

The Philips SIE implements the full USB protocol layer. It is completely hardwired for

speed and needs no firmware intervention. The functions of this block include:

synchronization pattern recognition, parallel/serial conversion, bit (de-)stuffing, CRC

checking/generation, Packet IDentifier (PID) verification/generation, address

recognition, handshake evaluation/generation.

7.3 Voltage regulators

Two 5 V to 3.3 V voltage regulators are integrated on-chip to separately supply the

analog transceiver and the internal logic. The analog supply voltage is available at pin

V

reg(3.3)

ISP1581

USB 2.0 HS interface device

to supply an external 1.5 kΩ pull-up resistor on the D+ line.

Remark: Pin V

cannot be used to supply external devices.

reg(3.3)

7.4 Memory Management Unit (MMU) and integrated RAM

The MMU and the integrated RAM provide the conversion between the USB speed

(full speed: 12 Mbit/s, high speed: 480 Mbit/s) and the Microcontroller Handler or the

DMA Handler. The data from the USB Bus is stored in the integrated RAM, which is

cleared only when the microcontroller clears the endpoint buffer or when the DMA

Handler has read/written all data from/to the endpoint buffer. A total of 8 kbytes RAM

is available for buffering.

7.5 SoftConnect

The connection to the USB is established by pulling the D+ line (for high-speed

devices) HIGH through a 1.5 kΩ pull-up resistor. In the ISP1581 an external 1.5 kΩ

pull-up resistor must be connected between pins RPU and V

connects the pull-up resistor to the D+ line, when bit SOFTCT in the Mode register is

set (see Table 7). After a hardware reset the pull-up resistor is disconnected by

default (SOFTCT = 0). Bit SOFTCT remains unchanged by a USB bus reset.

. The RPU pin

reg(3.3)

7.6 Bit clock recovery

The bit clock recovery circuit recovers the clock from the incoming USB data stream

using 4× over-sampling principle. It is able to track the jitter and the frequency drift as

specified by the USB specification.

7.7 Multiplying PLL oscillator

A 12 MHz to 480 MHz clock multiplier Phase-Locked Loop (PLL) is integrated

on-chip. This allows the use of a low-cost 12 MHz crystal, which also minimizes EMI.

No external components are needed for the operation of the PLL.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 9 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

7.8 Microcontroller Interface and Microcontroller Handler

The Microcontroller Interface allows direct interfacing to most microcontrollers. The

interface is configured at power-up via inputs BUS_CONF, MODE1 and MODE0.

When BUS_CONF is set to logic 1, the Microcontroller Interface switches to the

Generic Processor mode in which AD[7:0] is the 8-bit address bus and DATA[15:0]

is the separate 16-bit data bus. If BUS_CONF is made logic 0, the interface is in the

Split Bus mode, where AD[7:0] is the local microprocessor bus (multiplexed

address/data) and DATA[15:0] is used as the DMA bus.

If pin MODE0 is set to logic 1, pins RD and WR are the read and write strobes (8051

style). If pin MODE0 is logic 0, pins R/W and DS pins represent the direction and data

strobe (Motorola style).

When pin MODE1 is made logic 0, ALE is used to latch the multiplexed address on

pins AD[7:0]. If pin MODE1 is set to logic 1, A0 is used to indicate address or data.

Pin MODE1 is only used in Split Bus mode: in Generic Processor mode it must be

tied to V

The Microcontroller Handler allows the external microcontroller to access the register

set in the Philips SIE as well as the DMA Handler. The initialization of the DMA

configuration is done via the Microcontroller Handler.

CC(5.0)

ISP1581

USB 2.0 HS interface device

(logic 1).

7.9 DMA Interface and DMA Handler

The DMA block can be subdivided into two blocks: the DMA Handler and the DMA

Interface.

The firmware writes to the DMA Command register to start a DMA transfer (see

Table 30). The command opcode determines whether a generic DMA, PIO,MDMA or

UDMA transfer will start. The Handler interfaces to the same FIFO (internal RAM) as

used by the USB core. Upon receiving the DMA Command, the DMA Handler directs

the data from the internal RAM to the external DMA device and vice versa.

The DMA Interface configures the timings and how the DMA data is accessed. Data

can be transferred either using DIOR and DIOW strobes or by the DACK and DREQ

handshakes. The different DMA configurations are set up by writing to the DMA

Configuration register (see Table 35).

For an IDE-based storage interface, the applicable DMA modes are PIO (Parallel

I/O), MDMA (Multiword DMA; ATA), and UDMA (Ultra DMA; ATA).

For a generic DMA interface, the DMA modes that can be used are Generic DMA

(Slave) and MDMA (Master).

7.10 System Controller

The System Controller implements the USB power-down capabilities of the ISP1581.

Two modes are supported during ‘suspend’ state: powered-on and powered-off.

These modes are selected via bit PWROFF in the Mode register (see Table 7).

Registers are protected against data corruption during wake-up following a ‘resume’.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 10 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

USB 2.0 HS interface device

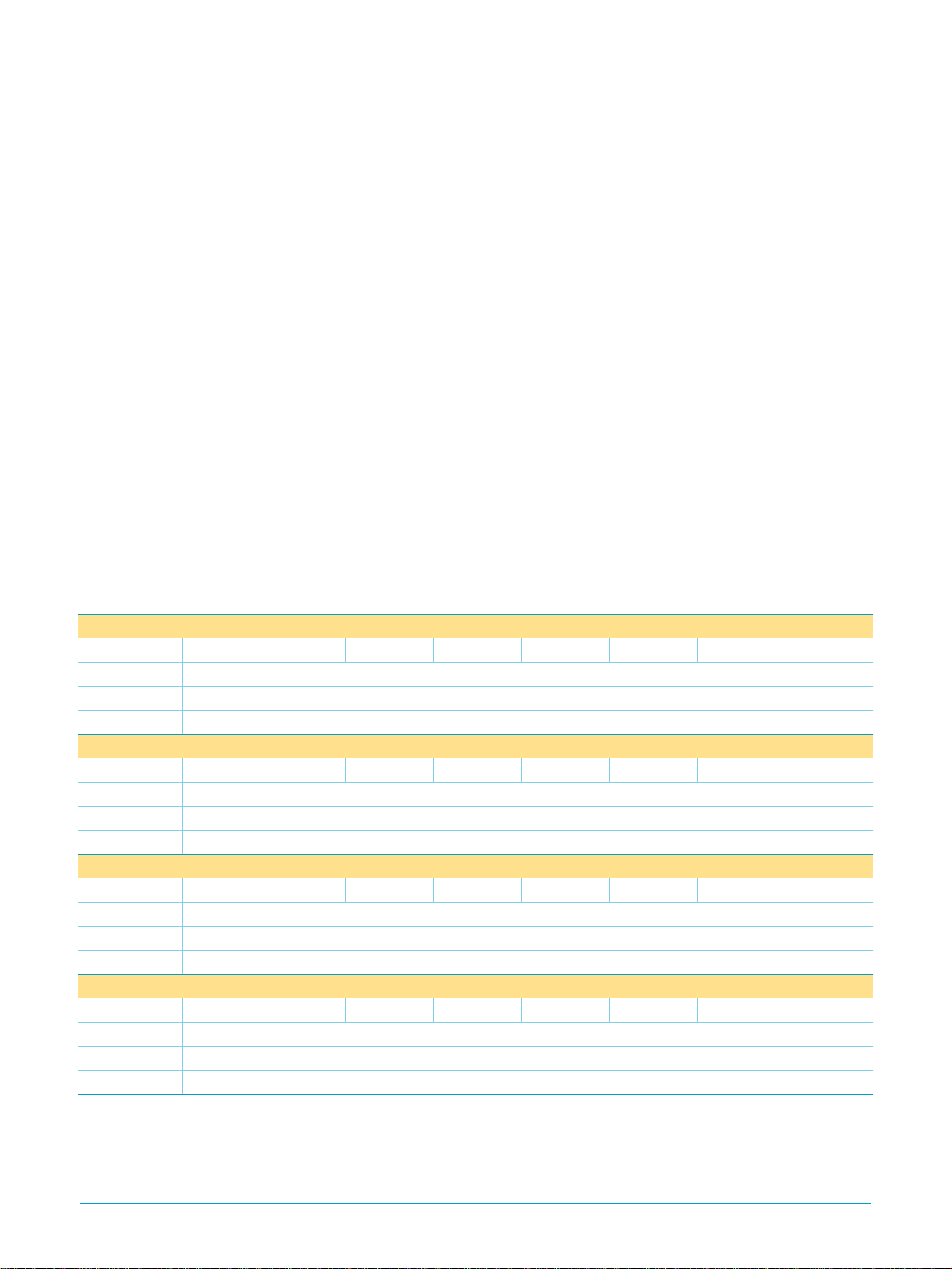

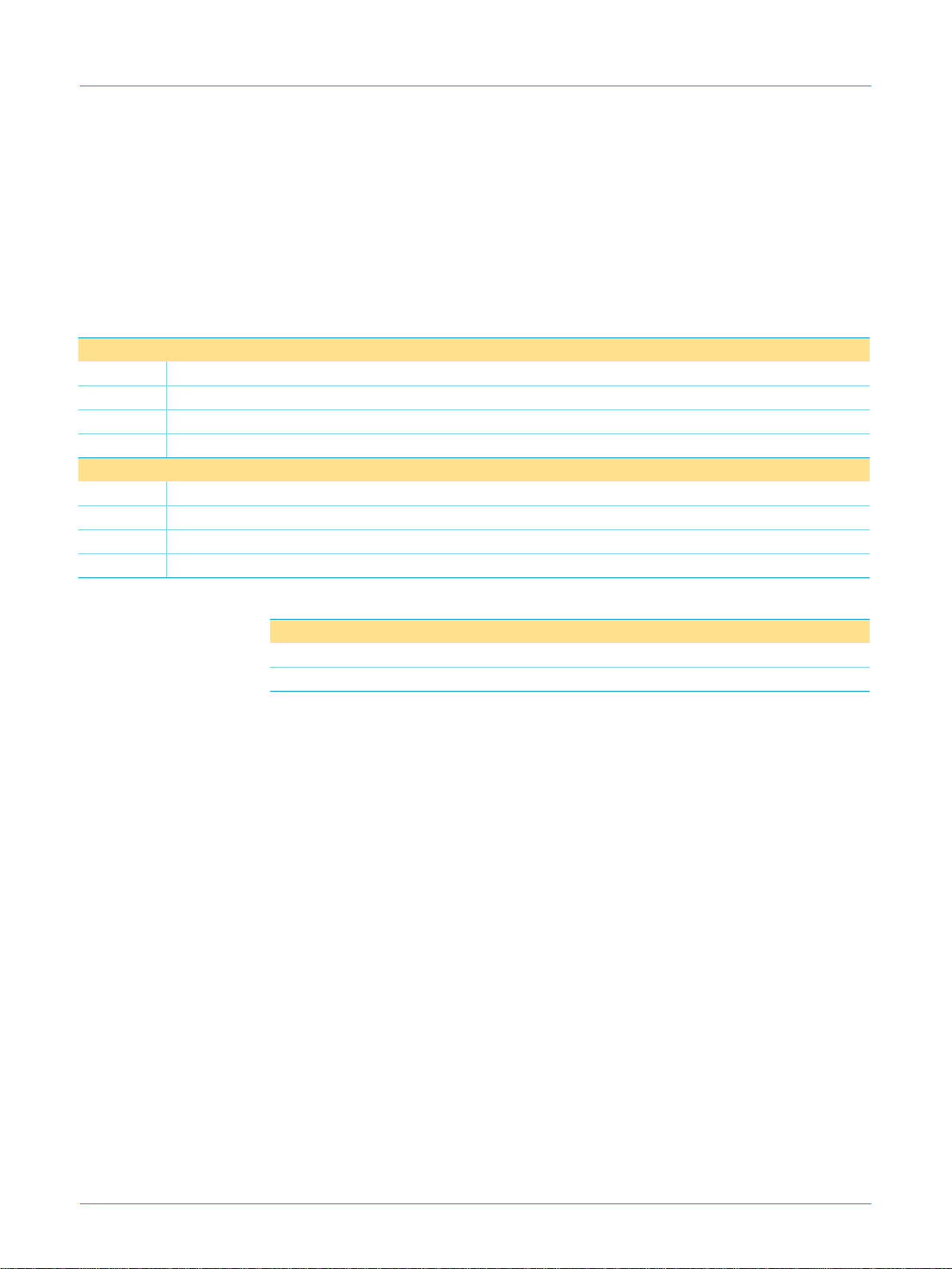

8. Modes of operation

The ISP1581 has two bus configuration modes, selected via pin BUS_CONF/DA0 at

power-up:

Split Bus mode (BUS_CONF = 0): 8-bit multiplexed address/data bus and

•

separate 8-bit/16-bit DMA bus

Generic Processor mode (BUS_CONF = 1); separate 8-bit address and 16-bit

•

data bus

Details of the bus configurations for each mode are given in Table 3. Typical interface

circuits for each mode are given in Section 13 “Application information”.

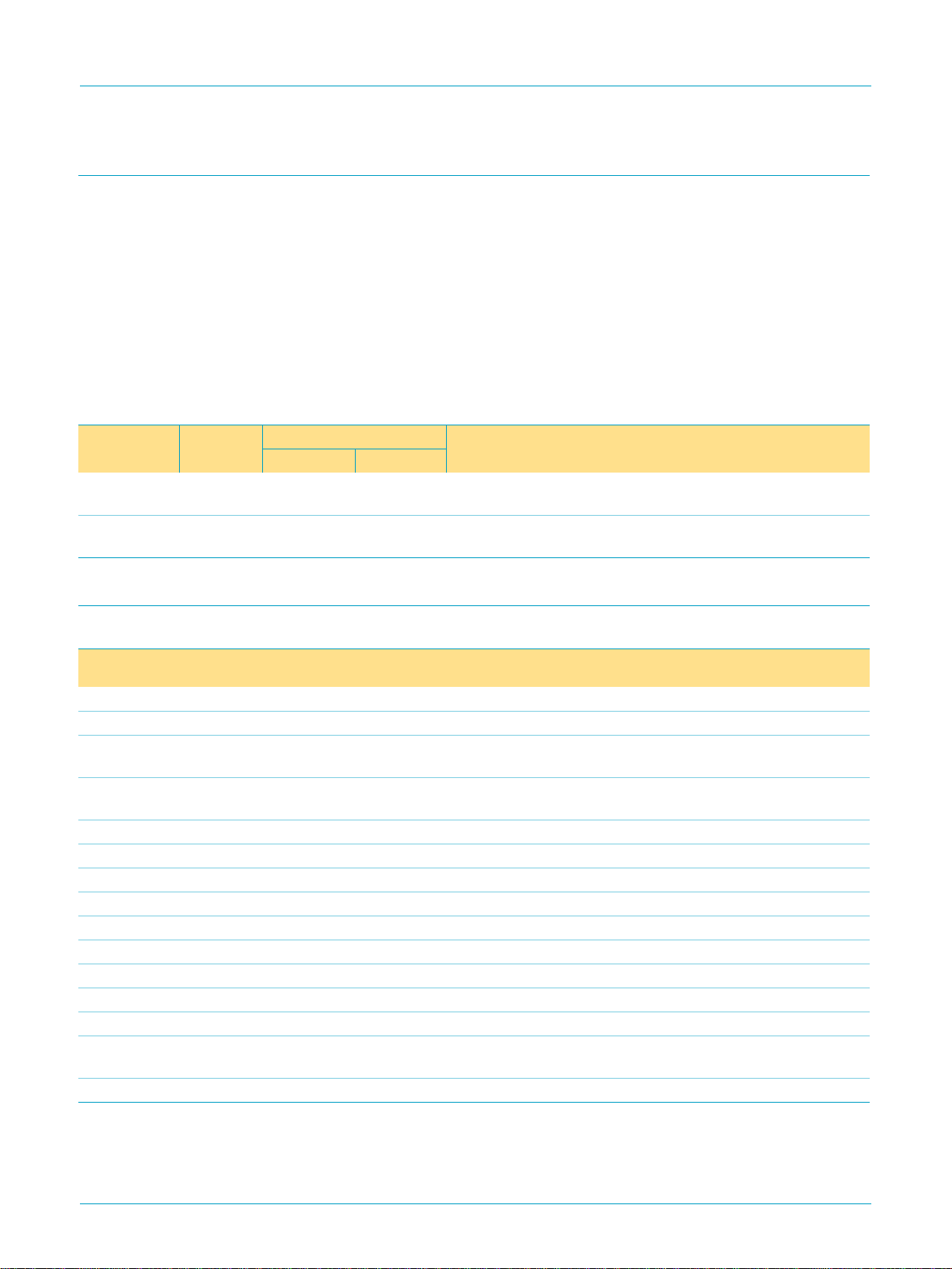

Table 3: Bus configuration modes

BUS_CONF PIO width DMA width Description

DMAWD = 0 DMAWD = 1

0 AD[7:0] D[7:0] D[15:0] Split Bus mode: multiplexed address/data on pins AD[7:0];

separate 8/16-bit DMA bus on pins DATA[15:0]

1 A[7:0]

D[15:0]

D[7:0] D[15:0] Generic Processor mode: separate 8-bit address on pins

AD[7:0]; 16-bit data (PIO and DMA) on pins DATA[15:0]

ISP1581

9. Register descriptions

Table 4: Register summary

Name Destination Address

(Hex)

Initialization registers

Address device 00 USB device address + enable 1

Mode device 0C power-down options, global interrupt

Interrupt Configuration device 10 interrupt sources, trigger mode, output

Interrupt Enable device 14 interrupt source enabling 4

DMA Configuration DMA controller 38 see DMA registers 2

DMA Hardware DMA controller 3C see DMA registers 1

Data flow registers

Endpoint Index endpoints 2C endpoint selection, data flow direction 1

Control Function endpoint 28 endpoint buffer management 1

Data Port endpoint 20 data access to endpoint FIFO 2

Buffer Length endpoint 1C packet size counter 2

Endpoint MaxPacketSize endpoint 04 maximum packet size 2

Endpoint Type endpoint 08 selects endpoint type: control,

Short Packet endpoint 24 short packet received on OUT endpoint 2

Description Size

enable, SoftConnect

polarity

isochronous, bulk or interrupt

(bytes)

1

1

2

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 11 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

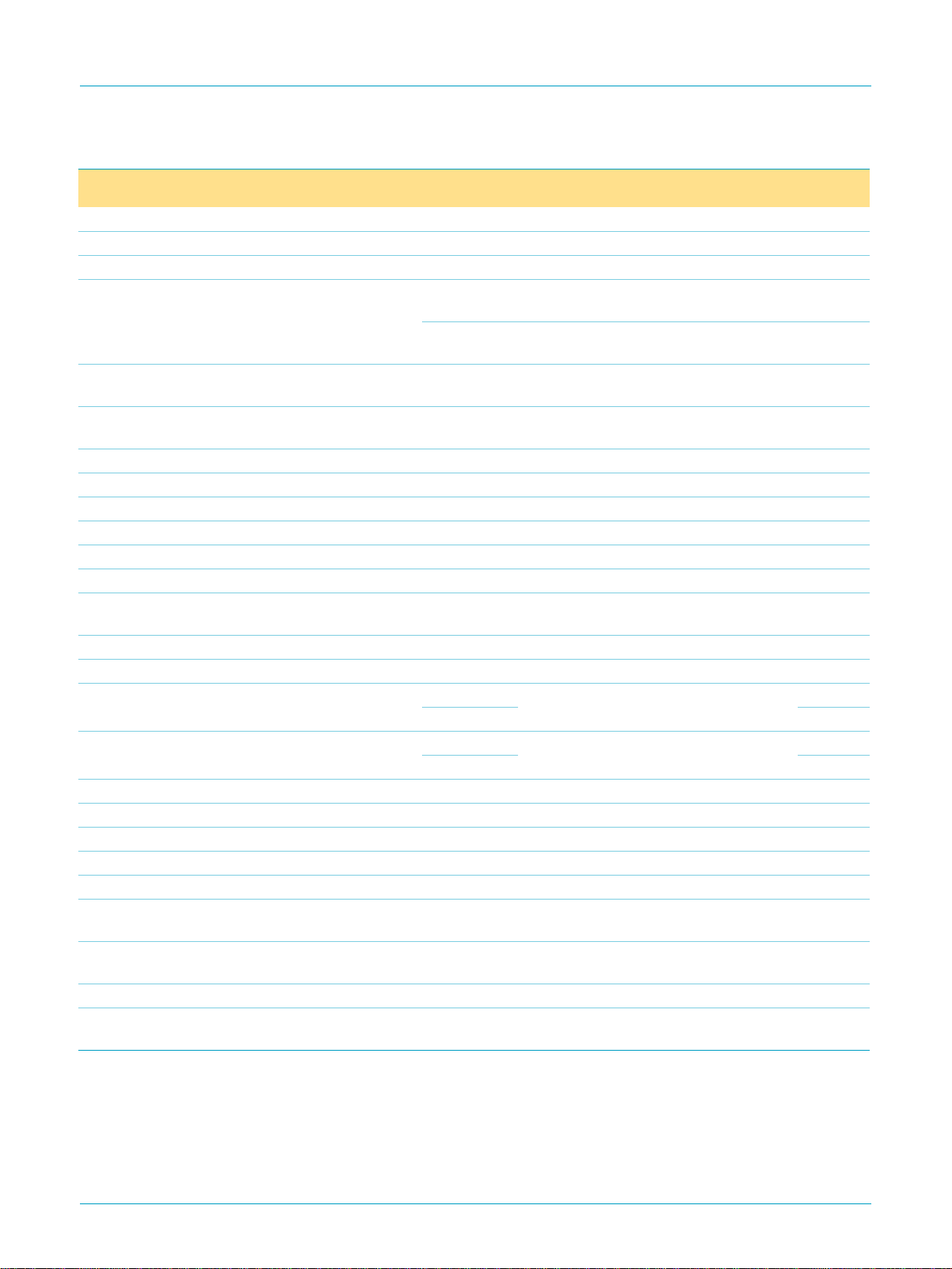

Table 4: Register summary

Name Destination Address

DMA registers

DMA Command DMA controller 30 controls all DMA transfers 1

DMA Transfer Counter DMA controller 34 sets byte count for DMA Transfer 4

DMA Configuration DMA controller 38 (byte 0) sets GDMA configuration (counter enable,

DMA Hardware DMA controller 3C endian type, master/slave selection, signal

1F0 Task File ATAPI peripheral 40 single address word register: byte 0 (lower

1F1Task File ATAPI peripheral 48 IDE device access 1

1F2 Task File ATAPI peripheral 49 IDE device access 1

1F3 Task File ATAPI peripheral 4A IDE device access 1

1F4 Task File ATAPI peripheral 4B IDE device access 1

1F5 Task File ATAPI peripheral 4C IDE device access 1

1F6 Task File ATAPI peripheral 4D IDE device access 1

1F7 Task File ATAPI peripheral 44 IDE device access (write only; reading

3F6 Task File ATAPI peripheral 4E IDE device access 1

3F7 Task File ATAPI peripheral 4F IDE device access 1

DMA Interrupt Reason DMA controller 50 (byte 0) shows reason (source) for DMA interrupt 1

DMA Interrupt Enable DMA controller 54 (byte 0) enables DMA interrupt sources 1

DMA Endpoint DMA controller 58 selects endpoint FIFO, data flow direction 1

DMA Strobe Timing DMA controller 60 strobe duration in UDMA/MDMA mode 1

General registers

Interrupt device 18 shows interrupt sources 4

Chip ID device 70 product ID code and hardware version 3

Frame Number device 74 last successfully received Start Of Frame:

Scratch device 78 allows save/restore of firmware status

Unlock Device device 7C re-enables register access after ‘suspend’ 2

Test Mode PHY 84 direct setting of D+, D− states, loopback

…continued

Description Size

(Hex)

burst length, data strobing, bus width)

39 (byte 1) sets ATA configuration (IORDY enable,

mode selection: ATA/UDMA/MDMA/PIO)

polarity for DACK, DREQ, DIOW, DIOR

byte) is accessed first

returns 00H)

51 (byte 1) 1

55 (byte 1) 1

lower byte (byte 0) is accessed first

during ‘suspend’

mode, internal transceiver test (PHY)

(bytes)

1

1

1

2

1

2

2

1

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 12 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

9.1 Register access

Register access depends on the bus width used:

•

•

Endpoint specific registers are indexed via the Endpoint Index register. The target

endpoint must be selected first, before accessing the following registers:

•

•

•

•

•

•

9.2 Initialization registers

ISP1581

USB 2.0 HS interface device

8-bit bus: multi-byte registers are accessed lower byte (LSB) first.

16-bit bus: for single-byte registers the upper byte (MSB) must be ignored.

Buffer Length

Control Function

Data Port

Endpoint MaxPacketsize

Endpoint Type

Short Packet.

9.2.1 Address register (address: 00H)

This register is used to set the USB assigned address and enable the USB device.

Table 5 shows the Address register bit allocation.

The DEVEN and DEVADDR bits will be cleared whenever a bus reset, a power-on

reset or a soft reset occurs.

In response to the standard USB request SET_ADDRESS, the firmware must write

the (enabled) device address to the Address register, followed by sending an empty

packetto the host. The new device address is activated when the host acknowledges

the empty packet.

Table 5: Address register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol DEVEN DEVADDR[6:0]

Reset 0 00H

Bus reset 0 00H

Access R/W R/W

Table 6: Endpoint Configuration register: bit description

Bit Symbol Description

7 DEVEN A logic 1 enables the device.

6 to 0 DEVADDR[6:0] This field specifies the USB device address.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 13 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

9.2.2 Mode register (address: 0CH)

This register consists of 1 byte (bit allocation: see Table 7). In 16-bit bus mode the

upper byte is ignored.

The Mode register controls the resume, suspend and wake-up behaviour, interrupt

activity, soft reset, clock signals and SoftConnect operation. This register also

controls the Power Off mode during ‘suspend’ state.

Table 7: Mode register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol CLKAON SNDRSU GOSUSP SFRESET GLINTENA WKUPCS PWROFF SOFTCT

Reset 00000000

Bus reset 0 0 0 0 unchanged 0 unchanged unchanged

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 8: Mode register: bit description

Bit Symbol Description

7 CLKAON Clock Always On: A logic 1 indicates that the internal clocks

are always running even during ‘suspend’ state. A logic 0

switches off the internal oscillator and PLL, when they are not

needed. During ‘suspend’ state, this bit must be set to logic 0 to

meet the suspend current requirements. The clock is stopped

after a delay of approximately 2 ms, following the setting of bit

GOSUSP.

6 SNDRSU Send Resume: Writing a logic 1 followed by a logic 0 will

generate an upstream ‘resume’ signal of 10 ms duration, after a

5 ms delay.

5 GOSUSP Go Suspend: Writing a logic 1 followed by a logic 0 will activate

‘suspend’ mode.

4 SFRESET Soft Reset: Writing a logic 1 followed by a logic 0 will enable a

software-initiated reset to ISP1581. A soft reset is similar to a

hardware-initiated reset (via the

3 GLINTENA Global Interrupt Enable: A logic 1 enables all interrupts.

Individual interrupts can be masked OFF by clearing the

corresponding bits in the Interrupt Enable register. Bus reset

value: unchanged.

2 WKUPCS Wake-up on Chip Select: A logic 1 enables remote wake-up

via a LOW level on input

1 PWROFF Power Off mode: A logic 1 enables powering-off during

‘suspend’ state. Output SUSPEND is configured as a power

switch control signal for external devices (HIGH during

‘suspend’). Bus reset value: unchanged.

0 SOFTCT SoftConnect: A logic 1 enables the connection of the 1.5 kΩ

pull-up resistor on pin RPU to the D+ line. Bus reset value:

unchanged.

RESET pin).

CS.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 14 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

9.2.3 Interrupt Configuration register (address: 10H)

This 1-byte register determines the behaviour and polarity of the INT output. The bit

allocation is shown in Table 9. When the USB SIE receives or generates a ACK, NAK

or STALL, it will generate interrupts depending on three Debug mode bit fields:

CDBGMOD[1:0]: interrupts for the Control endpoint 0

•

DDBGMODIN[1:0]: interrupts for the DATA IN endpoints 1 to 7

•

DDBGMODOUT[1:0]: interrupts for the DATA OUT endpoints 1 to 7.

•

The Debug mode settings for CDBGMOD, DDBGMODIN and DDBGMODOUT allow

the user to individually configure when the ISP1581 will send an interrupt to the

external microprocessor. Table 11 lists the available combinations.

Bit INTPOL controls the signal polarity of the INT output (active HIGH or LOW, rising

or falling edge). For level-triggering bit INTLVL must be made logic 0. By setting

INTLVL to logic 1 an interrupt will generate a pulse of 60 ns (edge-triggering).

Table 9: Interrupt Configuration register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol CDBGMOD[1:0] DDBGMODIN[1:0] DDBGMODOUT[1:0] INTLVL INTPOL

Reset 03H 03H 03H 0 0

Bus reset 03H 03H 03H unchanged unchanged

Access R/W R/W R/W R/W R/W

Table 10: Interrupt Configuration register: bit description

Bit Symbol Description

7 to 6 CDBGMOD[1:0] Control 0 Debug Mode: values see Table 11

5 to 4 DDBGMODIN[1:0] Data Debug Mode IN: values see Table 11

3 to 2 DDBGMODOUT[1:0] Data Debug Mode OUT: values see Table 11

1 INTLVL Interrupt Level: selects the signaling mode on output

INT (0 = level, 1 = pulsed). In pulsed mode an interrupt

produces a 60 ns pulse. Bus reset value: unchanged.

0 INTPOL Interrupt Polarity: selects signal polarity on output INT

(0 = active LOW, 1 = active HIGH). Bus reset value:

unchanged.

Table 11: Debug mode settings

Value CDBGMOD DDBGMODIN DDBGMODOUT

00H Interrupt on all ACK,

STALL and NAK

01H Interrupt on all ACK and

STALL

1XH Interrupt on all ACK,

STALL and first NAK

[1] First NAK: the first NAK on an IN or OUT token after a previous ACK response.

Interrupt on all ACK

and NAK

Interrupt on ACK Interrupt on ACK, STALL and

Interrupt on all ACK

[1]

and first NAK

[1]

Interrupt on all ACK, STALL,

NYET and NAK

NYET

Interrupt on all ACK, STALL,

NYET and first NAK

[1]

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 15 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

9.2.4 Interrupt Enable register (address: 14H)

This register enables/disables individual interrupt sources. The interrupt for each

endpoint can be individually controlled via the associated IEPnRX or IEPnTX bits (‘n’

representing the endpoint number). All interrupts can be globally disabled via bit

GLINTENA in the Mode Register (see Table 7).

An interrupt is generated when the USB SIE receives or generates an ACK, NAK or

STALL on the USB bus. The interrupt generation depends on the Debug mode

settings of bit fields CDBGMOD, DDBGMODIN and DDBGMODOUT.

All data IN transactions use the Transmit buffers (TX), which are handled by the

DDBGMODIN bits. All data OUT transactions go via the Receive buffers (RX), which

are handled by the DDBGMODOUT bits. Transactions on Control endpoint 0 (IN,

OUT and SETUP) are handled by the CDBGMOD bits.

Interrupts caused by events on the USB bus (SOF, Pseudo SOF, suspend, resume,

bus reset, Setup and High Speed Status) can also be controlled individually. A bus

reset disables all enabled interrupts except bit IEBRST (bus reset), which remains

unchanged.

ISP1581

USB 2.0 HS interface device

The Interrupt Enable Register consists of 4 bytes. The bit allocation is given in

Table 12.

Table 12: Interrupt Enable register: bit allocation

Bit 31 30 29 28 27 26 25 24

Symbol reserved reserved reserved reserved reserved reserved IEP7TX IEP7RX

Reset 00000000

Bus Reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 23 22 21 20 19 18 17 16

Symbol IEP6TX IEP6RX IEP5TX IEP5RX IEP4TX IEP4RX IEP3TX IEP3RX

Reset 00000000

Bus Reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 15 14 13 12 11 10 9 8

Symbol IEP2TX IEP2RX IEP1TX IEP1RX IEP0TX IEP0RX reserved IEP0SETUP

Reset 00000000

Bus Reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7 6 5 4 3 2 1 0

Symbol reserved IEDMA IEHS_STA IERESM IESUSP IEPSOF IESOF IEBRST

Reset 00000000

Bus Reset 0000000unchanged

Access R/W R/W R/W R/W R/W R/W R/W R/W

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 16 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

Table 13: Interrupt Enable register: bit description

Bit Symbol Description

31 to 26 - reserved; must write logic 0

25 to 12 IEP7TX to

11 IEP0TX A logic 1 enables interrupt from the Control IN endpoint 0.

10 IEP0RX A logic 1 enables interrupt from the Control OUT endpoint 0.

9 - reserved

8 IEP0SETUP A logic 1 enables the interrupt for the Setup data received on

7 - reserved

6 IEDMA A logic 1 enables interrupt upon DMA status change detection.

5 IEHS_STA A logic 1 enables interrupt upon detection of a High Speed

4 IERESM A logic 1 enables interrupt upon detection of a ‘resume’ state.

3 IESUSP A logic 1 enables interrupt upon detection of a ‘suspend’ state.

2 IEPSOF A logic 1 enables interrupt upon detection of a Pseudo SOF.

1 IESOF A logic 1 enables interrupt upon detection of an SOF.

0 IEBRST A logic 1 enables interrupt upon detection of a bus reset.

ISP1581

USB 2.0 HS interface device

A logic 1 enables interrupt from the indicated endpoint.

IEP1RX

endpoint 0.

Status change.

9.2.5 DMA Configuration register (address: 38H)

See Section 9.4.3.

9.2.6 DMA Hardware register (address: 3CH)

See Section 9.4.4.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 17 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

9.3 Data flow registers

9.3.1 Endpoint Index register (address: 2CH)

The Endpoint Index register selects a target endpoint for register access by the

microcontroller. The register consists of 1 byte and the bit allocation is shown in

Table 14. The following registers are indexed:

Endpoint MaxPacketsize

•

Endpoint Type

•

Buffer Length

•

Data Port

•

Short Packet

•

Control Function.

•

For example, to access the OUT data buffer of endpoint 1 via the Data Port register,

the Endpoint Index register has to be written first with 02H.

Table 14: Endpoint Index register: bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol reserved reserved EP0SETUP ENDPIDX[3:0] DIR

Reset 0 0 0 00H 0

Bus reset 0 0 0 00H 0

Access R/W R/W R/W R/W R/W

Table 15: Endpoint Index register: bit description

Bit Symbol Description

7 to 6 - reserved

5 EP0SETUP Selects the SETUP buffer for Endpoint 0:

0 — EP0 data buffer

1 — SETUP buffer.

Must be logic 0 for access to other endpoints than Endpoint 0.

4 to 1 ENDPIDX[3:0] Endpoint Index: Selects the target endpoint for register access

of Buffer Length, Control Function, Data Port, Endpoint Type,

MaxPacketSize and Short Packet.

0 DIR Direction bit: Sets the target endpoint as IN or OUT endpoint:

0 — target endpoint refers to OUT (RX) FIFO

1 — target endpoint refers to IN (TX) FIFO.

Table 16: Addressing of Endpoint 0 buffers

Buffer name EP0SETUP ENDPIDX DIR

SETUP 1 00H 0

Data OUT 0 00H 0

Data IN 0 00H 1

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 18 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

9.3.2 Control Function register (address: 28H)

The Control Function register is used to perform the buffer management on the

endpoints. It consists of 1 byte and the bit configuration is given in Table 17.The

register bits can stall, clear or validate any enabled data endpoint. Before accessing

this register, the Endpoint Index register must be written first to specify the target

endpoint.

Table 17: Control Function register: bit allocation

Bit 7 6 5 4 3 2 1 0

[1]

Symbol reserved reserved reserved CLBUF VENDP reserved STATUS

Reset 00000000

Bus reset 00000000

Access R/W R/W R/W R/W R/W R/W R/W R/W

[1] Only applicable for Endpoint 0.

Table 18: Control Function register: bit description

Bit Symbol Description

7 to 5 - reserved.

4 CLBUF Clear Buffer: A logic 1 clears the RX buffer of the indexed

endpoint; the TX buffer is not affected. Before new data can be

received, old data in the buffer must be cleared first.

3 VENDP Validate Endpoint: A logic 1 validates the data in the TX FIFO

of an IN endpoint for sending on the next IN token. The FIFO

byte count is below or equal to the Endpoint MaxPacketSize.

2 - reserved

1 STATUS Status Acknowledge: This bit controls the generation of ACK

or NAK during the status stage of a SETUP packet. It is

automatically cleared upon completion of the status stage and

upon receiving a SETUP token.

0 — sends NAK

1 — sends empty packet following IN token (host-to-device) or

ACK following OUT token (device-to-host).

0 STALL Stall Endpoint: A logic 1 stalls the indexed endpoint. This bit is

not applicable for isochronous transfers.

STALL

9.3.3 Data Port register (address: 20H)

This 2-byte register provides direct access for a microcontroller to the FIFO of the

indexedendpoint. In case of an 8-bit bus the upper byte is not used. The bit allocation

is shown in Table 19.

Device to host (IN endpoint): After each write action an internal counter is

auto-incremented (by 2 for a 16-bit access, by 1 for an 8-bit access) to the next

location in the TX FIFO. When all bytes have been written, the buffer can be validated

via the Control Function register (bit VENDP). The data packet will then be sent on

the next IN token.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 19 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

Host to device (OUT endpoint): After each read action an internal counter is

auto-decremented (by 2 for a 16-bit access, by 1 for an 8-bit access) to the next

location in the RX FIFO. When all bytes have been read, the buffer contents can be

cleared via the Control Function register (bit CLBUF). A new data packet can then be

received on the next OUT token.

Remark: The buffer can be validated or cleared automatically by using the Buffer

Length register (see Table 21).

Table 19: Data Port register: bit allocation

Bit 15 14 13 12 11 10 9 8

Symbol DATAPORT[15:8]

Reset 00H

Bus reset 00H

Access R/W

Bit 7 6 5 4 3 2 1 0

Symbol DATAPORT[7:0]

Reset 00H

Bus reset 00H

Access R/W

Table 20: Data Port register: bit description

Bit Symbol Description

15 to 8 DATAPORT[15:8] data (upper byte); not used in 8-bit bus mode

7 to 0 DATAPORT[7:0] data (lower byte)

9.3.4 Buffer Length register (address: 1CH)

This 2-byte register determines the current packet size (DATACOUNT) of the indexed

endpoint FIFO. The bit allocation is given in Table 21.

The Buffer Length register is automatically loaded with the FIFO size, when the

Endpoint MaxPacketSize register is written (see Table 22). A smaller value can be

written when required. After a bus reset the Buffer Length register is made zero.

IN endpoint: When writing bytes into the TX FIFO, the buffer is automatically

validatedwhen DATACOUNT exceeds MaxPacketSize. During the subsequent packet

transmission DATACOUNT is decremented with the number of bytes sent. This

process is repeated until the number of remaining bytes is less than MaxPacketSize

(case I) or zero (case II). In case I, the remaining bytes are automatically validated

and a short packet is sent. In case II, a final empty packet will be appended if bit

NOEMPKT in the Endpoint Type register is cleared (see Table 24). Otherwise (if bit

NOEMPKT is set), data transfer is considered finished when the buffer is empty.

OUT endpoint: The DATACOUNT value is automatically initialized to the number of

data bytes sent by the host on each ACK. After reading DATACOUNT bytes from the

RX buffer, the buffer is automatically cleared to allow the next packet to be received

from the host.

Remark: For a 16-bit bus, the last byte of an odd-sized packet is output as the lower

byte (LSB).

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 20 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

Table 21: Buffer Length register: bit allocation

Bit 15 14 13 12 11 10 9 8

Symbol DATACOUNT[15:8]

Reset 00H

Bus reset 00H

Access R/W

Bit 7 6 5 4 3 2 1 0

Symbol DATACOUNT[7:0]

Reset 00H

Bus reset 00H

Access R/W

9.3.5 Endpoint MaxPacketSize register (address: 04H)

This register determines the maximum packet size for all endpoints except Control 0.

The register contains 2 bytes and the bit allocation is given in Table 22.

Each time the register is written, the Buffer Length registers of all endpoints are

re-initialized to the FFOSZ field value. The NTRANS bits control the number of

transactions allowed in a single micro-frame (for high-speed operation only).

Table 22: Endpoint MaxPacketSize register: bit allocation

Bit 15 14 13 12 11 10 9 8

Symbol reserved reserved reserved NTRANS[1:0] FFOSZ[10:8]

Reset 0 0 0 00H 00H

Bus reset 0 0 0 00H 00H

Access R/W R/W R/W R/W R/W

Bit 7 6 5 4 3 2 1 0

Symbol FFOSZ[7:0]

Reset 00H

Bus reset 00H

Access R/W

Table 23: Endpoint MaxPacketSize register: bit description

Bit Symbol Description

15 to 13 reserved reserved

12 to 11 NTRANS[1:0] Number of Transactions (HS mode only):

0 — 1 packet per microframe

1 — 2 packets per microframe

2 — 3 packets per microframe

3 — reserved.

10 to 0 FFOSZ[10:0] FIFO Size: Sets the FIFO size in bytes for the indexed endpoint.

Applies to both HS and FS operation.

Remark: A FIFO size of zero will disable the endpoint.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 21 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Philips Semiconductors

ISP1581

USB 2.0 HS interface device

9.3.6 Endpoint Type register (address: 08C)

This register sets the Endpoint type of the indexed endpoint: control, isochronous,

bulk or interrupt. It also serves to enable the endpoint and configure it for double

buffering. Automatic generation of an empty packet for a zero length TX buffer can be

disabled via bit NOEMPKT. The register contains 2 bytes and the bit allocation is

shown in Table 24.

Table 24: Endpoint Type register: bit allocation

Bit 15 14 13 12 11 10 9 8

Symbol reserved

Reset 00H

Bus reset 00H

Access R/W

Bit 7 6 5 4 3 2 1 0

Symbol reserved reserved reserved NOEMPKT ENABLE DBLBUF ENDPTYP[1:0]

Reset 000000 00H

Bus reset 000000 00H

Access R/W R/W R/W R/W R/W R/W R/W

Table 25: Endpoint Type register: bit description

Bit Symbol Description

15 to 5 reserved reserved.

4 NOEMPKT No Empty Packet: A logic 0 causes an empty packet to be

appended to the next IN token of the USB data, if the Buffer

Length register or the Endpoint MaxPacketSize register is zero.

A logic 1 disables this function.

3 ENABLE Endpoint Enable: A logic 1 enables the FIFO of the indexed

endpoint. The memory size is allocated as specified in the

Endpoint MaxPacketSize register. A logic 0 disables the FIFO.

2 DBLBUF Double Buffering: A logic 1 enables double buffering for the

indexed endpoint. A logic 0 disables double buffering.

1 to 0 ENDPTYP[1:0] Endpoint Type: These bits select the endpoint type as follows:

00H — control

01H — isochronous

02H — bulk

03H — interrupt.

9.3.7 Short Packet register (address: 24H)

This read-only register is applicable only for OUT endpoints. It contains 2 bytes and

the bit allocation is shown in Table 26.

If the number of bytes of a received packet is less than the value specified in the

Endpoint MaxPacketSize register (see Table 22), the corresponding short packet

status bit (OUTnSH) is set. The Short Packet register is updated on every

successfully received new packet.

9397 750 07648

Objective specification Rev. 02 — 23 October 2000 22 of 73

© Philips Electronics N.V. 2000. All rights reserved.

Loading...

Loading...