Philips 83C654 Datasheet

INTEGRATED CIRCUITS

83C654

CMOS single-chip 8-bit microcontroller

Product specification

Supersedes data of 1996 Aug 15

IC20 Data Handbook

1998 Jan 06

Philips Semiconductors Product specification

83C654CMOS single-chip 8-bit microcontroller

DESCRIPTION

The P83C654 Single-Chip 8-Bit

Microcontroller is manufactured in an

advanced CMOS process and is a derivative

of the 80C51 microcontroller family. The

83C654 has the same instruction set as the

80C51. Two versions of the derivative exist:

83C654 — 16k bytes mask programmable

ROM

87C654 — EPROM version (described in a

separate data sheet)

This device provides architectural

enhancements that make it applicable in a

variety of applications for general control

systems. The 83C654 contains a non-volatile

16k × 8 read-only program memory, a volatile

256 × 8 read/write data memory, four 8-bit I/O

ports, two 16-bit timer/event counters

(identical to the timers of the 80C51), a

multi-source, two-priority-level, nested

interrupt structure, an I

2

C interface, UART

and on-chip oscillator and timing circuits. For

systems that require extra capability, the

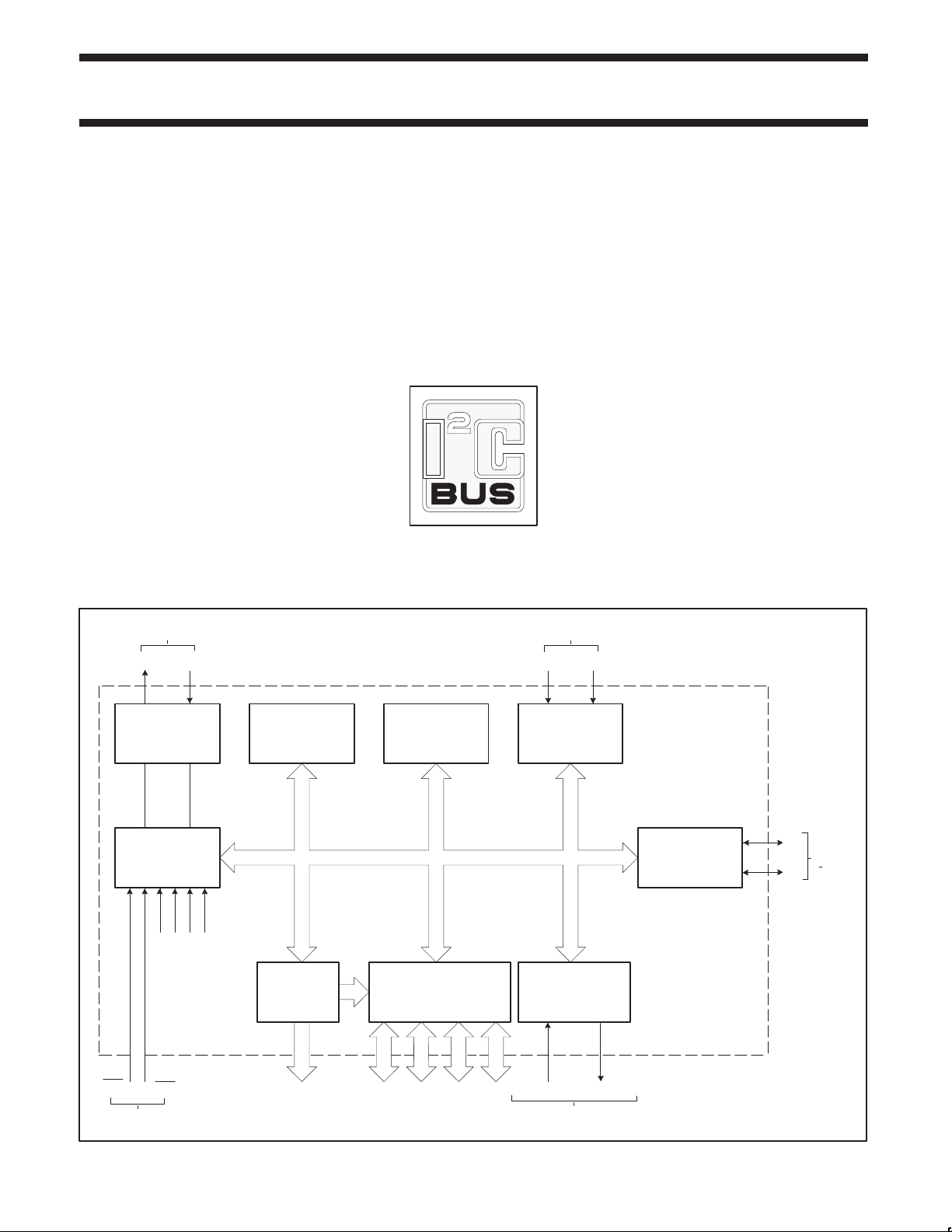

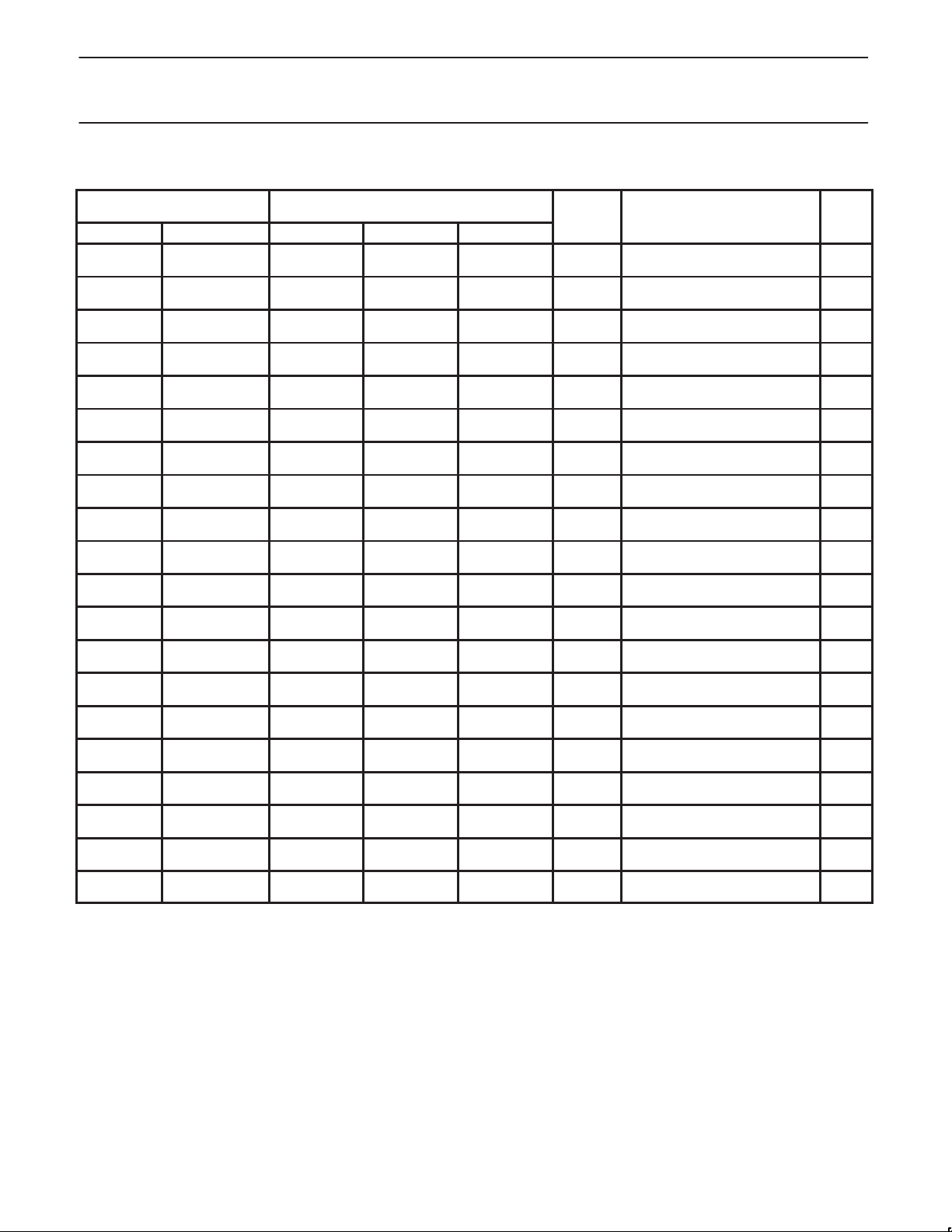

BLOCK DIAGRAM

FREQUENCY

REFERENCE

8XC654 can be expanded using standard

TTL compatible memories and logic.

The device also functions as an arithmetic

processor having facilities for both binary and

BCD arithmetic plus bit-handling capabilities.

The instruction set consists of over 100

instructions: 49 one-byte, 45 two-byte and 17

three-byte. With a 16(24)MHz crystal, 58% of

the instructions are executed in 0.75(0.5)µs

and 40% in 1.5(1)µs. Multiply and divide

instructions require 3(2)µs.

COUNTERS

FEATURES

•80C51 central processing unit

•16k × 8 ROM expandable externally to

64k bytes

•256 × 8 RAM, expandable externally to

64k bytes

•Two standard 16-bit timer/counters

•Four 8-bit I/O ports

2

•I

C-bus serial I/O port with byte oriented

master and slave functions

•Full-duplex UART facilities

•Power control modes

– Idle mode

– Power-down mode

•ROM code protection

•Extended frequency range: 3.5 to 24 MHz

•Three operating ambient temperature

ranges:

0 to +70°C

–40 to +85°C

–40 to +125°C

XTAL2 XTAL1

OSCILLATOR

INT0

EXTERNAL

INTERRUPTS

AND

TIMING

CPU

INTERNAL

INTERRUPTS

INT1

PROGRAM

MEMORY

(16K x 8 ROM)

64K BYTE BUS

EXPANSION

CONTRTOL

CONTROL

DATA

MEMORY

(256 x 8 RAM)

PROGRAMMABLE I/O

PARALLEL PORTS,

ADDRESS/DATA BUS

AND I/O PINS

T0 T1

TWO 16-BIT

TIMER/EVENT

COUNTERS

PROG SERIAL PORT

FULL DUPLEX UART

SYNCHRONOUS SHIFT

SERIAL IN SERIAL OUT

SHARED WITH

PORT 3

2

I

C SERIAL I/O

SDA

SCL

SHARED

WITH

PORT 1

1998 Jan 06

2

Philips Semiconductors Product specification

83C654CMOS single-chip 8-bit microcontroller

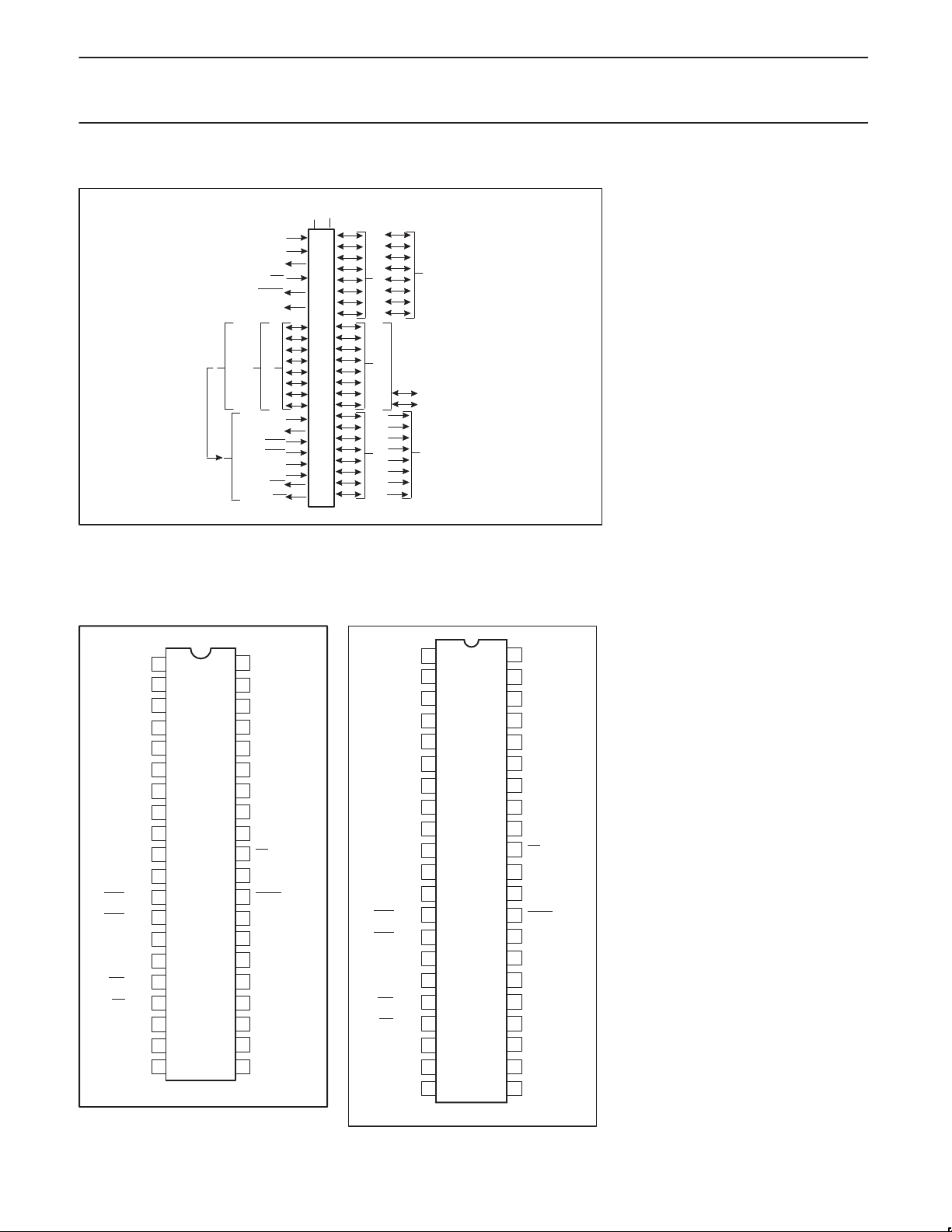

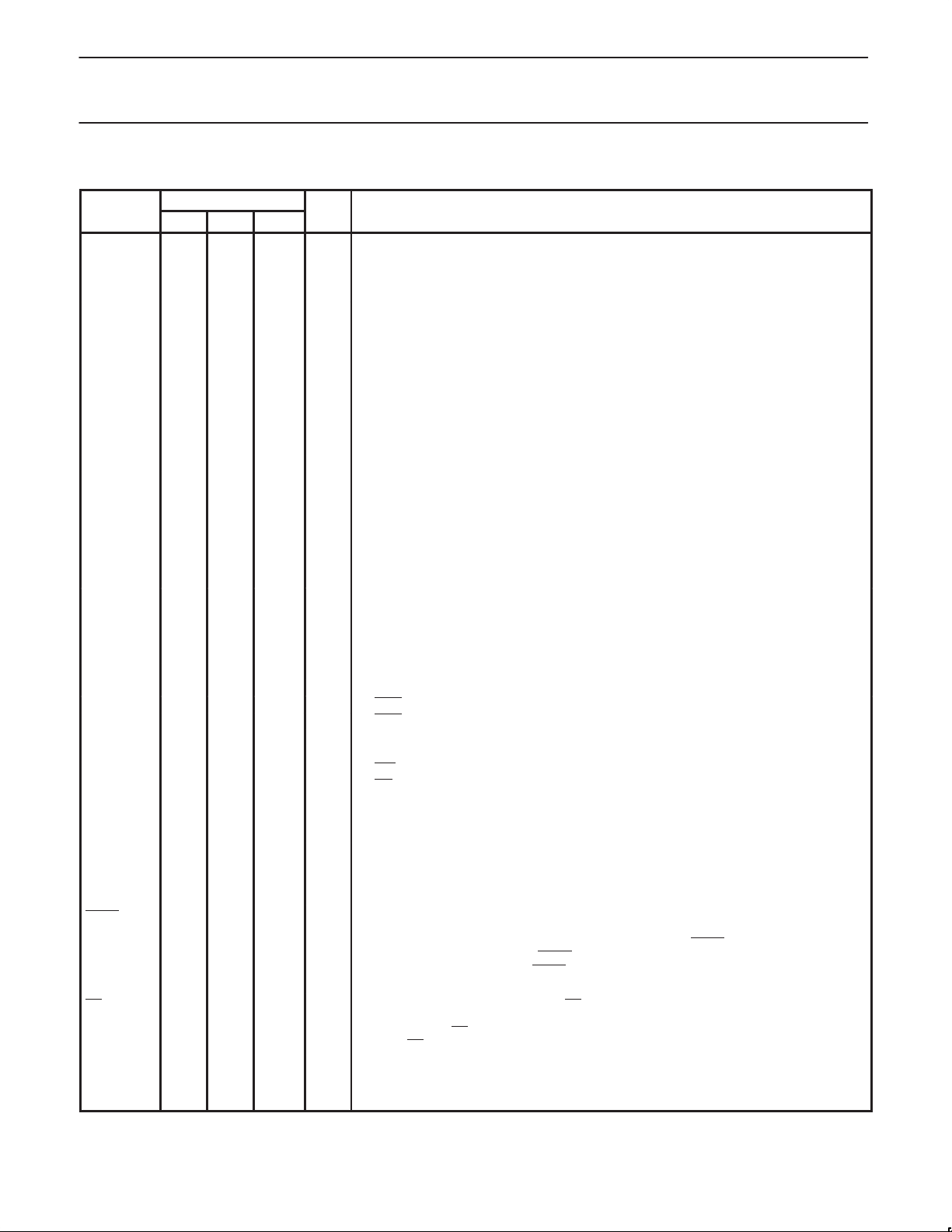

LOGIC SYMBOL

VSSV

DD

RST

XTAL1

XTAL2

PSEN

ALE

FUNCTIONS

ALTERNATE

INT0

INT1

EA

PORT 3

RxD

TxD

T0

T1

WR

RD

PORT 0PORT 1PORT 2

DATA BUS

ADDRESS AND

SCL

SDA

ADDRESS BUS

PIN CONFIGURA TIONS

Plastic dual in-line package

V

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

SCL/P1.6

SDA/P1.7

RST

RxD/P3.0

TxD/P3.1

/P3.2

INT0

/P3.3

INT1

T0/P3.4

T1/P3.5

WR

/P3.6

/P3.7

RD

XTAL2

XTAL1

V

1

2

3

4

5

6

7

8

9

PLASTIC

10

DUAL

IN-LINE

11

PACKAGE

12

13

14

15

16

17

18

19

20

SS

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

DD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA

ALE

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

P2.4/A12

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

SU00933

Plastic shrink dual in-line package

V

1

P1.0

P1.1

2

3

P1.2

4

P1.3

5

P1.4

6

P1.5

RST

/P3.2

/P3.3

T0/P3.4

T1/P3.5

/P3.6

RD

/P3.7

XTAL2

XTAL1

NC*

V

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

SS

SCL/P1.6

SDA/P1.7

RxD/P3.0

TxD/P3.1

INT0

INT1

WR

* Do not connect.

SHRINK

DUAL

IN-LINE

PACKAGE

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

DD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA

NC*

ALE

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

P2.4/A12

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

SU00934

1998 Jan 06

3

Philips Semiconductors Product specification

83C654CMOS single-chip 8-bit microcontroller

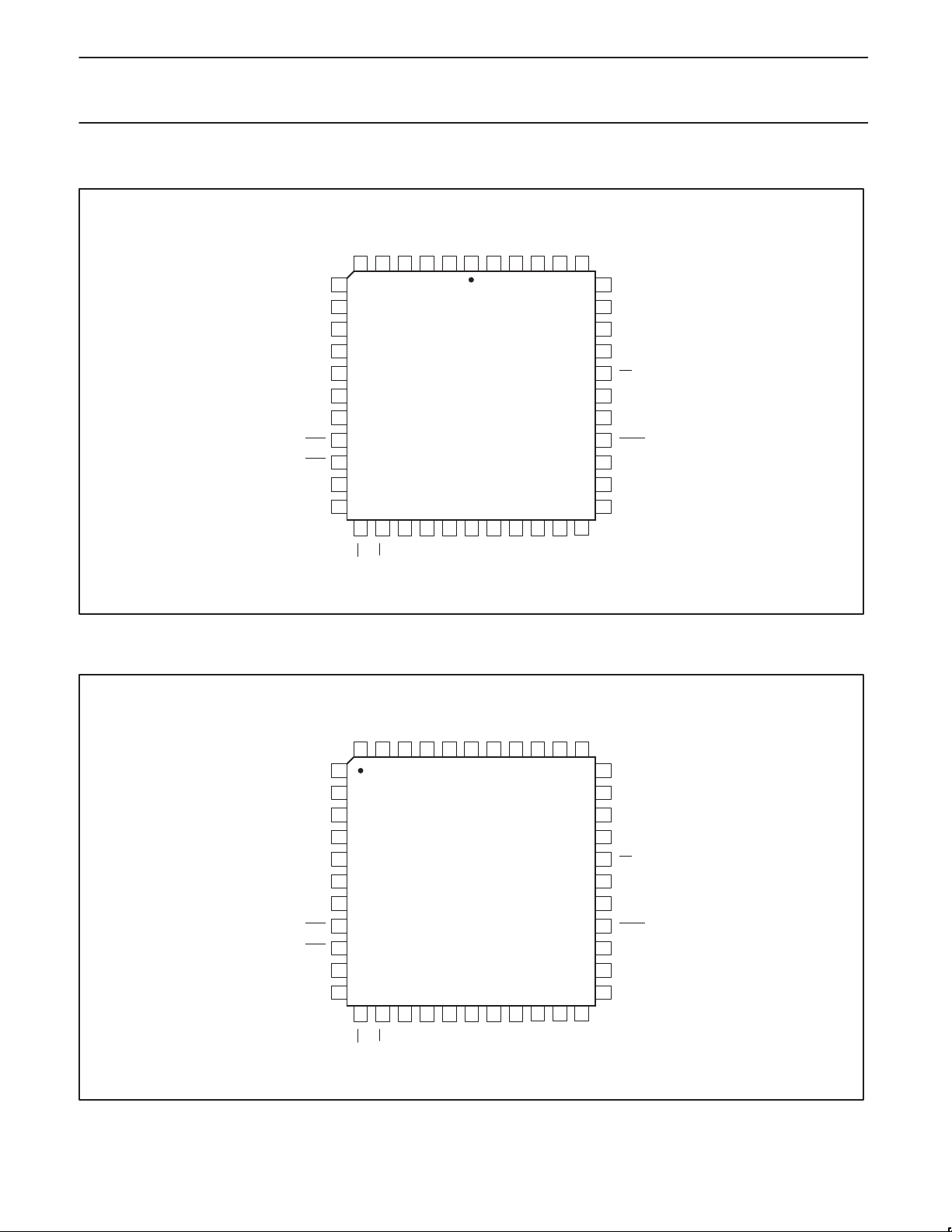

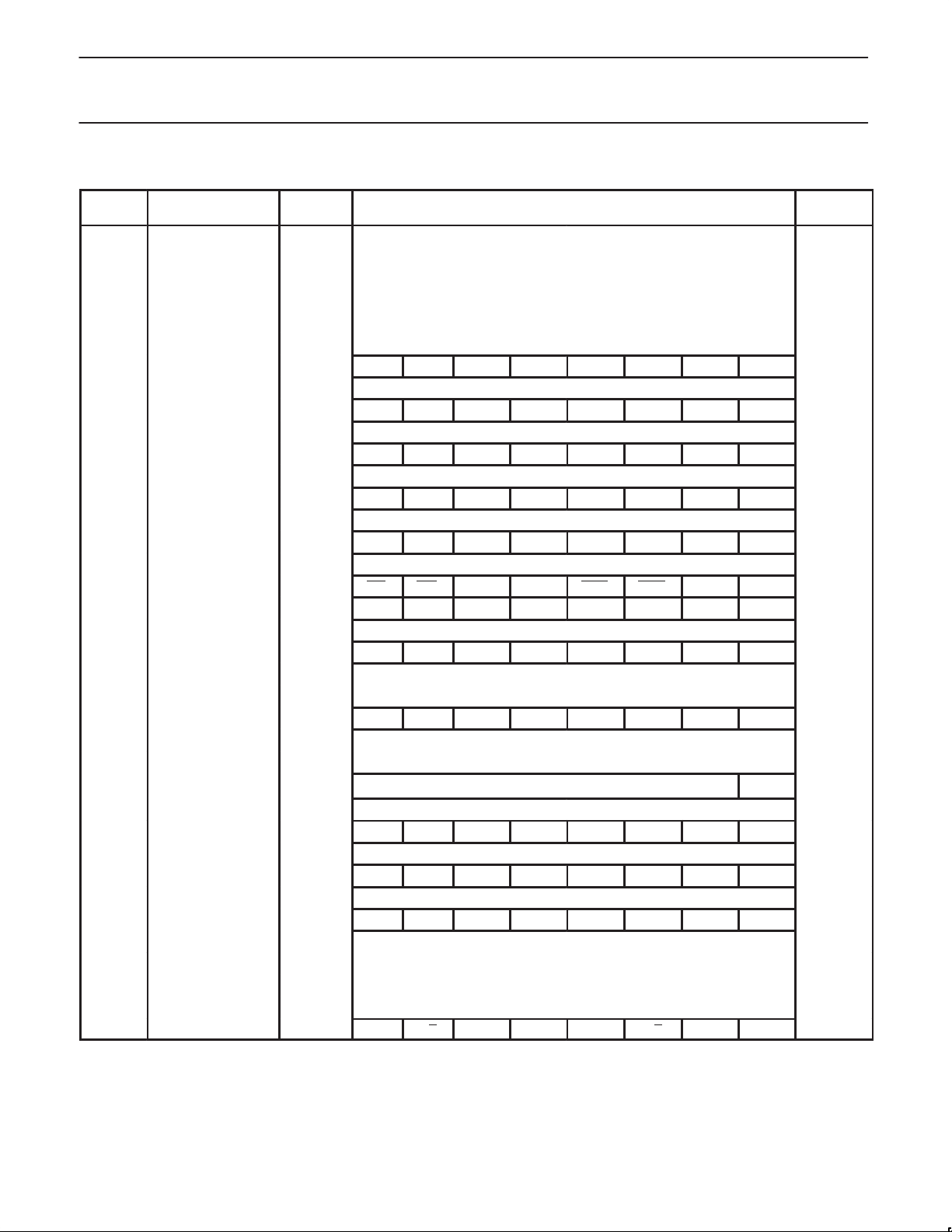

Plastic leaded chip carrier

P1.4

P1.3

P1.2

P1.1

P1.0

NC*

VDDP0.0/AD0

P0.1/AD1

P0.2/AD2

27 28

P2.3/A11

P2.2/A10

P0.3/AD3

4041

39 P0.4/AD4

38

37

36

35

34

33

32

31

30 P2.6/A14

29

P2.4/A12

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA

NC*NC*

ALE

PSEN

P2.7/A15

P2.5/A13

SU00929

P1.5

P1.6/SCL

P1.7/SDA

RST

P3.0/RxD

P3.1/TxD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

XTAL1

1234

SS

NC*

V

56

7

8

9

10

11

PLASTIC LEADED CHIP CARRIER

12

13

14

15

16

17

18 19

20 21 22 23 24 25 26

XTAL2

P3.7/RD

P3.6/WR

P2.0/A8

424344

P2.1/A9

* Do not connect.

Plastic quad flat pack

P1.5

P1.6/SCL

P1.7/SDA

RST

P3.0/RxD

V

SS4

P3.1/TxD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

SS3

P1.4

P1.3

P1.2

4344

1

2

3

4

5

6

7

8

9

10

11

12 13

P3.6/WR

QUAD FLAT PACK

14 15 16 17 18 19 20

XTAL2

P3.7/RD

P1.1

XTAL1

P1.0

SS1

V

V

39404142

NC*

VDDP0.0/AD0

P0.1/AD1

363738

P2.1/A9

P2.0/A8

P2.2/A10

P0.2/AD2

21 22

P2.3/A11

P0.3/AD3

3435

33 P0.4/AD4

32

31

30

29

28

27

26

25

24 P2.6/A14

23

P2.4/A12

P0.5/AD5

P0.6/AD6

P0.7/AD7

/V

EA

PP

V

SS2

ALE

PSEN

P2.7/A15

P2.5/A13

SU00935

* Do not connect.

(QFP only): Due to EMC improvements, all V

1998 Jan 06

pins (6, 16, 28, 39) must be connected to V

SS

4

on the 80C652/83C654.

SS

Philips Semiconductors Product specification

NUMBER

AND PACKAGE

MH

2,3

83C654CMOS single-chip 8-bit microcontroller

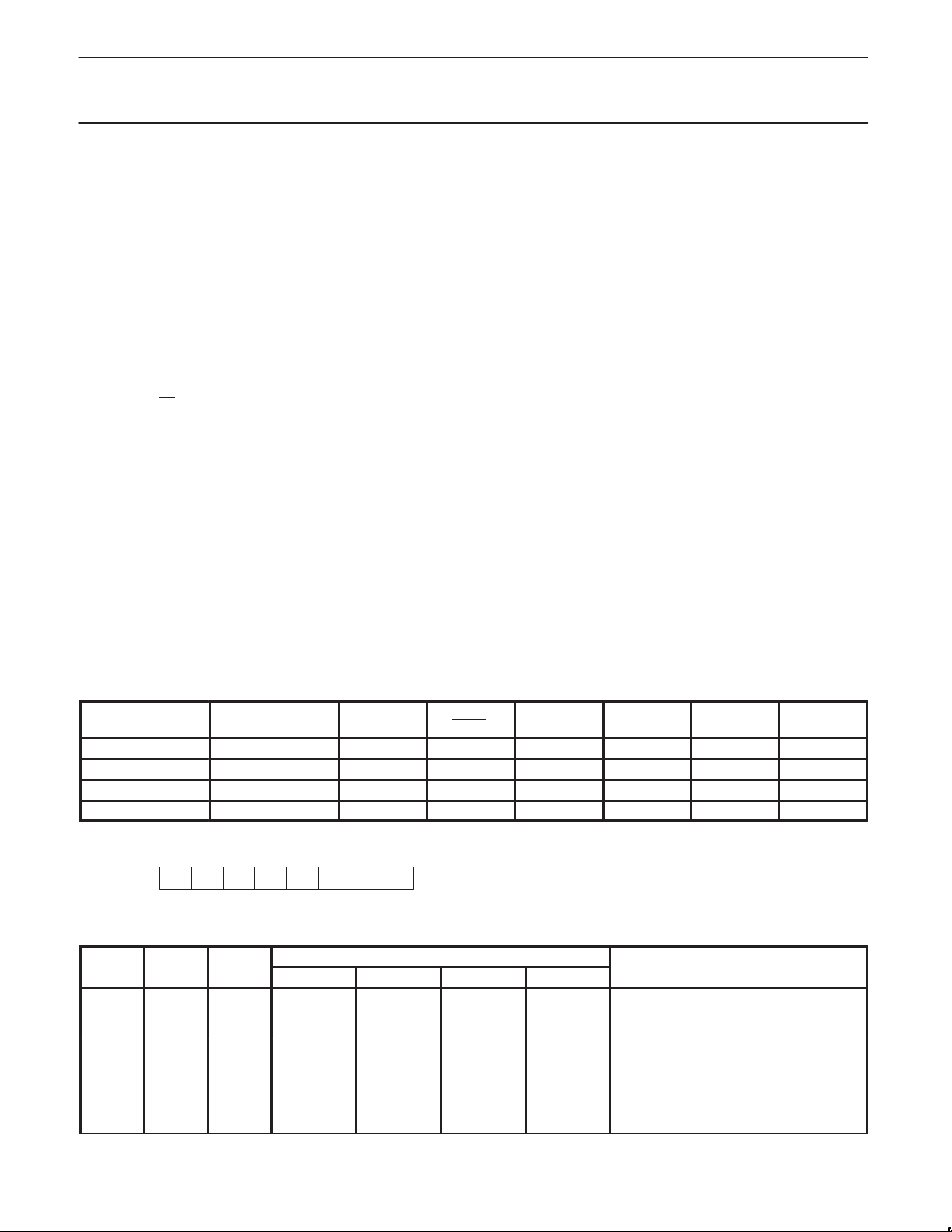

ORDERING INFORMATION

PHILIPS PART ORDER NUMBER

PART MARKING

ROMless

P80C652EBP P83C654EBP/xxx P80C652EBPN P83C654EBPN S87C654-4N40 SOT129-1 0 to +70,

P80C652EBA P83C654EBA/xxx P80C652EBAA P83C654EBAA S87C654-4A44 SOT187-2 0 to +70,

P80C652EBB P83C654EBB/xxx P80C652EBBB P83C654EBBB S87C654-4B44 SOT307-2 0 to +70,

P80C652EFP P83C654EFP/xxx P80C652EFPN P83C654EFPN S87C654-5N40 SOT129-1 –40 to +85,

P80C652EFA P83C654EFA/xxx P80C652EFAA P83C654EFAA S87C654-5A44 SOT187-2 –40 to +85,

P80C652EFB P83C654EFB/xxx P80C652EFBB P83C654EFBB S87C654-5B44 SOT307-2 –40 to +85,

P80C652EHP P83C654EHP/xxx P80C652EHPN P83C654EHPN SOT129-1 –40 to +125,

P80C652EHA P83C654EHA/xxx P80C652EHAA P83C654EHAA SOT187-2 –40 to +125,

P80C652EHB P83C654EHB/xxx P80C652EHBB P83C654EHBB SOT307-2 –40 to +125,

P80C652IBP P83C654IBP/xxx P80C652IBPN P83C654IBPN SOT129-1 0 to +70,

P80C652IBA P83C654IBA/xxx P80C652IBAA P83C654IBAA SOT187-2 0 to +70,

P80C652IBB P83C654IBB/xxx P80C652IBBB P83C654IBBB SOT307-2 0 to +70,

P80C652IFP P83C654IFP/xxx P80C652IFPN P83C654IFPN SOT129-1 –40 to +85,

P80C652IFA P83C654IFA/xxx P80C652IFAA P83C654IFAA SOT187-2 –40 to +85,

P80C652IFB P83C654IFB/xxx P80C652IFBB P83C654IFBB SOT307-2 –40 to +85,

1

ROM ROMless

P83C654EBR/xxx SOT270-1 0 to +70,

NOTES:

1. For full specification, see the 80C652/83C652 data sheet.

2. 83C654 frequency range is 3.5MHz–16MHz or 3.5MHz–24MHz.

3. For specification of the EPROM version, see the 87C654 data sheet.

4. xxx denotes the ROM code number.

PHILIPS NORTH AMERICA

PART ORDER NUMBER

1

ROM EPROM

S87C654-7N40 SOT129-1 0 to +70,

S87C654-7A44 SOT187-2 0 to +70,

S87C654-8N40 SOT129-1 –40 to +85,

S87C654-8A44 SOT187-2 –40 to +85,

3

DRAWING

TEMPERA TURE RANGE (°C)

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Quad Flat Pack

Plastic Shrink Dual In-Line Package

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Quad Flat Pack

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Quad Flat Pack

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Quad Flat Pack

Plastic Dual In-line Package

Plastic Leaded Chip Carrier

Plastic Quad Flat Pack

FREQ

z

16

16

16

16

16

16

16

16

16

16

20

20

20

20

24

24

24

24

24

24

1998 Jan 06

5

Philips Semiconductors Product specification

83C654CMOS single-chip 8-bit microcontroller

PIN DESCRIPTIONS

PIN NUMBER

MNEMONIC DIP PLCC QFP TYPE NAME AND FUNCTION

V

SS

V

DD

P0.0–0.7 39–32 43–36 37–30 I/O Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them

P1.0–P1.7 1–8 2–9 40–44,

P1.6 7 8 2 I/O SCL: I2C-bus serial port clock line.

P1.7 8 9 3 I/O SDA: I2C-bus serial port data line.

P2.0–P2.7 21–28 24–31 18–25 I/O Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s

P3.0–P3.7 10–17 11,

RST 9 10 4 I Reset: A high on this pin for two machine cycles while the oscillator is running, resets the

ALE 30 33 27 I/O Address Latch Enable: Output pulse for latching the low byte of the address during an

PSEN 29 32 26 O Program Store Enable: Read strobe to external program memory via Port 0 and Port 2. It is

EA 31 35 29 I External Access: If during a RESET, EA is held at TTL, level HIGH, the CPU executes out

XTAL1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator

XTAL2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.

NOTE:

To avoid “latch-up” effect at power-on, the voltage on any pin at any time must not be higher than V

20 22 6, 16,

28, 39

I Ground: 0V reference. With the QFP package all VSS pins (V

connected.

SS1

to V

) must be

SS4

40 44 38 I Power Supply: This is the power supply voltage for normal, idle, and power-down

operation.

float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order

address and data bus during accesses to external program and data memory. In this

application, it uses strong internal pull-ups when emitting 1s.

I/O Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups, except P1.6 and P1.7

1–3

which are open drain. Port 1 pins that have 1s written to them are pulled high by the internal

pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will

source current because of the internal pull-ups. (See DC Electrical Characteristics: I

Alternate functions include:

written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs,

port 2 pins that are externally being pulled low will source current because of the internal

pull-ups. (See DC Electrical Characteristics: I

during fetches from external program memory and during accesses to external data memory

). Port 2 emits the high-order address byte

IL

that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal

pull-ups when emitting 1s. During accesses to external data memory that use 8-bit

addresses (MOV @Ri), port 2 emits the contents of the P2 special function register.

I/O Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s

13–195,7–13

written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs,

port 3 pins that are externally being pulled low will source current because of the pull-ups.

(See DC Electrical Characteristics: I

family, as listed below:

). Port 3 also serves the special features of the 80C51

IL

10 11 5 I RxD (P3.0): Serial input port

11 13 7 O TxD (P3.1): Serial output port

12 14 8 I INT0 (P3.2): External interrupt

13 15 9 I INT1 (P3.3): External interrupt

14 16 10 I T0 (P3.4): Timer 0 external input

15 17 11 I T1 (P3.5): Timer 1 external input

16 18 12 O WR (P3.6): External data memory write strobe

17 19 13 O RD (P3.7): External data memory read strobe

device. An internal diffused resistor to V

capacitor to V

DD

.

permits a power-on reset using only an external

SS

access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the

oscillator frequency . Note that one ALE pulse is skipped during each access to external data

memory.

activated twice each machine cycle during fetches from the external program memory. When

executing out of external program memory two activations of PSEN

access to external data memory. PSEN

from external program memory. PSEN

is not activated (remains HIGH) during no fetches

can sink/source 8 LSTTL inputs and can drive CMOS

are skipped during each

inputs without external pull–ups.

of the internal program memory ROM provided the Program Counter is less than 16384. If

during a RESET, EA

memory. EA

is held a TTL LOW level, the CPU executes out of external program

is not allowed to float.

circuits.

+ 0.5V or VSS – 0.5V, respectively.

DD

).

IL

1998 Jan 06

6

Philips Semiconductors Product specification

83C654CMOS single-chip 8-bit microcontroller

Table 1. 8XC652/654 Special Function Registers

SYMBOL DESCRIPTION

ACC* Accumulator E0H E7 E6 E5 E4 E3 E2 E1 E0 00H

B* B register F0H F7 F6 F5 F4 F3 F2 F1 F0 00H

DPTR:

DPH

DPL

IE*# Interrupt enable A8H EA ES1 ES0 ET1 EX1 ET0 EX0 0x000000B

IP*# Interrupt priority B8H – PS1 PS0 PT1 PX1 PT0 PX0 xx000000B

P0* Port 0 80H AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 FFH

P1*# Port 1 90H SDA SCL FFH

P2* Port 2 A0H A15 A14 A13 A12 A11 A10 A9 A8 FFH

P3* Port 3 B0H RD WR T1 T0 INT1 INT0 TXD RXD FFH

PCON# Power control 87H SMOD – – – GF1 GF0 PD IDL 0xxx0000B

S0CON*# Serial 0 port control 98H SM0 SM1 SM2 REN TB8 RB8 TI RI 00H

S0BUF# Serial 0 data buffer 99H xxxxxxxxB

PSW* Program status word D0H CY AC F0 RS1 RS0 OV F1 P 00H

S1DAT# Serial 1 data DAH 00H

SP Stack pointer 81H 07H

S1ADR# Serial 1 address DBH

Data pointer

(2 bytes)

Data pointer high

Data pointer low

DIRECT

ADDRESS

83H

82H

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION

MSB LSB

AF AE AD AC AB AA A9 A8

BF BE BD BC BB BA B9 B8

87 86 85 84 83 82 81 80

97 96 95 94 93 92 91 90

A7 A6 A5 A4 A3 A2 A1 A0

B7 B6 B5 B4 B3 B2 B1 B0

9F 9E 9D 9C 9B 9A 99 98

D7 D6 D5 D4 D3 D2 D1 D0

SLAVE ADDRESS

GC 00H

RESET

VALUE

00H

00H

S1STA# Serial 1 status D9H SC4 SC3 SC2 SC1 SC0 0 0 0 F8H

DF DE DD DC DB DA D9 D8

S1CON*# Serial 1 control D8H CR2 ENS1 STA STO SI AA CR1 CR0 00000000B

8F 8E 8D 8C 8B 8A 89 88

TCON* Timer control 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00H

TH1 T imer high 1 8DH 00H

TH0 T imer high 0 8CH 00H

TL1 Timer low 1 8BH 00H

TL0 Timer low 0 8AH 00H

TMOD Timer mode 89H GATE C/T M1 M0 GATE C/T M1 M0 00H

* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

1998 Jan 06

7

Philips Semiconductors Product specification

83C654CMOS single-chip 8-bit microcontroller

ROM CODE PROTECTION

(83C654)

The 83C654 has an additional security

feature. ROM code protection may be

selected by setting a mask–programmable

security bit (i.e., user dependent). This

feature may be requested during ROM code

submission. When selected, the ROM code

is protected and cannot be read out at any

time by any test mode or by any instruction in

the external program memory space.

The MOVC instructions are the only

instructions that have access to program

code in the internal or external program

memory. The EA

RESET and is “don’t care” after RESET

(also if the security bit is not set). This

implementation prevents reading internal

program code by switching from external

program memory to internal program memory

during a MOVC instruction or any other

instruction that uses immediate data.

input is latched during

OSCILLA T OR

CHARACTERISTICS

XTAL1 and XTAL2 are the input and output,

respectively, of an inverting amplifier. The

pins can be configured for use as an on-chip

oscillator, as shown in the Logic Symbol,

page 3.

To drive the device from an external clock

source, XTAL1 should be driven while XTAL2

is left unconnected. There are no

requirements on the duty cycle of the

external clock signal, because the input to

the internal clock circuitry is through a

divide-by-two flip-flop. However, minimum

and maximum high and low times specified in

the data sheet must be observed.

Reset

A reset is accomplished by holding the RST

pin high for at least two machine cycles (24

oscillator periods), while the oscillator is

running. To insure a good power-on reset, the

RST pin must be high long enough to allow

the oscillator time to start up (normally a few

milliseconds) plus two machine cycles. At

power-on, the voltage on V

come up at the same time for a proper

start-up.

and RST must

DD

Idle Mode

In the idle mode, the CPU puts itself to sleep

while all of the on-chip peripherals stay

active. The instruction to invoke the idle

mode is the last instruction executed in the

normal operating mode before the idle mode

is activated. The CPU contents, the on-chip

RAM, and all of the special function registers

remain intact during this mode. The idle

mode can be terminated either by any

enabled interrupt (at which time the process

is picked up at the interrupt service routine

and continued), or by a hardware reset which

starts the processor in the same manner as a

power-on reset.

Power-Down Mode

In the power-down mode, the oscillator is

stopped and the instruction to invoke

power-down is the last instruction executed.

Only the contents of the on-chip RAM are

preserved. A hardware reset is the only way

to terminate the power-down mode. The

control bits for the reduced power modes are

in the special function register PCON. Table 2

shows the state of the I/O ports during low

current operating modes.

I2C SERIAL COMMUNICA TION —

SIO1

The I2C serial port is identical to the I2C

serial port on the 8XC552. The operation of

this subsystem is described in detail in the

8XC552 section of this manual.

Note that in both the 8XC652/4 and the

8XC552 the I

to port pins P1.6 and P1.7. Because of this,

P1.6 and P1.7 on these parts do not have a

pull-up structure as found on the 80C51.

Therefore P1.6 and P1.7 have open drain

outputs on the 8XC652/4.

2

C pins are alternate functions

Table 2. External Pin Status During Idle and Power-Down Mode

MODE

Idle Internal 1 1 Data Data Data Data

Idle External 1 1 Float Data Address Data

Power-down Internal 0 0 Data Data Data Data

Power-down External 0 0 Float Data Data Data

Serial Control Register (S1CON) – See Table 3

S1CON (D8H)

Bits CR0, CR1 and CR2 determine the serial clock frequency that is generated in the master mode of operation.

CR2 ENS1 STA STO SI AA CR1 CR0

PROGRAM

MEMORY

ALE PSEN PORT 0 PORT 1 PORT 2 PORT 3

Table 3. Serial Clock Rates

BIT FREQUENCY (kHz) AT f

CR2 CR1 CR0

0 0 0 23 47 62.5 94 256

0 0 1 27 54 71 107

0 1 0 31.25 62.5 83.3 125

0 1 1 37 75 100 150

1 0 0 6.25 12.5 17 25 960

1 0 1 50 100 133

1 1 0 100 200

1 1 1 0.24 < 62.5

NOTES:

1. These frequencies exceed the upper limit of 100kHz of the I

6MHz 12MHz 16MHz 24MHz f

1

0 to 255

0.49 < 62.5

0 to 254

2

OSC

DIVIDED BY

OSC

1

1

1

1

1

267

0.65 < 55.6

0 to 253

C-bus specification and cannot be used in an I2C-bus application.

1

200

1

400

0.98 < 50.0

0 to 251

96 × (256 – (reload value Timer 1))

reload value range Timer 1 (in mode 2)

224

192

160

120

60

1998 Jan 06

8

Loading...

Loading...