Philips 74LV08DB, 74LV08D, 74LV08PW, 74LV08N Datasheet

INTEGRATED CIRCUITS

74LV08

Quad 2-input AND gate

Product specification

Supersedes data of 1997 Feb 03

IC24 Data Handbook

1998 Apr 20

Philips Semiconductors Product specification

Quad 2-input AND gate

FEA TURES

•Wide operating voltage: 1.0 to 5.5 V

•Optimized for Low Voltage applications: 1.0 to 3.6 V

•Accepts TTL input levels between V

•Typical V

T

amb

•Typical V

T

amb

(output ground bounce) < 0.8 V at V

OLP

= 25°C.

(output VOH undershoot) > 2 V at V

OHV

= 25°C.

•Output capability: standard

•I

category: SSI

CC

QUICK REFERENCE DATA

GND = 0 V; T

SYMBOL

t

NOTES:

1. C

is used to determine the dynamic power dissipation (PD in µW)

PD

= CPD V

P

D

f

= input frequency in MHz; CL = output load capacitance in pF;

i

= output frequency in MHz; VCC = supply voltage in V;

f

o

(C

L

2. The condition is V

= 25°C; tr = tf 2.5 ns

amb

PHL/tPLH

C

I

C

PD

CC

2

V

fo) = sum of the outputs.

CC

Propagation delay

nA, nB to nY

Input capacitance 3.5 pF

Power dissipation capacitance per gate See Notes 1 and 2 10 pF

2

fi (CL V

= GND to V

I

= 2.7 V and V

CC

PARAMETER CONDITIONS TYPICAL UNIT

2

fo) where:

CC

CC.

CC

CC

CC

= 3.3 V ,

= 3.3 V,

= 3.6 V

DESCRIPTION

The 74LV08 is a low-voltage Si-gate CMOS device and is pin and

function compatible with 74HC/HCT08.

The 74LV08 provides the 2-input AND function.

CL = 15 pF;

VCC = 3.3 V

7 ns

74L V08

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA PKG. DWG. #

14-Pin Plastic DIL –40°C to +125°C 74LV08 N 74LV08 N SOT27-1

14-Pin Plastic SO –40°C to +125°C 74LV08 D 74LV08 D SOT108-1

14-Pin Plastic SSOP Type II –40°C to +125°C 74LV08 DB 74LV08 DB SOT337-1

14-Pin Plastic TSSOP Type I –40°C to +125°C 74LV08 PW 74LV08PW DH SOT402-1

PIN DESCRIPTION

PIN NUMBER SYMBOL FUNCTION

1, 4, 9, 12 1A – 4A Data inputs

2, 5, 10, 13 1Y – 4B Data inputs

3, 6, 8, 11 1Y – 4Y Data outputs

7 GND Ground (0 V)

14 V

CC

Positive supply voltage

FUNCTION TABLE

INPUTS OUTPUTS

nA nB nY

L L L

L H L

H L L

H H H

NOTES:

H = HIGH voltage level

L = LOW voltage level

1998 Apr 20 853–1893 19256

2

Philips Semiconductors Product specification

Quad 2-input AND gate

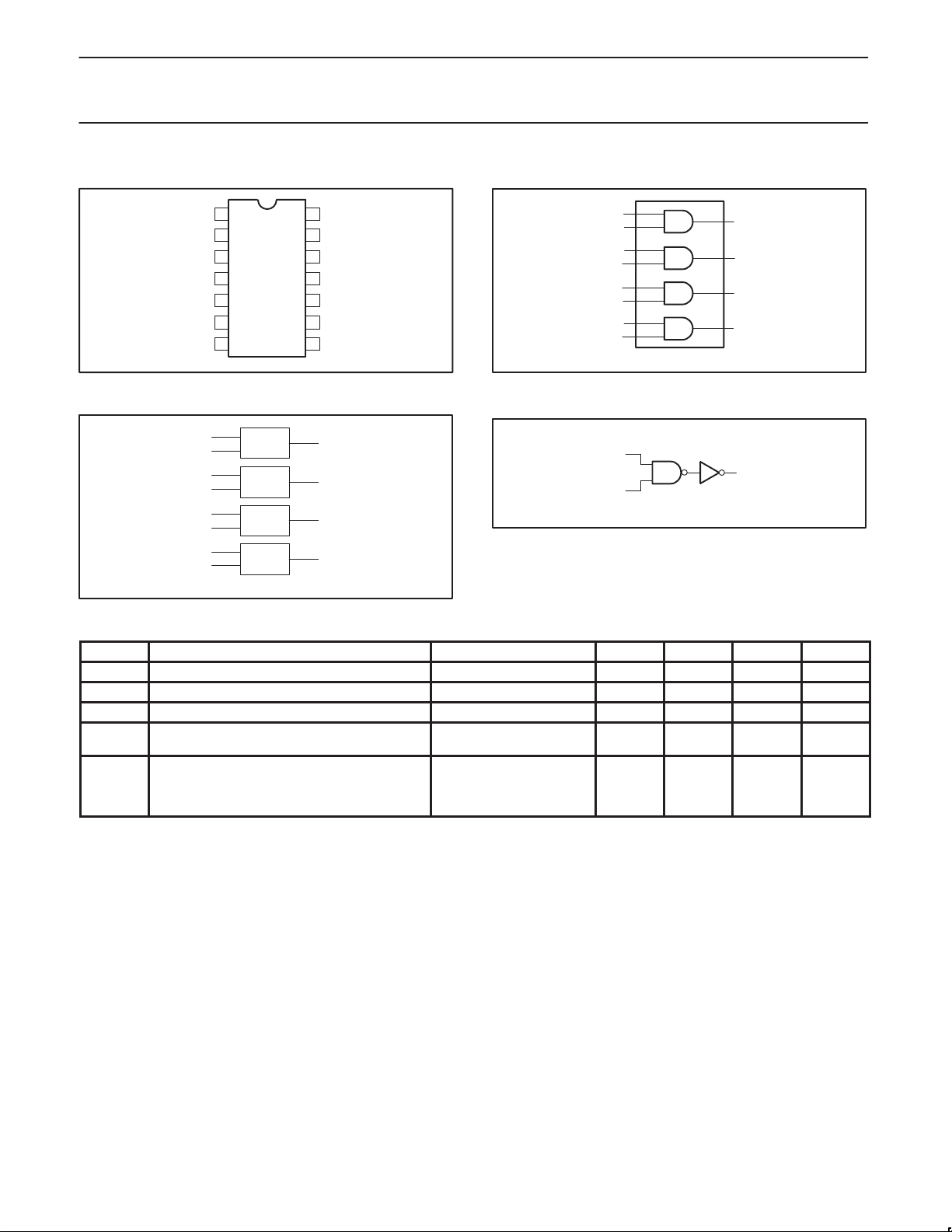

PIN CONFIGURATION

1

1A

2

1B

3

1Y

4

2A

5

2B

6

2Y

GND

LOGIC SYMBOL (IEEE/IEC)

1

2

4

5

9

10

12

13

&

&

&

&

SY00034

SV00436

74LV08

LOGIC SYMBOL

1A

14

V

CC

13

4B

12

4A

11

4Y

3B

10

3A

9

87

3Y

LOGIC DIAGRAM (ONE GATE)

3

6

8

11

1

1B

2

2A

4

2B

5

3A

9

3B

10

4A

12

4B

13

A

B

1Y

2Y

3Y

4Y

SV00435

SV00415

3

6

8

11

Y

RECOMMENDED OPERA TING CONDITIONS

SYMBOL PARAMETER CONDITIONS MIN TYP. MAX UNIT

V

V

V

T

amb

tr, t

NOTE:

1. The LV is guaranteed to function down to V

DC supply voltage See Note1 1.0 3.3 5.5 V

CC

Input voltage 0 – V

I

Output voltage 0 – V

O

Operating ambient temperature range in free air

Input rise and fall times

f

CC

See DC and AC

characteristics

VCC = 1.0V to 2.0V

VCC = 2.0V to 2.7V

VCC = 2.7V to 3.6V

VCC = 3.6V to 5.5V

= 1.0V (input levels GND or VCC); DC characteristics are guaranteed from VCC = 1.2V to VCC = 5.5V.

–40

–40

–

–

–

–

–

–

–

–

CC

CC

+85

+125

500

200

100

50

ns/V

V

V

°C

1998 Apr 20

3

Loading...

Loading...