DATA SH EET

Product specification

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT670

4 x 4 register file; 3-state

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990 2

Philips Semiconductors Product specification

4 x 4 register file; 3-state 74HC/HCT670

FEATURES

• Simultaneous and independent read and write

operations

• Expandable to almost any word size and bit length

• Output capability: bus driver

• ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT670 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT670 are 16-bit 3-state register files

organized as 4 words of 4 bits each. Separated read and

write address inputs (R

A

, RBand WA,WB) and enable

inputs (RE andWE) are available, permitting simultaneous

writing into one word location and reading from another

location. The 4-bit word to be stored is presented to four

data inputs (D0 to D3). The WA and WB inputs determine

the location of the stored word. When the WE input is

LOW, the data is entered into the addressed location. The

addressed location remains transparent to the data while

the WE input is LOW. Data supplied at the inputs will be

read out in true (non-inverting) form from the 3-state

outputs (Q0 to Q3). Dnand Wninputs are inhibited when

WE is HIGH.

Direct acquisition of data stored in any of the four registers

is made possible by individual read address inputs

(RAand RB). The addressed word appears at the four

outputs when the RE is LOW. Data outputs are in the high

impedance OFF-state when RE is HIGH. This permits

outputs to be tied together to increase the word capacity to

very large numbers.

Design of the read enable signals for the stacked devices

must ensure that there is no overlap in the LOW levels

which would cause more than one output to be active at

the same time. Parallel expansion to generate n-bit words

is accomplished by driving the enable and address inputs

of each device in parallel.

QUICK REFERENCE DATA

GND = 0 V; T

amb

=25°C; tr=tf= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (PD in µW):

PD=CPD× V

CC

2

× fi+∑ (CL× V

CC

2

× fo) where:

fi= input frequency in MHz

fo= output frequency in MHz

∑ (CL× V

CC

2

× fo) = sum of outputs

CL= output load capacitance in pF

VCC= supply voltage in V

2. For HC the condition is VI= GND to VCC;

for HCT the condition is VI= GND to VCC−1.5 V

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL

/ t

PLH

propagation delay Dn to Q

n

CL= 15 pF; VCC= 5 V 23 23 ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per package notes 1 and 2 122 124 pF

December 1990 3

Philips Semiconductors Product specification

4 x 4 register file; 3-state 74HC/HCT670

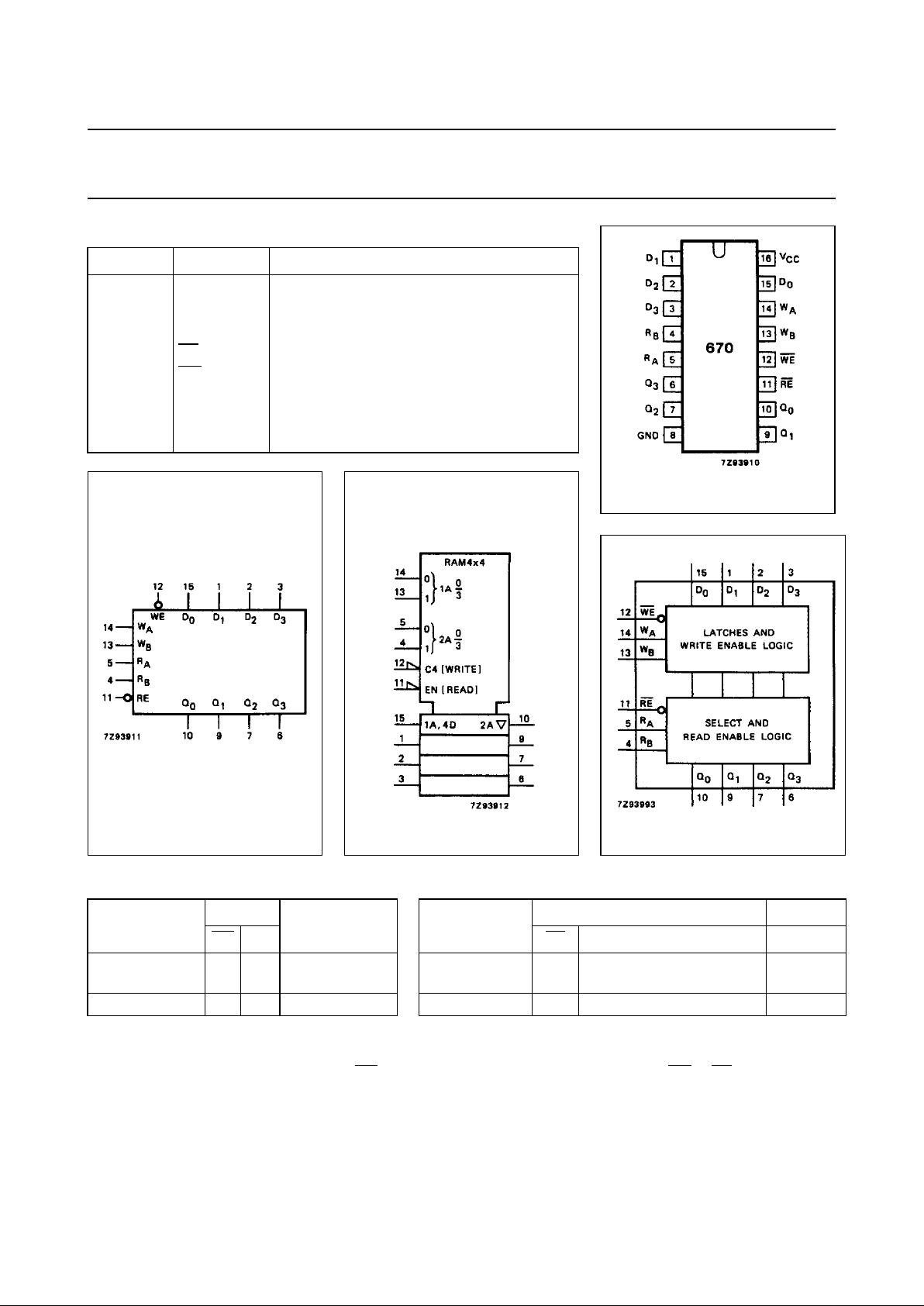

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

5, 4 R

A

, R

B

read address inputs

8 GND ground (0 V)

10, 9, 7, 6 Q

0

to Q

3

data outputs

11

RE 3-state output read enable input (active LOW)

12

WE write enable input (active LOW)

14, 13 W

A

, W

B

write address inputs

15, 1, 2, 3 D

0

to D

3

data inputs

16 V

CC

positive supply voltage

Fig.1 Pin configuration.

Fig.2 Logic symbol. Fig.3 IEC logic symbol. Fig.4 Functional diagram.

WRITE MODE SELECT TABLE

Note

1. The write address (WA and WB) to the

“internal latches” must be stable while WE is

LOW for conventional operation.

OPERATING

MODE

INPUTS

INTERNAL

LATCHES

(1)

WE D

n

write data

LLL

HLH

data latched H X no change

READ MODE SELECT TABLE

Notes

1. The selection of the “internal latches” by read address

(RA and RB) are not constrained by WE or RE operation.

H = HIGH voltage level

L = LOW voltage level

X = don’t care

Z = high impedance OFF-state

OPERATING

MODE

INPUTS OUTPUT

RE INTERNAL LATCHES

(1)

Q

n

read

L

L

L

H

L

H

disabled H X Z

Loading...

Loading...