Philips 74HCT423U, 74HCT423PW, 74HCT423N, 74HCT423DB, 74HCT423D Datasheet

...

DATA SH EET

Product specification

Supersedes data of December 1990

File under Integrated Circuits, IC06

1998 Jul 08

INTEGRATED CIRCUITS

74HC/HCT423

Dual retriggerable monostable

multivibrator with reset

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

1998 Jul 08 2

Philips Semiconductors Product specification

Dual retriggerable monostable

multivibrator with reset

74HC/HCT423

FEATURES

• DC triggered from active HIGH or active LOW inputs

• Retriggerable for very long pulses up to 100% duty

factor

• Direct reset terminates output pulse

• Schmitt-trigger action on all inputs except for the reset

input

• Output capability: standard (except for nR

EXT/CEXT

)

• ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT423 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT423 are dual retriggerable monostable

multivibrators with output pulse width control by two

methods. The basic pulse time is programmed by

selection of an external resistor (R

EXT

) and capacitor

(C

EXT

). The external resistor and capacitor are normally

connected as shown in Fig.6.

Once triggered, the basic output pulse width may be

extended by retriggering the gated active LOW-going edge

input (nA) or the active HIGH-going edge input (nB). By

repeating this process, the output pulse period

(nQ = HIGH, nQ = LOW) can be made as long as desired.

When nRDis LOW, it forces the nQ output LOW, the

nQ output HIGH and also inhibits the triggering.

Figures 7 and 8 illustrate pulse control by reset. The basic

output pulse width is essentially determined by the values

of the external timing components R

EXT

and C

EXT

.

For pulse widths, when C

EXT

< 10 000 pF, see Fig.9.

When C

EXT

> 10 000 pF, the typical output pulse width is

defined as:

tW= 0.45 × R

EXT

× C

EXT

(typ.),

where, tW= pulse width in ns;

R

EXT

= external resistor in kΩ;

C

EXT

= external capacitor in pF.

Schmitt-trigger action in the nA and nB inputs, makes the

circuit highly tolerant to slower input rise and fall times.

The “423” is identical to the “123” but cannot be triggered

via the reset input.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25 °C; tr= tf= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (PDin µW):

PD= CPD× V

CC

2

× fi+∑(CL× V

CC

2

× fo) + 0.75 × C

EXT

× V

CC

2

× fo+ D × 16 × VCCwhere:

fi= input frequency in MHz

fo= output frequency in MHz

D = duty factor in %

∑ (CL× V

CC

2

× fo) = sum of outputs

CL= output load capacitance in pF

VCC= supply voltage in V

C

EXT

= timing capacitance in pF

2. For HC the condition is VI= GND to V

CC

For HCT the condition is VI= GND to VCC− 1.5 V

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL

/ t

PLH

propagation delay CL= 15 pF; VCC= 5 V;

R

EXT

=5 kΩ; C

EXT

= 0 pF

n

A, nB to nQ, nQ2526ns

n

R

D

to nQ, nQ2022ns

C

I

input capacitance 3.5 3.5 pF

t

W

minimum output pulse width nQ, nQ notes 1 and 2 75 75 ns

1998 Jul 08 3

Philips Semiconductors Product specification

Dual retriggerable monostable

multivibrator with reset

74HC/HCT423

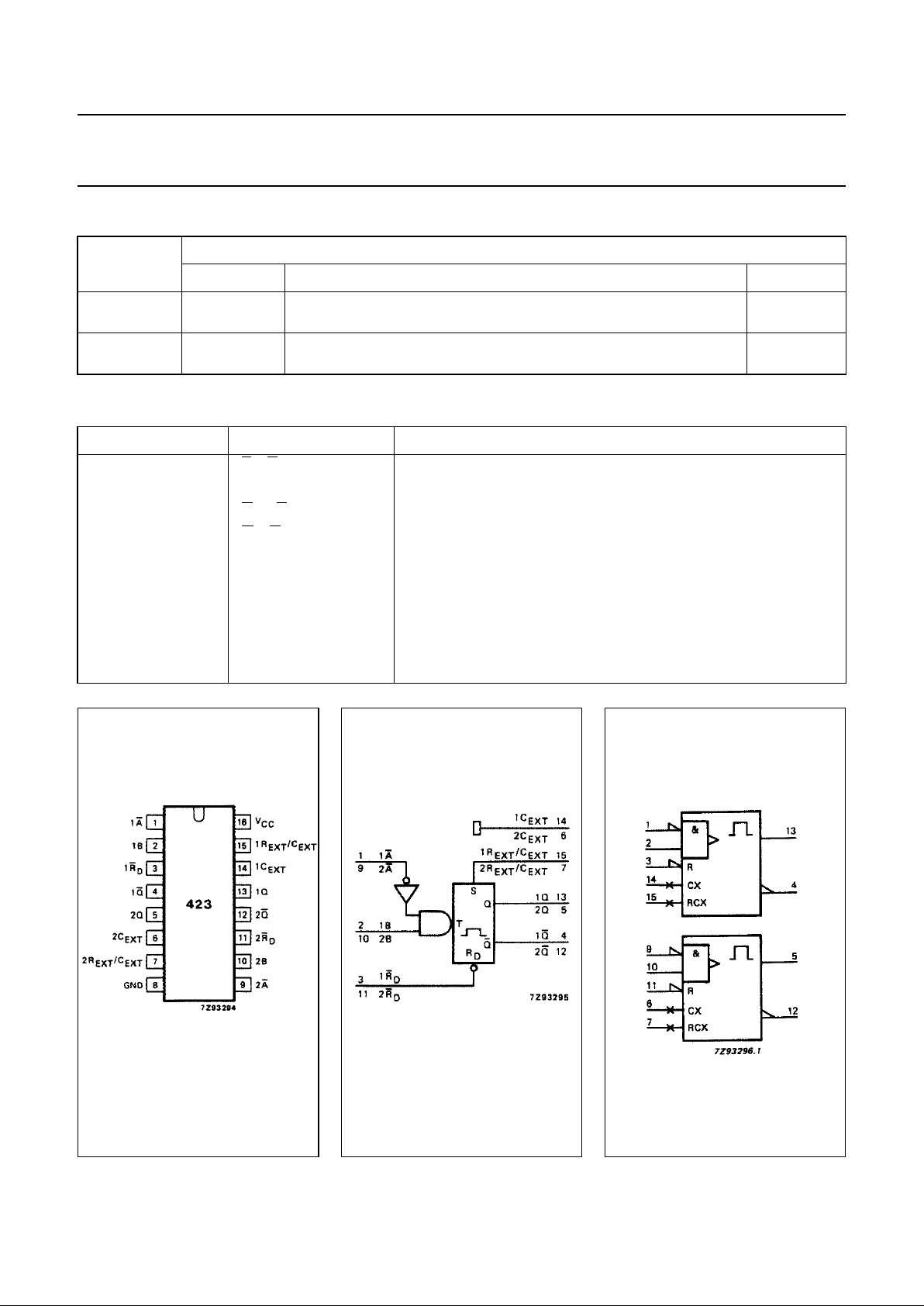

ORDERING INFORMATION

PIN DESCRIPTION

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

74HC423N;

74HCT423N

DIP16 plastic dual in-line package; 16 leads (300 mil); long body SOT38-1

74HC423D;

74HCT423D

SO16 plastic small outline package; 16 leads; body width 3.9 mm;

low stand-off height

SOT109-1

PIN NO. SYMBOL NAME AND FUNCTION

1, 9 1

A, 2A trigger inputs (negative-edge triggered)

2, 10 1B, 2B trigger inputs (positive-edge triggered)

3, 11 1

RD,2R

D

direct reset action (active LOW)

4, 12 1

Q, 2Q outputs (active LOW)

72R

EXT/CEXT

external resistor/capacitor connection

8 GND ground (0 V)

13, 5 1Q, 2Q outputs (active HIGH)

14, 6 1C

EXT

,2C

EXT

external capacitor connection

15 1R

EXT/CEXT

external resistor/capacitor connection

16 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Fig.3 IEC logic symbol.

1998 Jul 08 4

Philips Semiconductors Product specification

Dual retriggerable monostable

multivibrator with reset

74HC/HCT423

FUNCTION TABLE

Notes

1. H = HIGH voltage level

L = LOW voltage level

X = don’t care

↑ = LOW-to-HIGH transition

↓ = HIGH-to-LOW transition

= one HIGH level output pulse

= one LOW level output pulse

2. If the monostable was triggered before this condition was established, the pulse will continue as programmed.

INPUTS OUTPUTS

n

R

D

nAnB nQ nQ

LXX L H

XHXL

(2)

H

(2)

XXLL

(2)

H

(2)

HL↑

H↓H

Fig.4 Functional diagram.

1998 Jul 08 5

Philips Semiconductors Product specification

Dual retriggerable monostable

multivibrator with reset

74HC/HCT423

Fig.5 Logic diagram.

It is recommended to ground pins 6 (2C

EXT

) and 14

(1C

EXT

) externally to pin 8 (GND).

Fig.6 Timing component connections.

Loading...

Loading...