Page 1

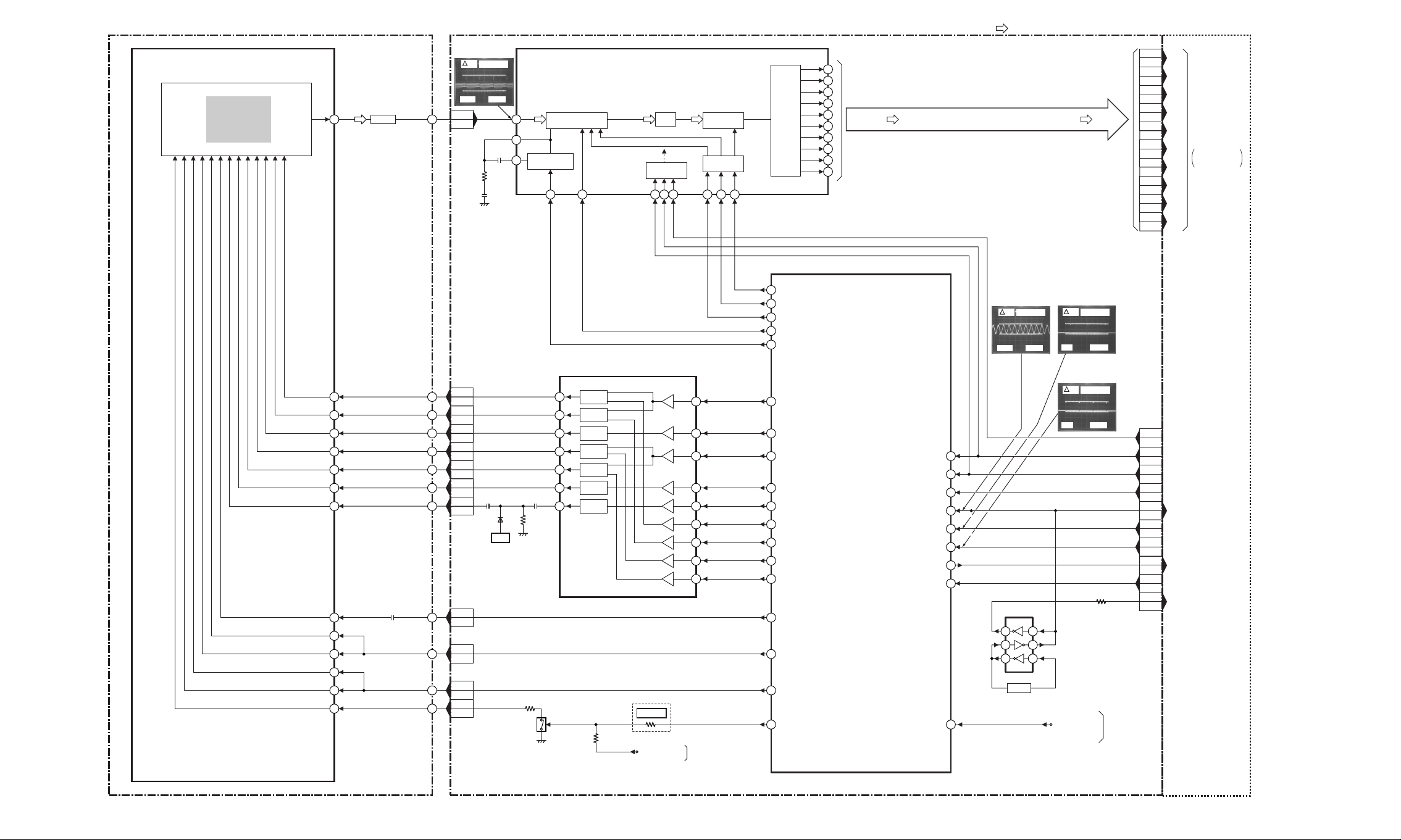

CCD C.B.A. MAIN C.B.A.

IC3001 (CCD)

V1 1.44 Vp-p

CCD

IMAGE

SENSOR

10

5

6

4

2

3

1

16

12

14

19

13

20

17

Q3001

BUFFER

0.5 V 50 µs

P3001

9

P3001

15

P3001

16

P3001

14

P3001

12

P3001

13

P3001

11

P3001

4

D3001

P3001

7

P3001

6

P3001

2

P3001

3

+15V

IC3004 (CAMERA SIGNAL PROCESS)

DOUBLE

SAMPLING HOLD

28

DC OFFSET

29

COMPENSATOR

17 18192616

20

IC3001 (V-DRIVE)

DRIVE

14

DRIVE

16

DRIVE

12

DRIVE

17

DRIVE

19

DRIVE

13

20

DRIVE

Q3001

AGC

SERIAL

INTERFACE

44 45 43

NOT USED

(FROM IC2003(4))

V-SUB CONTROL

10BIT A/D

CONVERTER

TIMING

GENERATOR

6

10

3

9

2

8

7

5

4

FROM SYSTEM CONTROL

BLOCK DIAGRAM

AD0

2

AD1

3

AD2

4

AD3

AD4

AD5

AD6

AD7

AD8

AD9

5

6

7

8

9

10

11

OUTPUT

LATCH

CIRCUIT

IC3002 (TIMING PULSE GENERATOR)

12

A/D CLOCK

37

DOUBLE SAMPLING PULSE 1

38

DOUBLE SAMPLING PULSE 2

44 H CLEAR PULSE

4

OB CLAMP PULSE

15

V1 PULSE

V2 PULSE

16

V3 PULSE

17

V4 PULSE

19

24

SUB CONTROL PULSE

20 V1A CHARGE PULSE

21

V1B CHARGE PULSE

22 V3A CHARGE PULSE

23

V3B CHARGE PULSE

RESET PULSE

34

H1 PULSE

31

H2 PULSE

28

V-SUB CONTROL

13

SERIAL DATA 10

2 FCK

CCD VD PULSE

CCD HD PULSE

SYSTEM CLOCK

RESET(L)

10BIT DIGITAL DATA

9SERIAL CLOCK

11TIMING GENERATOR CS (L)

1

6

5

48

45

2NTSC/PAL SELECT

CAMERA SIGNAL

V1 0.37 Vp-p

0.2 V 20 ns

IC3003

(INVERTER)

7 1

6 2

5 3

X3001

49.5MHz

V1 3.74 Vp-p

2 V 10 ms

V1 3.74 Vp-p

2 V 50 µs

(FROM IC2001(8))

NTSC/PAL SELSCT

CONTROL

P2001

10

P2001

11

P2001

12

P2001

15

P2001

16

P2001

13

P2001

14

P2001

17

P2001

18

P2001

19

P2001

58

P2001

51

P2001

50

P2001

57

P2001

P2001

22

P2001

21

P2001

24

P2001

76

P2001

FROM SYSTEM

CONTROL BLOCK

DIAGRAM

DIGITAL C.B.A.

AD0

AD1

AD2

AD3

AD4

10BIT DIGITAL DATA

AD5

AD6

AD7

AD8

AD9

CS (H)

SERIAL DATA

SERIAL CLOCK

TIMING GENERATOR CS (L)

MCLK

9

CCD VD PULSE

CCD HD PULSE

SYSTEM CLOCK

RESET(L)

2 FCK

8

TO RGB SIGNAL

PROCESS BLOCK

DIAGRAM

Loading...

Loading...