Panasonic MN89303A Datasheet

For Information Equipment

MN89303A

SVGA Display Controller

Overview

The MN89303A is an LCD/CRT display controller with

IBM™ VGA-compatible registers. It features all the necessary interfaces for a compact display system: ISA bus interface, local bus interface, DRAM interface, and LCD panel

interface. The built-in graphics acceleration functions include

support for hardware cursor.

Note: IBM™ and VGA are registered tr ademarks of International

Business Machines Corporation.

Features

Monochrome STN LCD panel support

Maximum display size: 800 × 600

Support for single and dual panels

16-monochrome gradation

Color STN LCD panel support

Maximum display size: 800 × 600

Support for single and dual panels

16-gradation for each color (RGB)

Color TFT LCD panel support

Maximum display size: 800 × 600

4-bit output for each color (RGB)

Maximum number of colors in concurrent display

640 × 480: 256/4096 palette (TFT, STN)

800 × 600: 256/4096 palette (TFT, STN)

Built-in graphics acceleration functions

• Hardware cursor (16 × 16 or 32 × 32)

Built-in automatic display centering

Built-in gradation control table (rewritable) for

optimizing gradation to match panel

DRAM interface with 16-bit bus

• Choice of DRAM access timing to match

system performance (EDO/normal)

• Support for 2CAS/2WE mode

• Refresh control

Host interfaces

• ISA bus (16-bit)

• i386/i486 local bus (16-bit)

Note: i386 and i486 are trademarks of Intel Corporation.

Applications

Point-of-sale terminals, Factory automation terminals,

word processors, and other terminals

325

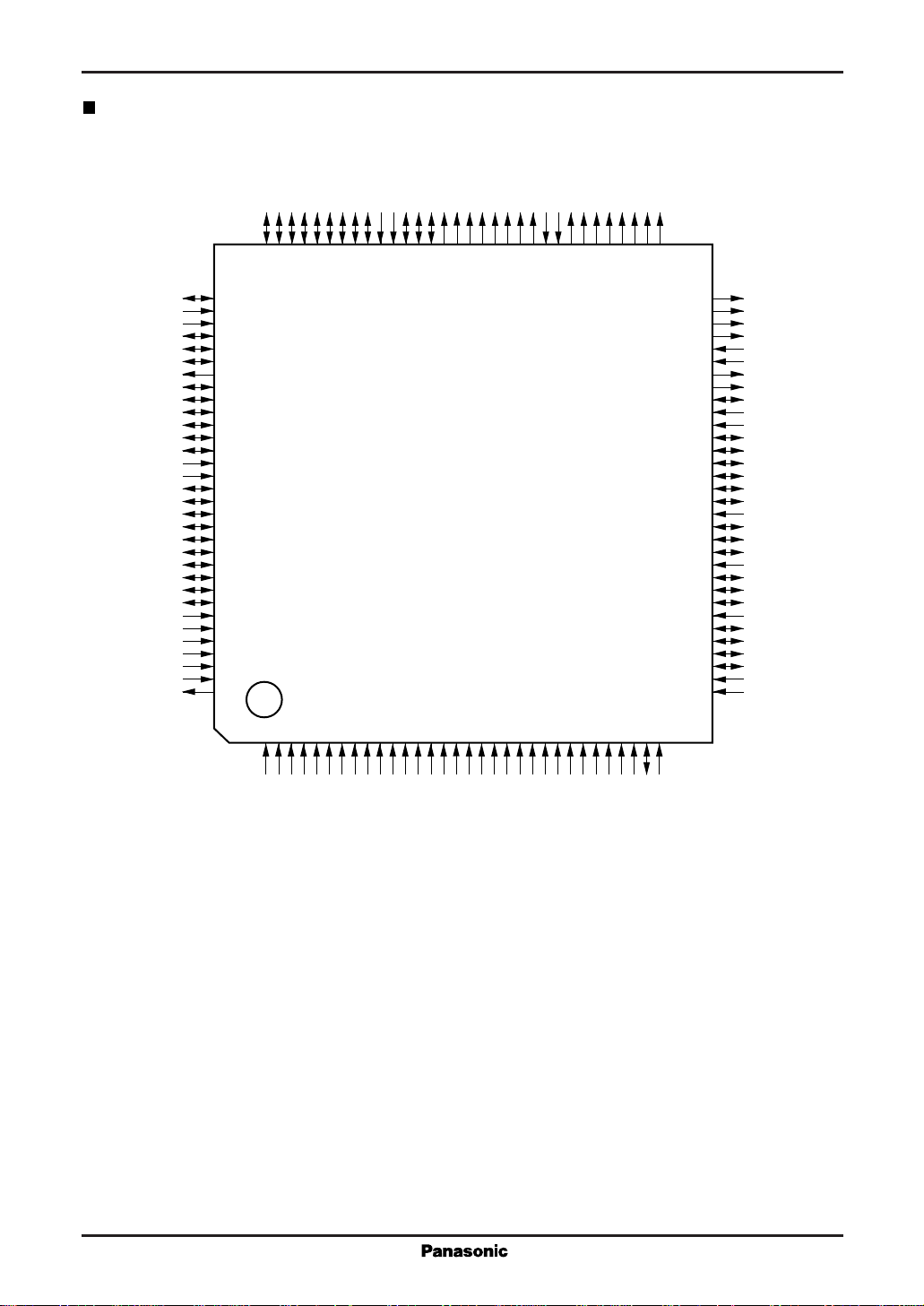

MN89303A For Information Equipment

Pin Assignment

DDVSS

LOGICON

LCDON

BACKON

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

VDDVSSUD0

UD1

UD2

UD3

UD4

UD5

UD6

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

V

UD7

MAO

V

V

RAS

UCAS

LCAS

WE

MD15

MD14

MD13

MD12

MD11

MD10

V

V

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

V

V

RESET

MINTEST

TEST

V

XOUT

96959493929190898887868584838281807978777675747372717069686766

97

98

SS

DD

DD

DD

99

100

101

102

103

104

105

106

107

108

109

110

SS

111

112

113

114

115

116

117

118

119

120

121

122

SS

123

124

125

126

127

SS

128

12345678910111213141516171819202122232425262728293031

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

FP

LP

DISP

DCLK

V

DD

V

SS

IOCS16

MEMCS16

IOCHRDY

V

DD

V

SS

SD0

SD1

SD2

SD3

SD4

SD5

V

SS

SD6

SD7

SD8

V

DD

SD9

SD10

SD11

V

SS

SD12

SD13

SD14

SD15

V

DD

V

SS

32

SS

V

XIN

Note: Never leave V

AEN

IORD

SBHE

IOWR

SMEMR

SMEMW

and VSS pins open.

DD

A21

A20

SA19

SA18

SA17

SA16

SA15

SA14

SA13

SA12

(TOP VIEW)

QFH128-P-1818

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

BIOSEN

REFRESH

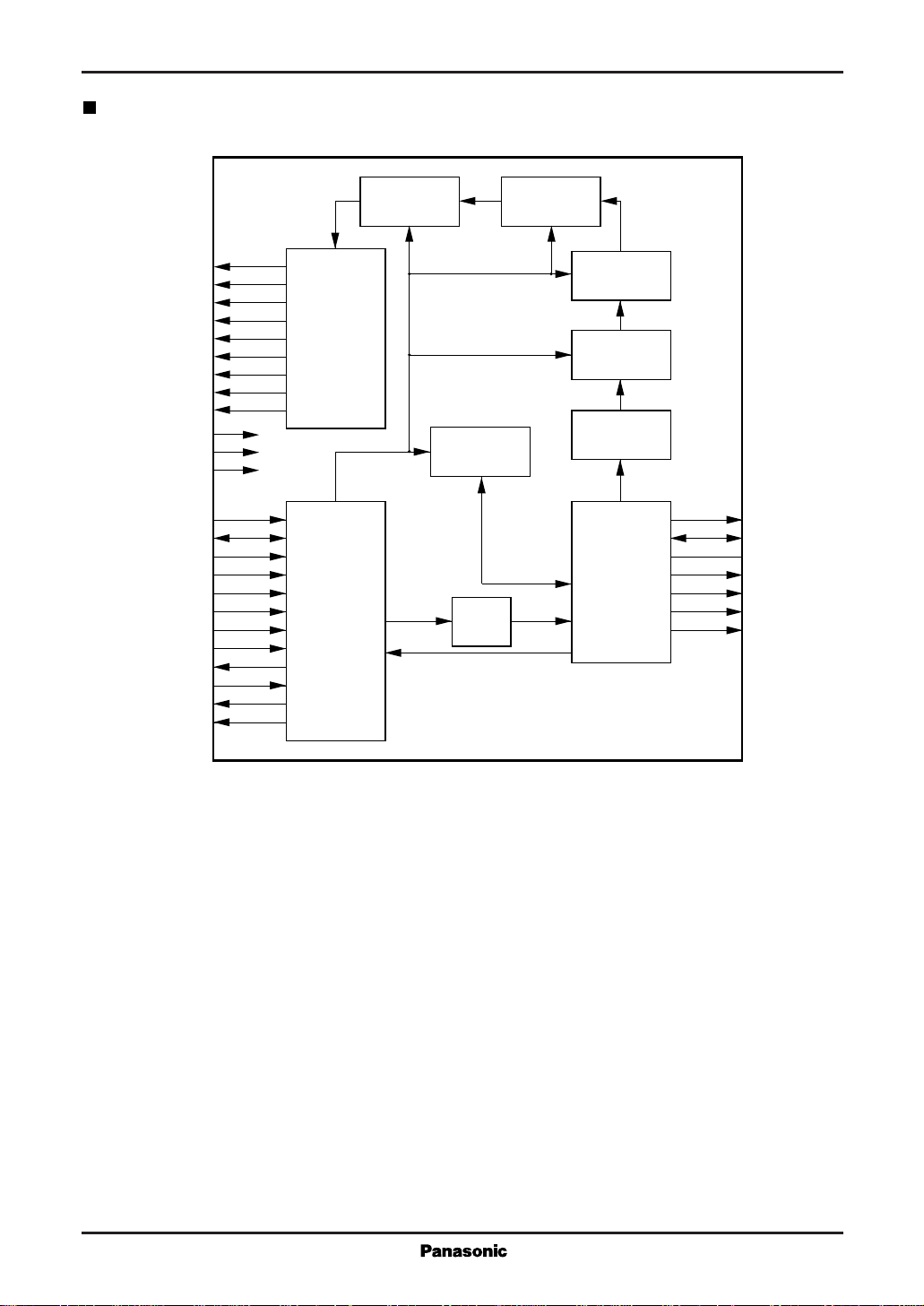

For Information Equipment MN89303A

Block Diagram

UD[7:0]

LD[7:0]

BACKON

LCDON

LOGICON

DISP

DCLK

XIN

RESET

TEST/MINTEST

Address[21:0]

SD[15:0]

AEN

SBHE

IOWR

IORD

SMEMW

SMEMR

IOCHRDY

REFRESH

MEMCS16

IOCS16

Gray scale

engine

RAM table

Hardware

cursor

Attribute

control

Video FIFO

LP

FO

83

84

85

63

64

62

61

1

124

126/125

LCD panel

controller

LCD/CRT

controller

Memory

3 100

4

5

6

7

8

56

32

57

58

Host

interface

Memory

write

buffer

interface

Access

attributer

Graphics

controller

101

102

103

31

MA[9:0]

MD[15:0]

RAS

UCAS

LCAS

WE

BIOSEN

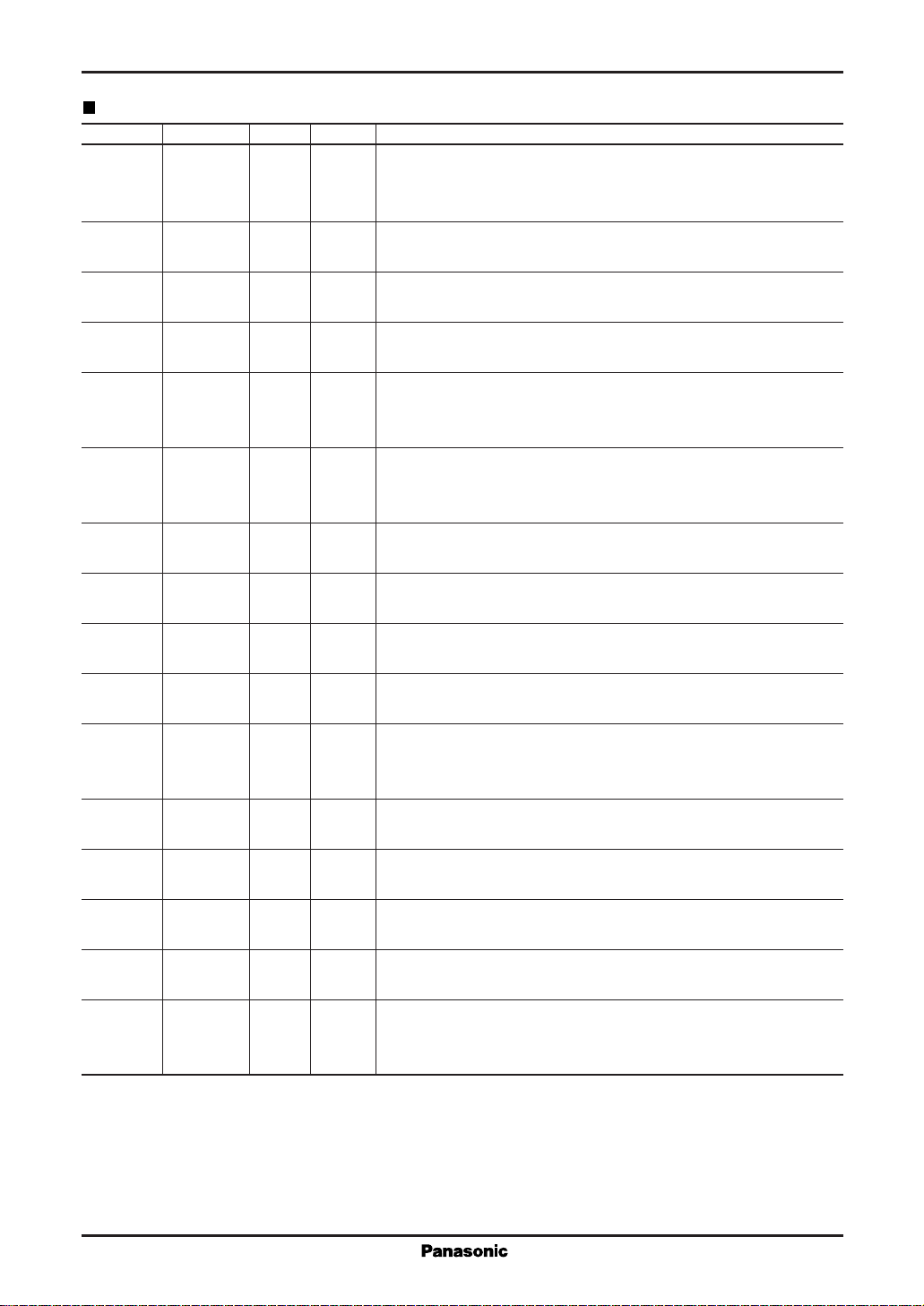

MN89303A For Information Equipment

Pin Descriptions

Pin No. Symbol I/O Level Function Description

3 AEN I TTL Address Enable

"H" level input from this pin indicates that a DMA transfer is in

progress, so the chip does not respond to I/O access.

4 SBHE I TTL Byte High Enable

This input indicates the state of the 16-bit bus.

5 IOWR I TTL I/O Write

This input indicates an I/O write request.

6 IORD I TTL I/O Read

This input indicates an I/O read request.

7 SMEMW I TTL Memory Write

This input indicates a memory write request dedicated for an address

space in the first megabyte (000000 to 0FFFFFH).

8 SMEMR I TTL Memory Read

This input indicates a memory read request dedicated for an address

space in the first megabyte (000000 to 0FFFFFH).

9 to 10 A[21:20] I TTL Address[21:20]

These inputs give the address 21:20.

11 to 30 SA[19:0] I TTL Address[19:0]

These inputs give the address 19:0.

35 to 53 SD[15:0] I/O TTL Data[15:0]

These pins represent the host data bus.

56 IOCHRDY I/O TTL I/O Channel Ready

This pin is "L" level when I/O or memory access is given wait state.

57 MEMCS16 O TTL Memory Chip Select 16

This output indicates to the system that 16-bit memory access is

available.

58 IOCS16 O TTL I/O Chip Select 16

This output indicates to the system that 16-bit I/O access is available.

32 REFRESH I TTL Refresh

"L" level input indicates that the system is refreshing its DRAM.

88 to 97 MA[9:0] O CMOS Memory Address

These outputs give the address of the display memory.

100 RAS O CMOS Row Address Strobe (RAS)

This output is the strobe signal for the row address latch.

101 UCAS O CMOS Upper Column Address Strobe (UCAS)

This output is the strobe signal for the upper column address latch.

In the 2WE mode, however, it functions as the CAS signal.

Loading...

Loading...