Panasonic MN89201 Datasheet

For Information Equipment

MN89201

VGA-NTSC Scan Converter

Overview

The MN89201 converts PC/AT VGA (640 × 480) display

data into an NTSC video signal without requiring an external

frame memory. It uses filtering to eliminate flicker and

produce a high-quality television image.

Note: PC/AT and VGA are registered trademarks of International

Business Machines Corporation.

Features

Conversion of PC/AT VGA (640 × 480) display data

into NTSC video signal

• 8-bit inputs for VGA R, G, and B signals

Horizontal frequency: 31.5 kHz

Vertical frequency: 59.94 Hz

• Conversion of non-interlaced display to interlaced

display

• Built-in phase-locked loop for synchronizing VGA

and NTSC data clocks

• Conversion from RGB to YCrCb (4:2:2) format

• Data output in NTSC display format (YCrCb24 or

YCrCb16-bit)

Flicker prevention

• Choice of line filters with 3 taps for preventing

flicker

Processing with only line memory

• No need for external VRAM

• All processing completes within built-in line memory

Choice of readout clocks for NTSC output

Choice 1: Choice of clock that has arbitrary

frequency and synchronizes with

VGA clock

External voltage-controlled

oscillator in addition to built-in

phase-locked loop

Choice 2: Choice of clock that has arbitrary

frequency and does not synchronize

with VGA clock

External oscillator

Choice 3: Clock with half frequency of the

VGA-dot-clock

Choose the clock matching the NTSC encoder.

The MN89201 offers high-quality NTSC-compatible

output from a compact configuration.

Applications

Point-of-sale terminals, Factory automation terminals,

word processors, and other terminals

MN89201 For Information Equipment

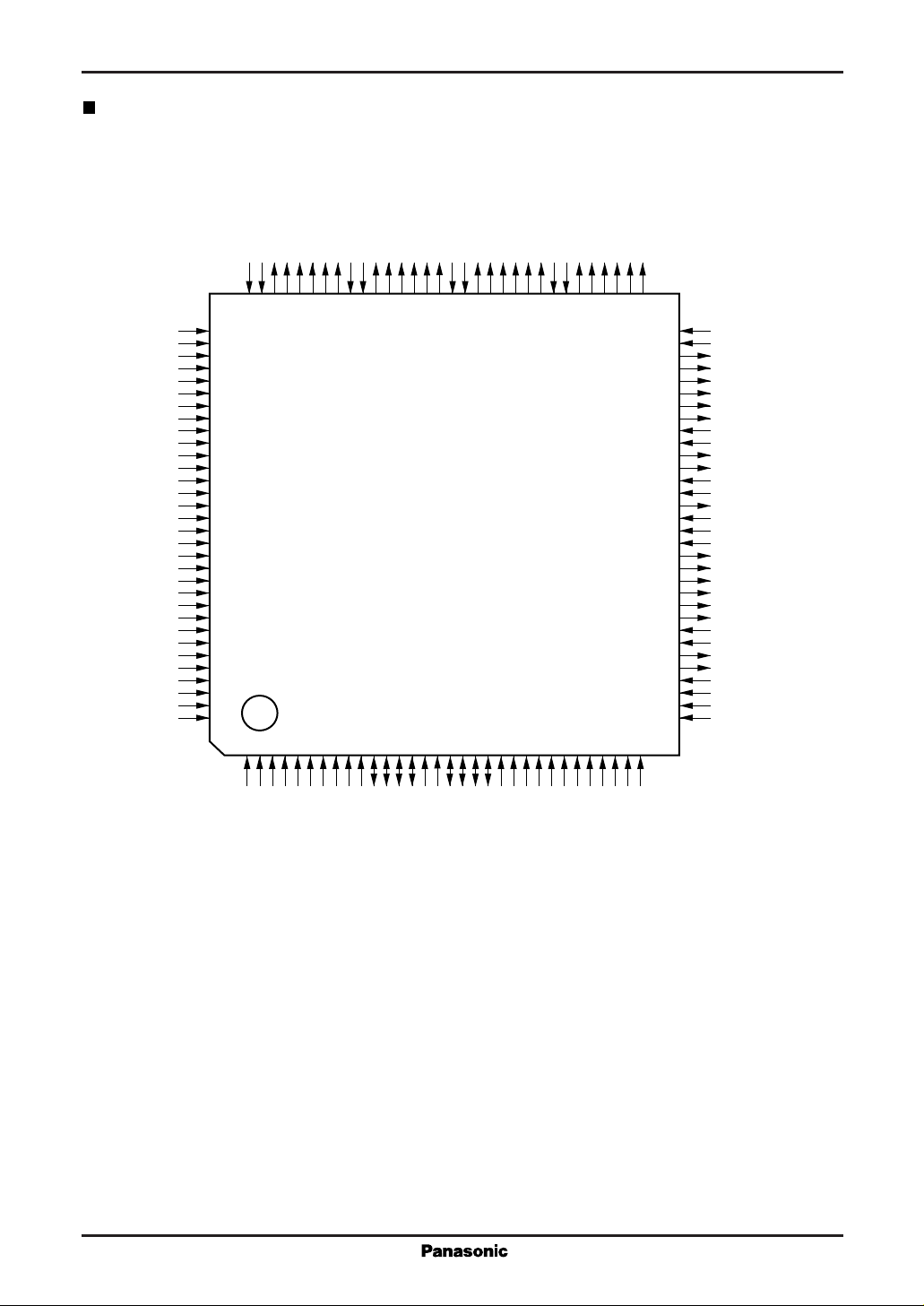

Pin Assignment

SSVDD

YOUT7

YOUT6

YOUT5

YOUT4

YOUT3

YOUT2

VSSVDDYOUT1

YOUT0

CROUT7

CROUT6

CROUT5

CROUT4

VSSVDDCROUT3

CROUT2

CROUT1

CROUT0

CBOUT7

CBOUT6

VSSVDDCBOUT5

CBOUT4

CBOUT3

CBOUT2

CBOUT1

V

CBOUT0

TEST0

TEST1

TEST2

TEST3

TEST4

BIN0

BIN1

BIN2

BIN3

BIN4

BIN5

BIN6

BIN7

GIN0

GIN1

GIN2

GIN3

GIN4

GIN5

GIN6

GIN7

RIN0

RIN1

RIN2

RIN3

RIN4

RIN5

RIN6

RIN7

XVSYNCIN

XHSYNCIN

DOTCLK

96959493929190898887868584838281807978777675747372717069686766

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

12345678910111213141516171819202122232425262728293031

SS

DD

V

V

AEN

XRD

XWE

RA3

RA2

RA1

RA0

REGLIN

DB7

DB6

DB5

DB4

SS

DD

V

V

DB3

DB2

DB1

DB0

SS

DD

V

V

RESET

MODSET1

MODSET0

MODPIN

MOD422F

MODVFIL

MODHFIL

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

MON1

MON0

MINTEST

V

DD

V

SS

RDCLK

XENCRST

XBLANK

XVSYNC

XHSYNC

RD2CLK

V

DD

V

SS

OEON

OEOP

V

DD

V

SS

XOO

OSXIN

V

DD

V

SS

MEMOUT0

MEMOUT1

MEMOUT2

MEMOUT3

MEMOUT4

MEMOUT5

V

DD

V

SS

MEMOUT6

MEMOUT7

MODST

MODCHAV

MODCRCB

SXRST

Note: Never leave V

QFH128-P-1818

and VSS pins open.

DD

(TOP VIEW)

For Information Equipment MN89201

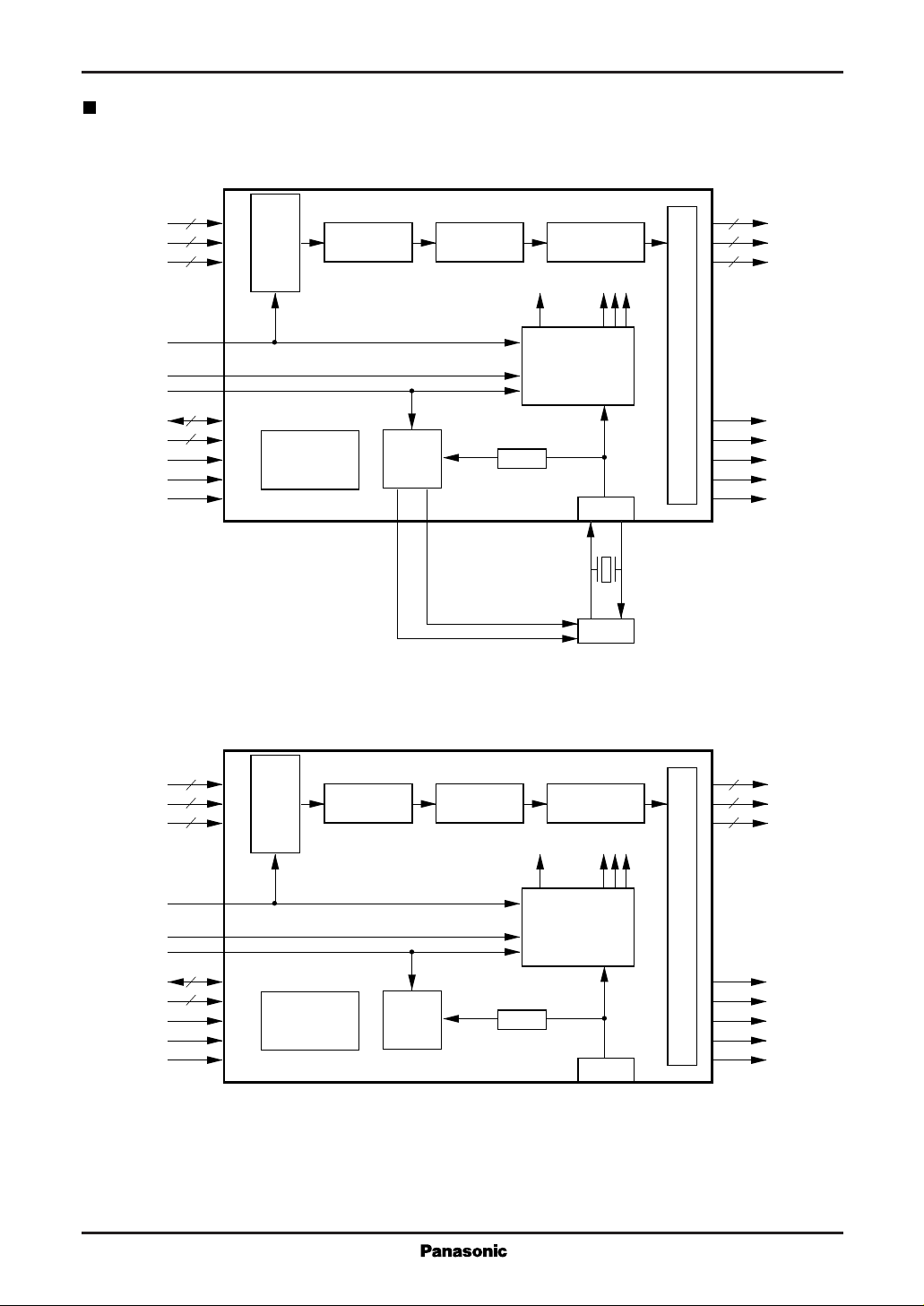

Block Diagram

• RDCLK from an external VCO clock synchronized with VGA clock

8

R

8

G

8

B

DOTCLK

XVSYNCIN

XHSYNCIN

DB[7:0]

RA[3:0]

8

4

CS (AEN)

WR

RD

• RDCLK from VGA clock

Latch

RGB-YCrCb

converter

Flicker

elimination

block

Registers PLL 1/N

OEOP

Conversion from

non-interlaced to

interlaced display

Control block

counters,

pulse generator, etc.

lead

lag

OSC I/F

VCO

8

Y

8

Cr

8

Cb

Coding interface

XVSYNC

XHSYNC

BLANK

RD2CLK

RDCLK

XOOOSXINOEON

DOTCLK

XVSYNCIN

XHSYNCIN

DB[7:0]

RA[3:0]

CS (AEN)

WR

RD

8

R

8

G

8

B

Latch

RGB-YCrCb

converter

Flicker

elimination

block

Conversion from

non-interlaced to

interlaced display

Control block

counters,

pulse generator, etc.

8

Y

8

Cr

8

Cb

Coding interface

8

4

Registers PLL 1/N

XVSYNC

XHSYNC

BLANK

RD2CLK

OSC I/F

RDCLK

MN89201 For Information Equipment

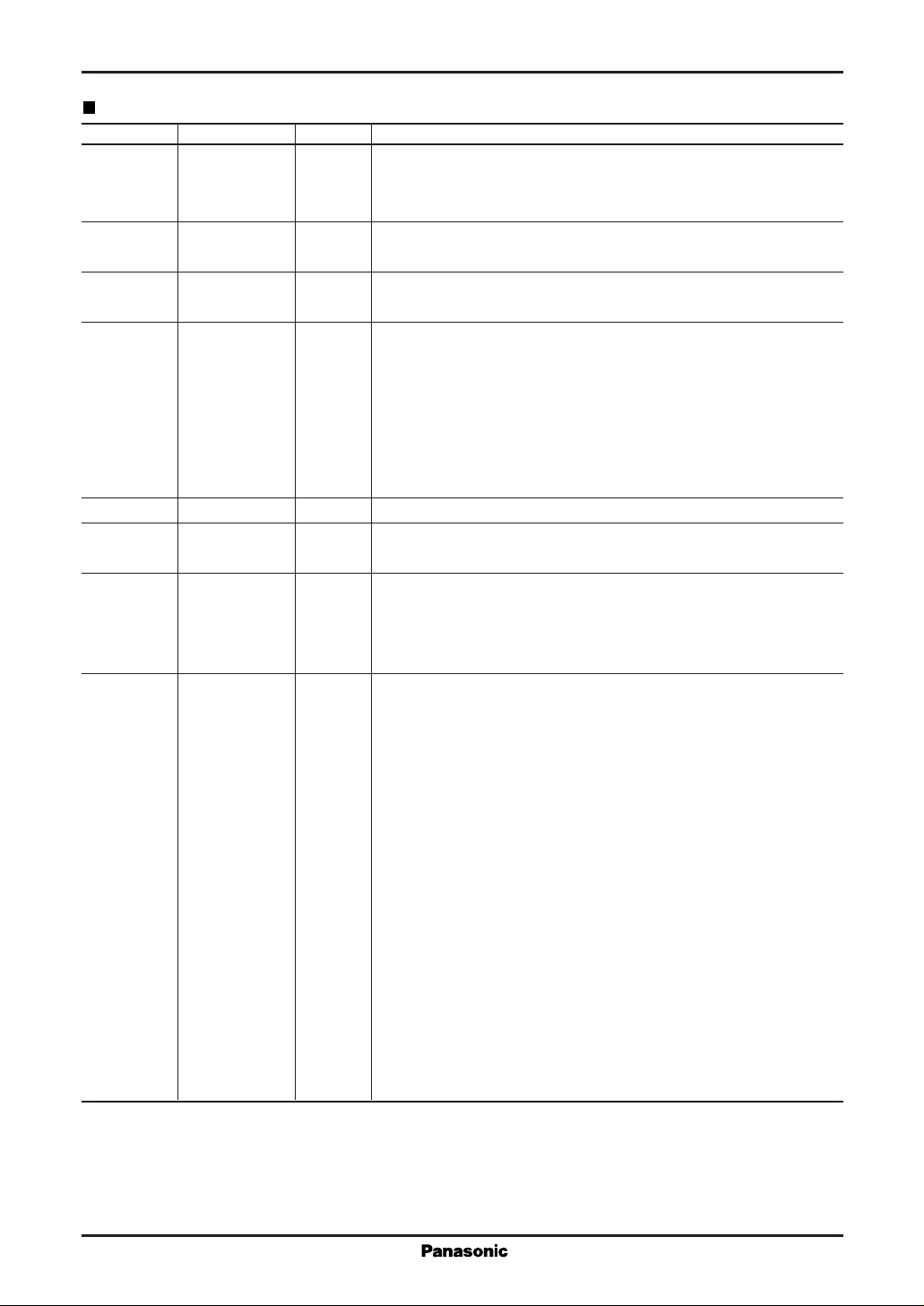

Pin Descriptions

Pin No. Symbol I/O Function Description

3 AEN I Chip select signal

"L" level: Register access enabled

"H" level: Register access disabled

4 XRD I Read control signal

"L" level: Read enabled

5 XWE I Write control signal

"L" level: Write enabled

6 REGLIN I Register address mode specification

"H" level: Obtain register address from RA[3:0]

"L" level: Obtain register address from address register

In the latter case, the address of the parameter/mode register are

specified by the address register .

Address register: 0H (4-bit decode)

Data register: 1H (4-bit decode)

7 to 10 RA[3:0] I Register address specification

11 to 14 DB[7:0] I Host data bus

17 to 20

23 RESET I MN89201 reset signal

Active "H"

This signal initializes internal registers to their default values and

resets internal synchronization counters.

24 ,25 MODSET[1:0] I Synchronization mode specification pins

These specify the RDCLK synchronization mode for output signals

to the NTSC encoder

(1:0)

0 0: Use an external VCO clock signal synchronized with the VGA

clock signal for RDCLK. The XH, XVSYNC, XBLANK, and

XENRST signals are generated inside the MN89201 and are

outputted. (synchronous)

0 1: Use an external oscillator clock signal not synchronized with

the VGA clock signal for RDCLK. The XH and XVSYNC

signals are retimed versions of the VGA H and VSYNC

signals. (asynchronous)

The other outputs use the VGA DOTCLK signal.

1 0: Use the VGA DOTCLK signal for RDCLK. The YCrCb data,

XVSYNC, XBLANK, and XENRST signals all are dealt in

the VGA clock. An external oscillator is not necessary.

(synchronous)

Loading...

Loading...