Panasonic MN88831 Datasheet

For Video Equipment

MN88831

PCM Audio Decoder LSI for Satellite Broadcasting Tuners

(Includes Built-In Digital Filter and D/A Converter)

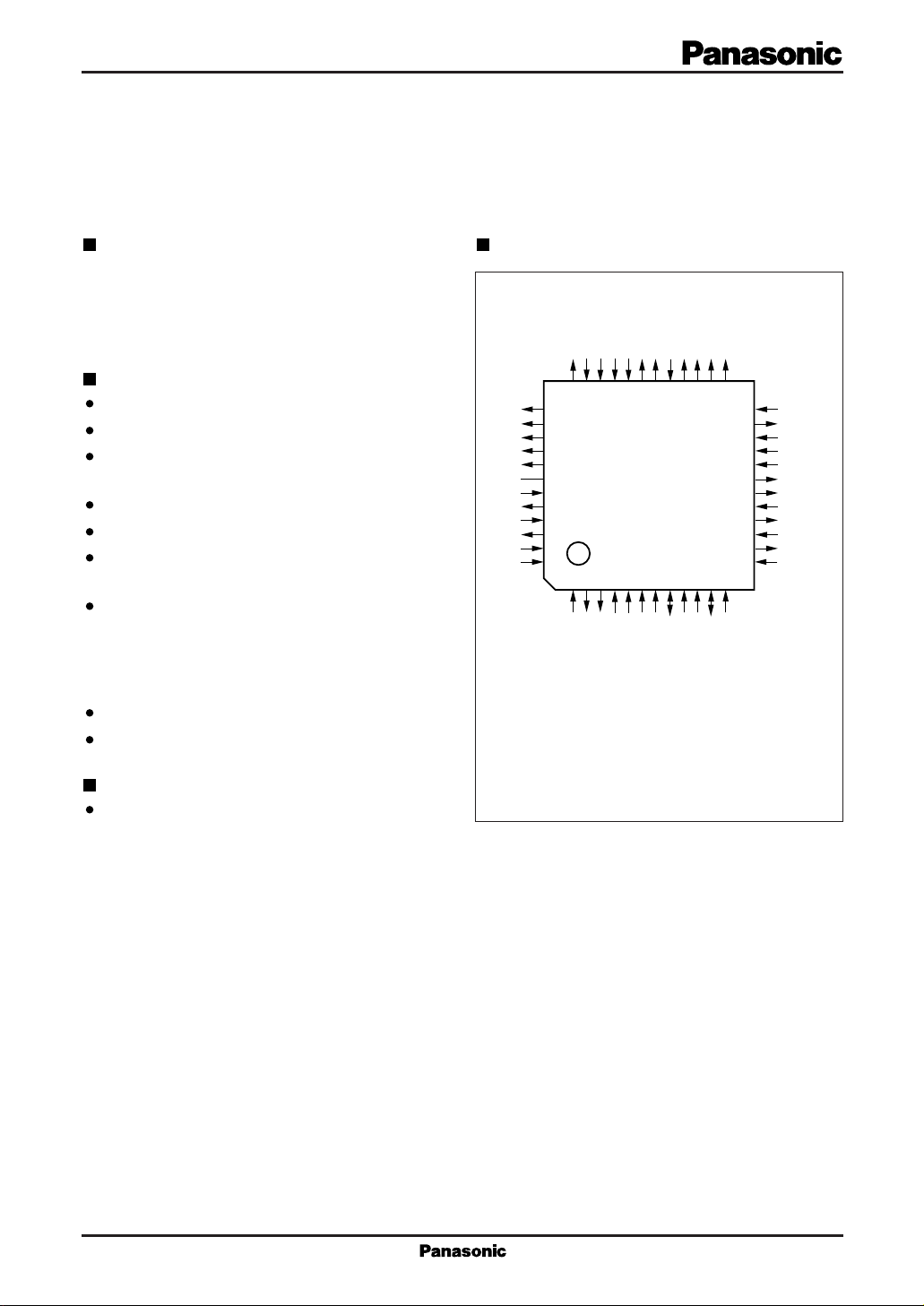

Pin Assignment Overview

The MN88831 greatly streamlines set design by incorporating a satellite broadcasting PCM audio decoder, a

switched capacitor D/A converter, and analog post filter

to a single chip.

Features

Built-in digital filter using 8-fold oversampling

Built-in tertiary ∆-∑ noise shaping D/A converter

Reduced jitter noise through use of switched

capacitor configuration

Built-in analog post filter

Built-in digital de-emphasis circuit

Choice of microcomputer interfaces with selector pin:

3-wired serial interface or I

Muting function supporting following settings

• Pay-per-view flag detection

• Error frequency detection

• Detection of control code bit-7

Built-in general-purpose microcomputer I/O port

Bit stream input pin supporting 0.4 V

2

C interface

P-P

input

DV

PO1

PO2

PO3

PO4

PC

IV

IV

XO

IIN

OIN

SS

I

O

XI

PO0/MTO

PI2

PI1

DVDDBSTIN

BSTRM

3635343332313029282726

37

38

39

40

41

42

43

44

45

46

47

48

1234567891011

DD

PO5

TES0

IFSEL

PO6/LIBP

TES1

DV

(TOP VIEW)

SYNCF

DCDI

ECDO

P2M

CHV

CS/SA

CCK/SCL

CWO/IFMOD

NAMODE

BPO

25

24

23

22

21

20

19

18

17

16

15

14

13

12

SS

DV

CTLI/SDA

NTI

NLOCK

NRES

DV

SS

AV

DDR

V

REF

OUTR

AV

SSR

BIAS

AV

SSL

OUTL

AV

DDL

Applications

Satellite broadcasting tuners (BS, CS)

QFP048-P-1212A

MN88831 For Video Equipment

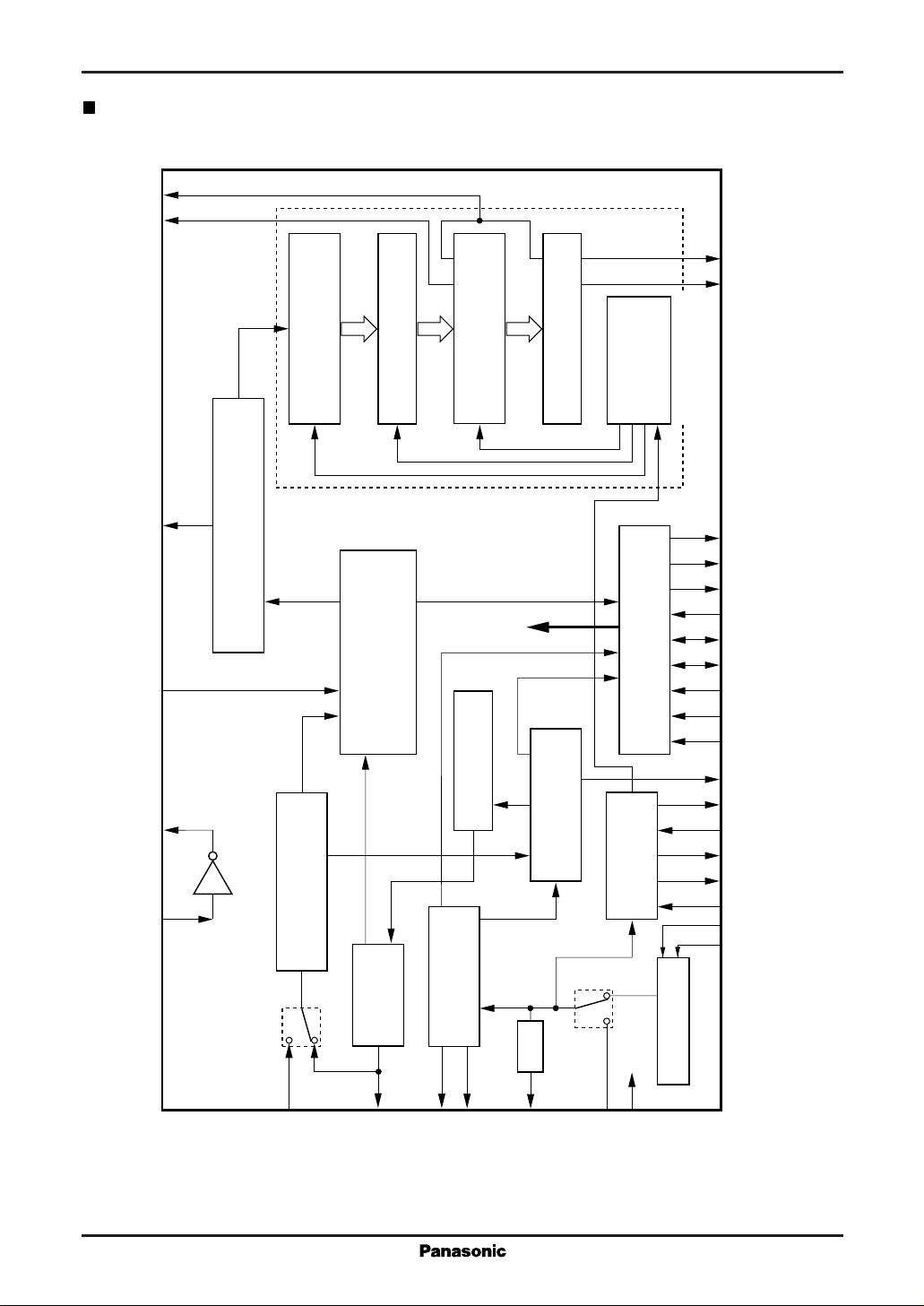

Block Diagram

BIAS

V

REF

BPO

MTI

IV

IV

16

19

18

OUTR

14

OUTL

Digital filter

Digital de-emphasis

∆–Σ noise shaper

Switched capacitor D/A

converter

Analog post filter

25

for

Timing generator

D/A converter block

(D/A converter block)

3

PO6/LIBP

PO1 to PO5

C bus

2

Serial or I

VCO

34,35

36

8

11

10

9

4

26

27

7

41

46

45

47

48

PO0/MTO

PI1,PI2

CWO/IFMOD

CTLI/SDA

CCK/SCL

CS/SA

IFSEL

NAMODE

P2M

CHV

PC

XO

XI

IIN

QIN

Data output control

Digital audio interface

24

A mode data expansion

Incompatible data range detection

Data interpolation

Muting

(

MTO

(

LIBP

)

)

Microcomputer interface:

De-interleaving

44

O

Descramble control code

integration and detection

43

I

Range bit detection and

correction.

)

DE

(

Pay-per-view flag detection

Clock generator

SW1

SW2

Duplex error

detection and

correction

Frame synchronization

detection

Timing generator

29

28

23

30

1 T

Differential decoder

serialization

22

31

32

ECDI

ECDO

SYNCF

NLOCK

BSTRM

NRES

BSTIN

Loading...

Loading...