Panasonic MN86062 Datasheet

For Communications Equipment

MN86062

CODEC LSI for Facsimile Images

Overview

The MN86062 is a high-speed LSI codec for compressing

and decompressing images using the MH, MR, and MMR

standard compression methods specified in the ITU-T T.4

and T.6 recommendation. Registers and other settings

provide flexible support for a variety of processing.

Features

Compression methods

MH, MR, and MMR

Operating mode:

Page mode

Bus configuration:

Choice of dual- or single-bus operation

Decoding error processing:

Choice of replacing with the previous line or a

white line

Image bus configuration:

8 bits, maximum 16 megabytes address

space of image bus, 2-channel master DMA

System bus configuration:

X80 interface compatible, 8 bits, 2-channel

slave DMA

Pixels per line:

maximum 64K, in byte increments

Concurrent DMA transfers over image bus and

command processing

Support for pointer management for image buffer

Wide selection of independent parameters for coding,

decoding, transfers between buses, and DMA

transfersr

Support for time-shared processing by line for both

coding and decoding

Applications

Facsimile equipment

MN86062 For Communications Equipment

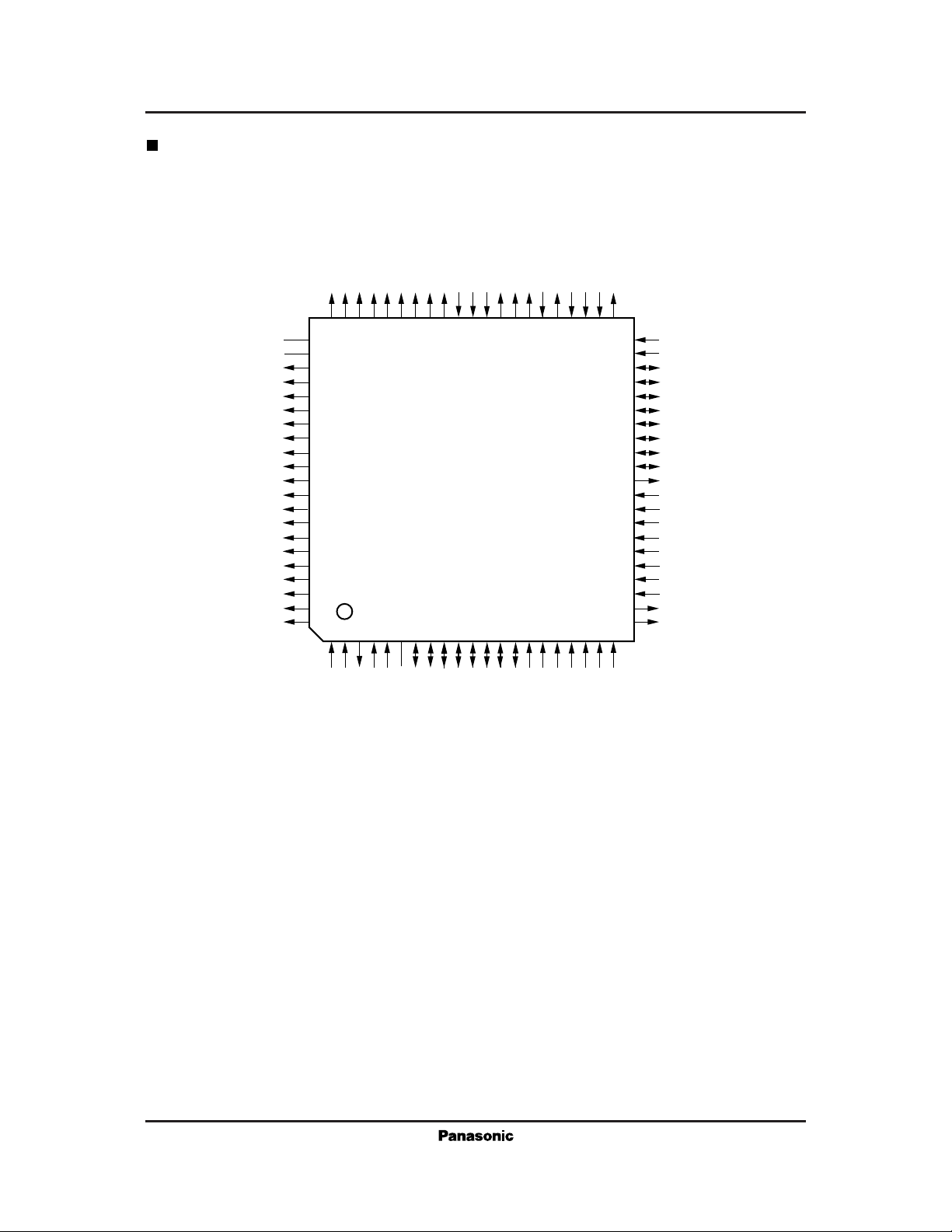

Pin Assignment

N.C.1

N.C.2

IA18

IA17

IA16

IA15

IA14

IA13

IA12

IA11

IA10

IA9

IA8

IA7

IA6

IA5

IA4

IA3

IA2

IA1

IA0

IA19

IA20

IA21

IA22

IA23

NDCMP

NDEND

NDACK1

NDACK0

NDREQ1

NDREQ0

NIDACK

IR/W

NIAEN

NDRUN

NIBACK

NIBREQ

2SYSCLK

636261605958575655545352515049484746454443

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

123456789101112131415161718192021

SS2

SS3

DD2

DD3

ID7

ID6

ID5

ID4

ID3

V

V

V

V

N.C.3

TACK

ID2

ID1

ID0

V

DD4

SS4

V

TEST2

TEST1

DD1VSS1

V

TEST0

NACKD

SYSCLK

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

NACKC

TEST3

TEST4

D0

D1

D2

D3

D4

D5

D6

D7

NIRQ

NRESET

A0

A1

A2

A3

NCS

NRD

NWT

NREQC

NREQD

(TOP VIEW)

QFP084-P-1818

For Communications Equipment MN86062

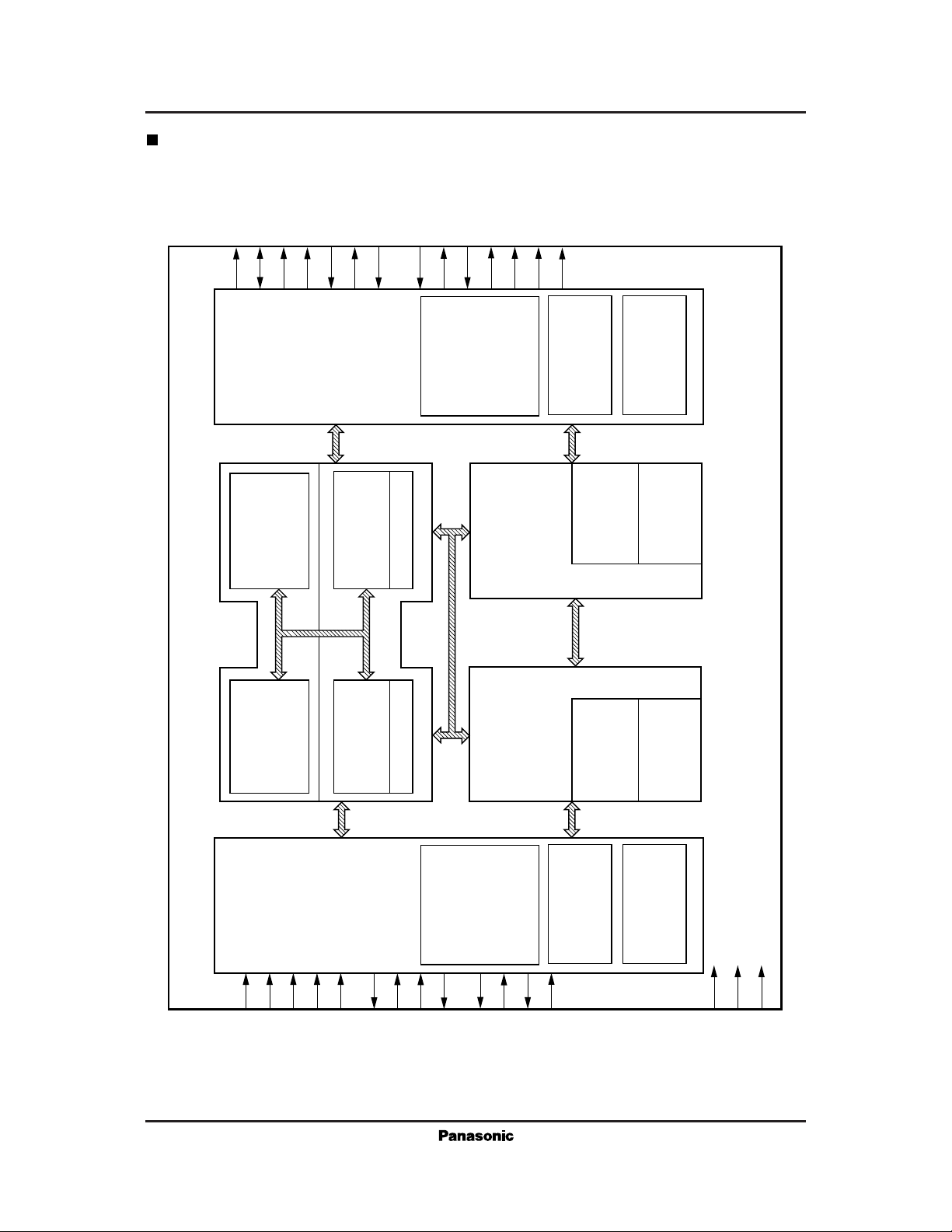

Block Diagram

IA(23:0)

ID(7:0)

IR/W

NIAEN

NIDACK

NIBREQ

NIBACK

51

50

52

Image bus interface

Sub sequencer

NDREQ0

47

48

53

Parameter register

NDACK0

55

54

NDREQ1

NDACK1

NDRUN

56

49

Master DMA

(2 channels)

NDEND

NDCMP

57

58

Reference line FIFO

Change point

detector

Mode selection block

Coding line FIFO

Image

reconstruction

block

Microprogram control block

Main sequencer

System bus

interface

25

NCS

A(3:0)

D(7:0)

NRD

24

NWT

ALU1 ALU2

32

NIRQ

Register bank

314643

NRESET

2SYSCLK

Slave DMA

23

SYSCLK

Table look-up block

(2 channels)

21

22

NREQC

NACKC

20

NREQD

NACKD

Coding table

Coding FIFO

Decoding table

Decoding FIFO

DD

V

SS

V

TEST(4:0)

Loading...

Loading...