Panasonic MN662740RE Datasheet

For Audio Equipment

MN662740RE

Signal Processing LSI for CD Players

Overview

The MN662740RE is a CD signal processing LSI that,

on a single chip, combines an optics servo for the CD

player (focus, tracking, and traverse servos), digital signal

processing (EFM demodulation and error correction),

digital servo processing for the spindle motor, digital

filter, and D/A converter, so thus covers all signal

processing functions from the head's RF amplifier onward.

Features

(Optics servo)

Focus, tracking, and traverse servos

Automatic adjustment functions for FO/TR gain,

FO/TR offset, and FO/TR balance

Built-in D/A converter for drive voltage output

Built-in dropout countermeasures

Anti-shock functions

Built-in track cross counter

Support for both linear motor and screw-based traverse

mechanisms

Support for 3- and 1-beam systems

(Spindle motor servo)

(Audio circuits)

(Other)

CLV digital servo

Digital filter using 8-fold oversampling

Built-in D/A converter (1-bit D/A converter)

Built-in differential operational amplifier (2nd order

low pass filter)

Built-in playback pitch control function (±13%)

Guaranteed operation for double-speed playback

except for D/A converter output and 4 f

output

Operating voltage 3.0 to 5.5V

mode serial

s

Applications

CD Players

(Digital signal processing)

Built-in DSL and PLL

Frame synchronization detection, holding, and insertion

Subcode data processing

Q data CRC check

Built-in Q data register

CIRC error detection and correction

C1 decoder: duplex error correction

C2 decoder: triplex error correction

Built-in 16-K bits of RAM for de-interleaving

Audio data interpolation

Four-sample average, hold of previous values

Soft muting

Digital attenuation (256 levels)

Software attenuation (256 levels)

Audio data peak level detection function

Auto cue detection function

Digital audio interface (EIAJ format)

Audio data serial interface for input and output

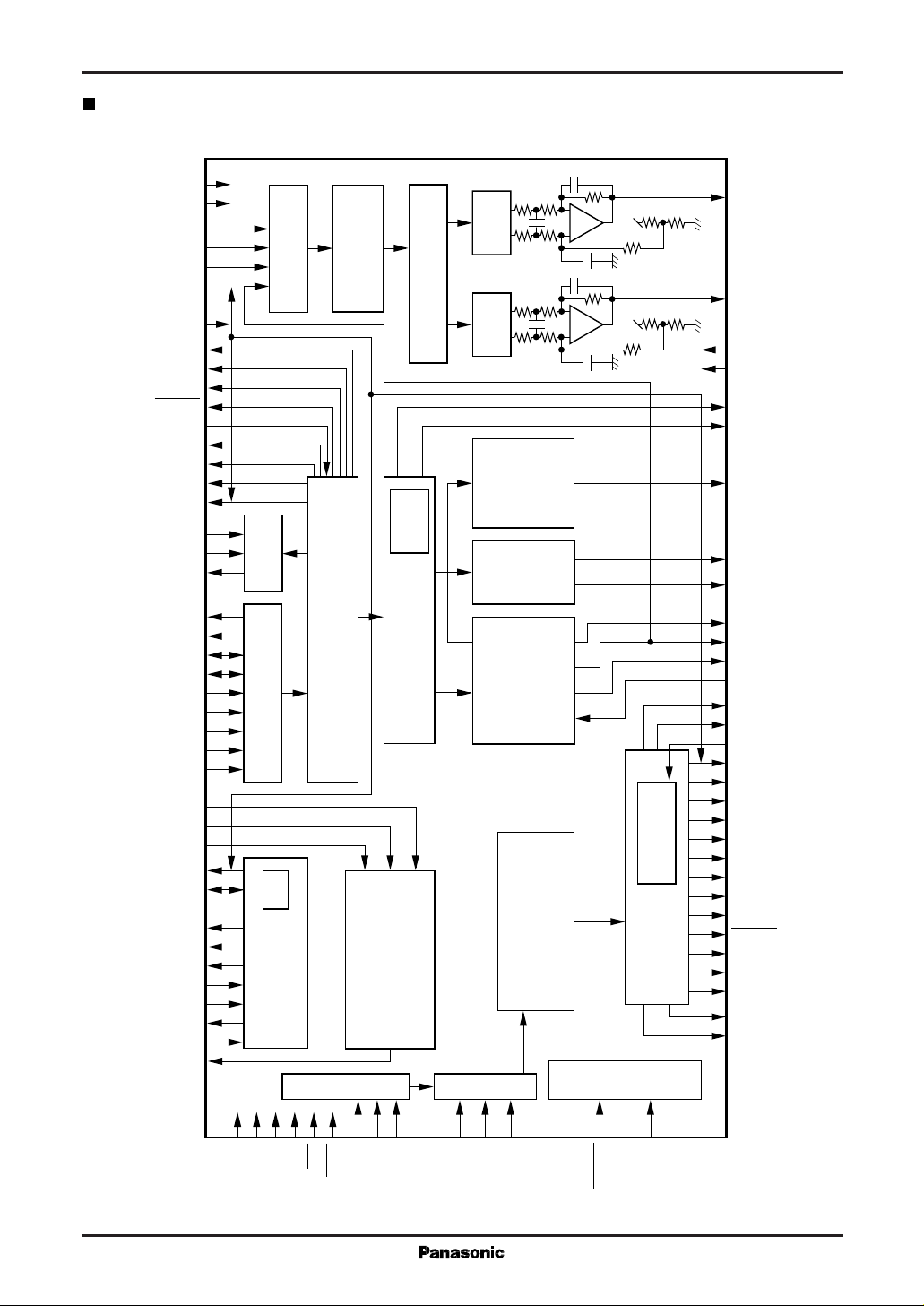

MN662740RE For Audio Equipment

Block Diagram

51

AV

SS2

AV

DD2

LRCKIN/MSEL

BCLKIN/SSEL

SRDATEIN/PSEL

IOSEL

CLVS

CRC

BLKCK

CLDCK

SBCK

SUBC

DEMPH

RESY

FLAG6/RESY

SSEL

SQCK

SUBQ

PCK

EFM

PLLF

DSLF

I

REF

DRF

ARF

RSEL

PSEL

MLD

MCLK

MDATA

CK384/EFM

VCOF

SMCK

FCLK

PMCK

CSEL

MSEL

X2

X1

STAT

50

)

R

(

PWM

DIGITAL

DEEMPHASIS

8 TIMES

OVER SAMPLING

DIGITAL FILTER

70

66

LOGICS

1 BIT DAC

)

L

(

PWM

–

+

–

+

67

13

62

56

55

68

69

DIGITAL

AUDIO

CLV

SERVO

INTERFACE

80

16K

14

15

BUFFER

SUBCODE

SRAM

53

52

48

47

45

46

44

76

DSL•PLL VCO

EFM DEMODULATION

SYNC INTERPOLATION

CIRC ERROR CORRECTION

SUBCODE DEMODULATION

DEINTERLEAVE

INTERPOLATION

SOFT MUTING

DIGITAL

ATTENUATION

PEAK DETECT

AUTO CUE

78

9

7

8

49

VCO

19

63

20

SERVO CPU

77

79

59

TIMING

GENERATOR

58

PITCH CONTROL

INTERFACE

MICROCOMPUTER

17

A/D CONVERTER INPUT PORT

SERVO

TIMING GENERATOR

D/A

CONVERTER

OUTPUT

PORT

75

OUTR

73

OUTL

74

AV

SS1

72

AV

DD1

65

FLAG

64

IPFLAG

6

TX

24

ECM

23

PC

2

LRCK

3

SRDATA

1

BCLK

16

DMUTE

21

TRV

26

KICK

29

V

REF

61

BYTCK/TRVSTOP

25

ECS

22

TVD

27

TRD

28

FOD

31

TBAL

30

FBAL

54

TOFS

41

TES

12

TLOCK

11

FLOCK

42

PLAY

40

LDON

43

WVEL

10

SENSE

605745187132

SS

DD

V

SS1

DD1

V

DV

DV

RST

TEST

33TE34

FE

RFENV

37

TRCRS

35

VDET

39

BDO

38

RFDET

36

OFT

Loading...

Loading...