Page 1

MICROCOMPUTER MN1030

MN103001G/F01K

LSI User’ s Manual

Pub.No.23101-050E

Page 2

Page 3

PanaX Series is a trademark of Matsushita Electric Industrial Co., Ltd.

The other corporation names, logotype and product names written in this book are trademarks or registered trademarks of their

corresponding corporations.

Request for your special attention and precautions in using the technical

informaition and semiconductors described in this book

(1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of

the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign

Trade Law" is to be exported or taken out of Japan.

(2) The contents of this book are subject to change without notice in matters of improved function.When

finalizing your design, therefore, ask for the most up-to-date version in advance in order to check for any

changes.

(3) We are not liable for any damage arising out of the use of the contents of this book, or for any infringement

of patents or any other rights owned by a third party.

(4) No part of this book may be reprinted or reproduced by any means without written permission from our

company.

(5) This book deals with standard specification. Ask for the latest individual Product Standards or Specifications

in advance for more detailsd infomation required for your design, purchasing and applications.

If you have any inquiries or questions about this book or our semiconductors, please contact one of our sales

offices listed at the back of this book.

Page 4

Page 5

Table of Contents/List of Figures and Tables

0

1. General Specifications

2. CPU

3. Extension Instruction Specifications

4. Memory Modes

5. Operating Mode

6. Clock Generator

1

2

3

4

5

6

7. Internal Memory

8. Bus Controller (BC)

9. Interrupt Controller

10. 8-bit Timers

11. 16-bit Timers

12. Watchdog Timer

7

8

9

10

11

12

13. Serial Interface

13

Page 6

Page 7

14. A/D Converter

14

15. I/O Ports

16. Internal Flash Memory

17. Ordering Mask ROM

Appendix

15

16

17

Page 8

Page 9

Table of Contents/List of Figures and Tables

0

Page 10

Table of Contents

1. General Specifications

1.1 Overview........................................................................................................................ 1-2

1.2 Features .......................................................................................................................... 1-2

1.3 Block Diagram ............................................................................................................... 1-4

1.4 Pin Description............................................................................................................... 1-5

1.4.1 Pin Assignments............................................................................................ 1-5

1.4.2 Pin Functions ................................................................................................ 1-7

2. CPU

2.1 Basic Specifications of CPU .......................................................................................... 2-2

2.2 Block Diagram ............................................................................................................... 2-3

2.3 Programming Model ...................................................................................................... 2-4

2.3.1 CPU Registers ............................................................................................... 2-4

2.3.2 Control Registers .......................................................................................... 2-7

2.4 Instructions................................................................................................................... 2-10

2.4.1 Addressing Modes ...................................................................................... 2-10

2.4.2 Data Types .................................................................................................. 2-11

2.4.3 Instruction Set ............................................................................................. 2-12

2.5 Interrupts ...................................................................................................................... 2-14

2.5.1 Overview of Interrupts ................................................................................ 2-14

2.5.2 Registers...................................................................................................... 2-15

2.5.3 Interrupt Types............................................................................................ 2-18

2.5.4 Interrupt Definition ..................................................................................... 2-19

3. Extension Instruction Specifications

3.1 Operation Extension Function ....................................................................................... 3-2

3.2 Extension Instructions.................................................................................................... 3-3

3.2.1 Explanation of Notations .............................................................................. 3-3

3.2.2 Extension Block Register Set........................................................................ 3-4

3.2.3 Extension Instruction Details ........................................................................ 3-5

3.2.4 Programming Notes .................................................................................... 3-31

4. Memory Modes

4.1 Memory Mode Types and Selection .............................................................................. 4-2

4.2 Memory Mode Pin Processing....................................................................................... 4-3

4.3 Description of Memory Mode ....................................................................................... 4-4

4.3.1 Memory Extension Mode ............................................................................. 4-4

4.3.2 Processor Mode............................................................................................. 4-5

ii

Page 11

5. Operating Mode

5.1 Overview........................................................................................................................ 5-2

5.2 Reset Mode .................................................................................................................... 5-3

5.3 Low Power Mode........................................................................................................... 5-4

6. Clock Generator

6.1 Overview........................................................................................................................ 6-2

6.2 Features .......................................................................................................................... 6-2

6.3 Block Diagram ............................................................................................................... 6-2

6.4 Description of Operation................................................................................................ 6-3

6.4.1 Input Frequency Setting ................................................................................ 6-3

6.4.2 Internal Clock Supply ................................................................................... 6-3

7. Internal Memory

7.1 Overview........................................................................................................................ 7-2

7.2 Features .......................................................................................................................... 7-2

7.3 Internal Memory Configuration ..................................................................................... 7-3

8. Bus Controller (BC)

8.1 Overview........................................................................................................................ 8-2

8.2 Features .......................................................................................................................... 8-2

8.3 Bus Configuration .......................................................................................................... 8-3

8.4 Block Diagram ............................................................................................................... 8-3

8.5 Pin Functions ................................................................................................................. 8-5

8.6 Description of Registers................................................................................................. 8-7

8.6.1 Memory Block 0 Control Register................................................................ 8-8

8.6.2 Memory Block 1 Control Register.............................................................. 8-10

8.6.3 Memory Block 2 Control Register.............................................................. 8-14

8.6.4 Memory Block 3 Control Register.............................................................. 8-19

8.6.5 DRAM control register ............................................................................... 8-22

8.6.6 Refresh count register ................................................................................. 8-23

8.6.7 Page Row Address Register........................................................................ 8-24

8.6.8 Clock Control Register ............................................................................... 8-24

8.7 Space Partitioning ........................................................................................................ 8-26

8.8 Operation Clocks ......................................................................................................... 8-28

8.9 Mode Settings .............................................................................................................. 8-28

8.10 Bus Cycle ..................................................................................................................... 8-29

8.11 Store Buffer.................................................................................................................. 8-30

8.12 Accessing the Internal I/O Space ................................................................................. 8-31

8.13 External Memory Space Access

(Non-DRAM Spaces).................................................................................... 8-32

8.13.1 16-bit Bus with Fixed Wait States, in Synchronous Mode

and in Address/Data Separate Mode........................................................... 8-33

iii

Page 12

8.13.2 16-bit Bus with Handshaking, in Synchronous Mode and in

Address/Data Separate Mode...................................................................... 8-35

8.13.3 16-bit Bus in Asynchronous Mode and in Address/Data

Separate Mode ............................................................................................ 8-37

8.13.4 8-bit Bus with Fixed Wait States, in Synchronous Mode

and in Address/Data Separate Mode........................................................... 8-39

8.13.5 8-bit Bus with Handshaking, in Synchronous Mode and in

Address/Data Separate Mode...................................................................... 8-41

8.13.6 8-bit Bus in Asynchronous Mode and in Address/Data

Separate Mode ............................................................................................ 8-45

8.13.7 16-bit Bus with Fixed Wait States, in Synchronous Mode

and in Address/Data Multiplex Mode......................................................... 8-46

8.13.8 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode................................................................ 8-48

8.13.9 16-bit Bus in Asynchronous Mode and in Address/Data

Multiplex Mode .......................................................................................... 8-51

8.13.10 8-bit Bus with Fixed Wait States, in Synchronous Mode

and in Address/Data Multiplex Mode......................................................... 8-52

8.13.11 8-bit Bus with Handshaking, in Synchronous Mode and in

Address/Data Multiplex Mode.................................................................... 8-56

8.13.12 8-bit Bus in Asynchronous Mode and in Address/Data

Multiplex Mode .......................................................................................... 8-60

8.14 External Memory Space Access (DRAM Space) ........................................................ 8-62

8.14.1 DRAM Space .............................................................................................. 8-62

8.14.2 DRAM page mode ...................................................................................... 8-65

8.14.3 Software Page Mode ................................................................................... 8-66

8.14.4 DRAM refresh ............................................................................................ 8-68

8.15 Bus Arbitration.............................................................................................................8-70

8.16 Cautions ....................................................................................................................... 8-73

9. Interrupt Controller

9.1 Overview........................................................................................................................ 9-2

9.2 Features .......................................................................................................................... 9-2

9.3 System Diagram............................................................................................................. 9-2

9.4 Block Diagram ............................................................................................................... 9-3

9.5 Description of Registers................................................................................................. 9-6

9.6 Description of Operation.............................................................................................. 9-30

10. 8-bit Timers

10.1 Overview...................................................................................................................... 10-2

10.2 Features ........................................................................................................................ 10-2

10.3 Block Diagram ............................................................................................................. 10-3

10.4 Functions...................................................................................................................... 10-9

10.5 Description of Registers............................................................................................. 10-10

iv

Page 13

10.6 Description of Operation............................................................................................ 10-20

10.6.1 Interval Timers and Timer Output ............................................................ 10-20

10.6.2 Event Counting ......................................................................................... 10-24

10.6.3 Cascaded Connection................................................................................ 10-26

10.6.4 PWM Output ............................................................................................. 10-31

11. 16-bit Timers

11.1 Overview...................................................................................................................... 11-2

11.2 Features ........................................................................................................................ 11-2

11.3 Block Diagram ............................................................................................................. 11-3

11.4 Functions...................................................................................................................... 11-7

11.5 Description of Registers............................................................................................... 11-8

11.6 Description of Operation of Timer 10 ....................................................................... 11-18

11.6.1 Compare Register Settings........................................................................ 11-18

11.6.2 Capture Register Settings.......................................................................... 11-19

11.6.3 Pin Output Settings ................................................................................... 11-21

11.6.4 Starting by an External Trigger................................................................. 11-24

11.6.5 One-shot Operation ................................................................................... 11-26

11.6.6 Interval Timer ........................................................................................... 11-28

11.6.7 Event Counting ......................................................................................... 11-31

11.7 Description of Operation of Timers 11, 12 and 13 .................................................... 11-33

11.7.1 Interval Timer and Timer Output.............................................................. 11-33

11.7.2 Event Counting ......................................................................................... 11-36

12. Watchdog Timer

12.1 Overview...................................................................................................................... 12-2

12.2 Features ........................................................................................................................ 12-2

12.3 Block Diagram ............................................................................................................. 12-3

12.4 Description of Registers............................................................................................... 12-4

12.5 Description of Operation.............................................................................................. 12-7

13. Serial Interface

13.1 Overview...................................................................................................................... 13-2

13.2 General-purpose serial interface .................................................................................. 13-3

13.2.1 Features ....................................................................................................... 13-3

13.2.2 Block Diagram of General-Purpose Serial Interface .................................. 13-5

13.2.3 Description of Registers for the General-Purpose Serial Interface............. 13-6

13.2.4 Description of Operation........................................................................... 13-10

13.3 Clock Synchronous Serial Interface........................................................................... 13-24

13.3.1 Features ..................................................................................................... 13-24

13.3.2 Block Diagram of Clock Synchronous Serial Interface............................ 13-25

13.3.3 Description of Registers for the Clock Synchronous Serial Interface ...... 13-26

13.3.4 Description of Operation........................................................................... 13-32

13.4 Universal Asynchronous Receiver-Transceiver Serial Interface ............................... 13-36

13.4.1 Features ..................................................................................................... 13-36

v

Page 14

13.4.2 Block Diagram of UART Serial Interface ................................................ 13-37

13.4.3 Description of Registers for the UART Serial Interface........................... 13-38

13.4.4 Description of Operation........................................................................... 13-45

14. A/D Converter

14.1 Overview...................................................................................................................... 14-2

14.2 Features ........................................................................................................................ 14-3

14.3 Block Diagram ............................................................................................................. 14-4

14.4 Description of Registers............................................................................................... 14-5

14.5 Description of Operation.............................................................................................. 14-7

15. I/O Ports

15.1 Overview...................................................................................................................... 15-2

15.2 Port 0 ............................................................................................................................ 15-6

15.2.1 Block Diagram ............................................................................................ 15-6

15.2.2 Register Descriptions .................................................................................. 15-7

15.2.3 Pin Configuration........................................................................................ 15-9

15.3 Port 1 .......................................................................................................................... 15-10

15.3.1 Block Diagram .......................................................................................... 15-10

15.3.2 Register Descriptions ................................................................................ 15-12

15.3.3 Pin Configuration...................................................................................... 15-14

15.4 Port 2 .......................................................................................................................... 15-15

15.4.1 Block Diagram .......................................................................................... 15-15

15.4.2 Register Descriptions ................................................................................ 15-16

15.4.3 Pin Configuration...................................................................................... 15-18

15.5 Port 3 .......................................................................................................................... 15-19

15.5.1 Block Diagram .......................................................................................... 15-19

15.5.2 Register Descriptions ................................................................................ 15-20

15.5.3 Pin Configurations .................................................................................... 15-21

15.6 Port 4 .......................................................................................................................... 15-22

15.6.1 Block Diagram .......................................................................................... 15-22

15.6.2 Register Descriptions ................................................................................ 15-25

15.6.3 Pin Configurations .................................................................................... 15-28

15.7 Port 5 .......................................................................................................................... 15-29

15.7.1 Block Diagram .......................................................................................... 15-29

15.7.2 Register Descriptions ................................................................................ 15-34

15.7.3 Pin Configurations .................................................................................... 15-37

15.8 Port 6 .......................................................................................................................... 15-38

15.8.1 Block Diagram .......................................................................................... 15-38

15.8.2 Register Descriptions ................................................................................ 15-39

15.8.3 Pin Configurations .................................................................................... 15-40

15.9 Port 7 .......................................................................................................................... 15-41

15.9.1 Block Diagram .......................................................................................... 15-41

15.9.2 Register Descriptions ................................................................................ 15-42

vi

Page 15

15.9.3 Pin Configurations .................................................................................... 15-44

15.10 Port 8 .......................................................................................................................... 15-45

15.10.1 Block Diagram .......................................................................................... 15-45

15.10.2 Register Descriptions ................................................................................ 15-46

15.10.3 Pin Configurations .................................................................................... 15-47

15.11 Port 9 .......................................................................................................................... 15-48

15.11.1 Block Diagram .......................................................................................... 15-48

15.11.2 Register Descriptions ................................................................................ 15-50

15.11.3 Pin Configurations .................................................................................... 15-52

15.12 Port A ......................................................................................................................... 15-53

15.12.1 Block Diagram .......................................................................................... 15-53

15.12.2 Register Descriptions ................................................................................ 15-54

15.12.3 Pin Configurations .................................................................................... 15-56

15.13 Port B ......................................................................................................................... 15-57

15.13.1 Block Diagram .......................................................................................... 15-57

15.13.2 Register Descriptions ................................................................................ 15-58

15.13.3 Pin Configurations .................................................................................... 15-60

15.14 Port C ......................................................................................................................... 15-61

15.14.1 Block Diagram .......................................................................................... 15-61

15.14.2 Register Descriptions ................................................................................ 15-62

15.14.3 Pin Configurations .................................................................................... 15-63

15.15 Treatment of Unused Pins.......................................................................................... 15-64

16. Internal Flash Memory

16.1 Overview...................................................................................................................... 16-2

16.2 Features ........................................................................................................................ 16-2

16.3 Block Diagram ............................................................................................................. 16-2

16.4 Flash Memory Overwrite Mode and Settings .............................................................. 16-3

16.5 Flash Memory Mode.................................................................................................... 16-4

16.5.1 Description of External Pins ....................................................................... 16-4

16.5.2 Erasure Blocks ............................................................................................ 16-7

16.6 On-board Write Mode.................................................................................................. 16-8

17. Ordering Mask ROM

17.1 Overview...................................................................................................................... 17-2

17.2 Procedure for Ordering ROM ...................................................................................... 17-2

Appendix

A. Register Map List....................................................................................................... Appendix-2

B. Instruction Set ............................................................................................................ Appendix-5

C. Memory Connection Example ................................................................................. Appendix-11

D. Pins and Their Operating Statuses upon Reset ........................................................ Appendix-12

E. Package Outline ....................................................................................................... Appendix-14

vii

Page 16

List of Figures and Tables

List of Figures

1. General Specifications

Fig. 1-3-1 MN103001G Block Diagram .................................................................................... 1-4

Fig. 1-4-1 Pin Assignments Diagram ......................................................................................... 1-5

2. CPU

Fig. 2-2-1 CPU Core Block Diagram ......................................................................................... 2-3

Fig. 2-3-1 CPU Registers ........................................................................................................... 2-4

Fig. 2-3-2 Processor Status Word............................................................................................... 2-5

Fig. 2-4-1 Little Endian Format ............................................................................................... 2-11

Fig. 2-5-1 Overview of the Interrupt System ........................................................................... 2-14

Fig. 2-5-2 Interrupt Control Register (GnICR) ........................................................................ 2-15

Fig. 2-5-3 Interrupt Accept Group Register ............................................................................. 2-17

Fig. 2-5-4 Interrupt Vector Address Register........................................................................... 2-17

Fig. 2-5-5 Interrupt Sequence Flow ......................................................................................... 2-20

Fig. 2-5-6 Interrupt Sequence Flow ......................................................................................... 2-21

Fig. 2-5-7 Stack Frame Configuration ..................................................................................... 2-22

3. Extension Instruction Specifications

Fig. 3-1-1 Block Diagram of the Extension Function Unit ........................................................ 3-2

Fig. 3-2-1 Extension Block Register Set .................................................................................... 3-4

4. Memory Modes

Fig. 4-2-1 Memory Mode Pin Connection Diagram .................................................................. 4-3

Fig. 4-3-1 Memory Space in Extension Memory Mode ............................................................ 4-4

Fig. 4-3-2 Memory Space in Processor Mode............................................................................ 4-5

5. Operating Mode

Fig. 5-1-1 Operating Mode Transition Diagram ........................................................................ 5-2

6. Clock Generator

Fig. 6-3-1 Clock Generator ........................................................................................................ 6-2

7. Internal Memory

Fig. 7-3-1 Internal Memory Block Diagram (In Memory Extension Mode) ............................. 7-3

8. Bus Controller (BC)

Fig. 8-3-1 Bus Configuration Diagram ...................................................................................... 8-3

Fig. 8-4-1 Block Diagram for the Bus Controller ...................................................................... 8-4

viii

Page 17

Fig. 8-7-1 Address Format When Accessing External Memory .............................................. 8-26

Fig. 8-7-2 Space Partitioning....................................................................................................8-27

Fig. 8-12-1 Internal I/O Space Access ....................................................................................... 8-31

Fig. 8-13-1 Access Timing on a 16-bit Bus with Fixed Wait States,

in Synchronous Mode and in Address/Data Separate Mode

(MCLK = SYSCLK multiplied by 4)...................................................................... 8-33

Fig. 8-13-2 Access Timing on a 16-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 2).................. 8-34

Fig. 8-13-3 Access Timing on a 16-bit Bus with Fixed Wait States, in Synchronous

Mode and in Address/Data Separate Mode (MCLK = SYSCLK) .......................... 8-34

Fig. 8-13-4 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 4).................. 8-35

Fig. 8-13-5 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 2).................. 8-36

Fig. 8-13-6 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK) ........................................... 8-36

Fig. 8-13-7 Access Timing on a 16-bit Bus in Asynchronous Mode and in

Address/Data Separate Mode (MCLK = SYSCLK multiplied by 4) ...................... 8-37

Fig. 8-13-8 Access Timing on a 16-bit Bus in Asynchronous Mode and in

Address/Data Separate Mode (MCLK = SYSCLK multiplied by 2) ...................... 8-38

Fig. 8-13-9 Access Timing on a 16-bit Bus in Asynchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK) ........................................... 8-38

Fig. 8-13-10 Access Timing on a 8-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 4).................. 8-39

Fig. 8-13-11 Access Timing on a 8-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 2).................. 8-40

Fig. 8-13-12 Access Timing on a 8-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK) ........................................... 8-40

Fig. 8-13-13 Access Timing on a 8-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 4).................. 8-42

Fig. 8-13-14 Access Timing on a 8-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 2).................. 8-43

Fig. 8-13-15 Access Timing on a 8-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK) ........................................... 8-44

Fig. 8-13-16 Access Timing on a 8-bit Bus in Asynchronous Mode and

in Address/Data Separate Mode (MCLK = SYSCLK multiplied by 4).................. 8-45

Fig. 8-13-17 Access Timing on a 16-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)................ 8-46

Fig. 8-13-18 Access Timing on a 16-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 2)................ 8-47

Fig. 8-13-19 Access Timing on a 16-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK) ......................................... 8-47

Fig. 8-13-20 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)................ 8-49

ix

Page 18

Fig. 8-13-21 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 2)................ 8-49

Fig. 8-13-22 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK) ......................................... 8-50

Fig. 8-13-23 Access Timing on a 16-bit Bus in Asynchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)................ 8-51

Fig. 8-13-24 Access Timing on a 8-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)................ 8-53

Fig. 8-13-25 Access Timing on a 8-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 2)................ 8-54

Fig. 8-13-26 Access Timing on a 8-bit Bus with Fixed Wait States, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK) ......................................... 8-55

Fig. 8-13-27 Access Timing on a 8-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)................ 8-57

Fig. 8-13-28 Access Timing on a 8-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 2)................ 8-58

Fig. 8-13-29 Access Timing on a 8-bit Bus with Handshaking, in Synchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK) ......................................... 8-59

Fig. 8-13-30 Access Timing on a 8-bit Bus in Asynchronous Mode and

in Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)................ 8-61

Fig. 8-14-1 DRAM Access Timing Chart .................................................................................. 8-62

Fig. 8-14-2 Case Where the RAS Precharge Interval is at Its Minimum

(Example Where RP = 1 and ASR = 1)................................................................... 8-63

Fig. 8-14-3 Example of an 8-bit Data Write Using 2 WE Control (16-bit Bus Width) ............. 8-64

Fig. 8-14-4 Example of an 8-bit Data Write Using 2 CAS Control (16-bit Bus Width) ........... 8-64

Fig. 8-14-5 DRAM Page Mode Read/Write Timing.................................................................. 8-65

Fig. 8-14-6 Software Page Mode Read/Write Timing ............................................................... 8-67

Fig. 8-14-7 DRAM Refresh Operation....................................................................................... 8-69

Fig. 8-14-8 DRAM Refresh Timing ........................................................................................... 8-69

Fig. 8-15-1 Bus Arbitration Timing 1

(Bus Authority Release/Bus Authority Acquisition, nfr = 4).................................. 8-71

Fig. 8-15-2 Bus Arbitration Timing 2

(Bus Authority Release/Bus Authority Acquisition, nfr = 2).................................. 8-71

Fig. 8-15-3 Bus Arbitration Timing 3

(Bus Authority Release/Bus Authority Acquisition, nfr = 1).................................. 8-72

Fig. 8-15-4 Bus Arbitration Timing 4

(Refresh Request Generated While Bus Authority Has Been Released) ................ 8-72

9. Interrupt Controller

Fig. 9-3-1 System Diagram ........................................................................................................ 9-2

Fig. 9-4-1 Block Diagram 1 ....................................................................................................... 9-3

Fig. 9-4-2 Block Diagram 2 ....................................................................................................... 9-4

Fig. 9-4-3 Block Diagram 3 ....................................................................................................... 9-5

x

Page 19

10. 8-bit Timers

Fig. 10-3-1 8-bit Timer Block Diagram (Timers 0 to 3) ............................................................ 10-3

Fig. 10-3-2 8-bit Timer Block Diagram (Timers 4 to B) ........................................................... 10-4

Fig. 10-3-3 8-bit Timer Connection Diagram (Overall)............................................................. 10-5

Fig. 10-3-4 8-bit Timer Connection Diagram (Timer 0 to 3 block) ........................................... 10-6

Fig. 10-3-5 8-bit Timer Connection Diagram (Timer 4 to 7 block) ........................................... 10-7

Fig. 10-3-6 8-bit Timer Connection Diagram (Timer 8 to B block) .......................................... 10-8

Fig. 10-6-1 Interval Timer Operation ....................................................................................... 10-22

Fig. 10-6-2 Interval Timer Operation (When Clock Source = IOCLK) .................................. 10-22

Fig. 10-6-3 Interval Timer Operation (Using Prescaler) .......................................................... 10-23

Fig. 10-6-4 Event Counting Operation ..................................................................................... 10-25

Fig. 10-6-5 Cascaded Connection ............................................................................................ 10-26

Fig. 10-6-6 Operation of Timers 0 and 1 (1) ............................................................................ 10-29

Fig. 10-6-7 Operation of Timers 0 and 1 (2) ............................................................................ 10-30

Fig. 10-6-8 PWM Output (When Clock Source = IOCLK, and "L" Level Is

Output Upon Initialization) ................................................................................... 10-33

Fig. 10-6-9 PWM Output (When Using Prescaler, and "H" Level is

Output Upon Initialization) ................................................................................... 10-33

11. 16-bit Timers

Fig. 11-3-1 16-bit Timer Block Diagram (Timer 10)................................................................. 11-3

Fig. 11-3-2 16-bit Timer Block Diagram (Timers 11, 12 and 13) ............................................. 11-4

Fig. 11-3-3 16-bit Timer Connection Diagram .......................................................................... 11-5

Fig. 11-3-4 Timer 10 Compare/Capture Register Block Diagram ............................................. 11-6

Fig. 11-3-5 PWM Output Section Block Diagram ..................................................................... 11-6

Fig. 11-6-1 Compare Register Operation (When Clock Source = IOCLK)............................. 11-19

Fig. 11-6-2 Input Capture Operation (When "Rising Edge" is Selected)................................. 11-20

Fig. 11-6-3 Pin Output Waveform (1) ...................................................................................... 11-22

Fig. 11-6-4 Pin Output Waveform (2) ...................................................................................... 11-22

Fig. 11-6-5 Pin Output Waveform (3) ...................................................................................... 11-23

Fig. 11-6-6 Pin Output Waveform (4) ...................................................................................... 11-23

Fig. 11-6-7 Pin Output Waveform (5) ...................................................................................... 11-23

Fig. 11-6-8 Timer 10 Startup by an External Trigger (When "Rising Edge" is Selected) ....... 11-25

Fig. 11-6-9 One-shot Operation (When Clock Source = IOCLK) ........................................... 11-27

Fig. 11-6-10 One-shot Operation (When Using Prescaler)........................................................ 11-27

Fig. 11-6-11 Timer 10 Interval Timer Operation (1) ................................................................. 11-29

Fig. 11-6-12 Timer 10 Interval Timer Operation (2) ................................................................. 11-29

Fig. 11-6-13 Timer 10 Interval Timer Operation (When Clock Source = IOCLK)................... 11-30

Fig. 11-6-14 Timer 10 Interval Timer Operation (When Using Prescaler)................................ 11-30

Fig. 11-6-15 Event Count Operation (When "Rising Edge" is Selected)................................... 11-32

Fig. 11-7-1 Interval Timer Operation ....................................................................................... 11-34

Fig. 11-7-2 Interval Timer Operation (When Clock Source = IOCLK) .................................. 11-35

Fig. 11-7-3 Interval Timer Operation (When Using the Prescaler).......................................... 11-35

Fig. 11-7-4 Event Count Operation .......................................................................................... 11-37

xi

Page 20

12. Watchdog Timer

Fig. 12-3-1 Block Diagram ........................................................................................................ 12-3

Fig. 12-5-1 Operation Diagram 1: When Reset Is Released ...................................................... 12-7

Fig. 12-5-2 Operation Diagram 2: When Recovering from STOP Mode .................................. 12-8

Fig. 12-5-3 Operation Diagram 3: Watchdog Operation ........................................................... 12-9

13. Serial Interface

Fig. 13-1-1 Structure Diagram ................................................................................................... 13-2

Fig. 13-2-1 Block Diagram ........................................................................................................ 13-5

Fig. 13-2-2 Connections ........................................................................................................... 13-10

Fig. 13-2-3 Timing Chart (1).................................................................................................... 13-11

Fig. 13-2-4 Timing Chart (2).................................................................................................... 13-11

Fig. 13-2-5 Timing Chart (3).................................................................................................... 13-12

Fig. 13-2-6 Timing Chart (4).................................................................................................... 13-12

Fig. 13-2-7 Timing Chart (5).................................................................................................... 13-13

Fig. 13-2-8 Connections ........................................................................................................... 13-14

Fig. 13-2-9 Timing Chart (6).................................................................................................... 13-16

Fig. 13-2-10 Timing Chart (7).................................................................................................... 13-16

Fig. 13-2-11 Timing Chart (8).................................................................................................... 13-17

Fig. 13-2-12 Timing Chart (9).................................................................................................... 13-17

Fig. 13-2-13 Timing Chart (10).................................................................................................. 13-18

Fig. 13-2-14 Connections ........................................................................................................... 13-19

Fig. 13-2-15 Timing Chart (11).................................................................................................. 13-22

Fig. 13-2-16 Timing Chart (12).................................................................................................. 13-23

Fig. 13-3-1 Block Diagram ...................................................................................................... 13-25

Fig. 13-3-2 Connections ........................................................................................................... 13-32

Fig. 13-3-3 Timing Chart (13).................................................................................................. 13-33

Fig. 13-3-4 Timing Chart (14).................................................................................................. 13-33

Fig. 13-3-5 Timing Chart (15).................................................................................................. 13-34

Fig. 13-3-6 Timing Chart (16).................................................................................................. 13-34

Fig. 13-3-7 Timing Chart (17).................................................................................................. 13-35

Fig. 13-4-1 Block Diagram ...................................................................................................... 13-37

Fig. 13-4-2 Connections ........................................................................................................... 13-45

Fig. 13-4-3 Timing Chart (18).................................................................................................. 13-49

Fig. 13-4-4 Timing Chart (19).................................................................................................. 13-49

Fig. 13-4-5 Timing Chart (20).................................................................................................. 13-50

Fig. 13-4-6 Timing Chart (21).................................................................................................. 13-50

Fig. 13-4-7 Timing Chart (22).................................................................................................. 13-51

14. A/D Converter

Fig. 14-1-1 A/D Coverter Configuration Diagram..................................................................... 14-2

Fig. 14-3-1 The Block Diagram of A/D Converter .................................................................... 14-4

Fig. 14-5-1 External Trigger Input Conversion Example .......................................................... 14-7

xii

Page 21

Fig. 14-5-2 External Trigger Input Conversion Example

(for Channels 0 to 2, One Time Each)..................................................................... 14-8

Fig. 14-5-3 External Trigger Input Conversion Example .......................................................... 14-9

Fig. 14-5-4 External Trigger Input Conversion Example

(for Channels 0 to 2, Continuous Conversion)...................................................... 14-10

Fig. 14-5-5 Conversion Timing When Using Two Sampling Cycles ...................................... 14-11

Fig. 14-5-6 Conversion Timing When Using Four Sampling Cycles ...................................... 14-11

Fig. 14-5-7 Example of Conversion by Switching to

External Trigger Mode (Single Conversion)......................................................... 14-12

Fig. 14-5-8 Example of Conversion by Switching to

External Trigger Mode (Continuous Conversion)................................................. 14-12

15. I/O Ports

Fig. 15-2-1 Port 0 Block Diagram (P02) .................................................................................... 15-6

Fig. 15-2-2 Port 0 Block Diagram (P01, P00)............................................................................ 15-7

Fig. 15-3-1 Port 1 Block Diagram (P17 to P12)....................................................................... 15-10

Fig. 15-3-2 Port 1 Block Diagram (P11, and P10) ................................................................... 15-11

Fig. 15-4-1 Port 2 Block Diagram (P27 to P20)....................................................................... 15-15

Fig. 15-5-1 Port 3 Block Diagram (P30) .................................................................................. 15-19

Fig. 15-6-1 Port 4 Block Diagram (P45 and P43) .................................................................... 15-22

Fig. 15-6-2 Port 4 Block Diagram (P44) .................................................................................. 15-23

Fig. 15-6-3 Port 4 Block Diagram (P42, P40).......................................................................... 15-24

Fig. 15-6-4 Port 4 Block Diagram (P41) .................................................................................. 15-24

Fig. 15-7-1 Port 5 Block Diagram (P55) .................................................................................. 15-29

Fig. 15-7-2 Port 5 Block Diagram (P54) .................................................................................. 15-30

Fig. 15-7-3 Port 5 Block Diagram (P53) .................................................................................. 15-31

Fig. 15-7-4 Port 5 Block Diagram (P52, P50).......................................................................... 15-32

Fig. 15-7-5 Port 5 Block Diagram (P51) .................................................................................. 15-33

Fig. 15-8-1 Port 6 Block Diagram (P63 to P60)....................................................................... 15-38

Fig. 15-9-1 Port 7 Block Diagram (P73) .................................................................................. 15-41

Fig. 15-9-2 Port 7 Block Diagram (P72 to P70)....................................................................... 15-41

Fig. 15-10-1 Port 8 Block Diagram (P83 to P80)....................................................................... 15-45

Fig. 15-11-1 Port 9 Block Diagram (P97).................................................................................. 15-48

Fig. 15-11-2 Port 9 Block Diagram (P96).................................................................................. 15-48

Fig. 15-11-3 Port 9 Block Diagram (P95, P91, P90) ................................................................. 15-49

Fig. 15-11-4 Port 9 Block Diagram (P94, P93, P92) ................................................................. 15-49

Fig. 15-12-1 Port A Block Diagram (PA7 to PA0).................................................................... 15-53

Fig 15-13-1 Port B Block Diagram (PB7 to PB0)..................................................................... 15-57

Fig 15-14-1 Port C Block Diagram (PC3 to PC0)..................................................................... 15-61

16. Internal Flash Memory

Fig. 16-3-1 Flash Memory Block Diagram ................................................................................ 16-2

Fig. 16-5-1 MN1030F01K Pin Assignments in Flash Memory Mode....................................... 16-4

Fig. 16-5-2 Flash Memory Erasure Blocks ................................................................................ 16-7

xiii

Page 22

17. Ordering Mask ROM

Fig. 17-2-1 ROM Ordering Method 1 ........................................................................................ 17-2

Fig. 17-2-2 ROM Ordering Method 2 ........................................................................................ 17-3

Appendix

Fig. C-1 Memory Connection Example................................................................... Appendix-11

Fig. E-1 Package Outline......................................................................................... Appendix-14

xiv

Page 23

List of Tables

1. General Specifications

Table 1-4-1 Pin Assignments ........................................................................................................ 1-6

Table 1-4-2 Pin Function Table (1/2)............................................................................................ 1-7

Table 1-4-2 Pin Function Table (2/2)............................................................................................ 1-8

2. CPU

Table 2-3-1 List of Control Registers ........................................................................................... 2-7

Table 2-4-1 Addressing Mode Types.......................................................................................... 2-10

Table 2-4-2 Data Types............................................................................................................... 2-11

Table 2-4-3 Instruction Types (All 46 types and extension instructions) ................................... 2-12

Table 2-5-1 Relationship between Mask Levels and Interrupt Levels that Can Be Accepted.... 2-15

3. Extension Instruction Specifications

Table 3-2-1 Notes on Instruction Description............................................................................. 3-31

4. Memory Modes

Table 4-2-1 Memory Mode Setting............................................................................................... 4-3

5. Operating Mode

Table 5-2-1 Status of Internal Registers Immediately after a Reset ............................................. 5-3

6. Clock Generator

Table 6-4-1 CKSEL Mode (PLL used/PLL not used) .................................................................. 6-3

Table 6-4-2 Relationship between the Oscillation Mode and the SYSCLK, MCLK, and

IOCLK Frequencies .................................................................................................. 6-4

Table 6-4-3 Relationship between the Input Frequency and the SYSCLK, MCLK

and IOCLK Frequencies When Reset is Released .................................................... 6-4

8. Bus Controller (BC)

Table 8-3-1 Characteristics of Each Bus....................................................................................... 8-3

Table 8-5-1 External Pin Functions Relating to the Bus Controller ............................................. 8-5

Table 8-5-2 Operating Status of Pins Concerning BC .................................................................. 8-6

Table 8-6-1 List of Bus Control Registers .................................................................................... 8-7

Table 8-7-1 Features of Each Block............................................................................................ 8-26

Table 8-8-1 Frequency Ratios of BC Operation Clocks ............................................................. 8-28

Table 8-9-1 Mode Settings by the BC External Pins .................................................................. 8-28

Table 8-10-1 Relationship between the Clock Frequency and the Number of Cycles

(CPU Cycles) Required for Access ......................................................................... 8-29

Table 8-13-1 External Bus Transaction ........................................................................................ 8-32

9. Interrupt Controller

Table 9-5-1 Register List .............................................................................................................. 9-6

xv

Page 24

10. 8-bit Timers

Table 10-4-1 List of 8-bit Timer Functions .................................................................................. 10-9

Table 10-5-1 List of 8-bit Timer Registers (1/2) ........................................................................ 10-10

Table 10-5-1 List of 8-bit Timer Registers (2/2) ........................................................................ 10-11

Table 10-5-2 PWM Output Waves ............................................................................................. 10-14

Table 10-5-3 8-bit Timer Clock Sources .................................................................................... 10-15

11. 16-bit Timers

Table 11-4-1 List of 16-bit Timer Functions ................................................................................ 11-7

Table 11-5-1 List of 16-bit Timer Registers ................................................................................. 11-8

Table 11-5-2 List of 16-bit Timer Clock Source ........................................................................ 11-11

12. Watchdog Timer

Table 12-4-1 List of Watchdog Timer Registers .......................................................................... 12-4

13. Serial Interface

Table 13-2-1 List of General-Purpose Serial Interface Registers ................................................. 13-6

Table 13-2-2 Bit Rates (1) (When IOCLK = 15 MHz)............................................................... 13-15

Table 13-2-3 Bit Rates (2) (When IOCLK = 12 MHz)............................................................... 13-15

Table 13-2-4 Bit Rates (3) (When IOCLK = 8 MHz)................................................................. 13-15

Table 13-3-1 List of Clock Synchronous Serial Interface Registers........................................... 13-26

Table 13-4-1 List of UART Serial Interface Registers ............................................................... 13-38

Table 13-4-2 Bit Rates (1) (When IOCLK = 15 MHz)............................................................... 13-46

Table 13-4-3 Bit Rates (2) (When IOCLK = 12 MHz)............................................................... 13-47

Table 13-4-4 Bit Rates (3) (When IOCLK = 8 MHz)................................................................. 13-47

14. A/D Converter

Table 14-4-1 A/D Register List..................................................................................................... 14-5

15. I/O Ports

Table 15-1-1 List of Registers (1/2).............................................................................................. 15-4

Table 15-1-1 List of Registers (2/2).............................................................................................. 15-5

Table 15-2-1 Port 0 Configuration................................................................................................ 15-9

Table 15-3-1 Port 1 Configuration.............................................................................................. 15-14

Table 15-4-1 Port 2 Configuration.............................................................................................. 15-18

Table 15-5-1 Port 3 Configuration.............................................................................................. 15-21

Table 15-6-1 Port 4 Configuration.............................................................................................. 15-28

Table 15-7-1 Port 5 Configuration.............................................................................................. 15-37

Table 15-8-1 Port 6 Configuration.............................................................................................. 15-40

Table 15-9-1 Port 7 Configuration.............................................................................................. 15-44

Table 15-10-1Port 8 Configuration.............................................................................................. 15-47

Table 15-11-1Port 9 Configuration.............................................................................................. 15-52

Table 15-12-1Port A Configuration ............................................................................................. 15-56

xvi

Page 25

Table 15-13-1Port B Configuration ............................................................................................. 15-60

Table 15-14-1Port C Configuration ............................................................................................. 15-63

Table 15-15-1Treatment of Unused Pins ..................................................................................... 15-64

16. Internal Flash Memory

Table 16-4-1 Mode Settings through the External Pins ................................................................ 16-3

Table 16-5-1 MN1030 F01K Pin Assignments ............................................................................ 16-5

Table 16-5-2 Pin Functions........................................................................................................... 16-6

Table 16-6-1 Flash Memory Register List ..................................................................................... 16-8

xvii

Page 26

xviii

Page 27

0

1. General Specifications

1

Page 28

General Specifications

1.1 Overview

The MN1030 Series is a 32-bit microcontroller that maintains the software assets of Matsushita Electronics' 16-bit

MN102 Series of microcontrollers by offering ease of use and excellent cost-performance with a simple, highperformance architecture.

Built around a compact 32-bit CPU core with a basic instruction word length of one byte, the MN103001G (mask

ROM version) includes ROM, RAM, a bus control circuit, interrupt control circuit, timers, a serial interface, A/D

converter, and input/output ports in a 100-pin QFP. The MN1030F01K (flash memory version) is equipped with

flash memory instead of mask ROM, has the same on-chip peripheral functions as the MN103001G, and has the

same package and pin specifications. This microcontroller is ideal for multimedia devices, which must be able to

process large volumes of data (for audio, stills, video, etc.), as well as for real-time control equipment that requires

fast and precise control. When supplied with power supply voltage of 3.3 V, the MN103001G operates at

60 MHz and achieves performance of 60 MIPS.

1.2 Features

Low voltage, high-speed processing, low power consumption

■ Minimum instruction execution time:

16.7 ns (during 3.3 V internal 60 MHz operation *MN103001G)

25 ns (during 3.3 V internal 40 MHz operation *MN1030F01K)

■ Power consumption (TYP.):

300 mW (during 3.3 V internal 60 MHz operation *MN103001G)

270 mW (during 3.3 V internal 40 MHz operation *MN1030F01K)

Compact and high-performance CPU core

■ Simple and highly efficient instruction set

(Number of basic instructions: 46; number of extension instructions: 24; number of addressing modes: 6)

■ Excellent coding efficiency with instructions that have a basic word length of one byte

■ Load/store architecture with 5-stage pipeline organization provides fast instruction execution

■ High-speed branch processing

■ Supports linear address space of up to 4 GB

(External extension 8 Mbytes x 4 = 32 Mbytes)

Extension operation functions

■ Multiply-and-accumulate operation instructions (32 bits x 32 bits + 64 bits = 64 bits; throughput: 2

clocks)

■ Saturation operation instructions

■ Bit search instructions

■ Swap instructions

Large on-chip memory

■ 128 Kbytes of on-chip ROM/256 Kbytes of flash memory

■ 8 Kbytes of on-chip RAM (for data storage)

Flexible clock control

■ Self-excited/externally excited oscillation

• Maximum 60 MHz internal operation when a 15-MHz oscillator is connected or a 15-MHz clock

is input (in the case of the MN103001G)

• Can switch between using PLL (programmable: multiply by four, multiply by two, multiply by

one)/not using PLL (divide by two)

■ Low power consumption mode

• HALT, STOP, SLEEP mode

1-2

Page 29

High-speed/high-performance bus interface

■ Can select either separate address/data buses or multiplex address/data bus

• Address: 24 bits/Data: 8/16 bits

■ External memory space can be partitioned into four blocks

• Chip select signal output for each block

• Blocks 2 to 3 can be switched between fixed wait insertion or handshaking

• Blocks 0 to 3 can be switched between synchronous mode and asynchronous mode

• Blocks 1 and 2 can be used as DRAM space

■ DRAM control circuit on chip

• Address multiplexing function

• Programmable RAS/CAS timing setting

• Refresh control

- CAS-before-RAS refresh support

- Programmable refresh interval

• High-speed page mode support

■ One store buffer on chip

• Avoids time penalty when performing a store operation in an internal peripheral or an external

device

Input/output interface

■ Supports 3.3 V, CMOS-level input/output interface

Wide variety of internal peripheral functions

■ Interrupts

• 38 sources

-

External interrupts: 9 sources (IRQn (n=7 to 0) x 8, and NMIRQ x 1)

- Internal interrupts: 29 sources (timers: 18; Serial I/F: 8; WDT: 1; A/D: 1; system error: 1)

■ Timers

• Twelve 8-bit timers (all are down-counters)

- Format: Reload timer

- Cascaded connection possible (permits use as 16- to 32-bit timers)

- Timer output possible (duty ratio; 1:1,12 outputs)

- PWM output possible (8 outputs)

- Internal clock source or external clock source can be selected

- Serial interface clock generation

- A/D converter start timing generation

• One 16-bit timer (up-counter)

- Internal clock source or external clock source can be selected

- Input capture function (rising edge, falling edge, or both edges can be selected)

- PWM generation functions

- 2 compare and capture registers

• Three 16-bit timers (down-counter)

- Format: reload timer

- Internal clock source or external clock source can be selected

• One watchdog timer

■ Serial interface

• UART/synchronous system/I2C (multipurpose) x 1 channel

• UART-serial interface x 1 channel (maximum bit rate: 230.4 kbit/s)

• Synchronous x 2 channels

■ A/D converter

• 10 bits: 4 inputs

- Automatic scanning possible (0 to 3 channels can be set)

General Specifications

_____________

1-3

Page 30

General Specifications

■ Input ports:

• 4 (all multipurpose)

■ Output ports:

• 15 (all multipurpose)

■ Input/output ports:

• 53 (all multipurpose)

Flash microcontroller specifications

■ Performance identical to that of a mask ROM product guaranteed

■ Overwriting while on board possible through serial communications

■ Batch/block erase possible

Block units 8 KB (multiple blocks can be selected simultaneously)

Package

• LQFP100-P-1414

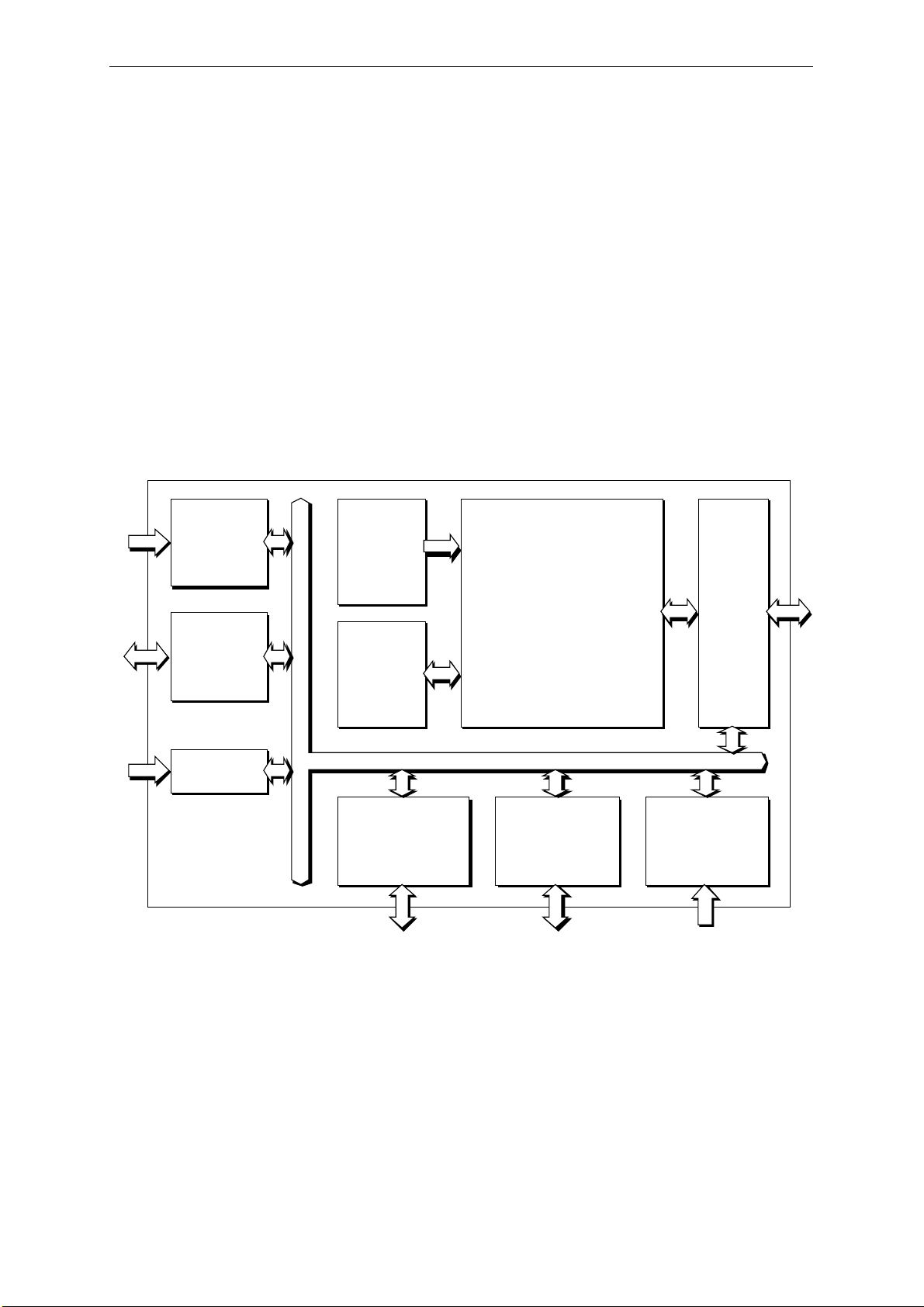

1.3 Block Diagram

A/D

10-bit

4 inputs

SIF

UART x 1

multipurpose x 1

synchronous system x 2

Clock and

system controller

ROM

128 KB

(flash memory

256 KB)

32-bit

CPU core

Data

RAM

8 KB

I/O ports

72 pins

(all multipurpose)

Fig. 1-3-1 MN103001G Block Diagram

Timers

16-bit x 4

8-bit x 12

WDT x 1

Bus

controller

includes

DRAM

controller

Interrupt

controller

38 sources

* The MN1030F01K (flash version) is equipped with 256 KB of flash memory instead of 128 KB of ROM.

1-4

Page 31

1.4 Pin Description

1.4.1 Pin Assignments

The pin assignments are shown in Fig. 1-4-1 and Table 1-4-1.

P55/SBO3/TM5IO/TM13IO

P54/SBI3/TM4IO/TM12IO

P53/SBT3/TM3IO/TM11IO

P52/SBO2/TM2IO

P51/SBI2/TM1IO

P50/SBT2/TM0IO

P45/SBO1/DWE

VDD

P44/SBI1/DCAS1

P43/SBT1/DCAS0

VSS

P42/SBO0

P41/SBI0

P40/SBT0

62

63

64

65

66

67

68

69

70

71

72

73

74

75

P30/BG

P27/D15

P26/D14

VDD

P25/D13

P24/D12

P23/D11

P22/D10

P21/D9

VSS

VDD2(VPP)*

P20/D8

P17/D7

P16/D6

P15/D5

P14/D4

VDD

P13/D3

P12/D2

P11/RWSEL/D1

P10/AS/D0

P02/CAS/A22

VSS

P01/A21

P00/A20

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

TOP VIEW

100-Pin QFP

9

8

7

6

5

4

3

2

1

10

11

12

13

14

P62/IRQ2/TM10IOA

P61/IRQ1/TM7IO

P60/IRQ0/TM6IO

VSS

NMIRQ

57

58

59

60

61

19

18

17

16

15

General Specifications

P73/A23/CS3

P72/RAS2/CS2

P71/RAS1/CS1

VDD

P70/CS0

P63/IRQ3/ADTRG/TM10IOB

51

52

53

54

55

56

20

21

22

23

24

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

AVDD

VREFH

P80/AN0/IRQ4

P81/AN1/IRQ5

P82/AN2/IRQ6

P83/AN3/IRQ7

AVSS

EXMOD0/P90

EXMOD1/P91

VDD

P92/RE

P93/WE0

P94/WE1

P95/DK

P96/BR

VSS

SYSCLK/P97

VDD

OSCI

OSCO

RST

MMOD0

MMOD1

PVDD

PVSS

VDD

PC1/A17

PC2/A18

PC3/A19

VSS

PC0/A16

PB4/ADM12/A12

PB5/ADM13/A13

PB6/ADM14/A14

PB7/ADM15/A15

VDD

PB0/ADM8/A8

PB1/ADM9/A9

PB2/ADM10/A10

PB3/ADM11/A11

PA6/ADM6/A6

PA7/ADM7/A7

VSS

PA1/ADM1/A1

PA2/ADM2/A2

PA3/ADM3/A3

PA4/ADM4/A4

PA5/ADM5/A5

CKSEL

PA0/ADM0/A0

Fig. 1-4-1 Pin Assignments Diagram

* "VDD2" in the case of the MN103001G, "VPP" in the case of the MN1030F01K.

1-5

Page 32

General Specifications

Table 1-4-1 Pin Assignments

Pin

Pin Name

No.

1 PC3/A19 26 PVSS 51 P73/A23/CS3 76 P30/BG

2 PC2/A18 27 PVDD 52 P72/RAS2/CS2 77 P27/D15

3 VDD 28 MMOD1 53 P71/RAS1/CS1 78 P26/D14

4 PC1/A17 29 MMOD0 54 VDD 79 VDD

5 PC0/A16 30 RST 55 P70/CS0 80 P25/D13

6 PB7/ADM15/A15 31 OSCO 56 P63/IRQ3/ADTRG/TM10IOB 81 P24/D12

7 PB6/ADM14/A14 32 OSCI 57 P62/IRQ2/TM10IOA 82 P23/D11

8 PB5/ADM13/A13 33 VDD 58 P61/IRQ1/TM7IO 83 P22/D10

9 VSS 34 SYSCLK/P97 59 P60/IRQ0/TM6IO 84 P21/D9

10 PB4/ADM12/A12 35 VSS 60 VSS 85 VSS

11 PB3/ADM11/A11 36 P96/BR 61 NMIRQ 86 VDD2(VPP) *

12 PB2/ADM10/A10 37 P95/DK 62 P55/SBO3/TM5IO/TM13IO 87 P20/D8

13 PB1/ADM9/A9 38 P94/WE1 63 P54/SBI3/TM4IO/TM12IO 88 P17/D7

14 PB0/ADM8/A8 39 P93/WE0 64 P53/SBT3/TM3IO/TM11IO 89 P16/D6

15 VDD 40 P92/RE 65 P52/SBO2/TM2IO 90 P15/D5

16 PA7/ADM7/A7 41 VDD 66 P51/SBI2/TM1IO 91 P14/D4

17 PA6/ADM6/A6 42 EXMOD1/P91 67 P50/SBT2/TM0IO 92 VDD

18 PA5/ADM5/A5 43 EXMOD0/P90 68 P45/SBO1/DWE 93 P13/D3

19 PA4/ADM4/A4 44 AVSS 69 VDD 94 P12/D2

20 PA3/ADM3/A3 45 P83/AN3/IRQ7 70 P44/SBI1/DCAS1 95 P11/RWSEL/D1

21 VSS 46 P82/AN2/IRQ6 71 P43/SBT1/DCAS0 96 P10/AS/D0

22 PA2/ADM2/A2 47 P81/AN1/IRQ5 72 VSS 97 P02/CAS/A22

23 PA1/ADM1/A1 48 P80/AN0/IRQ4 73 P42/SBO0 98 VSS

24 PA0/ADM0/A0 49 VREFH 74 P41/SBI0 99 P01/A21

25 CKSEL 50 AVDD 75 P40/SBT0 100 P00/A20

Pin

No.

Pin Name

Pin

No.

Pin Name

Pin

No.

Pin Name

• Pins for which two or more names are shown are multipurpose pins.

* "VDD2" in the case of the MN103001G, "VPP" in the case of the MN1030F01K.

1-6

Page 33

1.4.2 Pin Functions

Table 1-4-2 shows the function of each pin of this microcontroller.

Table 1-4-2 Pin Function Table (1/2)

General Specifications

Category Pin name

Power supply VDD 8 Digital system power supply (+3.3 V)

VSS 7 Digital system GND

VDD2(VPP) 1 “VDD2” in the case of the MN103001G, “VPP” in the

Clock OSCI I 1 Oscillator input

OSCO O 1 Oscillator output

SYSCLK O 1 System clock output (multipurpose)

CKSEL I 1 Switch for using/not using PLL

PVDD 1 PLL power supply (+3.3 V)

PVSS 1 PLL GND

Address bus A23 to 0 O 24 Address lines 23 to 0 (multipurpose, A23 also serves as

Data bus D15 to 0 I/O 16 Data lines 15 to 0 (multipurpose)

Address/ ADM15 to 0 I/O (16) Address/Data lines 15 to 0 (A15 to 0 multipurpose)

Data bus

Bus control MMOD1 to 0 I 2 Mode setting signals

signals EXMOD1 to 0 I 2 Extension mode setting (multipurpose)

RE O 1 Memory read signal (multipurpose)