Page 1

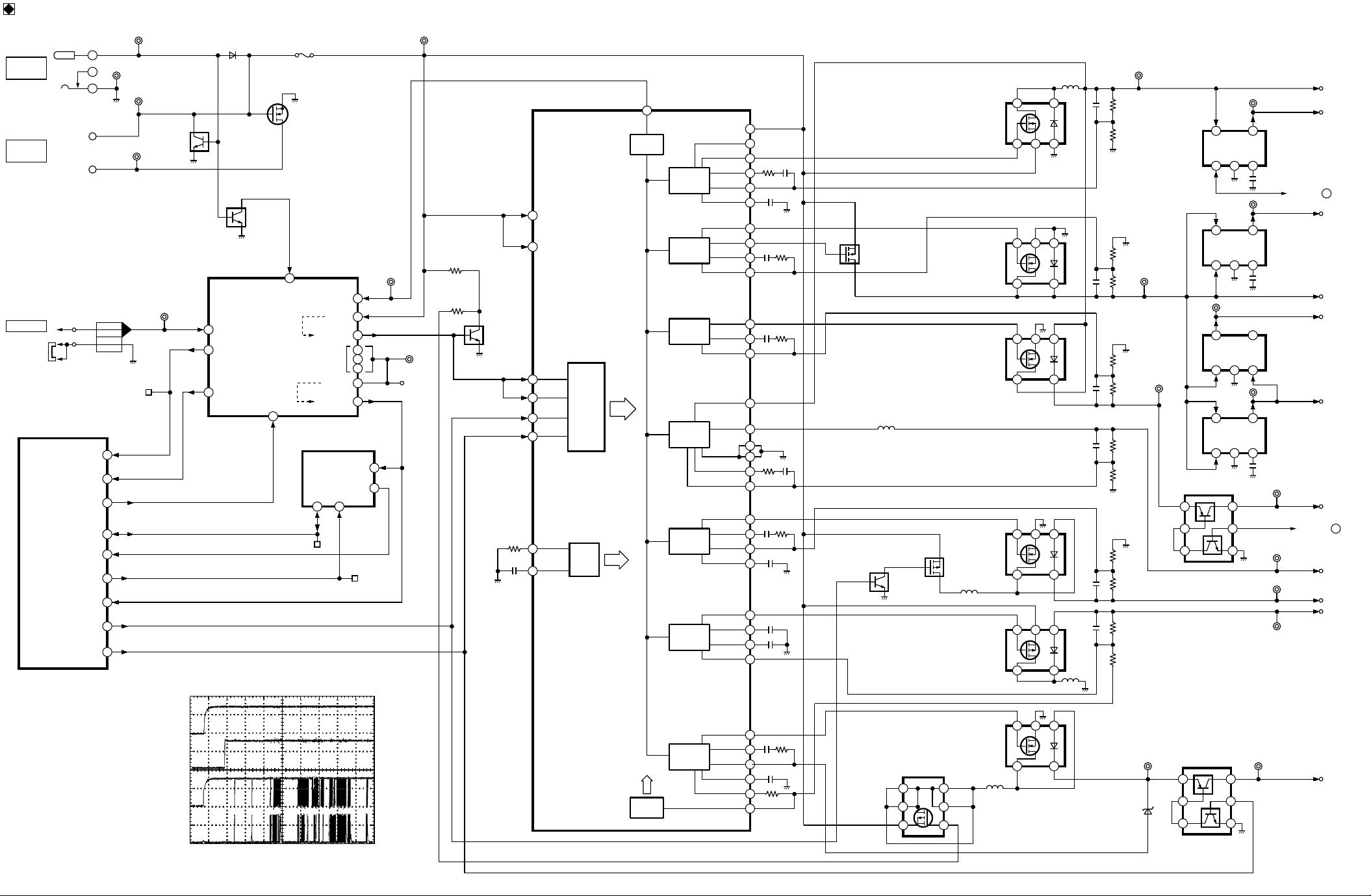

POWER BLOCK DIAGRAM

CL2004

JK2004

BAT+

BAT-

ON

OFF

SW UNREG

POWER ON H

CPUD16

CPUWE2B

RSTB

CCD POWER

LCD BLT

2

4

3

CL2005

FP9007

13

FP9007

11

223

27

196

140

144

145

191

193

244

CL2013

CL2014

DC

JACK

BATTERY

POWER SW

IC6001

(VENUS2)

POWER SW ON

RL9102

QR2003

CL9010

IC9101

(SYSTEM IC)

36

POWERSWON(L)

44

POWERSWON(H)

19

SW UNREG

G

QR2002

POWERON

34

F2001

S

Q2001

D

20

NACADP

IC6002

(FLASH ROM/16Mbit)

RL6015

CL1012

37

SCP

24

UNREG

23

POWERSW

5

VDD

18

46

32

RESETIN D2.9V

33

RESETOUT

12

/RESET

11

/WE

/OE

DQ0

28

29

RL6017CPUREB

CL1010

CL1013

QR1001

IC1001

(7CH SW REGULATORIC)

21

CC

V

46

PVCC

STB1

11

STB234

12

13

14

23

24

STB56

STB7

RT

CT

ON/OFF

LOGIC

OSC

SCP

SCP

CL1003

ToIC6001

ToIC6001

5.3V

LCD 5V

239

SD 3.0V

3.3V

A3.1V

D2.9V

LCD8.5V

238

D1.2V

CCD12.0V

CCD-6.0V

CL1005

5

IN OUT

CNT

GND

1

CL1017

5

IN OUT

CNT

GND

1

CL1001

5

OUT NC

IN

GND

1

2

CL1010

5

IN OUT

CNT

GND

1

2

1

CNT

4

3NP2

4

3NP2

4

3

4

3NP2

IC1002

(REGULATOR)

IC1005

(REGULATOR)

IC1003

(REGULATOR)

IC1004

(REGULATOR)

CL1014

CL1002

CL1007

CL1008

25

4

VBAT

OUT1B

5

OUT1

48

FB1

CH1

(Pch)

CH2

(Pch)

CH3

(Nch)

CH4

(H&L)

CH5

(Pch)

INV1

SUB2

MAIN2

INV2

OUT3

INV3

DRAIN4H

DRAIN4L

PGND4

INV4

OUT5

INV5

DTC5

SS1

FB2

FB3

FB4

FB5

18

19

17

43

44

32

33

47

27

26

9

8

6

7

16

15

41

35

34

38

G

S

Q1003

(MOS-FET:Pch)

D

Q1006

(MOS-FET:Pch)

QR1002

OUT6

40

FB6

CH6

(Pch)

DTC6

NON6

36

39

37

G

Q1001

(MOS-FET:Pch)

Q1004

(MOS-FET:Nch)

Q1002

(MOS-FET:Nch)

Q1007

S

(MOS-FET:Nch)

D

Q1008

(MOS-FET:Pch)

G

G

G

G

G

D

S

1 2 3

1 2 3

S

D

1 2 3

S

D

1 2 3

S

D

1 2 3

S

D

45

45

45

CL1004

CL1006

QR1003

4 3

5

6

45

45

CL1010

(D2.9V)

IC6001-191

(RSTB)

RL6017

(CPUREB)

RL6015

(CPUD16)

2.0V 10msec./DIV

VREF

CH7

(Nch)

OUT7

FB7

INV7

DTC7

NON7

VREF

45

28

29

3

30

20

Q1009

(MOS-FET:Pch)

6

5

Q1005

(MOS-FET:Nch)

1

2

34

1 2 3

S

G

D

45

QR1004

4 3

5

6

CL1005CL1011

BL 12V

2

1

DMC-FZ30 POWER BLOCK DIAGRAM

Loading...

Loading...