MJD44H11 (NPN)

MJD45H11 (PNP)

Preferred Device

Complementary Power

Transistors

DPAK For Surface Mount Applications

Designed for general purpose power and switching such as output or

driver stages in applications such as switching regulators, converters,

and power amplifiers.

Features

•Lead Formed for Surface Mount Application in Plastic Sleeves

(No Suffix)

•Straight Lead Version in Plastic Sleeves (“-1” Suffix)

•Electrically Similar to Popular D44H/D45H Series

•Low Collector Emitter Saturation Voltage -

V

•Fast Switching Speeds

•Complementary Pairs Simplifies Designs

•Epoxy Meets UL 94 V-0 @ 0.125 in

•ESD Ratings: Human Body Model, 3B u 8000 V

•Pb-Free Packages are Available

= 1.0 Volt Max @ 8.0 Amperes

CE(sat)

Machine Model, C u 400 V

http://onsemi.com

SILICON

POWER TRANSISTORS

8 AMPERES

80 VOLTS, 20 WATTS

MARKING

DIAGRAMS

4

2

1

3

DPAK

CASE 369C

STYLE 1

4

YWW

J4

xH11G

MAXIMUM RATINGS

Rating Symbol Max Unit

Collector-Emitter Voltage V

Emitter-Base Voltage V

Collector Current - Continuous

Total Power Dissipation

@ T

= 25°C

C

Derate above 25°C

Total Power Dissipation (Note 1)

@ T

= 25°C

A

Derate above 25°C

Operating and Storage Junction

Temperature Range

- Peak

TJ, T

CEO

EB

I

C

P

D

P

D

stg

80 Vdc

5 Vdc

8

16

20

0.16

1.75

0.014

-55 to +150 °C

Adc

W

W/°C

W

W/°C

THERMAL CHARACTERISTICS

Characteristic Symbol Max Unit

Thermal Resistance, Junction-to-Case

Thermal Resistance, Junction-to-Ambient

(Note 1)

Lead Temperature for Soldering T

Stresses exceeding Maximum Ratings may damage the device. Maximum

Ratings are stress ratings only. Functional operation above the Recommended

Operating Conditions is not implied. Extended exposure to stresses above the

Recommended Operating Conditions may affect device reliability.

1. These ratings are applicable when surface mounted on the minimum pad

sizes recommended.

R

q

JC

R

q

JA

L

6.25 °C/W

71.4 °C/W

260 °C

YWW

J4

1

2

3

Y = Year

WW = Work Week

J4xH11 = Device Code

G = Pb-Free Package

DPAK-3

CASE 369D

STYLE 1

x = 4 or 5

xH11G

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 6 of this data sheet.

Preferred devices are recommended choices for future use

and best overall value.

© Semiconductor Components Industries, LLC, 2008

January, 2008 - Rev. 8

1 Publication Order Number:

MJD44H11/D

MJD44H11 (NPN) MJD45H11 (PNP)

ELECTRICAL CHARACTERISTICS (T

= 25_C unless otherwise noted)

C

Characteristic

OFF CHARACTERISTICS

Collector-Emitter Sustaining Voltage

= 30 mA, IB = 0)

(I

C

Collector Cutoff Current

(V

= Rated V

CE

CEO

, VBE = 0)

Emitter Cutoff Current

(V

= 5 Vdc)

EB

ON CHARACTERISTICS

Collector-Emitter Saturation Voltage

= 8 Adc, IB = 0.4 Adc)

(I

C

Base-Emitter Saturation Voltage

(I

= 8 Adc, IB = 0.8 Adc)

C

DC Current Gain

(V

= 1 Vdc, IC = 2 Adc)

CE

DC Current Gain

(V

= 1 Vdc, IC = 4 Adc)

CE

DYNAMIC CHARACTERISTICS

Collector Capacitance

(V

CB

= 10 Vdc, f

= 1 MHz) MJD44H11

test

Gain Bandwidth Product

(I

= 0.5 Adc, VCE = 10 Vdc, f = 20 MHz) MJD44H11

C

SWITCHING TIMES

MJD45H11

MJD45H11

Symbol Min Typ Max Unit

V

CEO(sus)

I

CES

I

EBO

V

CE(sat)

V

BE(sat)

h

FE

80 Vdc

1.0

1.0

1 Vdc

1.5 Vdc

60 -

40

C

cb

45

130

f

T

MHz

85

90

mA

mA

pF

Delay and Rise Times

(I

= 5 Adc, IB1 = 0.5 Adc) MJD44H11

C

Storage Time

(I

= 5 Adc, IB1 = IB2 = 0.5 Adc) MJD44H11

C

Fall Time

(I

= 5 Adc, IB1 = IB2 = 0.5 Adc MJD44H11

C

MJD45H11

MJD45H11

MJD45H11

td + t

t

s

t

r

ns

300

135

ns

500

500

f

ns

140

100

http://onsemi.com

2

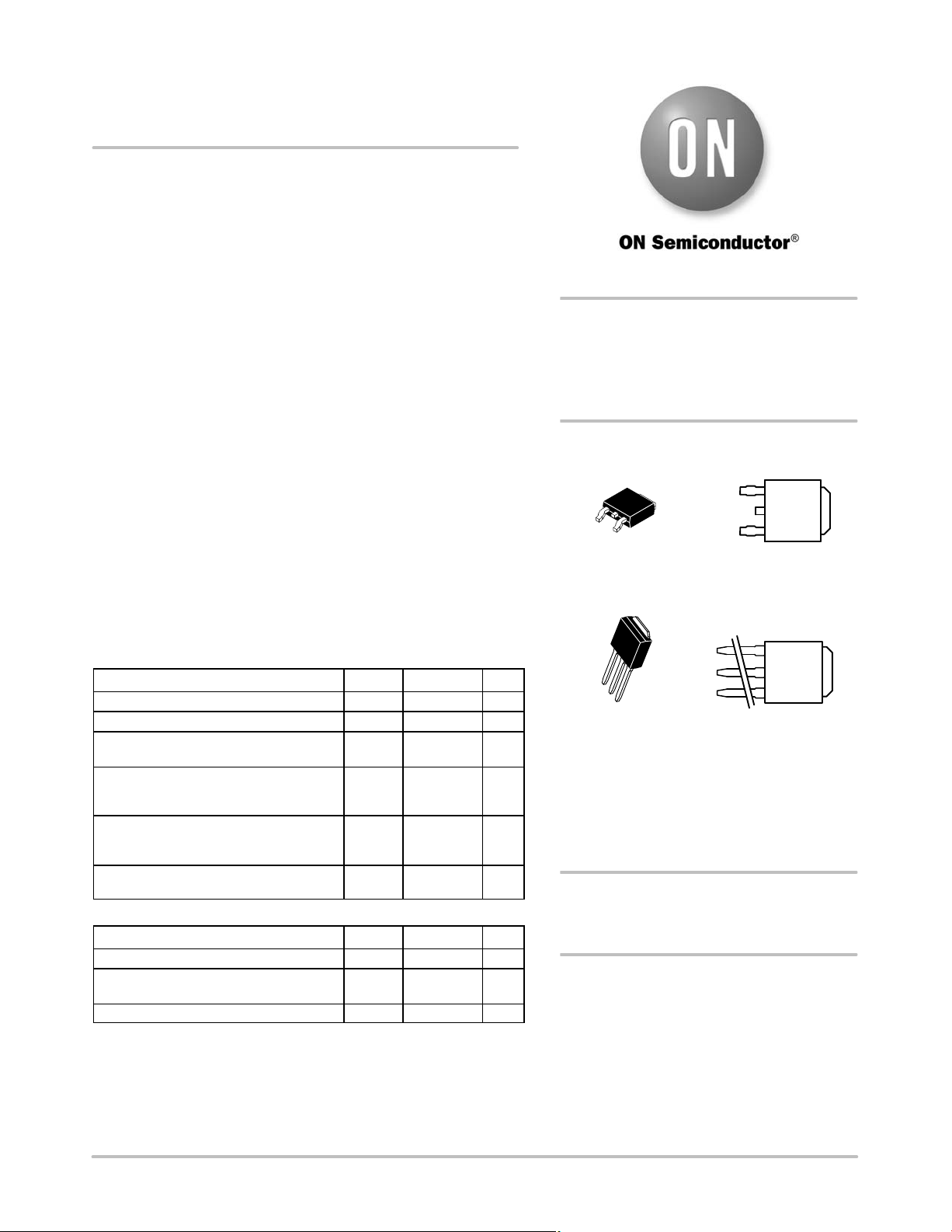

1

0.7

D = 0.5

0.5

0.3

0.2

0.1

0.05

0.07

0.02

0.05

0.03

RESISTANCE (NORMALIZED)

SINGLE PULSE

0.02

r(t), EFFECTIVE TRANSIENT THERMAL

0.01

0.01

MJD44H11 (NPN) MJD45H11 (PNP)

0.2

P

R

= r(t) R

q

0.1

0.01

0.02 0.03 0.05 0.1 0.2 0.3 0.5 1 2 3 5 10 20 30 50 100 200 300 500

JC(t)

R

q

JC

D CURVES APPLY FOR POWER

PULSE TRAIN SHOWN

READ TIME AT t

T

J(pk)

t, TIME (ms)

q

- TC = P

JC

1

(pk) qJC(t)

= 6.25°C/W MAX

Figure 1. Thermal Response

(pk)

t

1

t

2

DUTY CYCLE, D = t1/t

2

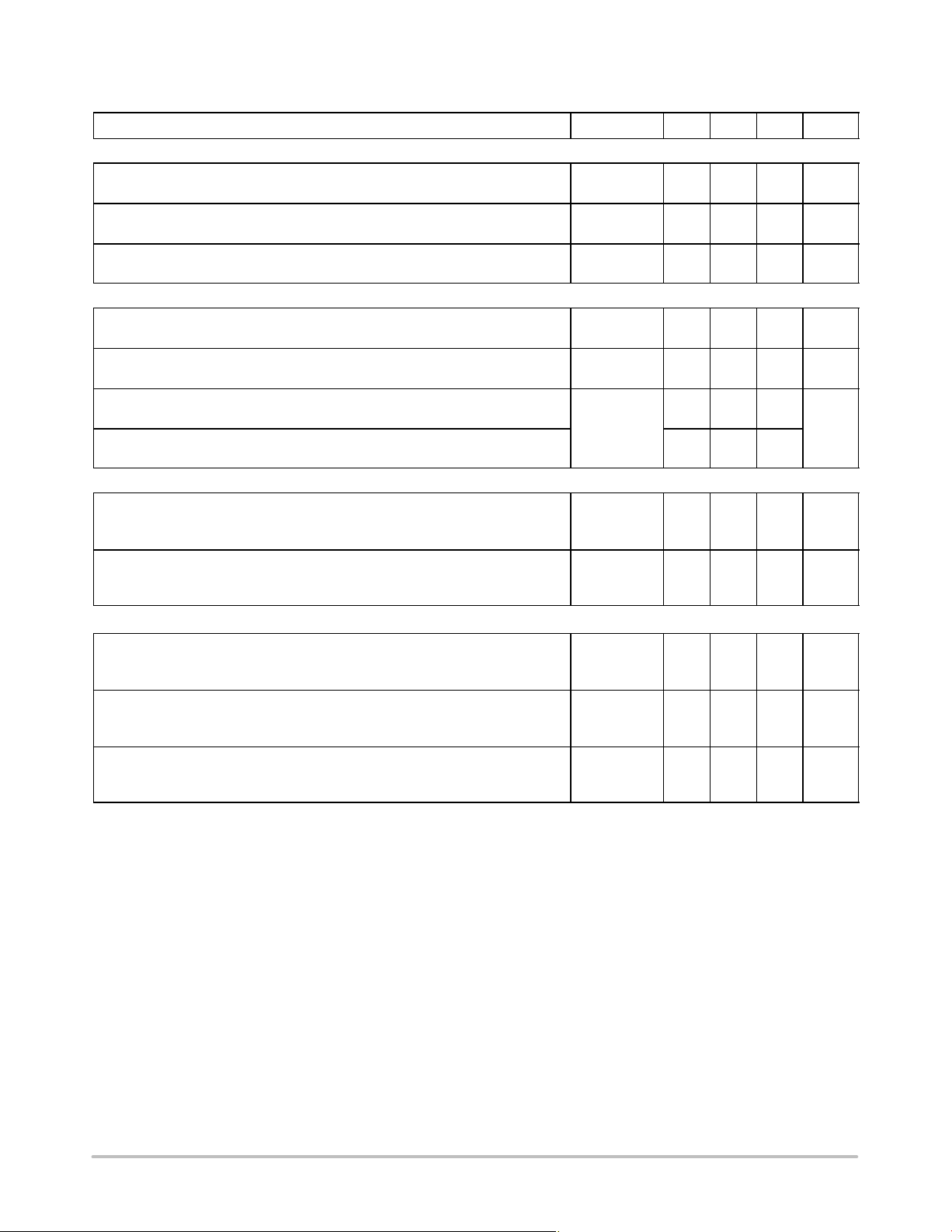

1 k

20

10

5

3

2

1

0.5

0.3

, COLLECTOR CURRENT (AMP)

0.1

C

I

0.05

0.02

500ms

5ms

dc

100ms

1ms

a transistor: average junction temperature and second

breakdown. Safe operating area curves indicate I

C

- V

CE

limits of the transistor that must be observed for reliable

operation; i.e., the transistor must not be subjected to greater

dissipation than the curves indicate.

There are two limitations on the power handling ability of

THERMAL LIMIT @ TC = 25°C

WIRE BOND LIMIT

The data of Figure 2 is based on T

variable depending on conditions. Second breakdown pulse

limits are valid for duty cycles to 10% provided T

v 150_C. T

may be calculated from the data in

J(pk)

= 150_C; TC is

J(pk)

J(pk)

Figure 1. At high case temperatures, thermal limitations will

reduce the power that can be handled to values less than the

1

V

CE

5 7 20 7010

3 100

, COLLECTOR-EMITTER VOLTAGE (VOLTS)

5030

Figure 2. Maximum Forward Bias

Safe Operating Area

TAT

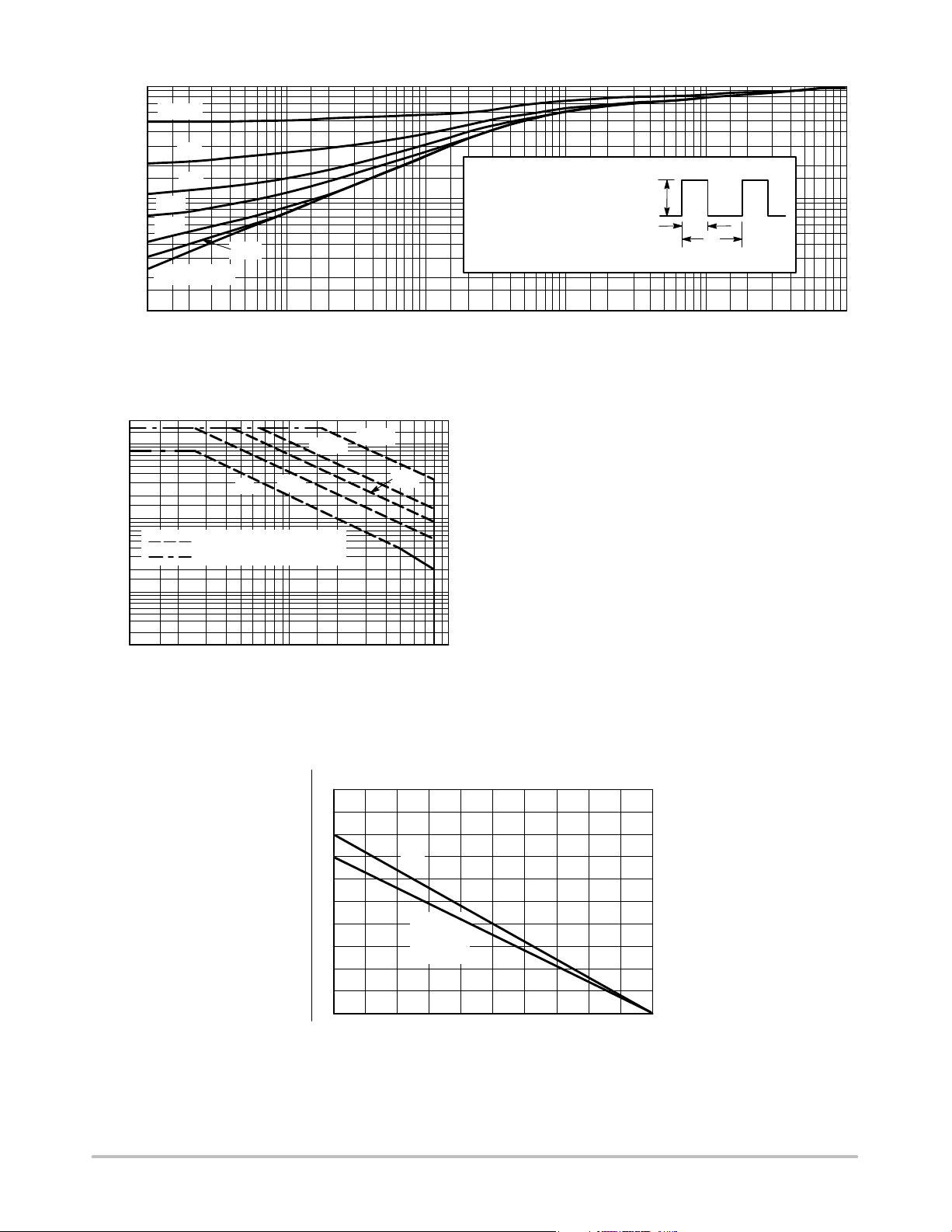

C

25

2.5

20

2

T

1.5

15

C

limitations imposed by second breakdown.

0.5

, POWER DISSIPATION (WATTS)

D

P

10

1

5

0

0

25

T

A

SURFACE

MOUNT

50 75 100 125 150

T, TEMPERATURE (°C)

Figure 3. Power Derating

http://onsemi.com

3

Loading...

Loading...