Page 1

Cat. No. W146-E1-5

SYSMAC

C20K/C28K/C40K/C60K

Programmable Controllers

Page 2

K-type

Programmable Controllers

OPERATION MANUAL

Revised July 1999

Page 3

Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator

and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this manual. Always heed

the information provided with them. Failure to heed precautions can result in injury to people or damage to property.

DANGER Indicates an imminently hazardous situation which, if not avoided, will result in death or

!

serious injury.

WARNING Indicates a potentially hazardous situation which, if not avoided, could result in death or

!

serious injury.

Caution Indicates a potentially hazardous situation which, if not avoided, may result in minor or

!

moderate injury, or property damage.

OMRON Product References

All OMRON products are capitalized in this manual. The word “Unit” is also capitalized when it refers

to an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation “Ch,” which appears in some displays and on some OMRON products, often means

“word” and is abbreviated “Wd” in documentation in this sense.

The abbreviation “PC” means Programmable Controller and is not used as an abbreviation for anything else.

Visual Aids

The following headings appear in the left column of the manual to help you locate different types of

information.

OMRON, 1992

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any

form, or by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is

constantly striving to improve its high-quality products, the information contained in this manual is subject to change

without notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no

responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in this publication.

Note Indicates information of particular interest for efficient and convenient operation

of the product.

1, 2, 3...

1. Indicates lists of one sort or another, such as procedures, checklists, etc.

ii

Page 4

About this Manual:

The OMRON K-type Programmable Controllers offer an effective way to automate processing, manufacturing, assembly, packaging, and many other processes to save time and money. Distributed control systems can also be designed to allow centralized monitoring and supervision of several separate

controlled systems. Monitoring and supervising can be done through a host computer, connecting the

controlled system to a data bank. It is thus possible to have adjustments in system operation made

automatically to compensate for requirement changes.

The K-type Units can utilize a number of additional Units including dedicated Special I/O Units that

can be used for specific tasks and Link Units that can be used to build more highly integrated systems.

The K-types are equipped with large programming instruction sets, data areas, and other features to

control processing directly. Programming utilizes ladder-diagram programming methods, which are

described in detail for those unfamiliar with them.

This manual describes the characteristics and abilities of the K-types programming operations, instructions, and other aspects of operation and preparation that demand attention. Before attempting

to operate the PC, thoroughly familiarize yourself with the information contained herein. Hardware

information is provided in detail in the

combination with this manual is provided at the end of

Section 1 Introduction

programming. It also provides an overview of the process of programming and operating a PC and

explains basic terminology used with OMRON PCs. Descriptions of peripheral devices used with the

K-types and a table of other manuals available to use with this manual for special PC applications are

also provided.

Section 2 Hardware Considerations

scribes the indicators that are referred to in other sections of this manual.

Section 3 Memory Areas

information provided there to aid in programming. It also explains how I/O is managed in memory and

how bits in memory correspond to specific I/O points.

Section 4 Programming

looking at the elements that make up the ‘ladder’ part of a ladder-diagram program and explaining

how execution of this program is controlled and the methods required to input it input the PC. S

tion 5 Instruction Set

ming, while

the program and tells how to coordinate inputs and outputs so that they occur at the proper times.

Section 6 Program Execution Timing

Section 7 Debugging and Execution

the program and to monitor and control system operation.

Finally,

means of reducing system down time. Information in this section is also necessary when debugging a

program.

The

tables of instructions and Programming Console operations, and other information helpful in PC operation.

Section 8 Troubleshooting

Appendices

explains the background and some of the basic terms used in ladder-diagram

takes a look at the way memory is divided and allocated and explains the

explains the basics of writing and inputting the ladder-diagram program,

then goes on to describe individually all of the instructions used in program-

provide tables of standard OMRON products available for the K-types, reference

Installation Guide

explains basic aspects of the overall PC configuration and de-

. A table of other manuals that can be used in

Section 1 Introduction

.

ec-

explains the scanning process used to execute

provides the Programming Console procedures used to debug

provides information on system error indications and other

WARNING Failure to read and understand the information provided in this manual may result in

!

personal injury or death, damage to the product, or product failure. Please read each

section in its entirety and be sure you understand the information provided in the section

and related sections before attempting any of the procedures or operations given.

iii

Page 5

TABLE OF CONTENTS

PRECAUTIONS ix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 Intended Audience x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 General Precautions x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Safety Precautions x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Operating Environment Precautions x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Application Precautions xi. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 1 – Background 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1 Introduction 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-2 Relay Circuits: The Roots of PC Logic 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-3 PC Terminology 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-4 OMRON Product Terminology 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-5 Overview of PC Operation 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-6 Peripheral Devices 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-7 Available Manuals 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 2 – Hardware Considerations 7. . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1 Introduction 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2 Indicators 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3 PC Configuration 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 3 – Memory Areas 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1 Introduction 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2 Data Area Structure 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-3 Internal Relay (IR) Area 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4 Special Relay (SR) Area 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-1 Battery Alarm Flag 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-2 Cycle Time Error Flag 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-3 High-speed Drum Counter Reset 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-4 Clock Pulse Bits 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-5 Error Flag (ER) 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-6 Step Flag 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-7 Always OFF, Always ON Flags 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-8 First Cycle Flag 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-9 Arithmetic Flags 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5 Data Memory (DM) Area 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-6 Holding Relay (HR) Area 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-7 Timer/Counter (TC) Area 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-8 Temporary Relay (TR) Area 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 4 – Writing and Inputting the Program 25. . . . . . . . . . . . . . . . . . .

4-1 Introduction 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-2 Instruction Terminology 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3 The Ladder Diagram 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-1 Basic Terms 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-2 Mnemonic Code 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-3 Ladder Instructions 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-4 OUT and OUT NOT 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-5 The END Instruction 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-6 Logic Block Instructions 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-7 Coding Multiple Right-hand Instructions 39. . . . . . . . . . . . . . . . . . . . . .

4-3-8 Branching Instruction Lines 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3-9 Jumps 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

Page 6

Table of contents

4-4 The Programming Console 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-4-1 The Keyboard 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-4-2 PC Modes 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-5 Preparation for Operation 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-5-1 Entering the Password 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-5-2 Clearing Memory 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-5-3 Clearing Error Messages 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-6 Inputting, Modifying, and Checking the Program 49. . . . . . . . . . . . . . . . . . . . . . . .

4-6-1 Setting and Reading from Program Memory Address 50. . . . . . . . . . . .

4-6-2 Inputting or Overwriting Programs 51. . . . . . . . . . . . . . . . . . . . . . . . . . .

4-6-3 Checking the Program 53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-6-4 Displaying the Cycle Time 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-6-5 Program Searches 55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-6-6 Inserting and Deleting Instructions 57. . . . . . . . . . . . . . . . . . . . . . . . . . .

4-7 Controlling Bit Status 59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-7-1 DIFFERENTIATE UP and DIFFERENTIATE DOWN 59. . . . . . . . . . .

4-7-2 KEEP 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-7-3 Self-maintaining Bits (Seal) 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-8 Work Bits (Internal Relays) 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-9 Programming Precautions 63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-10 Program Execution 65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 5 – Instruction Set 67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-1 Introduction 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-2 Notation 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-3 Instruction Format 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-4 Data Areas, Definer Values, and Flags 69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-4-1 Coding Other Instructions 69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-5 Ladder Diagram Instructions 73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-5-1 LOAD, LOAD NOT, AND, AND NOT, OR, and OR NOT 73. . . . . . . .

5-5-2 AND LOAD and OR LOAD 74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-6 Bit Control Instructions 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-6-1 OUTPUT and OUTPUT NOT – OUT and OUT NOT 75. . . . . . . . . . . .

5-6-2 DIFFERENTIATE UP and DIFFERENTIATE DOWN –

5-6-3 KEEP – KEEP(11) 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-7 INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03) 78. . . . . . . . . . . .

5-8 JUMP and JUMP END – JMP(04) and JME(05) 80. . . . . . . . . . . . . . . . . . . . . . . . .

5-9 END – END(01) 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-10 NO OPERATION – NOP(00) 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11 Timer and Counter Instructions 82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11-1 TIMER – TIM 83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11-2 HIGH-SPEED TIMER – TIMH(15) 86. . . . . . . . . . . . . . . . . . . . . . . . . .

5-11-3 Analog Timer Unit 87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11-4 COUNTER – CNT 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11-5 REVERSIBLE COUNTER – CNTR(12) 93. . . . . . . . . . . . . . . . . . . . . .

5-11-6 HIGH-SPEED DRUM COUNTER – HDM(61) 94. . . . . . . . . . . . . . . . .

5-11-7 REVERSIBLE DRUM COUNTER – RDM(60) 103. . . . . . . . . . . . . . . . .

5-12 Data Shifting 106. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-12-1 SHIFT REGISTER – SFT(10) 106. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-12-2 REVERSIBLE SHIFT REGISTER – SFTR(84) 109. . . . . . . . . . . . . . . . .

5-12-3 WORD SHIFT – WSFT(16) 110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-13 Data Movement 111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-13-1 MOVE – MOV(21) 111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-13-2 MOVE NOT – MVN(22) 112. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-14 DATA COMPARE – CMP(20) 112. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15 Data Conversion 115. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15-1 BCD-TO- BINARY – BIN(23) 115. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIFU(13) and DIFD(14) 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

Page 7

Table of contents

5-15-2 BINARY-TO-BCD – BCD(24) 115. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15-3 4-TO-16 DECODER – MLPX(76) 116. . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15-4 16-TO-4 ENCODER – DMPX(77) 118. . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16 BCD Calculations 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16-1 BCD ADD – ADD(30) 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16-2 BCD SUBTRACT – SUB(31) 122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16-3 BCD MULTIPLY – MUL(32) 123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16-4 BCD DIVIDE – DIV(33) 124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16-5 SET CARRY – STC(40) 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16-6 CLEAR CARRY – CLC(41) 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-17 Subroutines 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-17-1 SUBROUTINE DEFINE and SUBROUTINE RETURN

5-17-2 SUBROUTINE ENTRY – SBS(91) 126. . . . . . . . . . . . . . . . . . . . . . . . . .

5-18 Step Instructions 128. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-18-1 STEP DEFINE and STEP START – STEP(08)/SNXT(09) 128. . . . . . . .

5-19 Special Instructions 135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-19-1 I/O REFRESH – IORF(97) 135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-19-2 END WAIT – ENDW(62) 135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-19-3 NOTATION INSERT – NETW(63) 136. . . . . . . . . . . . . . . . . . . . . . . . . .

SBN(92)/RET(93) 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 6 – Program Execution Timing 137. . . . . . . . . . . . . . . . . . . . . . . . . .

6-1 Introduction 138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-2 Cycle Time 139. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-3 Calculating Cycle Time 141. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-3-1 Single PC Unit 141. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-3-2 PC with Additional Units 142. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-4 Instruction Execution Times 143. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-5 I/O Response Time 145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SECTION 7 – Program Debugging and Execution 147. . . . . . . . . . . . . . . . . . .

7-1 Introduction 148. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-2 Debugging 148. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-3 Monitoring Operation and Modifying Data 149. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-3-1 Bit/Digit Monitor 150. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-3-2 Force Set/Reset 153. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-3-3 Hexadecimal/BCD Data Modification 155. . . . . . . . . . . . . . . . . . . . . . . .

7-3-4 Changing Timer/Counter SV 156. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-4 Program Backup and Restore Operations 157. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-4-1 Saving Program Memory Data 158. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-4-2 Restoring or Comparing Program Memory Data 159. . . . . . . . . . . . . . . .

SECTION 8 – Troubleshooting 161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8-1 Introduction 162. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8-2 Reading and Clearing Errors and Messages 162. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8-3 Error Messages 162. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8-4 Error Flags 164. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix 165. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A – Standard Models 165. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B – Programming Instructions and Execution Times 171. . . . . . . . . . . . . . . . . . . . . . . . . . .

C – Programming Console Operations 183. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D – Error and Arithmetic Flag Operation 189. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E – Binary–Hexadecimal–Decimal Table 191. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

F – Word Assignment Recording Sheets 193. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

G – Program Coding Sheet 199. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Glossary 201. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Index 215. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

Page 8

PRECAUTIONS

This section provides general precautions for using the K-type Programmable Controllers (PCs) and related devices.

The information contained in this section is important for the safe and reliable application of Programmable Controllers. You must read this section and understand the information contained before attempting to set up or operate a PC

system.

1 Intended Audience x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 General Precautions x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Safety Precautions x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Operating Environment Precautions x. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Application Precautions xi. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ix

Page 9

1 Intended Audience

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

• Personnel in charge of installing FA systems.

• Personnel in charge of designing FA systems.

• Personnel in charge of managing FA systems and facilities.

2 General Precautions

The user must operate the product according to the performance specifications

described in the operation manuals.

Before using the product under conditions which are not described in the manual

or applying the product to nuclear control systems, railroad systems, aviation

systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment that

may have a serious influence on lives and property if used improperly, consult

your OMRON representative.

Make sure that the ratings and performance characteristics of the product are

sufficient for the systems, machines, and equipment, and be sure to provide the

systems, machines, and equipment with double safety mechanisms.

This manual provides information for programming and operating the Unit. Be

sure to read this manual before attempting to use the Unit and keep this manual

close at hand for reference during operation.

5Application Precautions

WARNING It is extremely important that a PC and all PC Units be used for the specified

!

purpose and under the specified conditions, especially in applications that can

directly or indirectly affect human life. You must consult with your OMRON

representative before applying a PC System to the above-mentioned

applications.

3 Safety Precautions

WARNING Do not attempt to take any Unit apart while the power is being supplied. Doing so

!

may result in electric shock.

WARNING Do not touch any of the terminals or terminal blocks while the power is being

!

supplied. Doing so may result in electric shock.

WARNING Do not attempt to disassemble, repair, or modify any Units. Any attempt to do so

!

may result in malfunction, fire, or electric shock.

4 Operating Environment Precautions

Caution Do not operate the control system in the following locations:

!

• Locations subject to direct sunlight.

• Locations subject to temperatures or humidity outside the range specified in

the specifications.

• Locations subject to condensation as the result of severe changes in temperature.

x

Page 10

• Locations subject to corrosive or flammable gases.

• Locations subject to dust (especially iron dust) or salts.

• Locations subject to exposure to water, oil, or chemicals.

• Locations subject to shock or vibration.

Caution Take appropriate and sufficient countermeasures when installing systems in the

!

following locations:

• Locations subject to static electricity or other forms of noise.

• Locations subject to strong electromagnetic fields.

• Locations subject to possible exposure to radioactivity.

• Locations close to power supplies.

Caution The operating environment of the PC System can have a large effect on the lon-

!

gevity and reliability of the system. Improper operating environments can lead to

malfunction, failure, and other unforeseeable problems with the PC System. Be

sure that the operating environment is within the specified conditions at installation and remains within the specified conditions during the life of the system.

5 Application Precautions

Observe the following precautions when using the PC System.

5Application Precautions

WARNING Always heed these precautions. Failure to abide by the following precautions

!

could lead to serious or possibly fatal injury.

• Always ground the system to 100 Ω or less when installing the Units. Not con-

necting to a ground of 100 Ω or less may result in electric shock.

• Always turn OFF the power supply to the PC before attempting any of the following. Not turning OFF the power supply may result in malfunction or electric

shock.

• Mounting or dismounting I/O Units, CPU Units, Memory Cassettes, or any

other Units.

• Assembling the Units.

• Setting DIP switches or rotary switches.

• Connecting cables or wiring the system.

• Connecting or disconnecting the connectors.

Caution Failure to abide by the following precautions could lead to faulty operation of the

!

PC or the system, or could damage the PC or PC Units. Always heed these precautions.

• Fail-safe measures must be taken by the customer to ensure safety in the

event of incorrect, missing, or abnormal signals caused by broken signal lines,

momentary power interruptions, or other causes.

• Interlock circuits, limit circuits, and similar safety measures in external circuits

(i.e., not in the Programmable Controller) must be provided by the customer.

• Always use the power supply voltages specified in the operation manuals. An

incorrect voltage may result in malfunction or burning.

• Take appropriate measures to ensure that the specified power with the rated

voltage and frequency is supplied. Be particularly careful in places where the

power supply is unstable. An incorrect power supply may result in malfunction.

• Install external breakers and take other safety measures against short-circuiting in external wiring. Insufficient safety measures against short-circuiting may

result in burning.

xi

Page 11

• Do not apply voltages to the Input Units in excess of the rated input voltage.

Excess voltages may result in burning.

• Do not apply voltages or connect loads to the Output Units in excess of the

maximum switching capacity . Excess voltages or loads may result in burning.

• Disconnect the functional ground terminal when performing withstand voltage

tests. Not disconnecting the functional ground terminal may result in burning.

• Be sure that all the mounting screws, terminal screws, and cable connector

screws are tightened to the torque specified in the relevant manuals. Incorrect

tightening torque may result in malfunction.

• Leave the label attached to the Unit when wiring. Removing the label may result in malfunction if foreign matter enters the Unit.

• Remove the label after the completion of wiring to ensure proper heat dissipation. Leaving the label attached may result in malfunction.

• Use crimp terminals for wiring. Do not connect bare stranded wires directly to

terminals. Connection of bare stranded wires may result in burning.

• Wire all connections correctly.

• Double-check all wiring and switch settings before turning ON the power sup-

ply. Incorrect wiring may result in burning.

• Be sure that the terminal blocks, Memory Units, expansion cables, and other

items with locking devices are properly locked into place. Improper locking

may result in malfunction.

• Check the user program for proper execution before actually running it on the

Unit. Not checking the program may result in an unexpected operation.

• Confirm that no adverse ef fect will occur in the system before attempting any of

the following. Not doing so may result in an unexpected operation.

• Changing the operating mode of the PC.

• Force-setting/force-resetting any bit in memory.

• Changing the present value of any word or any set value in memory.

• Resume operation only after transferring to the new CPU Unit the contents of

the DM Area, HR Area, and other data required for resuming operation. Not

doing so may result in an unexpected operation.

• Do not pull on the cables or bend the cables beyond their natural limit. Doing

either of these may break the cables.

• Do not place objects on top of the cables or other wiring lines. Doing so may

break the cables.

• When replacing parts, be sure to confirm that the rating of a new part is correct.

Not doing so may result in malfunction or burning.

• Before touching a Unit, be sure to first touch a grounded metallic object in order

to discharge any static built-up. Not doing so may result in malfunction or damage.

• Install the Units properly as specified in the operation manuals. Improper

installation of the Units may result in malfunction.

5Application Precautions

xii

Page 12

SECTION 1

Background

1-1 Introduction 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-2 Relay Circuits: The Roots of PC Logic 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-3 PC Terminology 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-4 OMRON Product Terminology 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-5 Overview of PC Operation 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-6 Peripheral Devices 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-7 Available Manuals 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1

Page 13

Relay Circuits: The Roots of PC Logic Section 1-2

1-1 Introduction

A Programmable Controller (PC) is basically a central processing unit (CPU)

containing a program and connected to input and output (I/O) devices (I/O

Devices). The program controls the PC so that when an input signal from an

input device turns ON, the appropriate response is made. The response normally involves turning ON an output signal to some sort of output device. The

input devices could be photoelectric sensors, pushbuttons on control panels,

limit switches, or any other device that can produce a signal that can be input

into the PC. The output devices could be solenoids, switches activating indicator lamps, relays turning on motors, or any other devices that can be activated by signals output from the PC.

For example, a sensor detecting a product passing by turns ON an input to

the PC. The PC responds by turning ON an output that activates a pusher

that pushes the product onto another conveyor for further processing. Another sensor, positioned higher than the first, turns ON a different input to

indicate that the product is too tall. The PC responds by turning on another

pusher positioned before the pusher mentioned above to push the too-tall

product into a rejection box.

Although this example involves only two inputs and two outputs, it is typical of

the type of control operation that PCs can achieve. Actually even this example is much more complex than it may at first appear because of the timing

that would be required, i.e., “How does the PC know when to activate each

pusher?” Much more complicated operations, however, are also possible.

The problem is how to get the desired control signals from available inputs at

appropriate times.

Desired control sequences are input to the K-type PCs using a form of PC

logic called ladder-diagram programming. This manual is written to explain

ladder-diagram programming and to prepare the reader to program and operate the K-type PCs.

1-2 Relay Circuits: The Roots of PC Logic

PCs historically originate in relay-based control systems. And although the

integrated circuits and internal logic of the PC have taken the place of the

discrete relays, timers, counters, and other such devices, actual PC operation proceeds as if those discrete devices were still in place. PC control, however, also provides computer capabilities and consistency to achieve a great

deal more flexibility and reliability than is possible with relays.

The symbols and other control concepts used to describe PC operation also

come from relay-based control and form the basis of the ladder-diagram programming method. Most of the terms used to describe these symbols and

concepts, however, originated as computer terminology.

Relay vs. PC Terminology

The terminology used throughout this manual is somewhat different from relay terminology, but the concepts are the same. The following table shows

the relationship between relay terms and the PC terms used for OMRON

PCs.

Relay term PC equivalent

contact input or condition

coil output or work bit

NO relay normally open condition

NC relay normally closed condition

2

Page 14

OMRON Product Terminology Section 1-4

Actually there is not a total equivalence between these terms, because the

term condition is used only to describe ladder diagram programs in general

and is specifically equivalent to one of certain basic instructions. The terms

input and output are not used in programming per se, except in reference to

I/O bits that are assigned to input and output signals coming into and leaving

the PC. Normally open conditions and normally closed conditions are explained in

4-3 The Ladder Diagram

.

1-3 PC Terminology

Although also provided in the

ing terms are crucial to understanding PC operation and are thus explained

here as well.

Glossary

at the back of this manual, the follow-

PC

Inputs and Outputs

When we refer to the PC, we are generally talking about the CPU and all of

the Units directly controlled by it through the program. This does not include

the I/O devices connected to PC inputs and outputs.

If you are not familiar with the terms used above to describe a PC, refer to

Section 2 Hardware Considerations

A device connected to the PC that sends a signal to the PC is called an input

device; the signal it sends is called an input signal. A signal enters the PC

through terminals or through pins on a connector on a Unit. The place where

a signal enters the PC is called an input point. This input point is allocated a

location in memory that reflects its status, i.e., either ON or OFF. This memory location is called an input bit. The CPU in its normal processing cycle

monitors the status of all input points and turns ON and OFF corresponding

input bits accordingly.

There are also output bits in memory that are allocated to output points on

Units through which output signals are sent to output devices, i.e., an output bit is turned ON to send a signal to an output device through an output

point. The CPU periodically turns output points ON and OFF according to the

status of the output bits.

These terms are used when describing different aspects of PC operation.

When programming, one is concerned with what information is held in memory, and so I/O bits are referred to. When describing the Units that connect

the PC to the controlled system and the places on these Units where signals

enter and leave the PC, I/O points are referred to. When wiring these I/O

points, the physical counterparts of the I/O points, either terminals or connector pins, are referred to. When describing the signals that enter or leave the

system, reference is made to input signals and output signals, or sometimes

just inputs and outputs.

for explanations.

Controlled System and

Control System

The Control System includes the PC and all I/O devices it uses to control an

external system. A sensor that provides information to achieve control is an

input device that is clearly part of the Control System. The controlled system

is the external system that is being controlled by the PC program through

these I/O devices. I/O devices can sometimes be considered part of the controlled system, e.g., a motor used to drive a conveyor belt.

1-4 OMRON Product Terminology

OMRON products are divided into several functional groups that have generic names.

The term Unit is used to refer to all OMRON PC products, depending on the

context.

The largest group of OMRON products is I/O Units. I/O Units come in a variety of point quantities and specifications.

Appendix A Standard Models

list products by these groups.

3

Page 15

Overview of PC Operation Section 1-5

Special I/O Units are dedicated Units that are designed to meet specific

needs. These include Analog Timer Units and Analog I/O Units.

Link Units are used to create Link Systems that link more than one PC or

link a single PC to remote I/O points. Link Units include I/O Link Units that

are used to connect K-type PCs to Remote I/O Systems controlled by a larger PC (e.g. C1000H) and Host Link Units.

Other product groups include Programming Devices and Peripheral De-

vices.

1-5 Overview of PC Operation

The following are the basic steps involved in programming and operating a

K-type PC. Assuming you have already purchased one or more of these

PCs, you must have a reasonable idea of the required information for steps

one and two, which are discussed briefly below. This manual is written to explain steps three through six, eight, and nine. The section(s) of this manual

that provide relevant information are listed with each of these steps.

1, 2, 3...

1. Determine what the controlled system must do, in what order, and at

what times.

2. Determine what Units will be required. Refer to the

a Link System is required, refer to the required

3. On paper, assign all input and output devices to I/O points on Units and

determine which I/O bits will be allocated to each. If the PC includes

Special I/O Units or Link Systems, refer to the individual

or

Manuals

Memory Areas

4. Using relay ladder symbols, write a program that represents the se-

quence of required operations and their inter-relationships. Be sure to

also program appropriate responses for all possible emergency situations. (

tion Set

5. Input the program and all required operating parameters into the PC.

Section 4 Writing and Inputting the Program

(

6. Debug the program, first to eliminate any syntax errors and then to elim-

inate execution errors. (

System Manuals

)

Section 4 Writing and Inputting the Program, Section 5 Instruc-

, and

Section 6 Program Execution Timing)

for details on I/O bit allocation. (

Section 4 Writing and Inputting the Program,

Section 7 Program Debugging and Execution

Troubleshooting

7. Wire the PC to the controlled system. This step can actually be started

as soon as step 3 has been completed. Refer to the

and to

Operation Manuals

Units.

8. Test the program in an actual control situation and fine tune it if required.

Section 7 Program Debugging and Execution

(

Troubleshooting

9. Record two copies of the finished program on masters and store them

safely in different locations. (

)

tion

)

and

System Manuals

)

Section 7 Program Debugging and Execu-

Installation Guide

System Manual(s)

Operation

Section 3

)

, and

Section 8

Installation Guide

for details on individual

and

Section 8

. If

.

Control System Design

4

Designing the Control System is the first step in automating any process. A

PC can be programmed and operated only after the overall Control System is

fully understood. Designing the Control System requires a thorough understanding of the system that is to be controlled. The first step in designing a

Control System is thus determining the requirements of the controlled system.

Page 16

Peripheral Devices Section 1-6

Input/Output Requirements

Sequence, Timing, and

Relationships

Unit Requirements

The first thing that must be assessed is the number of input and output points

that the controlled system will require. This is done by identifying each device

that is to send an input signal to the PC or which is to receive an output signal from the PC. Keep in mind that the number of I/O points available depends on the configuration of the PC. Refer to

for details on I/O capacity and assigning I/O bits to I/O points.

Next, determine the sequence in which control operations are to occur and

the relative timing of the operations. Identify the physical relationships between the I/O devices as well as the kinds of responses that should occur

between them.

For instance, a photoelectric switch might be functionally tied to a motor by

way of a counter within the PC. When the PC receives an input from a start

switch, it could start the motor. The PC could then stop the motor when the

counter has received five input signals from the photoelectric switch.

Each of the related tasks must be similarly determined, throughout the entire

control operation.

The actual Units that will be mounted must be determined according to the

requirements of the I/O devices. This will include actual hardware specifications, such as voltage and current levels, as well as functional considerations, such as those that require Special I/O Units or Link Systems. In many

cases, Special I/O Units or Link Systems can greatly reduce the programming burden. Details on these Units and Link Systems are available in indi-

Operation Manuals

vidual

Once the entire Control System has been designed, the task of program-

ming, debugging, and operation as described in the remaining sections of

this manual can begin.

and

System Manuals.

3-3 Internal Relay (IR) Area

1-6 Peripheral Devices

The following peripheral devices can be used in programming, either to input/

debug/monitor the PC program or to interface the PC to external devices to

output the program or memory area data. Model numbers for all devices

listed below are provided in

names have been placed in bold when introduced in the following descriptions.

Programming Console

Graphic Programming

Console: GPC

Ladder Support Software:

LSS

A Programming Console is the simplest form of programming device for OMRON PCs. Although a Programming Console Adapter is sometimes required, all Programming Consoles are connected directly to the CPU without

requiring a separate interface. The Programming Console also functions as

an interface to output programs to a standard cassette tape recorder.

Various types of Programming Console are available, including both

CPU-mounting and Handheld models. Programming Console operations are

described later in this manual.

A Peripheral Interface Unit is required to interface the GPC to the PC.

The GPC also functions as an interface to output programs directly to a stan-

dard cassette tape recorder. A PROM Writer, Floppy Disk Interface Unit, or

Printer Interface Unit can be directly mounted to the GPC to output programs directly to an EPROM chip, floppy disk drive, or printing device.

LSS is designed to run on IBM AT/XT compatibles to enable nearly all of the

operations available on the GPC. It also offers extensive documentation capabilities.

Appendix A Standard Models

. OMRON product

5

Page 17

Available Manuals Section 1-7

A Host Link Unit is required to interface a computer running LSS to the PC.

Using an Optical Host Link Unit also enables the use of optical fiber cable to

connect the FIT to the PC. Wired Host Link Units are available when desired.

(Although FIT does not have optical connectors, conversion to optical fiber

cable is possible by using Converting Link Adapters.)

Factory Intelligent Terminal:

FIT

PROM Writer

Floppy Disk Interface Unit

Printer Interface Unit

The FIT is an OMRON computer with specially designed software that allows

you to perform all of the operations that are available with the GPC or LSS.

Programs can also be output directly to an EPROM chip, floppy disk drive, or

printing device without any additional interface units. The FIT has an EPROM

writer and two 3.5” floppy disk drives built in.

A Peripheral Interface Unit or Host Link Unit is required to interface the

FIT to the PC. Using an Optical Host Link Unit also enables the use of optical

fiber cable to connect the FIT to the PC. Wired Host Link Units are available

when desired. (Although FIT does not have optical connectors, conversion to

optical fiber cable is possible by using Converting Link Adapters.)

Other than its applications described above, the PROM Writer can be

mounted to the PC’s CPU to write programs to EPROM chips.

Other than its applications described above, the Floppy Disk Interface Unit

can be mounted to the PC’s CPU to interface a floppy disk drive and write

programs onto floppy disks.

Other than its applications described above, the Printer Interface Unit can be

mounted to the PC’s CPU to interface a printer or X-Y plotter to print out programs in either mnemonic or ladder-diagram form.

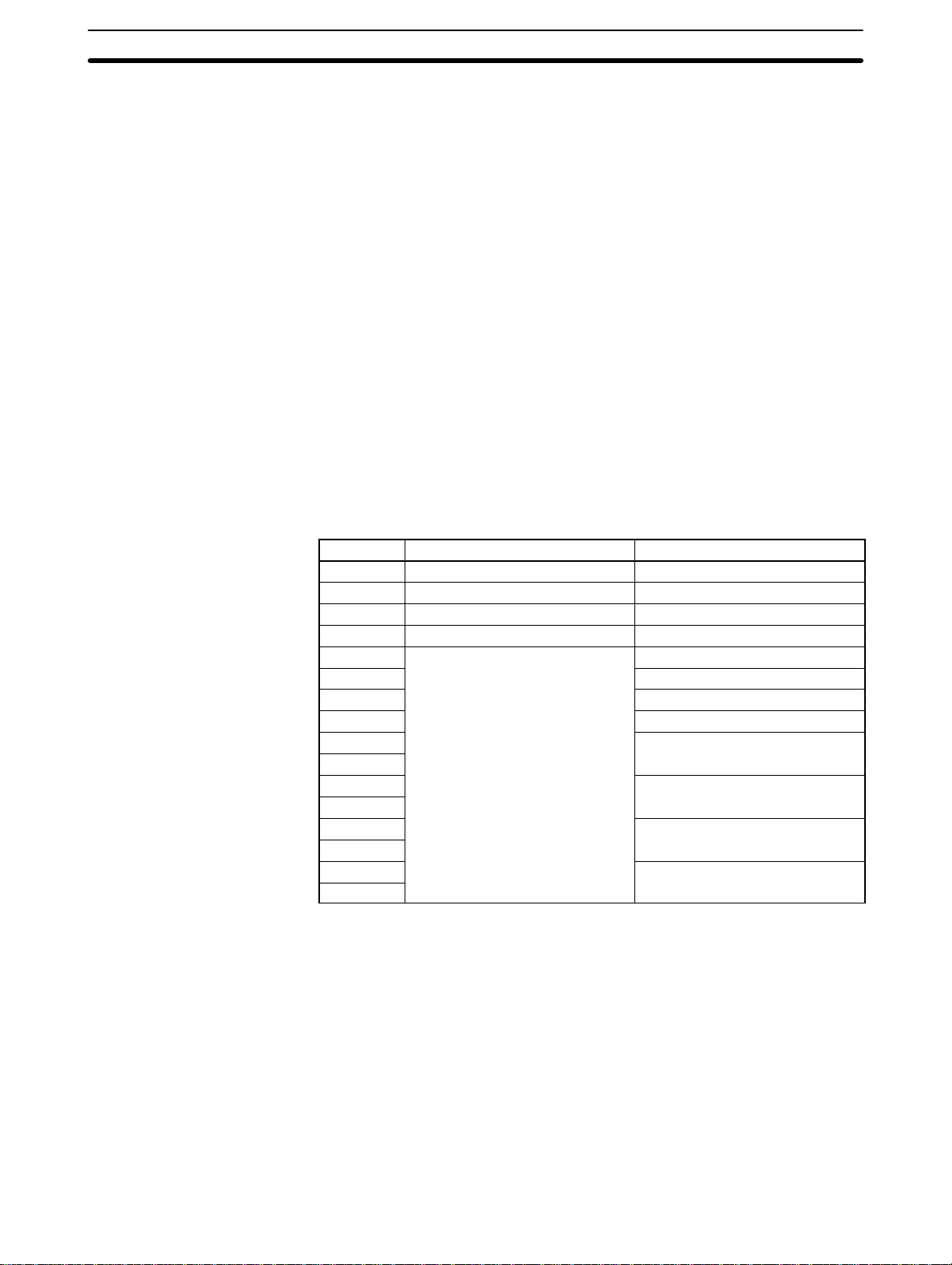

1-7 Available Manuals

The following table lists other manuals that may be required to program and/

or operate the K-type PCs.

Operation Manuals

also provided with individual Units and are required for wiring and other

specifications.

Name Cat. No. Contents

Installation Guide W147 Hardware specifications

Data Access Console Operation Guide W173 Procedures for monitoring and manipulating data.

GPC Operation Manual W84 Programming procedures for the GPC (Graphics

Programming Console)

FIT Operation Manual W150 Programming procedures for using the FIT (Factory Intelligent

Terminal

LSS Operation Manual W237 Programming procedures for using LSS (Ladder Support

Software)

Printer Interface Unit Operation Guide W107 Procedures for interfacing a PC to a printer

PROM Writer Operation Guide W155 Procedures for writing programs to EPROM chips

Floppy Disk Interface Unit Operation Guide W119 Procedures for interfacing a PC to a floppy disk drive

Optical Remote I/O System Manual W136 Information on building an Optical Remote I/O System to

enable remote I/O capability

Host Link System Manual W143 Information on building a Host Link System to manage PCs

from a ‘host’ computer

K-type Analog I/O Units Operation Guide W122 Hardware and software information on using Analog I/O Units

with the K-type PCs.

and/or

Operation Guides

are

6

Page 18

SECTION 2

Hardware Considerations

2-1 Introduction 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2 Indicators 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3 PC Configuration 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

Page 19

PC Configuration Section 2-3

2-1 Introduction

This section provides information on hardware aspects of K-type PCs that

are relevant to programming and software operation. These include indicators on the CPU and basic PC configuration. This information is covered in

detail in the

Installation Guide

.

2-2 Indicators

CPU indicators provide visual information on the general operation of the PC.

Using the flags and other error indicators provided in the memory data areas,

although not a substitute for proper error programming, provides ready confirmation of proper operation.

CPU Indicators

CPU indicators are located on the front right hand side of the PC adjacent to

the I/O expansion slot and are described in the following table.

Indicator Function

POWER Lights when power is supplied to the CPU.

RUN Lights when the CPU is operating normally .

ERR Lights when an error is discovered in system error diagnosis

ALARM Lights when an error is discovered in system error diagnosis

2-3 PC Configuration

The system must contain a K-type CPU and may additionally contain an Expansion I/O Unit, Special I/O Units and/or I/O Link Units.

The Expansion I/O Units are not a required part of the basic system and are

used to increase the number of I/O points available. Special I/O Units and I/O

Link Units are used to reduce programming complexity.

operations. When this indicator lights, the RUN indicator will go

off, CPU operation will be stopped, and all outputs from the PC

will be turned OFF.

operations. PC operation will continue.

8

Page 20

SECTION 3

Memory Areas

3-1 Introduction 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2 Data Area Structure 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-3 Internal Relay (IR) Area 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4 Special Relay (SR) Area 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-1 Battery Alarm Flag 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-2 Cycle Time Error Flag 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-3 High-speed Drum Counter Reset 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-4 Clock Pulse Bits 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-5 Error Flag (ER) 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-6 Step Flag 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-7 Always OFF, Always ON Flags 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-8 First Cycle Flag 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4-9 Arithmetic Flags 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5 Data Memory (DM) Area 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-6 Holding Relay (HR) Area 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-7 Timer/Counter (TC) Area 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-8 Temporary Relay (TR) Area 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

Page 21

Data Area Structure Section 3-2

3-1 Introduction

Various types of data are required to achieve effective and correct control. To

facilitate managing this data, the PC is provided with various memory areas

for data, each of which performs a different function. The areas generally accessible by the user for use in programming are classified as data areas.

The other memory area is the Program Memory, where the user’s program is

actually stored.

This section describes these areas individually and provides information that

will be necessary to use them. The name, acronym, range, and function of

each area are summarized in the following table. All but the last one of these

are data areas. All memory areas are normally referred to by their acronyms.

Area Acronym Range Function

Internal Relay

area

Special Relay

area

Data Memory

area

Holding Relay

area

Timer/Counter

area

Temporary Relay

area

Program Memory UM UM: 1,194 words. Contains the program executed by the CPU.

IR Words: 00 to 18 (bits 00 to 07)

Bits: 0000 to 1807

SR Words: 18 (bits 08 to 15) and

19 (bits 00 to 07)

Bits: 1808 to 1907

DM DM 00 to DM 63

(words only)

HR Words: HR 0 to HR 9

Bits: HR 000 to HR 915

TC TC 00 to TC 47 (TC numbers are

used to access other information)

TR TR 00 to TR 07 (bits only) Used to temporarily store execution conditions.

Used to manage I/O points, control other bits,

timers, and counters, to temporarily store data.

Contains system clocks, flags, control bits, and

status information.

Used for internal data storage and manipulation.

Used to store data and to retain the data values

when the power to the PC is turned off.

Used to define timers and counters and to access

completion flags, PV, and SV for them.

Work Bits and Words

When some bits and words in certain data areas are not used for their intended purpose, they can be used in programming as required to control

other bits. Words and bits available for use in this fashion are called work bits

and work words. Most, but not all, unused bits can be used as work bits.

Those that can be are specified by area in the remainder of this section. Actual application of work bits and work words is described in

and Inputting the Program

Flags and Control Bits

Some data areas contain flags and/or control bits. Flags are bits that are

automatically turned ON and OFF to indicate status of one form or another.

Although some flags can be turned ON and OFF by the user, most flags can

be read only; they cannot be controlled directly.

Control bits are bits turned ON and OFF by the user to control specific aspects of operation. Any bit given a name using the word bit rather than the

word flag is a control bit, e.g., Restart Bits are control bits.

3-2 Data Area Structure

When designating a data area, the acronym for the area is always required

for any but the IR and SR areas. Although the acronyms for the IR and SR

areas are often given for clarity, they are not required and not input when

programming. Any data area designation without an acronym is assumed to

be in either the IR and SR area. Because IR and SR addresses run consecutively, the word or bit addresses are sufficient to differentiate these two areas.

Section 4 Writing

.

10

An actual data location within any data area but the TC area is designated by

its address. The address designates the bit and/or word within the area

where the desired data is located. The TR area consists of individual bits

Page 22

Data Area Structure Section 3-2

used to store execution conditions at branching points in ladder diagrams.

The use of TR bits is described in

The TC area consists of TC numbers, each of which is used for a spe-

gram.

cific timer or counter defined in the program. Refer to

for more details on TC numbers and to

Area

for information on actual application.

tions

The rest of the data areas (i.e., the IR, SR, HR and DM areas) consist of

words, each of which consists of 16 bits numbered 00 through 15 from right

to left. IR words 00 and 01 are shown below with bit numbers. Here, the content of each word is shown as all zeros. Bit 00 is called the rightmost bit; bit

15, the leftmost bit.

Bit number 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

IR word 00 0000000000000000

IR word 01 0000000000000000

The term least significant is often used for rightmost; the term most signifi-

Note

cant, for leftmost. These terms have not been used in this manual because a

single word is often split into two or more parts, with each part used for different parameters or operands, sometimes even with bits in another word.

When this is done, the rightmost bits in a word may actually be the most significant bits, i.e., the leftmost bits, of a value with other bits, i.e., the least significant bits, contained in another word.

Section 4 Writing and Inputting the Pro-

3-7 Timer/Counter (TC)

5-11 Timer and Counter Instruc-

Data Structure

Digit number 3210

The DM area is accessible by word only; you cannot designate an individual

bit within a DM word. Data in the IR, SR and HR areas is accessible either by

bit or by word, depending on the instruction in which the data is being used.

To designate one of these areas by word, all that is necessary is the acronym

(if required) and the one or two-digit word address. To designate an area by

bit, the word address is combined with the bit number as a single three- or

four-digit address. The examples in the following table should make this

clear. The two rightmost digits of a bit designation must indicate a bit between 00 and 15.

The same TC number can be used to designate either a word containing the

present value (PV) of the timer or counter or a bit that functions as the completion flag for the timer or counter. This is explained in more detail in

Timer/Counter (TC) Area

Area Word designation Bit designation

IR 00 0015 (leftmost bit in word 00)

SR 19 1900 (rightmost bit in word 19)

DM DM 10 Not possible

TC TC 46 (designates PV) TC 46 (designates completion flag)

.

3-7

Word data input as decimal values is stored in binary-coded decimal (BCD)

code; word data input as hexadecimal is stored in binary form. Because each

word contains 16 bits, each four bits of a word represents one digit: either a

hexadecimal digit equivalent numerically to the binary bits or decimal. One

word of data thus contains four digits, which are numbered from right to left.

These digit numbers and the corresponding bit numbers for one word are

shown below.

Bit number

Contents 0000000000000000

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

11

Page 23

Internal Relay (IR) Area Section 3-3

When referring to the entire word, the digit numbered 0 is called the rightmost digit; the one numbered 3, the leftmost digit.

When inputting data into data areas, it must be input in the proper form for

the intended purpose. This is no problem when designating individual bits,

which are merely turned ON (equivalent to a binary value of 1) or OFF (a binary value of 0). When inputting word data, however, it is important to input it

either as decimal or as hexadecimal, depending on what is called for by the

instruction it is to be used for.

ticular form of data is required for an instruction.

Section 5 Instruction Set

specifies when a par-

Converting Different Forms

of Data

Binary and hexadecimal can be easily converted back and forth because

each four bits of a binary number is numerically equivalent to one digit of a

hexadecimal number. The binary number 0101111101011111 is converted to

hexadecimal by considering each set of four bits in order from the right. Binary 1111 is hexadecimal F; binary 0101 is hexadecimal 5. The hexadecimal

equivalent would thus be 5F5F, or 24,415 in decimal (16

x 5 + 15).

Decimal and BCD can also be easily converted back and forth. In this case,

each BCD digit (i.e., each four BCD bits) is numerically equivalent of the corresponding decimal digit. The BCD bits 0101011101010111 are converted to

decimal by considering each four bits from the right. Binary 0101 is decimal

5; binary 0111 is decimal 7. The decimal equivalent would thus be 5,757.

Note that this is not the same numeric value as the hexadecimal equivalent

of 0101011101010111, which would be 5,757 hexadecimal, or 22,359 in decimal (16

Because the numeric equivalent of each four BCD binary bits must be

equivalent to a decimal value, any four bit combination numerically greater

then 9 cannot be used, e.g., 1011 is not allowed because it is numerically

equivalent to 11, which cannot be expressed as a single digit in decimal notation. The binary bits 1011 are of course allowed in hexadecimal and they are

equivalent to the hexadecimal digit C.

There are instructions provided to convert data in either direction between

BCD and hexadecimal. Refer to

binary equivalents to hexadecimal and BCD digits are provided in the appendices for reference.

3

x 5 + 162 x 7 + 16 x 5 + 7).

5-15 Data Conversion

3

x 5 + 162 x 15 + 16

for details. Tables of

Decimal Points

Decimal points are used in timers only. The least significant digit represents

tenths of a second. All arithmetic instructions operate on integers only.

3-3 Internal Relay (IR) Area

The IR area is used both to control I/O points and as work bits to manipulate

and store data internally. It is accessible both by bit and by word. Those

words that can be used to control I/O points are called I/O words. Bits in I/O

words are called I/O bits.

The number of I/O words varies between the K-type PCs. As shown, the IR

area is comprised of three main sections. These are input words, output

words and work words (work bits). Work bits are used in programming to manipulate data and control other bits. IR area work bits are reset when power

is interrupted or PC operation is stopped.

12

Page 24

Internal Relay (IR) Area Section 3-3

I/O Words

Input Bit Usage

Output Bit Usage

The maximum number of available I/O bits is 16 (bits/word) times the number

of I/O words. I/O bits are assigned to input or output points as described in

Word Allocations

If a Unit brings inputs into the PC, the bit assigned to it is an input bit; if the

Unit sends an output from the PC, the bit is an output bit. To turn on an output, the output bit assigned to it must be turned ON. When an input turns on,

the input bit assigned to it also turns ON. These facts can be used in the program to access input status and control output status through I/O bits.

I/O bits that are not assigned to I/O points can be used as work bits, unless

otherwise specified in

Input bits can directly input external signals to the PC and can be used in any

order in programming. Each input bit can also be used in as many instructions as required to achieve effective and proper control. They cannot be

used in instructions that control bit status, e.g., the OUTPUT, DIFFERENTIATION UP, and KEEP instructions.

Output bits are used to output program execution results and can be used in

any order in programming. Because outputs are refreshed only once during

each cycle (i.e. once each time the program is executed), any output bit can

be used in only one instruction that controls its status, including OUT, OUT

NOT, KEEP(11), DIFU(13), DIFD(14), and SFT(10). If an output bit is used in

more than one such instruction, only the status determined by the last instruction will actually be output from the PC. See

SFT(10)

for an example of an output bit controlled by two instructions.

.

Word Allocations

.

5-12-1 SHIFT REGISTER -

Word Allocations

The maximum number of words available for I/O within the IR area is 10,

numbered 00 through 09. The remaining words (10 through 18) are to be

used for work bits. (Note that with word 18, only the bits 00 through 07 are

available for work bits although some of the remaining bits are required for

special purposes when RDM is used).

The actual number of bits that can be used as I/O bits is determined by the

model of the CPU and the PC configuration. There are different models of

Expansion I/O Units and Special I/O Units and I/O Link Units which can be

connected to any of the CPUs. Each CPU model provides a particular number of I/O bits and each Expansion I/O Unit, Special I/O Unit or I/O Link Unit

provides a particular number of I/O bits. Configuration charts for the possible

combinations of CPUs and Units are included later in this section. Refer to

those to determine the actual available I/O bits.

Within CPUs the I/O input words are always even numbered and the output

words are always odd numbered. The general rule when connecting Expansion I/O Units to CPUs is that the first available word for the Expansion I/O

Unit (whether input or output or a combination) is one more than the last I/O

word of the CPU. If the Expansion I/O Unit is only either input or output (and

not both) then the I/O words provided by the Expansion I/O Unit are allocated

consecutively and the remaining words up to word 09 may be used for work

bits. If the Expansion I/O Unit provides both input and output words then the

words are allocated alternatively (input words always having even numbers)

until all I/O words provided by the Expansion I/O Unit are allocated. The remaining words up to word 09 may then be used for work bits. Note that when

a portion of an input word is not allocated to an input point then that portion

may be used for work bits.

13

Page 25

Internal Relay (IR) Area Section 3-3

I/O Bits Available in CPUs

The following table shows which bits can be used as I/O bits in each of the

K-type CPUs. Bits in the shaded areas can be used as work bits but not as

output bits.

Model Input bits

Word 00

00

08

01

09

02

C20K

C28K

C40K

C60K

03

04

05

06

07

Word 00

00

01

02

03

04

05

06

07

Word 00

00

01

02

03

04

05

06

07

Word 00

00

01

02

03

04

05

06

07

10

11

Cannot

be

used.

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

indicates words that cannot be used for I/O,

but can be used as work bits.

Word 02

00

01

02

03

04

05

06

07

Word 02

00

01

02

03

04

05

06

07

Cannot

be

used.

08

09

10

11

12

13

14

15

Output bits

Word 01

00

01

02

03

04

05

06

07

Word 01

00

01

02

03

04

05

06

07

Word 01

00

01

02

03

04

05

06

07

Word 01

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

Word 03

00

01

02

03

04

05

06

07

Word 03

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

14

Page 26

Internal Relay (IR) Area Section 3-3

I/O Bits Available in

Expansion I/O Units

The following table shows which bits can be used as I/O bits in each of the

Expansion I/O Units. Bits in the shaded areas can be used as work bits but

not as output bits. The word addresses depend on the CPU that the Expansion I/O Unit is coupled to. In all cases the first Expansion I/O Unit address

for input and output words is one more than the last CPU address for input

and output words. For example, the last CPU word address for a C40K CPU

is 03 and hence the first input or output word address for any of the Expansion I/O Units coupled to a C40K CPU will be 04. In the tables below “n” is

the last CPU word allocated as an input or output word.

There are several models for some of the Units listed below. A blank space

(_) in the model number indicates that any of the applicable model numbers

could be inserted here.

Model Input bits Output bits Model Input bits Output bits

Word (n + 1)

00

01

02

03

04

05

06

07

Word (n + 1)

00

01

02

03

Cannot

be used

Word (n + 1)

00

01

02

03

Cannot

be used

08

09

10

11

12

13

14

15

Word (n + 1)

00

08

01

09

02

10

03

11

04

12

05

13

06

14

07

15

Word (n + 1)

00

08

01

09

02

10

03

11

04

12

05

13

06

14

07

15

Word (n + 2)

00

08

01

09

02

10

03

11

04

12

05

13

06

14

07

15

C20P

C28P

C40P

C60P

Word (n+1)

00

01

02

03

04

05

06

07

Word (n+1)

00

01

02

03

04

05

06

07

Word (n+1)

00

01

02

03

04

05

06

07

Word (n+1)

00

01

02

03

04

05

06

07

08

09

10

11

Cannot

be

used.

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

Word (n + 2)

00

08

01

09

02

10

03

11

04

12

05

13

06

14

07

15

Word (n + 2)

00

08

01

09

02

10

03

11

04

12

05

13

06

14

07

15

Word (n + 3)

00

01

02

Cannot

03

used.

04

05

06

07

Word (n + 3)

00

01

02

03

04

05

06

07

Word (n + 2)

00

01

02

03

be

04

05

06

07

Word (n + 2)

08

00

09

01

10

02

11

03

12

04

13

05

14

06

15

07

Word (n + 4)

00

01

02

03

04

05

06

07

Word (n + 4)

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

08

09

10

11

12

13

14

15

indicates words that cannot be used for I/O,

but can be used as work bits.

C16P

-Ij-j

C16P

-Oj-j

C4K-Ij

C4K-Oj

C4K-TM

15

Page 27

Internal Relay (IR) Area Section 3-3

PC Configuration

A K-type PC can be configured with a CPU Unit and one or more of the following Units: Expansion I/O Units, Analog Timer Units, or an I/O Link Unit. All

of these Units are connected in series with the CPU Unit at one end. An I/O

Link Unit, if included, must be on the other end (meaning only one I/O Link