OKI MSM9888LGS-AK Datasheet

E2D0083-27-44

Preliminary

¡ Semiconductor MSM9888L

¡ Semiconductor

This version: Jan. 1998

Previous version: May. 1997

MSM9888L

Flash-driving Recording and Playback IC

GENERAL DESCRIPTION

The MSM 9888L is a recording and playback IC that is controlled by the micro-controller in serial

mode, compresses voice with the Oki ADPCM system with high tone quality, and directly stores

voice data inthe serial voice flash momory. This IC can operate in a range of 2.7 to 3.6 V and

contains a mask ROM. Since the package is small and backup is not needed, this recording and

playback IC is suitable for the voice system such as handy terminals.

FEATURES

• Voice analyzing and synthesizing system

: 4-bit OKI ADPCM system•8-bit OKI non-linear PCM system

(for ROM playback only)

• Built-in 12-bit A/D•D/A converter

• Built-in LPF : Attenuation rate –40 dB/oct

• Sampling frequency (for 4.096 MHz of source oscillation frequency)

: 2.0 kHz, 2.7 kHz, 3.2kHz, 4.0 kHz, 5.3 kHz, 6.4 kHz, 8 kHz

• External memory for variable message

: 1Mb, 2Mb, 4Mb, 8Mb, serial voice flash memory

• Recording time (When the 1Mb serial voice flash is used)

: Approximately 32 seconds (Fsam=8.0 kHz)

: Approximately 40 seconds (Fsam=6.4 kHz)

: Approximately 65 seconds (Fsam=4.0 kHz)

• Built-in 512Kb mask ROM for fixed message

• Playback time for fixed message

: Approximately 15 seconds (Fsam=8.0 kHz)

: Approximately 20 seconds (Fsam=6.4 kHz)

: Approximately 31 seconds (Fsam=4.0 kHz)

• Number of pharase

Variable message : 63 phrases

Fixed message : 255 phrases

• Any data can be written to and read from a part in the voice flash memory.

• Serial microcontroller interface

• Source oscillation frequency : 4 MHz to 6 MHz

• Supply voltage : 2.7 V to 3.6 V

• Operating temperature : –10°C to 70°C

• Package :

30-pin plastic SSOP (SSOP30-P-56-0.65-K)(Product name : MSM9888LGS-AK)

1/14

¡ Semiconductor MSM9888L

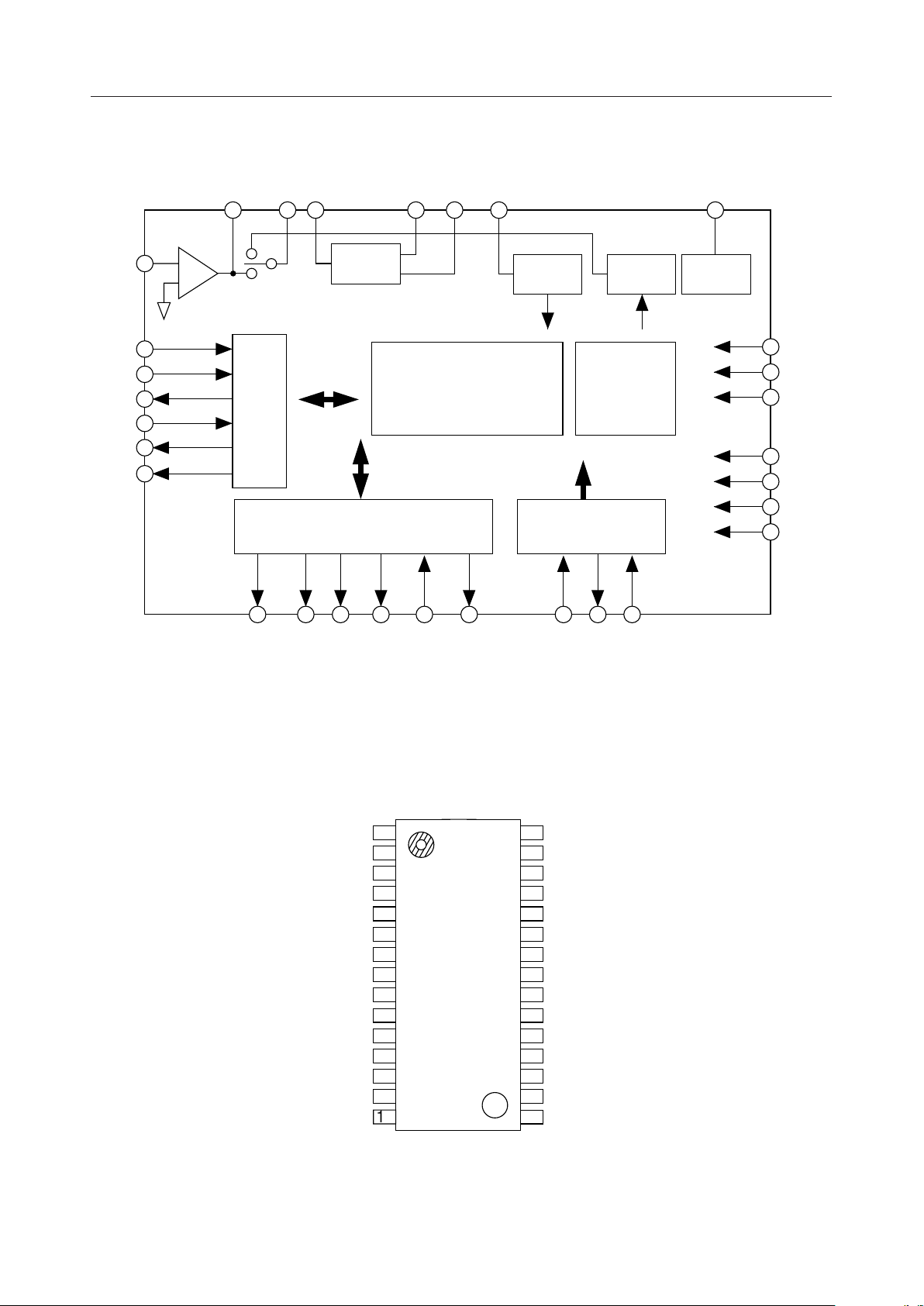

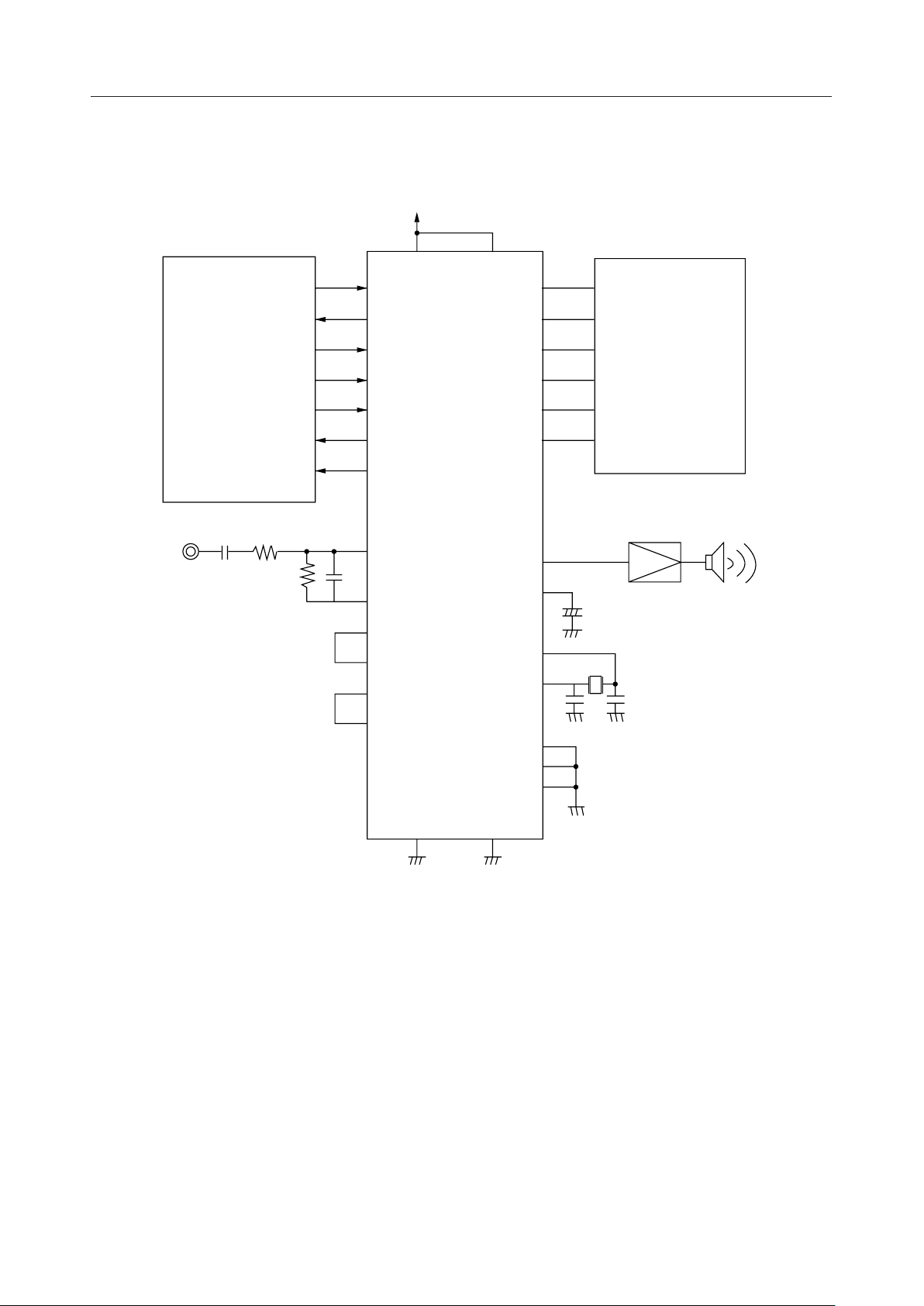

BLOCK DIAGRAM

ADINAOUTFOUTFINLOUT AMON SG

LIN

CS

DI

DO

SCK

BUSY

MON

MCU

I/F

LPF

ADPCM/PCM

Analyzer/Synthesizer

Flash Controller Timing Controller

ADC DAC SG

ROM

512Kbit

MASK ROM

RESETXTXTFDIFDOFSCKFCSFPRTFRESET

TEST0

TEST1

TEST2

AV

DD

AGND

DV

DD

DGND

PIN CONFIGURATION (TOP VIEW)

SG

1

AMON

FOUT

AOUT

DV

2

FIN

3

ADIN

4

5

6

AV

7

DD

8

DD

9

CS

XT

10

XT

11

SCK

12

DO

13

DI

14

15 16MON RESET

30-Pin Plastic SSOP

30

29

28

27

26

25

24

23

22

21

20

19

18

17

AGND

LOUT

LIN

FRESET

FPRT

FCS

FSCK

FDI

FDO

DGND

BUSY

TEST2

TEST1

TEST0

2/14

¡ Semiconductor MSM9888L

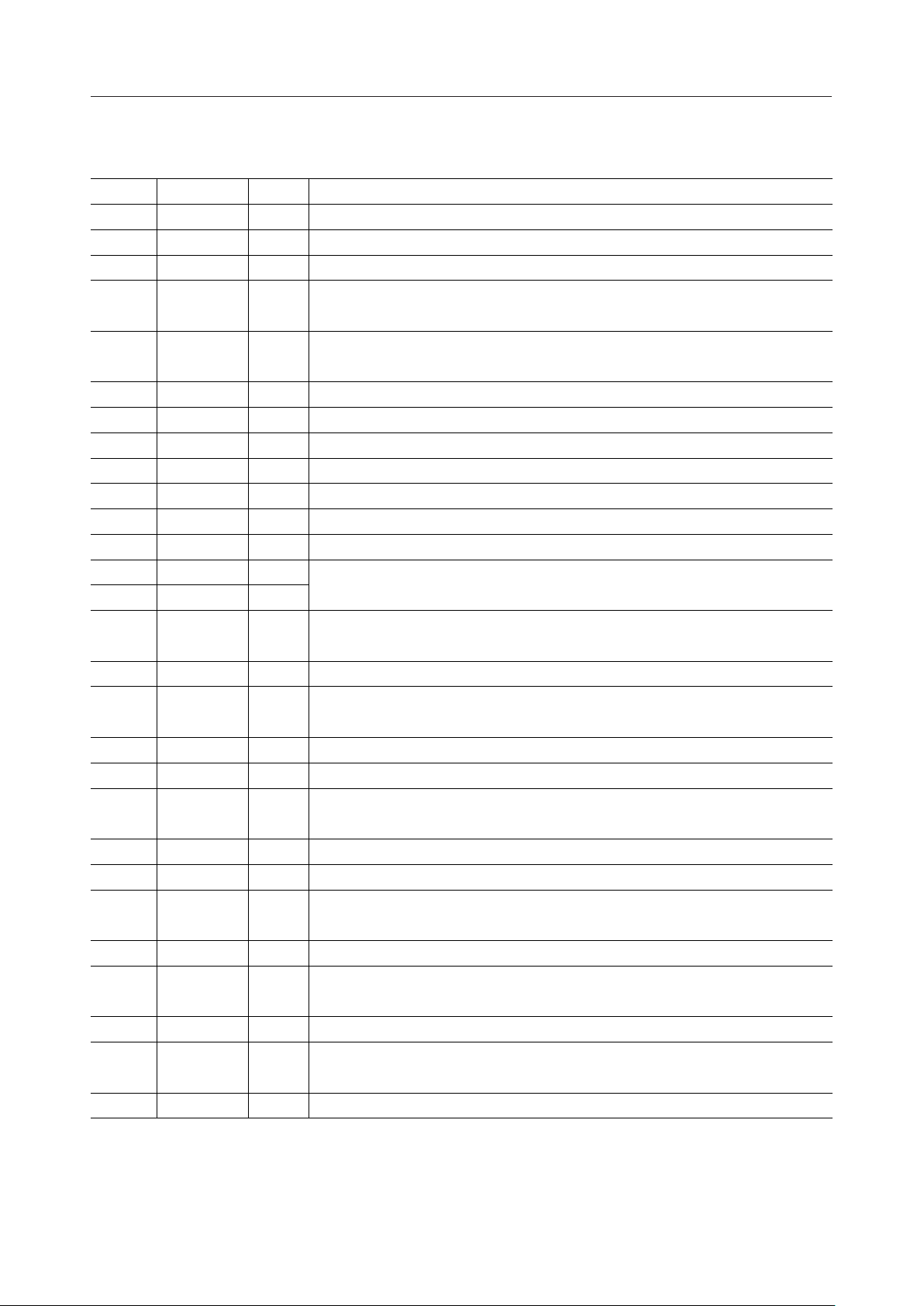

PIN DESCRIPTION

Pin

14

17-19

Symbol I/O Description

Inputs the 8-bit command data.DI I

Outputs the 8-bit status data.DO O13

Inputs the data transfer clock for the DI and DO pins.SCK I12

CS I9

BUSY O20

XT I10

XT O11

RESET I16

LIN I28

LOUT O29

ADIN I4

AMON O2

FIN I3

FOUT O5

AOUT O6

TEST0-2 I LSI testing pins. Fix to "L".

DV

AV

DD

DD

—8

—7

Accepts the SCK pulse, when CS is "L" level. Does not accept the SCL pulse

when CS is "H" level.

Indicates "H" level during command execution. When driven high, do not input a

command from the external micro-controller.

Outputs "H" level during recording or playback.MON O15

1s connected to the DI pin of the serial voice flash memory.FDI O23

1s connected to the DO pin of the serial voice flash memory.FDO I22

1s connected to the SCK pin of the serial voice flash memory.FSCK O24

1s connected to the CS pin of the serial voice flash memory.FCS O25

1s connected to the PRT pin of the serial voice flash memory.FPRT O26

1s connected to the RESET pin of the serial voice flash memory.FRESET O27

Oscillator connecting pins. When using an external clock, input the clock from

the XT pin and keep the XT pin open.

The LSI is reset and starts oscillation when "L" level is input, keep "L" level during

oscillation stabilization time. Set to "H" level after oscillation stabilizes.

Analog reference voltage (Signal Ground) output pinSG O1

Built-in OP amplifier's invention input pin. The non-invention input pin is

internally connected to SG.

Built-in OP amplifier's output pin

Built-in 12-bit AD converter's input signal

Connected to the LOUT pin when recording mode, and to the DA converter's

output pin when playback mode. Connected to the built-in LPF's input (FIN pin).

Built-in LPF's input pin

Built-in LPF's output pin. Connected to the AD converter's input (ADIN pin).

Built-in LPF's output pin. This is the output pin the played back waveform and

connected to the speaker driving amplifier.

Digital power supply pin. Insert a bypass capacitor of 0.1mF or higher between

this pin and DGND pin.

Digital DGND pinDGND —21

Analog power supply pin. Insert a bypass capacitor of 0.1mF or higher between

this pin and AGND pin.

Analog GND pinAGND —30

3/14

¡ Semiconductor MSM9888L

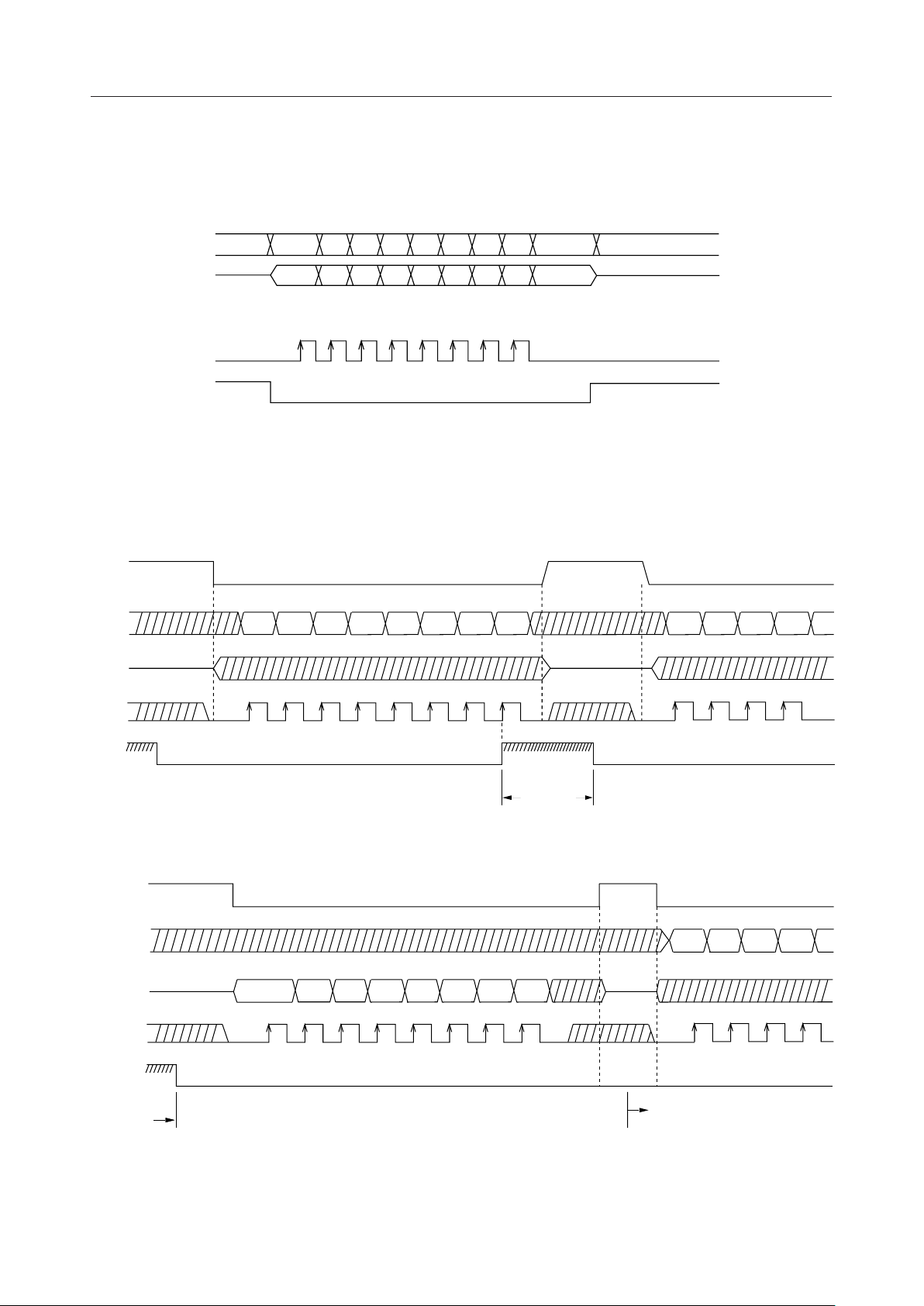

TIMING DIAGRAM

Flash driving Timing

MSB LSB

FDI

FDO

FSCK

FCS

MCU I/F driving Timing

<When data write>

CS

DI

DO

SCK

BUSY

Hi-Z

<When data read>

CS

DI

DO

First byte Second byte

MSB 2 3 4 5 6 7 LSB MSB 2 3 4

Data I/O not

permitted

MSB 2 3 4

MSB 2 3 4 5 6 7 LSB

SCK

BUSY

Preparation for

output data

Next data can

be input

4/14

¡ Semiconductor MSM9888L

APPLICATION CIRCUITS EXAMPLE

MCU

Voice input

DV

DI

DO

SCK

CS

RESET

BUSY

MON

LIN

LOUT

AMON

FIN

FOUT

DD

AV

DD

FDI

FDO

FSCK

FCS

FRESET

FPRT

MSM9888L

AOUT

SG

XT

XT

DI

DO

SCK

CS

RESET

PRT

MSM9891L

MSM9892L

MSC1157

MSM9893L

ADIN

DGND AGND

TEST0

TEST1

TEST2

5/14

Loading...

Loading...